Professional Documents

Culture Documents

Memory Interfacing With Example

Uploaded by

Sachin JaysenanOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Memory Interfacing With Example

Uploaded by

Sachin JaysenanCopyright:

Available Formats

7.

Memory Interfacing with Example

19 Aug. 2013

Module 1

Memory interfacing

Memory structure and its requirements. Basic concepts in memory interfacing. Address decoding and memory address.

Basics of 8085:

Types of memory and memory interfacing. Decoding techniques Absolute and Partial

Prepared By AJIT SARAF

Memory structure and its requirements (RAM)

Input data Input buffer A10

I N T E R N A L D E C O D E R

Memory structure and its requirements (ROM)

WR CS

A11

I N T E R N A L D E C O D E R

A0

R/W Memory N M 2048 8

N = number of register M = word length A0

EPROM 4096 8

N = number of register M = word length

Output buffer

RD

Output buffer Output data

CS RD

Output data Logic Diagram for RAM

Logic Diagram for EPROM

Prepared by AJIT SARAF

7. Memory Interfacing with Example

19 Aug. 2013

Example: If a memory is having 13 address lines and 8 data lines, then the number of registers / memory locations = 2^13 = 8129 word length = 8 bit Note: The number of address lines of a microprocessor depends on the Size of the memory. No. of lines

Memory size in bytes

Basic concepts in memory interfacing (Rules)

1) 8085 can access 64 KB of memory, since address bus is 16-bit. But it is not always necessary to use full 64Kbytes address space. The total memory size depends upon the application. 2) Generally EPROM is used as a program memory and RAM is used as data memory. when both are used then total 64 KB address will be shared by both. 3) The capacity of program memory and data memory depends on the application.

1 2 3 4 5 6 7

2 4 8 16 32 64 128

8 9 10 11 12 13 14 15 16

256 Bytes 512 Bytes 1024=1k 2048=2k 4096=4k 8129=8k 16384=16k 32768=32k 65536=64k

Basic concepts in memory interfacing (Rules)

4) It is not always necessary to select 1 EPROM and 1 RAM. We can have multiple EPROMs and multiple RAMs as per the requirement of application. 5) We can place EPROM / RAM anywhere in full 64 Kbytes address space. But program memory (EPROM) should be located from address 0000H since reset address of 8085 microprocessor is 0000H. 6) It is not always necessary to locate EPROM and RAM in consecutive memory addresses.

Q.1) Design a microprocessor system for 8085 such that it should contain 8k byte of EPROM and 8k byte of RAM using 1) Absolute / Full Decoding 2) Partial / Linear Decoding. Solution:

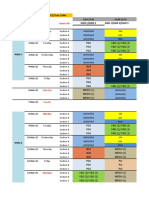

MEMORY ICs

Starting address Of EPROM End address Of EPROM Starting address Of RAM End address Of RAM A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Address

0 0 0 0 0 0 0 0 0 0 1 1 1

0 0 0 0

0 0

0 0 0 1 1 0 1

0000H 1FFFH 2000H 3FFFH

1 1 1

1 1 1

1 1

0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1

Prepared by AJIT SARAF

7. Memory Interfacing with Example

19 Aug. 2013

1 uF X1

D0-D7 VCC A0-A7 A8-A15 IOR IOW MEMR MEMW

6 MHz X2 1 uF + 5V + 5V

8085

ALE LE

WR A0 A7 RD IO/M

G A 7 Y5

READY

AD0 AD7

75 K RESETIN SW 1 uF

7 4 3 7 3

D0 D7

4 B L Y6 S 1 Y1 C 3 Y2 8

G1 G2

D7- D0 A12 A11 A10 A9 A8 A7-A0 OE VCC

D7- D0 A12 A11 A10 A9 A8 A7-A0 OE WR

EPROM (8K) 2764

G

RAM (8K) 6264 CS

TRAP RST 7.5 RST 6.5 RST 5.5 INTR INTA RESETOUT

A8 A15

A 7 4 A14 L Y0 B S 1 A15 C 3 Y1 8 G1 G2

A13

CS

Absolute Decoding Technique / Full Decoding

D0-D7 A0-A7 VCC A8-A15 IOR IOW MEMR MEMW

Q.2) Design a microprocessor system for 8085 such that it should contain 16k byte of EPROM and 4k byte of RAM using 8 Kbyte EPROMs and 2k byte RAMs. Solution:

Memory Ics

s.a of EPROM1 e.a of EPROM1 s.a of EPROM2

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

ADDRESS

WR RD IO/M

G A 7 Y5

4 B L Y6 S Y1 1 C 3 Y2 8

0 0 0 0 0 0 0 0

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 1 0 1 X X X X

0 1 0 1 X X X X

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0000H 1FFFH 2000H 3FFFH 4000H 47FFH 6000H 67FFH

G1 G2

D7- D0 A12 A11 A10 A9 A8 A7-A0 OE

D7- D0 A12 A11 A10 A9 A8 A7-A0 OE WR

e.a of EPROM2 s.a of RAM1 e.a of RAM1 s.a of RAM2

EPROM (8K) 2764 CS

RAM (8K) 6264 CS

A13

s.a of RAM2

Linear Decoding Technique / Partial Decoding

Prepared by AJIT SARAF

7. Memory Interfacing with Example

19 Aug. 2013

D0-D7 VCC A0-A7 A8-A15 IOR IOW MEMR MEMW

WR

A 7 Y5 4 RD L Y6 B S 1 Y1 IO/M 3 C 8 Y2 G1 G2

Q.3) Interface 2kb EPROM to 8085 using EPROM (1k X 4) chips, 74LS138 decoder and full address decoding and give the address map. Solution:

Memory Ics

s.a of EPROM1 e.a of EPROM1

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

ADDRESS

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 1 1 1 1

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0000H 03FFH 0000H 03FFH 2000H 23FFH 2000H 23FFH

VCC

D7- D0 A12 A11 A10 A9 A8 A7-A0 OE D7- D0 A12 A11 A10 A9 A8 A7-A0 OE

D7- D0 A10

A9

A8

A7-A0 OE WR

D7- D0 A10 A9

A8

A7-A0

OE WR

s.a of EPROM2 e.a of EPROM2 s.a of EPROM3 e.a of EPROM3

EPROM (8K) 2764 CS

EPROM (8K) 2764 CS

RAM (2K) 6116 CS

RAM (2K) 6116 CS

A13

A14

G

A 7 Y0 4 L Y1 S 1 Y2 3 8 Y3

A11 A12

A15

s.a of EPROM4 e.a of EPROM4

G1 G2

A11 A12

VCC

D0-D7 A0-A7 A8-A15

WR

A 7 Y5 4 RD L Y6 B S 1 Y1 IO/M 3 C 8 Y2 G1 G2

IOR IOW MEMR MEMW

Q.4) Design an 8085 based system for the following specifications: (a) CPU working at 3 MHz. (b) 8kB EPROM using 4kB devices. (c) 4kB RAM using 2kB devices. (d) One 8259 PIC in I/O mapped I/O. (e) One 8255 in I/O mapped I/O. Draw the complete interfacing diagram with latches, chip select logic, Reset circuit.

VCC

D7- D4 A9

A8 A7-A0 OE WR D3- D0 A9

A8 A7-A0 OE WR

D7- D4 A9 A8 A7-A0 OE WR D3- D0 A9 A8 A7-A0 OE WR

EPROM (1K) CS

EPROM (1K) CS

EPROM (1K) CS

EPROM (1K) CS

A13

A 7 Y0 4 A14 L B S 1 A15 3 Y1 C 8 G1 G2

A12

A11 A10

Prepared by AJIT SARAF

7. Memory Interfacing with Example

19 Aug. 2013

Solution: Memory Map:

Memory Ics

S.A. of EPROM1 E.A. of EPROM1 S.A. of EPROM2 E.A. of EPROM2 S.A. of RAM1 E.A. of RAM1 S.A. of RAM1 E.A. of RAM1

A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 ADDRESS

I/O Map

Ports and Registers Port A Port B Port C CWR 8259 Chip

A7 A15 A6 A14 A5 A13 A4 A12 A3 A11 A2 A10 A1 A9 A0 A8 ADDRESS

0 0 0 0 0

1 1 1 1 1

0 0 0 0 0

0 0 0 0 1

0 0 0 0 0

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0/1

40H 41H 42H 43H 50/51H

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 1 0 1 X X X X

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0 1 0 1 0 1 0 1

0000H 0FFFH 1000H 1FFFH 2000H 27FFH 3000H 37FFH

1 uF X1 WR 6 MHz X2 1 uF + 5V READY

VCC

D0-D7 A0-A7

A8-A15 IOR IOW MEMR MEMW

8085

ALE LE

A0 A7

+ 5V

AD0 AD7

75 K RESETIN SW 1 uF

7 4 3 7 3

D0 D7

A 7 Y5 4 RD L Y6 B S 1 Y1 IO/M 3 C 8 Y2 G1 G2

VCC

D7- D0 A11 A10 A9

A8 A7-A0 OE D7- D0 A11 A10 A9

A8 A7-A0 OE

D7- D0 A10

A9

A8

A7-A0 OE WR

D7- D0 A10 A9

A8

A7-A0

OE WR

EPROM 1(4K) CS

EPROM2 (4K) CS

RAM1 (2K) CS

RAM2 (2K) CS

TRAP RST 7.5 RST 6.5 RST 5.5 INTR INTA RESETOUT

A 7 Y0 4 A13 L Y1 B S 1 Y2 A14 3 C 8 Y3 G1 G2

A12

A11 A11

A8 A15

A15

Prepared by AJIT SARAF

7. Memory Interfacing with Example

19 Aug. 2013

VCC

D0-D7 A0-A7

A8-A15 IOR IOW MEMR MEMW

WR RD

University Questions (ELECTRONICS)

May-2012

1) Design a system based on 8085 with following configuration (i) 8K x 8 EPROM using 4K x 8 chips (10 Marks) (ii) 8K x 8 RAM using 4K x 8 chips Draw memory map and interface diagram.

A 7 Y5 4 L Y6 B S 1 Y1 IO/M 3 C 8 Y2 G1 G2

+ 5V

Dec-2012

VCC Vcc A0,A1 D0-D7 A0 D0-D7 SP/EN

IR0

A 7 Y4 4 A13 L B S 1 A14 3 C 8 Y5 G1 G2

A12

OE

PA PB PC

INTR INTA

8 WR 2 5 5

RESET OUT Reset

OE

8 WR 2 5 9

INT INTA CS

IR7

CAS0 CAS1 CAS2

CS

A15

2) Design 8085 based system with following specifications : (i) CPU operating at 3 MHz. (12 Marks) (ii) 16 KB program memory using 4 KB devices. (iii) 4 KB data memory using 2 KB devices. (iv) One 8 bit input port and one 8 bit output port performing interrupt driven I/O and interfaced in I/O mapped I/O mode. Use exhaustive decoding approach. Give detailed I/O map and memory map and neat interfacing diagram.

Prepared by AJIT SARAF

You might also like

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationFrom EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationNo ratings yet

- Microcontrollers: Introduction to 8051 and MSP430Document124 pagesMicrocontrollers: Introduction to 8051 and MSP430ManojKumarNo ratings yet

- Microprocessors Jto Lice Study Material SampleDocument16 pagesMicroprocessors Jto Lice Study Material SamplePrabha KaruppuchamyNo ratings yet

- 8085 Instruction SetDocument122 pages8085 Instruction SetgokulchandruNo ratings yet

- Class 2-Introduction To 8085 Microprocessor PDFDocument46 pagesClass 2-Introduction To 8085 Microprocessor PDFDeepika AgrawalNo ratings yet

- First Term Assignment CSC 471 Summer-2018: Rihab Rahman, 16103327, CSC 471, Sec-F, MAHDocument40 pagesFirst Term Assignment CSC 471 Summer-2018: Rihab Rahman, 16103327, CSC 471, Sec-F, MAHAbdur RazzakNo ratings yet

- Microprocessor Notes PDFDocument101 pagesMicroprocessor Notes PDFSuyash Sanjay SrivastavaNo ratings yet

- 8085Document56 pages8085Kunal MeherNo ratings yet

- M11 8085 ProgrammingDocument136 pagesM11 8085 ProgrammingPavan Deep100% (1)

- 8051 Microcontroller FAQDocument160 pages8051 Microcontroller FAQkranthi633No ratings yet

- C5 - Intro To 8085 - Hardware PDFDocument39 pagesC5 - Intro To 8085 - Hardware PDFsiti hajarNo ratings yet

- Introduction To 8085 MicroprocessorDocument35 pagesIntroduction To 8085 MicroprocessorCave BosNo ratings yet

- Presented by C.Gokul, Ap/Eee: Departments: Cse, It, Ece, Ece, Mech Regulation: 2013Document633 pagesPresented by C.Gokul, Ap/Eee: Departments: Cse, It, Ece, Ece, Mech Regulation: 2013SATHEESHNo ratings yet

- 8085 Microprocessor Architecture, Pin DiagramDocument10 pages8085 Microprocessor Architecture, Pin DiagramSachin Jaysenan0% (1)

- Microprocessor8085 BestDocument145 pagesMicroprocessor8085 BestDebashis TaraiNo ratings yet

- BE-II/IV-Sem-IV Computer Organization Lab Viva Questions With Answers-Osmania UniversityDocument15 pagesBE-II/IV-Sem-IV Computer Organization Lab Viva Questions With Answers-Osmania UniversitySirisha VamsiNo ratings yet

- MPMC PDFDocument210 pagesMPMC PDFAnonymous TxxI4MTTNo ratings yet

- 8085 Lab ManualDocument58 pages8085 Lab ManualShah JainamNo ratings yet

- Embedded Systems DesignDocument141 pagesEmbedded Systems DesignAryan Hrushik SharmaNo ratings yet

- Microprocessor Question BankDocument3 pagesMicroprocessor Question Bankstudy knowledge sumanjayNo ratings yet

- Microprocessor Fundamentals: by Physics Department Smt. CHM College, Ulhasanagar-3Document26 pagesMicroprocessor Fundamentals: by Physics Department Smt. CHM College, Ulhasanagar-3Prof. Yashavant p. JadhavNo ratings yet

- Microprocessor Programming: by Prof. Y. P. Jadhav. Physics Dept. Smt. C.H.M. College, Ulhasnagar-3Document104 pagesMicroprocessor Programming: by Prof. Y. P. Jadhav. Physics Dept. Smt. C.H.M. College, Ulhasnagar-3Prof. Yashavant p. JadhavNo ratings yet

- Assembly Language Program With 8085 MicroprocessorDocument22 pagesAssembly Language Program With 8085 MicroprocessorSithija AlwisNo ratings yet

- Microprocessors & Interfacing For GITAM University ECEDocument118 pagesMicroprocessors & Interfacing For GITAM University ECEDr Sreenivasa Rao Ijjada100% (1)

- 8085Document47 pages8085Govind GuptaNo ratings yet

- Biomedical Embedded SystemsDocument21 pagesBiomedical Embedded SystemsSathiya KumarNo ratings yet

- Microprocessor Lab ManualDocument97 pagesMicroprocessor Lab ManualSOWKATHKUTHBUDEEN_J14100% (2)

- THE 8051 MICROCONTROLLERDocument49 pagesTHE 8051 MICROCONTROLLERSabuj Ahmed100% (1)

- Bus Organization of 8085Document14 pagesBus Organization of 8085michaeledem_royalNo ratings yet

- 8051Document72 pages8051Arjun Aj100% (1)

- Block Diagram of 8085Document32 pagesBlock Diagram of 8085Shabd ShashankNo ratings yet

- Assembly Language Basics ExplainedDocument155 pagesAssembly Language Basics ExplainedIts MeNo ratings yet

- Experiments On 8085 MicroprocessorDocument18 pagesExperiments On 8085 MicroprocessorSaumya MohanNo ratings yet

- Microprocessors and Microcontrollers Module 1 - 5Document260 pagesMicroprocessors and Microcontrollers Module 1 - 5ncecentral0% (1)

- EE6502 MPMC UNIT 1-5 (Read-Only)Document607 pagesEE6502 MPMC UNIT 1-5 (Read-Only)Rajasekaran ThangarajuNo ratings yet

- The 8051 Microcontroler Based Embedded SystemsDocument43 pagesThe 8051 Microcontroler Based Embedded Systemsmanishpatel_790% (1)

- Power Electronics 05 60XXDocument58 pagesPower Electronics 05 60XXwhiteelephant93No ratings yet

- Washing Machine Control Using 8051 MicrocontrollerDocument4 pagesWashing Machine Control Using 8051 MicrocontrollerPrasath MurugesanNo ratings yet

- Microprocessor FileDocument93 pagesMicroprocessor FileHarshal AmbatkarNo ratings yet

- Microprocessor Interview Questions and AnswersDocument8 pagesMicroprocessor Interview Questions and AnswersGXTechno50% (2)

- The 8085 Microprocessor ArchitectureDocument30 pagesThe 8085 Microprocessor Architectureabhisheksharma12392% (13)

- Computer Organization: Instruction Set Architecture & Assembly Language ProgrammingDocument27 pagesComputer Organization: Instruction Set Architecture & Assembly Language ProgrammingbostanciNo ratings yet

- MPMC Rejinpaul (Other Univ) NotesDocument187 pagesMPMC Rejinpaul (Other Univ) NotesSheraaz0% (1)

- 8051 Microcontroller NotesDocument40 pages8051 Microcontroller Notesilg1100% (1)

- 8085 NotesDocument60 pages8085 NotesDavid TalamNo ratings yet

- Klu 8051Document165 pagesKlu 8051manvithbNo ratings yet

- BJT BasicsDocument55 pagesBJT BasicsMahendra DixitNo ratings yet

- Instruction Set of 8085Document43 pagesInstruction Set of 8085Abdul YaseenNo ratings yet

- ET7102-Microcontroller Based System DesignDocument19 pagesET7102-Microcontroller Based System DesignbalaNo ratings yet

- Programming Practices With SimulatorsDocument11 pagesProgramming Practices With Simulatorsarun0% (2)

- PPTDocument56 pagesPPTAkshay KumarNo ratings yet

- The 8085 Programming ModelDocument13 pagesThe 8085 Programming Modelapi-3850688100% (4)

- 8051 Instruction Set Rv01Document81 pages8051 Instruction Set Rv01lizhi0007No ratings yet

- Plasma Etching Processes for Interconnect Realization in VLSIFrom EverandPlasma Etching Processes for Interconnect Realization in VLSINicolas PossemeNo ratings yet

- Tutorial - 9Document15 pagesTutorial - 9divyarai12345No ratings yet

- 8085 PRJ Schematic 1Document44 pages8085 PRJ Schematic 1Jani ServiniNo ratings yet

- Microprocessor Lab Project EC - 316: Made ByDocument19 pagesMicroprocessor Lab Project EC - 316: Made ByJani ServiniNo ratings yet

- The 8051 ArchitectureDocument80 pagesThe 8051 ArchitectureManoj GadgeNo ratings yet

- 8085 Microprocessor Architecture, Pin DiagramDocument10 pages8085 Microprocessor Architecture, Pin DiagramSachin Jaysenan0% (1)

- Supporting Hardware For 8085Document2 pagesSupporting Hardware For 8085Sachin JaysenanNo ratings yet

- IO Data Transfer TechniquesDocument5 pagesIO Data Transfer TechniquesSachin JaysenanNo ratings yet

- Supporting Hardware For 8085Document2 pagesSupporting Hardware For 8085Sachin JaysenanNo ratings yet

- Program To Interface Stepper MotorDocument2 pagesProgram To Interface Stepper MotorSachin JaysenanNo ratings yet

- Harvest Moon Friends of Mineral Town GuideDocument59 pagesHarvest Moon Friends of Mineral Town GuideSachin JaysenanNo ratings yet

- Microprocessor HistoryDocument4 pagesMicroprocessor HistorySachin JaysenanNo ratings yet

- UntitledDocument1 pageUntitledSachin JaysenanNo ratings yet

- Binomial TheoremDocument17 pagesBinomial TheoremSachin JaysenanNo ratings yet

- Conversions Naming OBIADocument5 pagesConversions Naming OBIAVenkat SabbaniNo ratings yet

- Logging and Monitoring LogsDocument48 pagesLogging and Monitoring LogsirvingNo ratings yet

- JCB Online Interface Guide (2019)Document87 pagesJCB Online Interface Guide (2019)mitxael83No ratings yet

- Article ReviewDocument5 pagesArticle Reviewnuraerissa fadzilNo ratings yet

- IFS ERP PresentationDocument13 pagesIFS ERP Presentationbajihsn100% (1)

- Project plan and WBS for community health insurance systemDocument5 pagesProject plan and WBS for community health insurance systemLens NewNo ratings yet

- NovaDocument946 pagesNovaFeri IgnacNo ratings yet

- Sesi 1 Pendahuluan Big DataDocument78 pagesSesi 1 Pendahuluan Big DataIka PratiwiNo ratings yet

- Blockchain For Iot: The Challenges and A Way Forward: July 2018Document13 pagesBlockchain For Iot: The Challenges and A Way Forward: July 2018ronicaNo ratings yet

- The Essential Software RequirementDocument20 pagesThe Essential Software RequirementFARRUKH QAMARNo ratings yet

- IMS Transaction ManagerDocument147 pagesIMS Transaction ManagerBalaji Kishore Kumar100% (2)

- 04 Oracle Big Data Appliance Deep DiveDocument49 pages04 Oracle Big Data Appliance Deep DiveShiva RokaNo ratings yet

- The Main Elements of A Good SLADocument6 pagesThe Main Elements of A Good SLAFranz Lawrenz De TorresNo ratings yet

- Journal Subscription Form Indian Journals - 2021Document2 pagesJournal Subscription Form Indian Journals - 2021NISHANTHNo ratings yet

- Supplier Enablement Program Checklist: Phase Step Description 1. Identify Project Team Program PlanningDocument4 pagesSupplier Enablement Program Checklist: Phase Step Description 1. Identify Project Team Program PlanningbupeshNo ratings yet

- Updated - Term - 3 - Time Table - Batch (20-22)Document21 pagesUpdated - Term - 3 - Time Table - Batch (20-22)Nikhil SinghNo ratings yet

- Egd Protocol ManualDocument70 pagesEgd Protocol ManualDIPANJALI RANINo ratings yet

- Create Blog Account Use CaseDocument30 pagesCreate Blog Account Use CaseA ANo ratings yet

- DBA Database Management Checklist Written byDocument3 pagesDBA Database Management Checklist Written bydivandannNo ratings yet

- Hacking Database ServersDocument7 pagesHacking Database ServersPuspala ManojkumarNo ratings yet

- Assignment - Cloud ComputingDocument26 pagesAssignment - Cloud ComputingBiju PoudelNo ratings yet

- Data Integration Best PracticesDocument17 pagesData Integration Best PracticesSNo ratings yet

- Tic Tac Toe Cs ProjectDocument29 pagesTic Tac Toe Cs ProjectABU SALEEMNo ratings yet

- Data Mining Notes1Document56 pagesData Mining Notes1SOORAJ CHANDRANNo ratings yet

- Splunk 1003 - Question BanksDocument21 pagesSplunk 1003 - Question BanksnagarjunaNo ratings yet

- 9 - Analysis and Design - R0Document56 pages9 - Analysis and Design - R0Anonymous nPT6LOnRXNo ratings yet

- Introduction To CERTIFIED BLOCKCHAIN & SUPPLY CHAIN EXPERTDocument14 pagesIntroduction To CERTIFIED BLOCKCHAIN & SUPPLY CHAIN EXPERTPrashant YadavNo ratings yet

- Problem Solving Chatbot For DatastructureDocument15 pagesProblem Solving Chatbot For Datastructurekhedlekar shrutiNo ratings yet

- Chess Master ClubDocument2 pagesChess Master Clubg160689No ratings yet

- Bloomberg in A NutshellDocument86 pagesBloomberg in A Nutshellneilli1992No ratings yet