Professional Documents

Culture Documents

Gate Ringing

Uploaded by

Bhuvaneshwari_iraOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Gate Ringing

Uploaded by

Bhuvaneshwari_iraCopyright:

Available Formats

6.

002 Demo# 12

Gate Ringing Agarwal Fall 2000

Lecture 15

Purpose: This demo examines second order responses using two cascaded inverters. By lowering RL in the first

inverter (in an attempt to speed up the RC delay), the middle voltage (between the two inverters) is shown to

ring. This is caused by inductance in the loop between ground and the middle voltage.

Steps:

1. Show the input, middle and output voltages for the circuit with RL set at the high value (2kOhm). Note the

RC behavior of the middle voltage, and the resulting delay at the output.

2. Switch the 300 Ohm resistor into the circuit. Observe the ringing behavior in the middle voltage.

2K 300 2K

B

A B C

Description: Gate Ringing

To show the ringing taking place, set the switch on the board to on position and observe CH1 , CH2

and CH3.

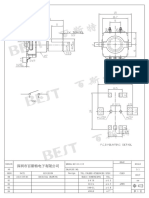

Note: for schematic diagram and pins output, see next page Fg 1 and Fg2 for more detail.

Oscilloscope Setup

CH V/DIV OFFSET MODE FUNC MATH VERTICAL HORIZONTAL

1 on 5 -9.31 DC off

2 on 5 170 DC off

3 on 5 9.70 DC off

4 off off

Horizontal: 1 us/Div Acquisition: Trigger: CH1

Waveform Generator Setup Power Supply Setup

UNIT WAVE AMP OFFSET FREQ +6 +25 -25 OUTPUT

FG1 Square 5 2.5 5 KHZ 0 5 on

Note: FG1 should be set @ Hi Z

You might also like

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsFrom EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsRating: 3 out of 5 stars3/5 (2)

- The Setting List of Generator Protection Relay (CEBU-P1-20-V-220003)Document39 pagesThe Setting List of Generator Protection Relay (CEBU-P1-20-V-220003)Sugar RayNo ratings yet

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Load Panel 1 - L/O + P/O Ligthing Outlet & Power OutletDocument6 pagesLoad Panel 1 - L/O + P/O Ligthing Outlet & Power OutletBhemalee Tono DimalaluanNo ratings yet

- Shimadzu UD-150L X-Ray - Installation GuideDocument35 pagesShimadzu UD-150L X-Ray - Installation GuideLuis Fernando Garcia S100% (1)

- Documentation For Approval: TO: Customers DATE: 2005.09.26Document36 pagesDocumentation For Approval: TO: Customers DATE: 2005.09.26barber1100% (1)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Demo 19Document2 pagesDemo 19MitpdfNo ratings yet

- Silicon Epitaxial Planar Transistor 2SA1179: Galaxy ElectricalDocument5 pagesSilicon Epitaxial Planar Transistor 2SA1179: Galaxy ElectricalsacralNo ratings yet

- Marking SO SMD-2SA1162Document5 pagesMarking SO SMD-2SA1162Wee Chuan PoonNo ratings yet

- Multi Stage Transistero AmplifierDocument4 pagesMulti Stage Transistero Amplifierkaran007_mNo ratings yet

- 2SD965 OkDocument4 pages2SD965 OkHuu NguyenNo ratings yet

- 2SB1197-MarkingCode AHpDocument5 pages2SB1197-MarkingCode AHpd4wq3No ratings yet

- Galaxy S9015 Silicon Epitaxial Planar Transistor SpecificationDocument5 pagesGalaxy S9015 Silicon Epitaxial Planar Transistor SpecificationFrame JoshNo ratings yet

- 2sa2018 - SMD Marking BW4Document5 pages2sa2018 - SMD Marking BW4julio montenegro100% (1)

- Lab 08Document3 pagesLab 08Juan TarquiNo ratings yet

- Toshiba TB6500AH Bipolar Stepper and DC Motor Driver ICDocument18 pagesToshiba TB6500AH Bipolar Stepper and DC Motor Driver ICJavier CuraNo ratings yet

- Silicon Epitaxial Planar Transistor 2SA1015Document5 pagesSilicon Epitaxial Planar Transistor 2SA1015James Edwin Arlantt TorresNo ratings yet

- Project: Layyah Combined Cycle Power Plant: Sub Station: Equipment: Panel Type Bay Ref: DateDocument3 pagesProject: Layyah Combined Cycle Power Plant: Sub Station: Equipment: Panel Type Bay Ref: DatesamlashNo ratings yet

- BL Galaxy 2SC1815 Transistor SpecificationDocument5 pagesBL Galaxy 2SC1815 Transistor SpecificationJose Eduardo Sanchez LarretaNo ratings yet

- Application Note AN-1214: LED Buck Converter Design Using The IRS2505LDocument16 pagesApplication Note AN-1214: LED Buck Converter Design Using The IRS2505LVitaliyGNo ratings yet

- Silicon Epitaxial Planar Transistor 2SC1623: Galaxy ElectricalDocument5 pagesSilicon Epitaxial Planar Transistor 2SC1623: Galaxy Electricalanu0393No ratings yet

- High-Performance PNP Transistor SpecificationDocument5 pagesHigh-Performance PNP Transistor SpecificationEisenhower Garcia LealNo ratings yet

- BL Galaxy 2SA1204 Transistor SpecDocument4 pagesBL Galaxy 2SA1204 Transistor Specmhmd193No ratings yet

- Single-Stage BJT Amplifiers: Experiment-2Document19 pagesSingle-Stage BJT Amplifiers: Experiment-2karan007_mNo ratings yet

- Galaxy Electrical NPN General Purpose Transistor MMBT5551Document5 pagesGalaxy Electrical NPN General Purpose Transistor MMBT5551Y. Leonel MolinaNo ratings yet

- NPN Silicon Epitaxial Planar Transistor 2PD601AW: Galaxy ElectricalDocument4 pagesNPN Silicon Epitaxial Planar Transistor 2PD601AW: Galaxy ElectricalГеннадий БабенкоNo ratings yet

- EC11I-152 DatasheetDocument6 pagesEC11I-152 DatasheetJuan Pablo Montoya CardenasNo ratings yet

- LIC Lab ManualDocument94 pagesLIC Lab Manualmamathasuvarna1121No ratings yet

- 2 SC 2655Document5 pages2 SC 2655alshhbndrNo ratings yet

- Sound Activated Switch: EE-389 Electronic Design Lab-II Project Report, EE Dept, IIT Bombay, Submitted On 02-12-2005Document12 pagesSound Activated Switch: EE-389 Electronic Design Lab-II Project Report, EE Dept, IIT Bombay, Submitted On 02-12-2005Skfgi EceNo ratings yet

- Technology: 2 Phase DC Motor Drive Ic General DescriptionDocument13 pagesTechnology: 2 Phase DC Motor Drive Ic General DescriptionalexNo ratings yet

- AEC Manuel For AutnomusDocument24 pagesAEC Manuel For Autnomusanon_648461124No ratings yet

- MMBT5551 NPN General Purpose Transistor SpecificationDocument3 pagesMMBT5551 NPN General Purpose Transistor SpecificationJuly DemariaNo ratings yet

- MMBT5401 Marking 2LDocument3 pagesMMBT5401 Marking 2LJuly DemariaNo ratings yet

- Silicon Epitaxial Planar Transistor 2SC945: Galaxy ElectricalDocument5 pagesSilicon Epitaxial Planar Transistor 2SC945: Galaxy ElectricalAri RamwanNo ratings yet

- Integrated Circuits: Multistage Amplifiers, Current Sources & Current MirrorsDocument25 pagesIntegrated Circuits: Multistage Amplifiers, Current Sources & Current MirrorsMalik JameelNo ratings yet

- An Dispatch 20BDocument6 pagesAn Dispatch 20B11031974didinNo ratings yet

- Galaxy 2SA1662 Transistor SpecificationDocument5 pagesGalaxy 2SA1662 Transistor SpecificationFathe BallaNo ratings yet

- Aec Lab ManualDocument33 pagesAec Lab Manualganga_ch1No ratings yet

- Recitation 050814Document5 pagesRecitation 050814William Zhuang100% (1)

- PNP Silicon Epitaxial Planar Transistor 2SA1611Document5 pagesPNP Silicon Epitaxial Planar Transistor 2SA1611khanNo ratings yet

- BUB941ZTDocument8 pagesBUB941ZTrun awayNo ratings yet

- ECET 2310 Lab 6 - Differential Amplifier PerformanceDocument4 pagesECET 2310 Lab 6 - Differential Amplifier Performancetarottaurus54No ratings yet

- C UK and Sepic ConverterDocument15 pagesC UK and Sepic ConverterSon TelmanNo ratings yet

- Experiment 3Document3 pagesExperiment 3ugurgul123No ratings yet

- 2 S 1Document8 pages2 S 1Nelson Naval CabingasNo ratings yet

- LIC Lab ManualDocument89 pagesLIC Lab ManualTAMILAN XEROX VtmNo ratings yet

- 2sc3263 Ds enDocument8 pages2sc3263 Ds enNam TàoNo ratings yet

- BJTDocument18 pagesBJTMohd Nasrul Shafiq MnsNo ratings yet

- Plaza Stage NewDocument11 pagesPlaza Stage NewFelix Albit Ogabang IiiNo ratings yet

- Silicon Epitaxial Planar Transistor 2SA1235A: Galaxy ElectricalDocument4 pagesSilicon Epitaxial Planar Transistor 2SA1235A: Galaxy ElectricalGABRIEL ALFONSONo ratings yet

- Skhi 22B DatasheetDocument9 pagesSkhi 22B DatasheetRakesh RoyNo ratings yet

- Temp 13083111391929Document13 pagesTemp 13083111391929sebas ruizNo ratings yet

- High-performance NPN transistor specificationDocument5 pagesHigh-performance NPN transistor specificationMtfNo ratings yet

- Galaxy Electrical PNP General Purpose Amplifier 2SB1132Document5 pagesGalaxy Electrical PNP General Purpose Amplifier 2SB1132Ssr ShaNo ratings yet

- EDC Lab ManualDocument46 pagesEDC Lab ManualMOUNIRAGESHNo ratings yet

- An2001 Application Note: Vipower™: The Viper53-E Single Output Reference Board With 90 To 264 Vac Input, 24 W OutputDocument6 pagesAn2001 Application Note: Vipower™: The Viper53-E Single Output Reference Board With 90 To 264 Vac Input, 24 W OutputamitNo ratings yet

- Demo 21 RPDocument4 pagesDemo 21 RPMitpdfNo ratings yet

- Demo 24Document4 pagesDemo 24MitpdfNo ratings yet

- 6.002 Demo# 28 Boost Converter Agarwal Fall 00: Purpose: A DC/DC Converter Using A Boost Topology StepsDocument4 pages6.002 Demo# 28 Boost Converter Agarwal Fall 00: Purpose: A DC/DC Converter Using A Boost Topology StepsMitpdfNo ratings yet

- Diode Circuits and CharacteristicsDocument3 pagesDiode Circuits and CharacteristicsBhuvaneshwari_iraNo ratings yet

- Demo 22Document3 pagesDemo 22MitpdfNo ratings yet

- 6002L23Document13 pages6002L23MitpdfNo ratings yet

- Demo 18 RPDocument3 pagesDemo 18 RPMitpdfNo ratings yet

- Demo 21Document6 pagesDemo 21Mitpdf100% (1)

- Demo 19 BDocument2 pagesDemo 19 BMitpdfNo ratings yet

- Energy and Power: Circuits ElectronicsDocument15 pagesEnergy and Power: Circuits ElectronicsMitpdfNo ratings yet

- Violating The Abstraction Barrier: Circuits ElectronicsDocument13 pagesViolating The Abstraction Barrier: Circuits ElectronicsMitpdfNo ratings yet

- Demo 20Document3 pagesDemo 20MitpdfNo ratings yet

- Energy and Power in RC NetworkDocument2 pagesEnergy and Power in RC NetworkBhuvaneshwari_iraNo ratings yet

- 6002L24Document20 pages6002L24MitpdfNo ratings yet

- Demo 27Document2 pagesDemo 27MitpdfNo ratings yet

- 6.002 Demo# 26 RC Response Agarwal Fall 00Document3 pages6.002 Demo# 26 RC Response Agarwal Fall 00MitpdfNo ratings yet

- Demo 17Document2 pagesDemo 17Mitpdf100% (3)

- Demo 19 ADocument2 pagesDemo 19 AMitpdfNo ratings yet

- Energy and Power in RC NetworkDocument2 pagesEnergy and Power in RC NetworkBhuvaneshwari_iraNo ratings yet

- Demo 15Document1 pageDemo 15MitpdfNo ratings yet

- Demo 23Document3 pagesDemo 23MitpdfNo ratings yet

- 6.002 Demo# 13 First Order Sinusoidal Steady State Agarwal Fall 00Document3 pages6.002 Demo# 13 First Order Sinusoidal Steady State Agarwal Fall 00MitpdfNo ratings yet

- Gate DelayDocument3 pagesGate DelayBhuvaneshwari_iraNo ratings yet

- Demo 10Document3 pagesDemo 10MitpdfNo ratings yet

- 6.002 Demo# 09GS (Load Set Up demo#09GS - Set) MOSFET Inverting Amplifier Small Signal Fall 00Document3 pages6.002 Demo# 09GS (Load Set Up demo#09GS - Set) MOSFET Inverting Amplifier Small Signal Fall 00MitpdfNo ratings yet

- Demo 08Document2 pagesDemo 08MitpdfNo ratings yet

- Demo 06Document3 pagesDemo 06Mitpdf100% (1)

- Demo 07Document2 pagesDemo 07Mitpdf100% (1)