Professional Documents

Culture Documents

HC 11-2

Uploaded by

theartofthedeviladamOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

HC 11-2

Uploaded by

theartofthedeviladamCopyright:

Available Formats

IUFM de Toulouse - 68HC11 - 13/01/98

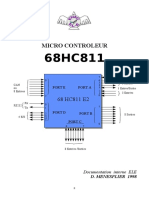

Le microcontrôleur 68HC11 ( Motorola )

I/ Présentation de l’architecture d’un microcontrôleur

Contrôles ( R/W, E, ... )

Adresses 16 bits

Données 8 bits

Mémoires Periphériques

RAM µP Liaisons séries

ROM Liaisons parallèles

EEPROM TIMER

etc.

Microcontrôleur 68HC11

Œ Rôle du µC

La seule fonction du µP est de prendre des données, de les traiter, puis de les renvoyer vers

les périphériques ou les mémoires.

• Découpage du plan mémoire

Le plan mémoire est fonction du bus d’adresse.

16

Sur le 68HC11, son format est de 16 bits. On peut donc adresser 2 octets, soit 64Ko.

Il existe diverses versions de 68HC11 ( A1, A8, F1, etc.) qui disposent de leur propre plan

mémoire, veuillez vous reporter à la doc constructeur pour de plus amples informations à ce

sujet.

II/ Les registres internes

ΠRegistres 8 Bits : A, B, CCR

• A Ces 2 registres servent pratiquement à tout faire au format 8 Bits.

• B

Leur juxtaposition donnent le registre D ( 16 bits ), de la manière suivante :

b7 b0 b7 b0

A B

D

b15 b0

Guillaume COMTE - Jean-Louis CALMON Page 1

IUFM de Toulouse - 68HC11 - 13/01/98

• CCR : le registre d’état

b7 b0

S X H I N Z V C

Le registre CCR est positionné par l’instruction en cours, à la fin de son traitement par le

processeur. Bien qu’on puisse regrouper différentes instructions entre elles de manière à

connaître leur résultat vis à vis de ce registre, chaque instruction va influencer sur le CCR

d’une manière qui lui est propre. Pour lever le moindre doute, le seul recours est le jeu

d’instructions fourni par le constructeur qui fait état des bits suite à une instruction donnée.

Signification des différents bits :

å C ( Carry : Retenue ) : est mis à 1 lorsque le résultat de l’instruction génère une

retenue.

Le terme retenue doit être pris au sens large du terme, elle concerne les

instructions qui se rapportent à :

n l’arithmétique

n les décalages / rotations

n les comparaisons

n les calculs de compléments

n etc.

å V ( oVerflow = débordement ) : positionné à 1 lorsque l’opération arithmétique a

généré un débordement de l’accumulateur utilisé.

Ex : LDAA #255

INCA ici A=0

et V=1

En effet, il y a débordement car la valeur de A devrait

être 256 ce que ne peut stocker un registre 8 bits, et qui

passe donc à 0.

å Z ( Zéro ) : passe à 1 lorsque le résultat de l’instruction est nul.

Ex : CLRA ou LDA #01

DECA ici Z=1 car

A=0

å N ( Négatif ) : positionné à 1 si le résultat de la dernière opération arithmétique

réalisée est négative, c’est à dire lorsque le bit de poids fort vaut 1 ( cas des nombres

signés ).

å H ( Half Carry = demi retenue ) : utilisé lors des calculs DCB ( Décimal Codé

Binaire ).

å I ( Interrupt mask = masque d’interruption ) : ce bit inhibe les interruptions lorsqu’il

vaut 1.

Guillaume COMTE - Jean-Louis CALMON Page 2

IUFM de Toulouse - 68HC11 - 13/01/98

å X ( XIRQ interrupt mask = masque d’interruption XIRQ ) : de la même manière

que le bit I, X inhibe l’interruption XIRQ lorsqu’il vaut 1.

å S ( Stop ) : positionné à 1, l’exécution de l’instruction STOP est remplacée par un

NOP.

Remarque : l’instruction STOP fait passer le processeur en mode

« endormi ». Cela signifie que l’horloge interne est arrêtée. Lorsque le

processeur est réveillé, cette horloge sera valide après un certains nombres

de cycles dus à un état transitoire de mise en oscillation du quartz ( ce qui

peut être à proscrire dans certaines applications de type temps réel ).

• Registres 16 bits : D, X, Y, SP, PC.

• D : Juxtaposition des registres A et B ( 8 bits ).

• X : Voici la version du « registre à tout faire » au format 16 bits.

Contrairement à ses confrères 8 bits ( A et B ), il assure aussi un rôle

fondamental d’index.

• Y : Idem au registre X.

Cependant, les instructions concernant ce registre sont codées avec un octet

supplémentaire par rapport au registre X, et donc, prennent un cycle machine en plus

lors de leur exécution.

Donc, ayez le réflexe de :

1. Utiliser de préférence le registre X au registre Y de manière générale

2. Lorsque deux boucles sont imbriquées, utilisez le registre X pour la

boucle centrale

• SP ( Stack Pointer = pointeur de pile ) : indique en permanence la prochaine

adresse de l’octet libre de la pile.

Fonctionnement de la pile :

donnée 8 bits

Sauvegarde dans la Chargement à partir de la

pile pile

Octet → ( SP ) SP ← SP+1

SP ← SP-1 ( SP ) → Octet

donnée 16 bits

Sauvegarde dans la Chargement à partir de la

pile pile

Octet → ( SP ) SP ← SP+1

Guillaume COMTE - Jean-Louis CALMON Page 3

IUFM de Toulouse - 68HC11 - 13/01/98

SP ← SP-1 ( SP ) → Octet

Octet → ( SP ) SP ← SP+1

SP ← SP-1 ( SP ) → Octet

Ex : LDS #$FF Initialisation de la pile

LDAA#$33

LDX #$1234

PSHA Stockage dans la pile ( on empile )

Avant PSHA Après PSHA

Pointeur S Adresse Mémoire Pointeur S Adresse Mémoire

FC XX FC XX

FD XX FD XX

FE XX → FE XX

→ FF XX FF 33

.

. Suite du programme

.

PULA Chargement à partir de la pile ( on dépile )

Avant PULA Après PULA

Pointeur S Adresse Mémoire Pointeur S Adresse Mémoire

FC XX FC XX

FD XX FD XX

→ FE XX FE XX

FF 33 → FF 33

PSHX

Avant PSHX Après PSHX

Pointeur S Adresse Mémoire Pointeur S Adresse Mémoire

FC XX FC XX

FD XX → FD XX

FE XX FE 12

→ FF 33 FF 34

L’empilement d’un registre 16 bits se décompose en deux phases ( transparent pour

l’utilisateur ) :

1ère phase FC XX

Stockage poids faible FD XX

→ FE XX

Pointeur S Adresse Mémoire FF 34

Guillaume COMTE - Jean-Louis CALMON Page 4

IUFM de Toulouse - 68HC11 - 13/01/98

2ème phase → FD XX

Stockage poids fort FE 12

FF 34

Pointeur S Adresse Mémoire

FC XX

PULX Chargement à partir de la pile ( on dépile )

Avant PULX Après PULX

Pointeur S Adresse Mémoire Pointeur S Adresse Mémoire

FC XX FC XX

→ FD XX FD XX

FE 12 FE 12

FF 34 → FF 34

Le dépilement d’un registre 16 bits se décompose en deux phases ( transparent pour

l’utilisateur ) :

1ère phase 2ème phase

Dépilement poids fort Dépilement poids faible

Pointeur S Adresse Mémoire Pointeur S Adresse Mémoire

FC XX FC XX

FD XX FD XX

→ FE 12 FE 12

FF 34 → FF 34

Remarque : - il FAUT INITIALISER LA PILE au début du programme

- la gestion de la pile est automatique

- le contenu de la pile n’est pas effacé ( voir tableaux plus haut )

- la pile est utilisée par les instructions suivantes : PSHx, PULx, JSR, RTS, RTI.

• PC ( Program Counter = Compteur ordinal ) : ce registre 16 bits contient en

permanence l’adresse de la prochaine instruction à exécuter.

III/ Les modes d’adressage

Rappel : constitution d’une instruction

Lors de la compilation, les instructions sont traduites en codes hexadécimaux comprises par le

processeur. Elles se décomposent en deux parties :

- le code opérateur, qui correspond au code d’une instruction.

- l’opérande, qui est la donnée utile de l’instruction.

Guillaume COMTE - Jean-Louis CALMON Page 5

IUFM de Toulouse - 68HC11 - 13/01/98

Instruction Code héxa

LDAA #$80 86 80

Code opérateur Opérande

Exemple

Œ Adressage inhérent

Dans ce mode, les instructions n’ont ni opérande, ni « saut relatif », elles se suffisent à elles

mêmes.

Ex : CLRA

COMA

ABA

ABX

etc.

• Adressage immédiat

Dans ce mode, la donnée à traiter se trouve immédiatement après l’instruction.

Le signe caractéristique est le dièse : #.

Ex : LDAA #$15 A ← $15

SUBA #03 A ← A-03

ORAA #04 A ← A ou 04

etc.

Ž Adressage étendu

La donnée utile se trouve à l’adresse définie par l’opérande de l’instruction.

Ex : LDAA $3000

ANDA $3001

STAA $3002

Contenu de la mémoire :

Adresse Contenu Remarque

$3000 $33 A ← $33

$3001 $11 A ← A and $11

$3002 $11 A → $3002

Guillaume COMTE - Jean-Louis CALMON Page 6

IUFM de Toulouse - 68HC11 - 13/01/98

• Adressage direct

Ce mode est pratiquement identique à l’adressage étendu. La différence se situe au niveau du

codage de l’adresse : alors que dans l’étendu on note l’adresse entière ( 16 bits ), ici on va

indiquer que l’octet de poids faible de l’adresse ( 8 bits ).

Les 8 bits de poids fort qui manquent pour reconstituer l’adresse sont définis, sur des

µP tel que le 6809, dans un registre spécifique DP ( Direct Page ).

Suivant la valeur de DP, on accédera à différents blocs mémoires de 256 octets chacun.

Ex :

Adresse Contenu Adress Contenu Adresse Contenu

e

$0000 01 $0100 22 $1000 33

$0001 03 $0101 04 $1001 05

Avec la même initialisation LDAA $00

Si DP = $00 A = 01 Correspondrait à LDAA $0000

DP = $01 A = 22 ( mode étendu ) LDAA $0100

DP = $10 A = 33 LDAA $1000

De même : LDAA $01

Si DP = $00 A = 03 Correspondrait à LDAA $0001

DP = $01 A = 04 ( mode étendu ) LDAA $0101

DP = $10 A = 05 LDAA $1001

Sur le HC11, le registre DP n’existe pas ! La valeur de l’octet de poids fort est nulle.

L’adressage direct permet d’adresser les 256 premiers octets de la mémoire.

Avantages : l’adresse 16 bits est codée sur 8 bits.

F on économise un octet, donc 1 cycle machine par instruction.

• Adressage indexé

Ce mode utilise le même principe que l’adressage étendu, mais ici l’adresse est contenue dans

un index 16 bits : X ou Y.

Ex :

Adresse Contenu Adresse Contenu

Guillaume COMTE - Jean-Louis CALMON Page 7

IUFM de Toulouse - 68HC11 - 13/01/98

$1000 66 $009A 51

$009B 52

LDX #$1000 X ← $1000

LDAA ,X A ← 66

LDY #$009A

INY

LDAB ,Y B ← 52

Utilisation fréquente : Lecture, écriture, copie de tables.

• Déplacement nul

Correspond au cas précédent. L’indication du déplacement nul est facultatif. Ainsi, ne

soyez pas surpris de voir apparaître suite à un désassemblage :

LDAB 0,Y

Après avoir tapé LDAB ,Y dans le code source.

• Déplacement non nul

L’adresse résultante de l’opérande est la somme du déplacement avec l’adresse.

Adresse résultante = Déplacement + Index

Remarque : Le déplacement est codé sur un octet non signé. Ainsi, il ne peut être que

positif et compris entre 0 et 255.

Ex :

Adresse Contenu

X 03

X+1 04

X+2 05

LDAA $02 ,X A ← 05

Remarque d’ordre générale

Erreur fréquemment réalisée :

Guillaume COMTE - Jean-Louis CALMON Page 8

IUFM de Toulouse - 68HC11 - 13/01/98

Déterminer les valeurs de A et X suite aux instructions suivantes :

LDX #01 LDAB #$55

STX $100 STAB $103

LDAA $100 LDX $103

Valeur de A ? Valeur de X ?

( Solutions page suivante )

Réponses : A=00

X=55xx xx = octet indéterminé

Le format de la donnée «utile»

est du même format que l’instruction.

Ex :

LDX # $10

X est un registre 16 bits, donc X = $0010 !

STX $100

X 16 bits, donc l’instruction va stocker 2 octets à partir de $0100.

Adresse Contenu Remarque

$0100 $00 Poids fort de X

$0101 $10 Poids faible de X

Guillaume COMTE - Jean-Louis CALMON Page 9

IUFM de Toulouse - 68HC11 - 13/01/98

LDAA #$1FF ® NON ! ! ! !

A registre 8 bits, donc IMPOSSIBLE car le format de la donnée est supérieur à 8 bits.

LDAA #$FF

STAA $100

A registre 8 bits, donc va stocker 1 octet à partir de $0100.

Adresse Contenu

$0100 $FF

‘ Adressage relatif

Ce mode est en étroite relation avec le registre PC.

On a vu que le PC est un registre 16 bits qui contient en permanence l’adresse de la prochaine

instruction à exécuter :

Ex : Adresse du code Code Instruction

B600 86 01 LDAA #01

B602 B7 01 00 STAA $0100

Lorsque le processeur exécute LDAA #01, qui se trouve à l’adresse B600, le PC pointe sur

l’instruction suivante, soit PC = B602.

Les instructions de branchement utilisent cet adressage relatif.

L’opérande d’une telle instruction indique en fait la valeur à ajouter au PC pour effectuer le

saut.

Cette valeur est codée sur 1 octet signé :

ë On peut donc effectuer un saut de -128 à +127, soit de 128 octets

avant à 127 après la valeur actuelle du PC.

Analysons le programme suivant et cherchons la valeur du branchement ( xx ) :

Adresse du code Code Instruction Remarque

B600 B6 03 LDAA #03 Quand le processeur exécute

B602 4A Ici DECA l’instruction BNE,

B603 26 xx BNE Ici le PC = B605.

Guillaume COMTE - Jean-Louis CALMON Page 10

IUFM de Toulouse - 68HC11 - 13/01/98

B605

Le branchement vaudra donc B602-B605 = -03, soit sur 1 octet signé $F9.

Donc xx = $F9.

Pour calculer la valeur du saut, déterminer :

- la valeur du PC lors de l’exécution de l’instruction de branchement, PCi.

- la valeur du PC de l’instruction où renvoie le branchement, PCf.

- calculer la valeur du saut = PCf - PCi

Dans l’exemple précédent, PCi = B605

PCf = B602

Autre exemple : Adresse du code Code Instruction

B600 20 xx BRA là

B602 7E 00 FE JMP $00FE

B605 86 30 là LDAA #$30

Lorsque le processeur exécute BRA, le PC vaut B602, PCi = B602.

On souhaite brancher en B605, PCf = B605.

Saut = PCf - PCi

= B605 - B602

= 03

Donc xx = 03.

Guillaume COMTE - Jean-Louis CALMON Page 11

You might also like

- PrsenatationassembleurDocument155 pagesPrsenatationassembleurgo88No ratings yet

- 68hc11 v2 PDFDocument17 pages68hc11 v2 PDFmoutchedNo ratings yet

- Programmation Assembleur Des PICDocument12 pagesProgrammation Assembleur Des PICEden BenNo ratings yet

- Utilisation Des Timer Avec Le PICDocument3 pagesUtilisation Des Timer Avec Le PICAnouar BenlaqlibNo ratings yet

- Microprocess EurDocument7 pagesMicroprocess EurChihab YasserNo ratings yet

- Electronique Numerique 1Document121 pagesElectronique Numerique 1guyguychouNo ratings yet

- Rapport TPDocument12 pagesRapport TPoumaimaNo ratings yet

- ANNEXE: Microcontrôleur PIC Microchip Un MicrocontrôleurDocument7 pagesANNEXE: Microcontrôleur PIC Microchip Un MicrocontrôleurlaghmiNo ratings yet

- 4 TP Timer PDFDocument5 pages4 TP Timer PDFkaoutarNo ratings yet

- Rapport TP AssembleurDocument11 pagesRapport TP AssembleurSarah100% (1)

- Cours Filtres PDFDocument58 pagesCours Filtres PDFFarid Afifi100% (1)

- Histoire LinuxDocument3 pagesHistoire LinuxAmira ManaiNo ratings yet

- Chapitre 1 SEDocument20 pagesChapitre 1 SEBadr HamedNo ratings yet

- Chapitre 1 Architecture Pic 16f877Document25 pagesChapitre 1 Architecture Pic 16f877Moujahed GassoumiNo ratings yet

- FMX 12 Notice TechniqueDocument246 pagesFMX 12 Notice TechniqueSidy Elbechir DrameNo ratings yet

- PIC16F84Document22 pagesPIC16F84Rida bellarraneNo ratings yet

- Base Elect ImportantDocument14 pagesBase Elect ImportantRabeb BayoudhiNo ratings yet

- Un Module de Minuterie Dans Sa Forme La Plus Élémentaire Est Un Circuit Logique Numérique Qui Compte Chaque Cycle DDocument46 pagesUn Module de Minuterie Dans Sa Forme La Plus Élémentaire Est Un Circuit Logique Numérique Qui Compte Chaque Cycle DAwatef MessaoudiNo ratings yet

- 2bau TNP TP 9Document18 pages2bau TNP TP 9Houda KeurtiNo ratings yet

- Cours Assembleur 8086 PDFDocument63 pagesCours Assembleur 8086 PDFالورود جنةNo ratings yet

- TD Proc Emb 2016Document3 pagesTD Proc Emb 2016MahdiNjahi100% (1)

- 2005 National Exo1 RC RLC Alarme EDocument3 pages2005 National Exo1 RC RLC Alarme EziedbelguithNo ratings yet

- Cours SoC 2011Document72 pagesCours SoC 2011cointoinNo ratings yet

- Presentation de L Analyse Frequentielle 2008 PDFDocument6 pagesPresentation de L Analyse Frequentielle 2008 PDFMustafa Moussaoui100% (1)

- Modifs GA15 Harley BentonDocument20 pagesModifs GA15 Harley BentonjimmyjoeNo ratings yet

- TP Prise en MainDocument8 pagesTP Prise en MainElyazghi AbdellahNo ratings yet

- Le Microprocesseur 8086 8088Document16 pagesLe Microprocesseur 8086 8088Nassimos YalanosNo ratings yet

- Archi05 Sentieys DSPDocument36 pagesArchi05 Sentieys DSPamidi5555913No ratings yet

- 68 HC 11Document27 pages68 HC 11زهر الدين ضيفNo ratings yet

- PWM Generation Avec 68HC11 PDFDocument2 pagesPWM Generation Avec 68HC11 PDFSofiane MelkiNo ratings yet

- Chapitre 04Document101 pagesChapitre 04Fadi ZidiNo ratings yet

- SP Microcontrôleur PIC16F887 A.OUMNAD 1 LES MICROCONTROLEURS Par La Pratique IDocument9 pagesSP Microcontrôleur PIC16F887 A.OUMNAD 1 LES MICROCONTROLEURS Par La Pratique IOumhineAliNo ratings yet

- Ex 1 TP 3 DSPDocument4 pagesEx 1 TP 3 DSPAmineSlamaNo ratings yet

- TD1Document2 pagesTD1Abdelfatah FerhatNo ratings yet

- Microcontroleur Harvard Pic16f84 - CompressDocument5 pagesMicrocontroleur Harvard Pic16f84 - CompressMeziane BelkacemNo ratings yet

- 2BACSTE - Pic 16F84 Et Pic 16F877 - RACHID BOUTSAIDDocument25 pages2BACSTE - Pic 16F84 Et Pic 16F877 - RACHID BOUTSAIDAFAD100% (1)

- CH1 Suite PDFDocument14 pagesCH1 Suite PDFMontassar SlamaNo ratings yet

- MandeDocument6 pagesMandeAdem AounNo ratings yet

- TP 3Document8 pagesTP 3Adem AounNo ratings yet

- Chap II Architecture Des MicrocontrôleursDocument8 pagesChap II Architecture Des MicrocontrôleursMohamed Aziz Ben RomdhaneNo ratings yet

- Examen Master RE 2019Document1 pageExamen Master RE 2019Omar BekkarNo ratings yet

- TP 5 Realisation Modulation FM À VaricapDocument3 pagesTP 5 Realisation Modulation FM À VaricapYves AbrahamNo ratings yet

- Programmer HP41Document177 pagesProgrammer HP41Dhénin Jean-JacquesNo ratings yet

- A-Préliminaires B - Présentation de CPU 8086 C - Registres de CPU 8086 Icroprocesseur (CPU) 8086Document34 pagesA-Préliminaires B - Présentation de CPU 8086 C - Registres de CPU 8086 Icroprocesseur (CPU) 8086Hiba SaghirNo ratings yet

- Module 1 - 8086Document19 pagesModule 1 - 8086Hiba TouneNo ratings yet

- Cours Microprocesseur MicroControleur M1 GI Chap 3Document15 pagesCours Microprocesseur MicroControleur M1 GI Chap 3Hassan MohamedNo ratings yet

- Microprocesseur 8086Document79 pagesMicroprocesseur 8086Hichem Hamdi100% (3)

- Le Microprocesseur 8086Document22 pagesLe Microprocesseur 8086Merbai YassineNo ratings yet

- TP 555Document7 pagesTP 555ʚïɞ OùŠšàmà ʚïɞNo ratings yet

- Cours 68 HC 11 V 31Document55 pagesCours 68 HC 11 V 31Zineddine El Mehdi MustaphaNo ratings yet

- Assembleur 1Document5 pagesAssembleur 1Asmaâ EL OuakiliNo ratings yet

- Présentation Chapitre 567Document30 pagesPrésentation Chapitre 567faouzighribiNo ratings yet

- Le Pic 16f877Document5 pagesLe Pic 16f877karam karamNo ratings yet

- Microprocesseur CPU: Etude Du Microprocesseur DéfinitionDocument12 pagesMicroprocesseur CPU: Etude Du Microprocesseur DéfinitionIbrahim FofanaNo ratings yet

- Best PrsenatationassembleurDocument155 pagesBest PrsenatationassembleurSamir Said100% (1)

- 2015 08 21 TD32 Le Microprocesseur 0708S1Document4 pages2015 08 21 TD32 Le Microprocesseur 0708S1Mēđ GouigaNo ratings yet

- Les Instructions Du 8051: BooleenDocument5 pagesLes Instructions Du 8051: BooleensetupNo ratings yet

- Cours No 04 Etude de L'architecture Du Microprocesseur 8086Document6 pagesCours No 04 Etude de L'architecture Du Microprocesseur 8086Wassim AmamicheNo ratings yet

- Etude de L'architecture Du Microprocesseur 8086.: Chapitre N 04Document6 pagesEtude de L'architecture Du Microprocesseur 8086.: Chapitre N 04Zakaria ToualbiaNo ratings yet

- Cours Assembleur IIDocument25 pagesCours Assembleur IImhaouch AyoubNo ratings yet

- Théorie Et Traitement Du Signal - Tome 1 - Représentation Des Signaux Et Des Systèmes - Cours Et Exercices Corrigés-Dunod (2002)Document271 pagesThéorie Et Traitement Du Signal - Tome 1 - Représentation Des Signaux Et Des Systèmes - Cours Et Exercices Corrigés-Dunod (2002)moutchedNo ratings yet

- 402B Base de donnees-II PDFDocument40 pages402B Base de donnees-II PDFamira_menifNo ratings yet

- Montages de Physique CapesDocument270 pagesMontages de Physique CapesmoutchedNo ratings yet

- Materéalisation GRAFCET EleveDocument46 pagesMateréalisation GRAFCET Elevemoutched100% (1)

- Introduction A C++Document19 pagesIntroduction A C++niko100% (5)

- Chap3 DipoleActifDocument12 pagesChap3 DipoleActifmoutchedNo ratings yet

- La Loi Des Noeuds TD CompletDocument8 pagesLa Loi Des Noeuds TD Completmoutched0% (1)

- Cours & Exercices D'electricite - Cesi - 20042007Document114 pagesCours & Exercices D'electricite - Cesi - 20042007Oumaima Slim100% (4)

- PIC16F877Document77 pagesPIC16F877Mandar Mehdi100% (1)

- Poly TD Elec1 2012 2013 V2Document43 pagesPoly TD Elec1 2012 2013 V2moutchedNo ratings yet

- Merise Exercices MCD EnoncesDocument37 pagesMerise Exercices MCD Enoncesyefloussen7175% (20)

- Electronique de PuissanceDocument33 pagesElectronique de PuissanceBleck Cool100% (2)

- CA Ateliers ArtDocument60 pagesCA Ateliers Artmoutched100% (1)

- GRAFCET Et AutomatismeDocument41 pagesGRAFCET Et AutomatismeEden Ben80% (5)

- Excel5 1Document86 pagesExcel5 1moutchedNo ratings yet

- Java ToutDocument392 pagesJava Toutapi-3743772100% (2)

- Bases de DonnéesDocument1 pageBases de DonnéesmoutchedNo ratings yet

- Exercices ExcelDocument10 pagesExercices Excelmoutched50% (2)

- Bases de DonnéesDocument1 pageBases de DonnéesmoutchedNo ratings yet

- TD1 MCDDocument2 pagesTD1 MCDmoutchedNo ratings yet

- Controle Pascal1Document1 pageControle Pascal1moutchedNo ratings yet

- MINUTERIEDocument2 pagesMINUTERIEmoutchedNo ratings yet

- TPN I. But.: °1: Réalisation de Fonctions LogiquesDocument2 pagesTPN I. But.: °1: Réalisation de Fonctions LogiquesmoutchedNo ratings yet

- Cours de Langage CDocument33 pagesCours de Langage Cmoutched50% (2)

- Chap7 PipelineDocument45 pagesChap7 PipelineSirNo ratings yet

- Résumé DSPDocument6 pagesRésumé DSPOmar ZemraniNo ratings yet

- Chapitre 6 - Structure Interne Du PIC 16F887Document24 pagesChapitre 6 - Structure Interne Du PIC 16F887OumhineAliNo ratings yet

- Cours 2 - Archtecure Du PIC 16F84Document31 pagesCours 2 - Archtecure Du PIC 16F84KhadidjaNo ratings yet

- Chapitre 3Document49 pagesChapitre 3Hamza BenineNo ratings yet

- Micro Control Eur 1Document73 pagesMicro Control Eur 1Marcelin SoukroumdeNo ratings yet

- Chapitre 2Document7 pagesChapitre 2Ulrich JordanNo ratings yet

- Wa0042.Document5 pagesWa0042.Soufiane AbdelouahabNo ratings yet

- Apostila de Montagem e Manutenção de ComputadoresDocument1,156 pagesApostila de Montagem e Manutenção de ComputadoresneubersaNo ratings yet

- Serie ExercicesDocument5 pagesSerie ExercicesvernightNo ratings yet

- SoumaireDocument3 pagesSoumairekolechi dzNo ratings yet

- Up Mu0Document38 pagesUp Mu0MBADJOUN DanielNo ratings yet

- Le Microcontroleur PIC16F876Document13 pagesLe Microcontroleur PIC16F876hmema13No ratings yet

- Examen Assembleur 2007Document3 pagesExamen Assembleur 2007Yassine AmrNo ratings yet

- SYS Up Serie3 12-13 S5 PDFDocument3 pagesSYS Up Serie3 12-13 S5 PDFlahjaouziNo ratings yet

- TP Debug InfoDocument47 pagesTP Debug InfoBagol SayaNo ratings yet

- Chapitre 2 Lat 54Document3 pagesChapitre 2 Lat 54Smati DjamelNo ratings yet

- Isetkl - Courarchi - TI MicroprocesseurDocument72 pagesIsetkl - Courarchi - TI Microprocesseurahmed choucheneNo ratings yet

- DSP IIT 2télécom ch3Document28 pagesDSP IIT 2télécom ch3Rahma FakhfakhNo ratings yet

- Examen Final Du Module Informatique Industrielle: Question - 1 (Document7 pagesExamen Final Du Module Informatique Industrielle: Question - 1 (oassarikhiNo ratings yet

- Conception À Microprocesseurs - ArdjaniDocument146 pagesConception À Microprocesseurs - Ardjaniamine menadNo ratings yet

- Programmation Des Microcontrôleurs en Langage C: Ports E/S Et Temporisateur TMR0 Du PIC16F87x. NDocument6 pagesProgrammation Des Microcontrôleurs en Langage C: Ports E/S Et Temporisateur TMR0 Du PIC16F87x. NAyman LamzouriNo ratings yet

- Interruptions Et Timers Du 8051Document8 pagesInterruptions Et Timers Du 8051Maha BadriNo ratings yet

- Tous Au Niveau3Document203 pagesTous Au Niveau3tonye joel100% (1)

- Série D'exercicesDocument4 pagesSérie D'exercicesnesrine nina100% (1)

- Cours DSP ISEN Partie2Document20 pagesCours DSP ISEN Partie2Smart ClasseNo ratings yet

- Chapitre 1 Initiation À L'assembleur 68000: Table Des MatièresDocument36 pagesChapitre 1 Initiation À L'assembleur 68000: Table Des MatièresBadr Eddine EL HAGAOUINo ratings yet

- Correction TD3Document3 pagesCorrection TD3Mouna Ben MohamedNo ratings yet

- Performances Des ProcesseursDocument29 pagesPerformances Des ProcesseursSalas Salvador DiosdadoNo ratings yet

- Cours 7 CpuDocument90 pagesCours 7 CpuSandra BouNo ratings yet