Professional Documents

Culture Documents

Ap7102 Adsd

Uploaded by

shankar0 ratings0% found this document useful (0 votes)

782 views5 pagesadd

Original Title

AP7102-ADSD

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentadd

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

782 views5 pagesAp7102 Adsd

Uploaded by

shankaradd

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 5

KONGUNADU COLLEGE OF ENGINEERING AND TECHNOLOGY, THOTTIAM.

AP 7102 ADVANCED DIGITAL LOGIC SYSTEM DESIGN L T P C

3 0 0 3

OBJECTIVES:

To analyze synchronous and asynchronous sequential circuits

To realize and design hazard free circuits

To familiarize the practical issues of sequential circuit design

To gain knowledge about different fault diagnosis and testing methods

To estimate the performance of digital systems

To know about timing analysis of memory and PLD

UNIT I SEQUENTIAL CIRCUIT DESIGN 9

Analysis of Clocked Synchronous Sequential Networks (CSSN) - Modeling of CSSN State Assignment

and Reduction Design of CSSN Design of Iterative Circuits ASM Chart ASM Realization, Design of

Arithmetic circuits for Fast adder- Array Multiplier.

UNIT II ASYNCHRONOUS SEQUENTIAL CIRCUIT DESIGN 9

Analysis of Asynchronous Sequential Circuit (ASC) Flow Table Reduction Races in ASC State

Assignment Problem and the Transition Table Design of ASC Static and Dynamic Hazards Essential

Hazards Design of Hazard free circuits - Data Synchronizers Designing Vending Machine Controller

Mixed Operating Mode Asynchronous Circuits. Practical issues such as clock skew, synchronous and

asynchronous inputs and switch bouncing.

UNIT III FAULT DIAGNOSIS & TESTING 9

Fault diagnosis: Fault Table Method Path Sensitization Method Boolean Difference Method Kohavi

Algorithm Tolerance Techniques The Compact Algorithm. Design for testability: Test Generation

Masking Cycle DFT Schemes. Circuit testing fault model, specific and random faults, testing of sequential

circuits, Built in Self Test, Built in Logic Block observer (BILBO), signature analysis.

UNIT IV PERFORMANCE ESTIMATION 9

Estimating digital system reliability, transmission lines, reflections and terminations, system integrity,

network issues for digital systems, formal verifications of digital system: model-checking, binary decision,

theorem proving, circuit equivalence.

UNIT V TIMING ANALYSIS 9

ROM timings, Static RAM timing, Synchronous Static RAM and its timing, Dynamic RAM timing,

Complex Programmable Logic Devices, Logic Analyzer Basic Architecture, Internal structure, Data display,

Setup and Control, Clocking and Sampling.

TOTAL: 45 PERIODS

REFERENCES:

1. Charles H.Roth Jr Fundamentals of Logic Design, Thomson Learning 2004.

2. Nripendra N Biswas Logic Design Theory Prentice Hall of India, 2001.

3. Parag K.Lala An introduction to Logic Circuit Testing Morgan and claypool publishers, 2009.

4. Stephen D Brown, Fundamentals of digital logic, TMH publication, 2007.

5. Balabanian, Digital Logic Design Principles, Wiley publication, 2007.

6. Stalling, Computer Organization & Architecture, Pearson Education India, 2008.

7. J.F.Wakerly, Digital Design, Pearson Education India, 2012.

8. J.F.Wakerly, Digital Design principles and practices, PHI publications, 2005.

9. Charles J. Sipil, Microcomputer Handbook McCrindle- Collins Publications 1977.

UNIT I SEQUENTIAL CIRCUIT DESIGN 9

Analysis of Clocked Synchronous Sequential Networks (CSSN) - Modeling of CSSN- State Assignment

and Reduction- Design of CSSN- Design of iterative circuits-ASM chart- ASM Realization, Design of

arithmetic Circuits for Fast adder-Array Multiplier.

Session

No.

Topics to be covered Time Ref

Teaching

Method

1.

Analysis of Clocked Synchronous Sequential Networks-

Introduction.

50m 1 BB

2.

Design of a Sequential parity checker, Analysis of Moore

and Mealy sequential circuit by signal tracing and timing

charts.

50m 1 BB

3.

Method of constructing state table and state graphs for

Moore and Mealy machines.

50m 1 BB

4.

General Models for a clocked Mealy and Moore sequential

circuits.

50m 1 BB

5.

Guidelines for state assignments and reduction of state

table using state assignment.

50m 1 BB

6.

Different types of State Assignment- Shared row, Multiple

row and One hot state assignment.

50m 1 BB

7.

Determination of state equivalence and circuit equivalence

using an implication table.

50m 1 BB

8. Design of iterative circuits, Design of a n-bit comparator. 50m 1 BB

9.

Algorithmic State Machine (ASM) Charts- Derivation and

realization of ASM Chart.

50m 1 BB

10.

Design of Arithmetic circuits for Fast adder- Carry look

ahead adder.

50m 4 BB

11. Array Multiplier Structure of an 4 X 4 Multiplier circuit. 50m 4 BB

UNIT II ASYNCHRONOUS SEQUENTIAL CIRCUIT DESIGN 9

Analysis of Asynchronous Sequential Circuit (ASC) - Flow Table Reduction-Races in ASC- State

Assignment Problem and the Transition Table- Design of ASC-Static and Dynamic Hazards- Essential

Hazards- Design of Hazard free circuits- Data Synchronizers- Designing Vending Machine Controller-

Mixed Operating Mode Asynchronous Circuits. Practical issues such as clock skew, synchronous and

asynchronous inputs and switch bouncing.

UNIT III FAULT DIAGNOSIS & TESTING 9

Fault diagnosis: Fault Table Method- Path Sensitization Method- Boolean Difference Method- Kohavi

Algorithm -Tolerance Techniques- The Compact Algorithm. Design for testability: Test Generation-

Masking Cycle - DFT schemes. Circuit testing fault model, specific and random faults, testing of sequential

circuits, Built in self test, Built in Logic Block observer (BILBO), Signature analysis.

Session

No.

Topics to be covered Time Ref

Teaching

Method

12. Analysis of Asynchronous Sequential Circuit - Design of

Fundamental mode sequential circuit - Primitive state

table, state table reduction and state assignment.

50m 4 BB

13. Design of Pulse mode sequential circuit- Primitive state

table, state table reduction and state assignment.

50m 4 BB

14. Problems in Asynchronous Sequential Circuits Cycles,

Critical race and Non- Critical race.

50m 2,5 BB

15. Hazards- Static, Dynamic and Essential Hazards. 50m 2,5 BB

16. Design of Hazard free switching circuits- Static Hazard

and Essential Hazard elimination.

50m 2,5 BB

17. Working principle of Data synchronizer. 50m 7 BB

18. Design of Vending machine controller- Description/

Specification, FSM design steps, State diagram and state

table.

50m 4 BB

19. Design of mixed operating mode asynchronous circuit. 50m 4 BB

20. Practical issues: Clock skew, synchronous and

asynchronous inputs and switch bouncing.

50m 7 BB

UNIT IV PERFORMANCE ESTIMATION 9

Estimating digital system reliability, transmission lines, reflections and terminations, system integrity,

network issues for digital systems, formal verifications of digital system: model- checking, binary decision

diagram, theorem proving, circuit equivalence.

Session

No.

Topics to be covered Time Ref

Teaching

Method

21. Fault Models- Stuck-at fault, Bridging fault, stuck-open fault

and Temporary faults.

50m 3 BB

22. Fault Diagnosis of Digital systems- Test generation for

combinational logic circuits- Fault Table Method and Path

Sensitization method.

50m 2 BB

23. Boolean Difference method. 50m 3 BB

24. Kohavi and Compact Algorithm. 50m 2 BB

25.

Tolerance techniques- Static redundancy, Dynamic redundancy

and Hybrid redundancy.

50m 3 BB

26. Self- purging redundancy, Sift-out modular redundancy 50m 3 BB

27. Fault in PLAs, Test generation and Masking cycle. 50m 2 BB

28. Design for Testability (DFT), DFT schemes, Circuit testing

fault model: Specific and random faults.

50m 4 BB

29. Testing of sequential circuits and Built In Self Test (BIST). 50m 4 BB

30. Built In Logic Block Observer (BILBO) and Signature

analysis.

50m 4 BB

Session

No.

Topics to be covered Time Ref

Teaching

Method

31. Estimating Digital System Reliability- Failure rates,

Reliability and MTBF, System Reliability.

50m 9 BB

32. Transmission lines with infinite and finite length

terminated with characteristic impedance, Logic

signal terminations.

50m 9 BB

33. Network issues for digital systems: Noise, Time

margin, Parasitic inductance and capacitances.

50m 9 BB

34. Digital System Integrity to minimize Noise Margin,

Transmission Line effects, Signal Path Return

currents and power distribution.

50m 9 BB

UNIT V TIMING ANALYSIS 9

ROM timings, Static RAM timing, Synchronous Static RAM and its timing. Dynamic RAM timing,

Complex Programmable Logic devices, Logic Analyzer Basic Architecture, Internal Structure, Data display,

Setup and Control, Clocking and Sampling.

35. Design and Verification of Digital Systems: Design

flow and RTL Verification.

50m 9 BB

36. Binary Decision Diagrams with an example. 50m 9 BB

37. Model for Design Verification, Functional

Validation.

50m 9 BB

38. Formal Verification and Challenges in Symbolic

Simulation.

50m 9 BB

Session

No.

Topics to be covered Time Ref

Teaching

Method

39. Read Only Memory (ROM) Timing diagram. 50m 7 BB

40.

Static RAM Internal Structure and Timing

parameters for Read and Write operation of static

RAM.

50m 7 BB

41.

Synchronous SRAM- Internal Structure and its read

and Write operation.

50m

7 BB

42.

Dynamic RAM Structure, Write and burst read cycle

Timing.

50m

7 BB

43,44

Complex Programmable Logic Devices general

architecture, Function block architecture, Input/output

block architecture and Switch Matrix.

100m

7

BB

45.

Logic Analyzer- Basic Architecture and Internal

Structure.

50m

6 BB

46.

Logic Analyzer- Clocking, Triggering, Acquisition and

Capturing Glitches.

50m

6 BB

47.

Logic Analyzer- Data display, Setup and Control

50m

6

BB

You might also like

- Top-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsFrom EverandTop-Down Digital VLSI Design: From Architectures to Gate-Level Circuits and FPGAsNo ratings yet

- VL7301 Testing of VLSI CircuitsDocument8 pagesVL7301 Testing of VLSI Circuitsmanojece80100% (1)

- DSDV MODULE 3 Implementation FabricsDocument17 pagesDSDV MODULE 3 Implementation Fabricssalman shariffNo ratings yet

- Analog & Digital VLSI Design Practice QuestionsDocument24 pagesAnalog & Digital VLSI Design Practice QuestionsAbhinav MishraNo ratings yet

- UNIT 1 Question BankDocument6 pagesUNIT 1 Question BankUjjwalNo ratings yet

- Computer Organisation and ArchitectureDocument6 pagesComputer Organisation and ArchitectureChalumuri JyothiswaroopNo ratings yet

- Electronic Devices Model Question PapersDocument2 pagesElectronic Devices Model Question Papersk_kunarajNo ratings yet

- ECE3073 Computer Systems Practice Questions Bus InterfacingDocument2 pagesECE3073 Computer Systems Practice Questions Bus InterfacingkewancamNo ratings yet

- ECE3073 P4 Bus Interfacing Answers PDFDocument3 pagesECE3073 P4 Bus Interfacing Answers PDFkewancamNo ratings yet

- Valliammai Engineering College: Department of Electronics and Communication EngineeringDocument9 pagesValliammai Engineering College: Department of Electronics and Communication EngineeringCecilia ChinnaNo ratings yet

- Record Electrical Quantities Over TimeDocument9 pagesRecord Electrical Quantities Over TimeManoj PatchiyanNo ratings yet

- Verilog CodeDocument60 pagesVerilog CodePriyanka JainNo ratings yet

- Digital Circuits For GATE ExamDocument15 pagesDigital Circuits For GATE ExamSAMIT KARMAKAR100% (1)

- Nirma University Institute of Technology: B. Tech. in Electronics and Communication Engineering Semester - VDocument15 pagesNirma University Institute of Technology: B. Tech. in Electronics and Communication Engineering Semester - VPragya jhalaNo ratings yet

- Verilog HDL Lecture Notes: Design Digital Systems Using Xilinx ToolsDocument124 pagesVerilog HDL Lecture Notes: Design Digital Systems Using Xilinx Toolsrachitha sNo ratings yet

- Software Design For Low PowerDocument20 pagesSoftware Design For Low PowerGokul B S MandyaNo ratings yet

- Question Bank Fundamentals of CMOS VLSI-10EC56 15-16Document10 pagesQuestion Bank Fundamentals of CMOS VLSI-10EC56 15-16Pranav KpNo ratings yet

- Simulation LaboratoryDocument102 pagesSimulation LaboratoryPUBG ASSASIN தமிழ் ASASSINNo ratings yet

- HDL Model QPDocument5 pagesHDL Model QPSubramanyaAIyerNo ratings yet

- JNTUH - B Tech - 2019 - 3 2 - May - R18 - EEE - 136FT PCCN Principles of Computer Communications andDocument2 pagesJNTUH - B Tech - 2019 - 3 2 - May - R18 - EEE - 136FT PCCN Principles of Computer Communications andNaga SekharNo ratings yet

- Me Maths ModelDocument2 pagesMe Maths ModelJagan RajendiranNo ratings yet

- EC 1401 - VLSI Design QuestionsDocument18 pagesEC 1401 - VLSI Design QuestionsChaitanya PrabhuNo ratings yet

- EC 6302 2-Marks and 16 Marks QuestionsDocument12 pagesEC 6302 2-Marks and 16 Marks QuestionsskaruppaiaheceNo ratings yet

- VirtuosoDocument6 pagesVirtuosoBhaskar KNo ratings yet

- A.V.C College of Engineering, Mannampandal M.E - Applied ElectronicsDocument3 pagesA.V.C College of Engineering, Mannampandal M.E - Applied ElectronicsAnonymous IkB7TZjNo ratings yet

- Digital System Objective QuestionsDocument17 pagesDigital System Objective QuestionsRanjeet pratap singh bhadoriyaNo ratings yet

- MicroProcessor MicroController LAB MANUAL MPMC Lab ManualDocument71 pagesMicroProcessor MicroController LAB MANUAL MPMC Lab ManualDossDossNo ratings yet

- Model Question Paper: SP 206 Wavelet Transforms: Theory and ApplicationsDocument2 pagesModel Question Paper: SP 206 Wavelet Transforms: Theory and Applicationssafu_117100% (1)

- p13 - Behavioral Modeling of LDO PDFDocument10 pagesp13 - Behavioral Modeling of LDO PDFTitan FredNo ratings yet

- Vtu Old Question Papers - Best PDFDocument1 pageVtu Old Question Papers - Best PDFpoojabadigerNo ratings yet

- CMRIT Wireless Cellular and LTE 4G CourseDocument4 pagesCMRIT Wireless Cellular and LTE 4G CourseSanjana AkkoleNo ratings yet

- Ec - 501 - Microprocessor and Its ApplicationDocument41 pagesEc - 501 - Microprocessor and Its ApplicationDr Nikita ShivhareNo ratings yet

- Understanding About CMOS Fabrication TechnologyDocument4 pagesUnderstanding About CMOS Fabrication TechnologyJayesh RaghuwanshiNo ratings yet

- Cyclic CodesDocument13 pagesCyclic CodesTushara NairNo ratings yet

- Embedded Syatem Question Paper.Document1 pageEmbedded Syatem Question Paper.Saurabh SinghNo ratings yet

- Dica Question BankDocument4 pagesDica Question BankOmprakash KuswahaNo ratings yet

- 100 TOP COMPUTER NETWORKS Multiple Choice Questions and Answers COMPUTER NETWORKS Questions and Answers PDFDocument21 pages100 TOP COMPUTER NETWORKS Multiple Choice Questions and Answers COMPUTER NETWORKS Questions and Answers PDFvaraprasad_ganjiNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)Val GinNo ratings yet

- DDDC87ECAA084E5DA4D2D77F7DC80391Document5 pagesDDDC87ECAA084E5DA4D2D77F7DC80391Sameer NandagaveNo ratings yet

- Modified Dual-Coupled Linear Congruential Generator Based Pseudorandom Bit GeneratorDocument11 pagesModified Dual-Coupled Linear Congruential Generator Based Pseudorandom Bit GeneratorGanesamoorthy BNo ratings yet

- UNIT 4 Analog Circuits MCQs and SolutionsDocument98 pagesUNIT 4 Analog Circuits MCQs and SolutionsvikramvivNo ratings yet

- EC6703 Question Paper Code X20461 BTech Degree Exams Nov/Dec 2020Document2 pagesEC6703 Question Paper Code X20461 BTech Degree Exams Nov/Dec 2020HOD ECE KNCETNo ratings yet

- EE6403 DSP Hand Written NotesDocument282 pagesEE6403 DSP Hand Written Notessyed ibrahim100% (1)

- B e BmeDocument42 pagesB e BmeRAMESHKUMAR.S MCE-LECT/MECHNo ratings yet

- Logic Circuits Midterm ReviewerDocument38 pagesLogic Circuits Midterm ReviewerHector Ledesma IIINo ratings yet

- Memories and PLDsDocument47 pagesMemories and PLDsHimanshu KhanduriNo ratings yet

- DECO Lab FileDocument101 pagesDECO Lab Fileshivam100% (1)

- Instruction PipelineDocument27 pagesInstruction PipelineEswin AngelNo ratings yet

- Digital System Design Using VHDL PaperDocument2 pagesDigital System Design Using VHDL PaperlambajituNo ratings yet

- II BTECH - I SEM - ECE - EDC - THEORY & QUIZ QUESTIONS - MID 2 - Students PDFDocument19 pagesII BTECH - I SEM - ECE - EDC - THEORY & QUIZ QUESTIONS - MID 2 - Students PDFK SrinuNo ratings yet

- VLSI& Embedded - MCQ's - 21 - 30Document5 pagesVLSI& Embedded - MCQ's - 21 - 30rohi89No ratings yet

- Research Notes On VlsiDocument70 pagesResearch Notes On VlsiMohit GirdharNo ratings yet

- Microprocessor and Microcontroller ProgrammingDocument39 pagesMicroprocessor and Microcontroller ProgrammingGunasekaranNo ratings yet

- A Seminar Report On Vlsi FloorplanningDocument17 pagesA Seminar Report On Vlsi FloorplanningPARAG100% (1)

- Rr311901 Digital Systems DesignDocument8 pagesRr311901 Digital Systems DesignSrinivasa Rao GNo ratings yet

- Dspa 17ec751 M5Document34 pagesDspa 17ec751 M5digital loveNo ratings yet

- Optimum Array Processing: Part IV of Detection, Estimation, and Modulation TheoryFrom EverandOptimum Array Processing: Part IV of Detection, Estimation, and Modulation TheoryNo ratings yet

- Ex06 - Answer Key Adaic Te-2Document8 pagesEx06 - Answer Key Adaic Te-2shankarNo ratings yet

- Design of Efficient Class-E Power Amplifiers For Short-Distance CommunicationsDocument11 pagesDesign of Efficient Class-E Power Amplifiers For Short-Distance CommunicationsshankarNo ratings yet

- Ex05 - Question Paper Adaic - ModelDocument2 pagesEx05 - Question Paper Adaic - ModelshankarNo ratings yet

- KONGUNADU COLLEGE OF ENGINEERING AND TECHNOLOGY TERMINAL EXAMINATION-I ANALYSIS AND DESIGN OF ANALOG INTEGRATED CIRCUITSDocument2 pagesKONGUNADU COLLEGE OF ENGINEERING AND TECHNOLOGY TERMINAL EXAMINATION-I ANALYSIS AND DESIGN OF ANALOG INTEGRATED CIRCUITSshankarNo ratings yet

- Introduction To MATLABDocument36 pagesIntroduction To MATLABViju JigajinniNo ratings yet

- MATLAB BasicsDocument24 pagesMATLAB BasicsshankarNo ratings yet

- Kongunadu College of Engineering and TechnologyDocument2 pagesKongunadu College of Engineering and TechnologyshankarNo ratings yet

- M.E. Applied Electronics - R2017Document47 pagesM.E. Applied Electronics - R2017Mr.R.Ragumadhavan ecestaffNo ratings yet

- Adaic TT 2016Document2 pagesAdaic TT 2016shankarNo ratings yet

- KONGUNADU COLLEGE M.E ECE I/I TIME TABLE 2018-19Document1 pageKONGUNADU COLLEGE M.E ECE I/I TIME TABLE 2018-19shankarNo ratings yet

- Zero Diagonal Property Symmetry Property Unitary Property Phase Shift PropertyDocument5 pagesZero Diagonal Property Symmetry Property Unitary Property Phase Shift PropertyshankarNo ratings yet

- HTTPDocument2 pagesHTTPshankarNo ratings yet

- Kongunadu College of Engineering and Technology, ThourpattiDocument1 pageKongunadu College of Engineering and Technology, ThourpattishankarNo ratings yet

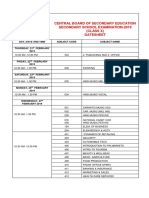

- Central Board of Secondary Education Secondary School Examination-2019 (Class X) DatesheetDocument4 pagesCentral Board of Secondary Education Secondary School Examination-2019 (Class X) DatesheetPriyanka SharmaNo ratings yet

- CH 3 - FeedbackDocument54 pagesCH 3 - FeedbackshankarNo ratings yet

- NBA Modified RF&MW LPDocument4 pagesNBA Modified RF&MW LPshankarNo ratings yet

- RF&MW M 1Document2 pagesRF&MW M 1shankarNo ratings yet

- Digital Signal Processing Introduction PartDocument13 pagesDigital Signal Processing Introduction Partshankar100% (1)

- Ec 6502 Principles of Digital Signal Processing - Question Bank - 2018Document17 pagesEc 6502 Principles of Digital Signal Processing - Question Bank - 2018shankarNo ratings yet

- Ada Syllabus 2013Document1 pageAda Syllabus 2013shankarNo ratings yet

- WN Unit1 and Unit5Document1 pageWN Unit1 and Unit5shankar0% (1)

- Ada Syllabus 2013Document1 pageAda Syllabus 2013shankarNo ratings yet

- HTTPDocument2 pagesHTTPshankarNo ratings yet

- Unit V: Time Varying Fields and Maxwell'S EquationsDocument12 pagesUnit V: Time Varying Fields and Maxwell'S EquationsshankarNo ratings yet

- Ec6802 Wireless NetworksDocument1 pageEc6802 Wireless NetworksBritto Ebrington AjayNo ratings yet

- MultiplierDocument16 pagesMultipliershankarNo ratings yet

- Unit 1 Ada 2014Document22 pagesUnit 1 Ada 2014shankarNo ratings yet

- Unit 1 Adsd KncetDocument46 pagesUnit 1 Adsd KncetshankarNo ratings yet

- AP9212Document7 pagesAP9212shankarNo ratings yet

- KSG-4.6K-DM / KSG-4.9K-DM / KSG-5K-DM / KSG-5.2K-DM: String Grid-Tied PV Inverter NG Grid-Tied PV InverterDocument1 pageKSG-4.6K-DM / KSG-4.9K-DM / KSG-5K-DM / KSG-5.2K-DM: String Grid-Tied PV Inverter NG Grid-Tied PV InvertergodinsideNo ratings yet

- VMB Enterprise Install Guide VMB10.5Document34 pagesVMB Enterprise Install Guide VMB10.5letranganhNo ratings yet

- Enterprise Level Controls General Controls For Information Technology Application Controls For Transaction ProcessingDocument54 pagesEnterprise Level Controls General Controls For Information Technology Application Controls For Transaction ProcessingMonica SanchezNo ratings yet

- Wireless Earbuds, Yobola Bluetooth Earbuds, IPX5Document2 pagesWireless Earbuds, Yobola Bluetooth Earbuds, IPX5Cheikh FayeNo ratings yet

- RGB 2 DviDocument4 pagesRGB 2 DviabrahamveeNo ratings yet

- Chapter: 3.2 Microsoft Windows Topic: 3.2.1A Introduction To Microsoft WindowsDocument20 pagesChapter: 3.2 Microsoft Windows Topic: 3.2.1A Introduction To Microsoft WindowsETL LABSNo ratings yet

- 1.1.1.4 Lab - Installing The CyberOps Workstation Virtual MachineDocument5 pages1.1.1.4 Lab - Installing The CyberOps Workstation Virtual Machinec583706No ratings yet

- Binary Code and Classification BookDocument20 pagesBinary Code and Classification BookRajNo ratings yet

- Re-Loading or Erasing Firmware for an EPB or Thin CameraDocument3 pagesRe-Loading or Erasing Firmware for an EPB or Thin CameraccarneroNo ratings yet

- Digital Wireless Telephone: Level 1 and 2 Service ManualDocument54 pagesDigital Wireless Telephone: Level 1 and 2 Service ManualCristinel StemateNo ratings yet

- Csound ExercisesDocument73 pagesCsound ExercisesmarceemarceeNo ratings yet

- Distributed Systems Concepts ExplainedDocument49 pagesDistributed Systems Concepts ExplainedDhrumil DancerNo ratings yet

- Log BookDocument8 pagesLog BookKISHAAN RAO A/L SUBRAMANIAM STUDENTNo ratings yet

- 2.5G CDR JC1225C - 複製Document3 pages2.5G CDR JC1225C - 複製Guan Ting LiuNo ratings yet

- Wide Screen TV Offers 100Hz Digital ScanDocument2 pagesWide Screen TV Offers 100Hz Digital ScanCommy jpnNo ratings yet

- Latest Pricelist PDFDocument4 pagesLatest Pricelist PDFSha Edd'sNo ratings yet

- MCTR-TRX MO MappingDocument29 pagesMCTR-TRX MO Mappingjuan carlos LP100% (1)

- Function Modules in SAP ABAPDocument11 pagesFunction Modules in SAP ABAPGobara DhanNo ratings yet

- Project Report Regulated Power SupplyDocument36 pagesProject Report Regulated Power SupplyPeerzada Wahid73% (11)

- Process Yield Calculator: Throughput Yield % Long-Term Capability Table Short-Term Capability Table 1-Sided 2-SidedDocument1 pageProcess Yield Calculator: Throughput Yield % Long-Term Capability Table Short-Term Capability Table 1-Sided 2-SidedMarcela TemoteoNo ratings yet

- Installation ManualDocument51 pagesInstallation Manualoscarzocon5105No ratings yet

- Santak Array 3A3 PT 600kwDocument8 pagesSantak Array 3A3 PT 600kwWaqar AghaNo ratings yet

- Experiment No. 5 BCD To 7-Segment Decoder/Driver: I.ObjectivesDocument9 pagesExperiment No. 5 BCD To 7-Segment Decoder/Driver: I.ObjectivesJun TobiasNo ratings yet

- Platform Technologies ReviewerDocument9 pagesPlatform Technologies ReviewerRaissa GonzagaNo ratings yet

- Configuring Split Tunnel Client VPN - Cisco MerakiDocument6 pagesConfiguring Split Tunnel Client VPN - Cisco Merakikatherine painiiNo ratings yet

- Ir5075 Series SMDocument650 pagesIr5075 Series SMtihamer_v91% (11)

- E 10108Document314 pagesE 10108Sairam BalaNo ratings yet

- 1e - Martin - Caitlin - Experience With Out of Step Relaying (... )Document13 pages1e - Martin - Caitlin - Experience With Out of Step Relaying (... )sriramv93No ratings yet

- OEM NetApp Quick Reference GuideDocument4 pagesOEM NetApp Quick Reference GuidekarthickNo ratings yet

- Example Network DesignDocument41 pagesExample Network DesignmichaelnancarrowNo ratings yet