Professional Documents

Culture Documents

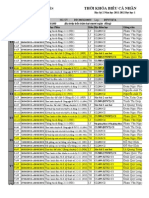

GTVDK Atecko

Uploaded by

Dương TiếnOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

GTVDK Atecko

Uploaded by

Dương TiếnCopyright:

Available Formats

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

BI 1: NHP MN VI IU KHIN PIC

I. PHN L THUYT

1. Gii thiu v vi iu khin PIC

1.1 Gii thiu v vi iu khin

B vi iu khin vit tt l Micro-controller l mch tch hp trn mt chip c th

lp trnh c, dng iu khin hot ng ca h thng .Theo cc tp lnh ca ngi

lp trnh, b vi iu khin tin hnh c, lu tr thng tin, x l thng tin, o thi gian v

tin hnh ng m mt c cu no .

Trong cc thit b in v in t, cc b vi iu khin iu khin hot ng ca ti

vi, my git, u c lase, l vi ba, in thoi Trong h thng sn xut t ng, b vi

iu khin s dng trong robot, cc h thng o lng gim st .Cc h thng cng thng

minh th vai tr ca vi iu khin ngy cng quan trng. Hin nay trn th trng c rt

nhiu h vi iu khin nh: 6811 ca Motorola, 8051 ca Intel, Z8 ca Zilog, PIC ca

Microchip Technology .

1.2 Gii thiu v vi iu khin PIC

PIC bt ngun t ch vit tt ca Programmable Intelligent Computer ( My

tnh kh trnh thng minh) l sn phm ca hng General Instrument t cho dng sn

phm u tin ca h l PIC 1650. Lc ny Pic dng giao tip vi cc thit b ngoi vi

cho my ch 16 bit CP1600, v vy ngi ta gi PIC vi tn l Peripheral Interface

Controller ( b iu khin giao tip ngoi vi) .

Nm 1985 General Instrument bn b phn vi in t ca h, v ch s hu mi

(Microchip Technology) hu b hu ht cc d n lc qu li thi. Tuy nhin PIC

c b sung EEPROM to thnh mt b iu khin vo ra kh trnh. Ngy nay c rt

nhiu dng PIC c sn xut vi hng lot cc modul ngoi vi c tch hp sn ( nh

:USART, PWM, ADC) vi b nh chng trnh t 512 word n 32k word.

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

PIC s dng tp lnh RISC, vi dng PIC low-end ( di m lnh 12 Bit v d

PIC12Cxxx) v mid-range ( di m lnh 14 bit , v d PIC16Fxxx), tp lnh bao gm

khong 35 lnh, v 70 lnh i vi dng PIC high-end( c di m lnh 16bit

PIC18Fxxxx). Tp lnh bao gm cc lnh tnh ton trn cc thanh ghi, v cc hng s,

hoc cc v tr nh, cng nh c cc lnh iu kin, nhy/ gi hm, v cc lnh quay tr

v, n cng c cc chc nng phn cng khc nh ngt hoc sleep( ch hot ng tit

kim in ). Microchip cung cp mi trng lp trnh MPLAB0, n bao gm phn mm

m phng v trnh dch ASM

Hin nay c kh nhiu dng PIC v c rt nhiu khc bit v phn cng, nhng

chng ta c th im qua mt vi nt nh sau :

8/16/24/32 bit CPU, xy dng theo kin trc Harvard

Flash v Rom c th tu chn 256 byte n 256 kbybe

B nh ni EEPROM - c th ghi/ xo ln ti hng triu ln

Cc cng xut/nhp (mc lgic thng t 0v n 5v, ng vi mc logic 0 v 1,

dng khong vi chc mA)

8/16 bit timer

Modun giao tip ngoi vi ni tip khng ng b: USART

Modun giao tip ngoi vi song song (kiu my in)

B chuyn i ADC 10 bit ni gm 8 knh u vo

Module ngoi vi MSSP dng cho cc giao tip I2C, SPI

Modul CCP c chc nng

o Comparator (so snh)

o Capture

o PWM: dng trong iu khin ng c

Mt s dng vi iu khin PIC h tr thm:

H tr iu khin ng c 3 pha, 1 pha

H tr giao tip USB

H tr iu khin Ethernet

H tr giao tip CAN

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

H tr giao tip LIN

H tr giao tip IRDA

DSP nhng tnh nng x l tn hiu s

1.3 Cc thnh phn c bn ca mt mch ng dng vi iu khin PIC:

1.4 Cc khi nim c bn:

Cng xut nhp I/O:

Trong vi iu khin PIC16F877A c 5 cng:

Cng A gm 6 chn: RA0, RA1.. RA5

Cng B gm 8 chn: RB0, RB1,..RB7

Cng C gm 8 chn: RC0, RC1, ..RC7

Cng D gm 8 chn: RD0, RD1,..RD7

Cng E gm 3 chn: RE0, RE1, RE2

Mi cng thc cht c qun l bi cc thanh ghi PORTA, PORTB, PORTC, PORTD,

PORTE nm trong b nh RAM ca vi iu khin. Xem hnh sau:

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

B nh RAM ca vi iu khin PIC 16F877A gm 4 bank nh. Nhn vo cc bank nh

ta c th thy cc thanh ghi c t tn v cc thanh ghi a mc ch (General Purpose

Register).

Cc thanh ghi c t tn l cc thanh ghi c bit dng iu khin, qun l

hoc th hin trng thi ca cc khi chc nng trong vi iu khin v d PORTA

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

l i din cho cc chn cng A, PORTB l i din cho cc chn cng B v.v. Cc

thanh ghi ny c a ch xc nh v khng c dng cho cc mc ch khc

Cc thanh ghi a mc ch c dng t bin trong mt chng trnh ng

dng ca vi iu khin. Nhn vo bn b nh RAM, ta thy bin c th t t

a ch 20F n 7Fh trong bank nh 0, A0h-EFh, 120h-16Fh, 1A0h-1EFh.

Tr li vn v cc cng, ti y ta c th a ra nhn xt:

Thanh ghi PORTA phn nh trng thi ca cc chn cng A, ngha l mun tn hiu u

ra ca cc chn cng A nh th no ta ch vic a gi tr vo cc bit tng ng trn

thanh ghi PORTA. Cng nh khi c gi tr ca thanh ghi PORTA ta s bit c trng

thi ca cc chn cng A.

V d:

Mun RA0 mc logic 1 (mc 5V), RA1 mc logic 0 (mc 0V), RA2 mc logic 1,

RA3 mc logic 0, RA4 mc logic 1, RA5 mc logic 1, ta ch vic gn gi tr

000110101 cho thanh ghi PORTA.

X

1

RA5

0

RA4

1

RA3

0

RA2

1

RA1

RA0

X: khng quan tm.

Tng t nh vy vi PORTB,PORT C,PORTD,PORTE.

Tnh a chc nng ca mt chn trn vi iu khin:

Nhn vo s chn ca vi iu khin, ta c th thy mt s chn ca vi iu khin c

tn gm nhiu phn vi du gch cho. V d: RA0/AN0, RC7/RX/DT, RC6/TX/CK

y chnh l tnh a chc nng ca mt chn trn vi iu khin hay cn gi l s dn

knh.

ngha ca n l:

Bnh thng nu khng c ci t th tc c cc chn trn 5 cng A, B, C, D, E l cc

chn vo ra s I/O.

Nu trong chng trnh ta c ci t mt chc nng no nh RS232, ADC hoc PWM

v.v th cc chn tng ng vi chc nng s hot ng theo chc nng . Khi

chn ny s khng c dng lm chn vo ra s nh bnh thng na.

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

V d: bnh thng chn RA0/ANO l chn vo ra s RA0, nu chc nng ADC vi knh

vo tn hiu analog l knh 0 c ci t khi chn RA0 /AN0 s l chn vo ca b

ADC, tc l hot ng theo chc nng AN0.

Tng t nh vy, khi ci t giao tip vi thit b ngoi vi theo chun RS232, chn vo

ra s RC7/RX/DT s hot ng nh u vo d liu RS232 tc l chc nng RX ca

chn ny.

Ci t vo/ra cho cc chn vo ra s trn cc cng:

Cc chn vo/ra s trn vi iu khin PIC phi c ci t l chn vo hoc chn ra th

mi hot ng ng chc nng. Vic mt chn trn cng X (X=A,B,..E) c qui nh l

u ra hay u vo ph thuc vo bit tng ng trn thanh ghi TRISX (X=A,B,..E) l 0

hay 1.

V d: Mun 4 chn thp (bit thp) trn cng B (RB0-RB3) l chn vo, 4 chn cao (bit

cao) trn cng B (RB4-RB7) l chn ra th gi tr cc bit trn thanh ghi TRISB s l:

0

Gi d nh l:

chn RB.m (m=0-7) l u ra, tc Output th gi tr TRISB.m l 0

L u vo, tc Input th gi tr TRISB.m l 1

Tng t nh vy i vi cc chn trn cc cng cn li

2. Ngn ng lp trnh cho vi iu khin PIC- CCS:

2.1 Cc ngn ng lp trnh cho vi iu khin PIC:

Ngn ng lp trnh cho vi iu khin PIC c 2 loi:

-

Ngn ng lp trnh cp thp- Hp ng: c phn mm MPLAB

Ngn ng lp trnh bc cao: c nhiu loi, c pht trin theo ngn ng C, nh:

CCS, HTPIC, PIC BASIC v.v

u im ca hp ng l gip ngi hc v lp trnh hiu r hn v cu trc bn trong ca

vi iu khin PIC, cng nh ti u ha b nh chng trnh. Tuy nhin, nhn chung

phng php tip cn hp ng l kh v kh nng pht trin ng dng l hn ch, mt

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

thi gian. V vy, kha hc s tp trung vo s dng ngn ng bc cao m c th l CCS

nghin cu v pht trin cc ng dng trn PIC.

u im ca CCS l:

-

K tha tc c c im ca ngn ng C- l ngn ng c bn, quen thuc m sinh

vin c o to

Xy dng sn cc hm phc v cho vic s dng d dng cc khi chc nng c

bit ca Vi iu khin PIC nh khi ADC, PWM, RS232, SPI

C kh nng kt hp vi ngn ng hp ng, to s mm do trong pht trin ng

dng

Kh nng pht trin, nng cp ng dng l d dng

Ngy cng c cp nht vi nhiu tnh nng u vit v hiu qu hn.

2.2 C bn v ngn ng lp trnh CCS:

2.2.1 V d v mt chng trnh vit trn ngn ng CCS:

// y l ch thch chng trnh

//Bt u cc ch th tin x l ca chng trnh

#include<16f877a.h> // cho file nh ngha thit b 16f877a.h vo chng trnh

#fuses HS,NOLVP,NOWDT// Cu hnh cho vi iu khin PIC

#use delay (clock=4000000) // dng thch anh tn s 4MHz

// Khai bo bin hng

byte const MAP[10] = {0xC0,0xF9,0xA4,0xB0,0x99,0x92,0x82,0xF8,0x80,0x90};

//===========================================

//===========================================

// Bt u chng trnh con hin th

void display(int n)

{

char b; // khai bo bin b

b=((MAP[n/10]) ^ 0x00);

if ((n/10)==(0)) b=0xff;

output_b(b); // s dng hm xut gi tr ra cng B

output_low(PIN_A4);// s dng hm a gi tr chn RA4 xung mc thp

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

delay_ms(2);// S dng hm to tr 2 ms

output_high(PIN_A4); // s dng hm a gi tr chn RA4 ln mc cao

output_b((MAP[n%10]) ^ 0x00);

output_low(PIN_A5);

delay_ms(2);

output_high(PIN_A5);

}

// Kt thc chng trnh con hin th

//============================================

// Bt u chng trnh chnh

// y l ni vi iu khin bt u chy lnh

//============================================

void main()

{

int i,count;

count=0;

while(TRUE)

{

for (i=0;i<=50;i++)

display(count);

// dispay 50 times

count=(count==99) ? 1: count+1;

}

}

2.2.2 Cu trc ca mt chng trnh vit bng CCS:

2.2.2.1 Khai bo tin x l:

Bt u mt chng trnh vit bng ngn ng CCS l phn khai bo tin x l:

1. u tin l phn khai bo file header: #include <tn chip dng.h>

V d: # include <16f877a.h>

Vic khai bo ny thc cht l chp c file 16f877a.h vo chng trnh ny.

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

Vy ni dung ca file .h ny l g? Ni dung ca file ny s nh ngha tc c cc

tn cng nh nh ngha cc hng s c dng trong cc hm chc nng ca

CCS.

V d trong chng trnh cho trn, trong dng lnh :

output_low(PIN_A4);// s dng hm a gi tr chn RA4 xung mc thp

th hng PIN_A4 c nh ngha trong file 16f877a.h l #define PIN_A4 44,

CCS hiu y l bit th 4 ca thanh ghi c a ch 04h (thanh ghi PORTA).

C th m file: C:\Program Files\PICC\Devices\16f877a.h hiu thm

2. Th hai l phn khai bo cu hnh: #fuses HS,NOLVP,NOWDT

Vi iu khin PIC c th hot ng nhiu ch khc nhau, cng nh cch cu

hnh phn cng ca n cng c nhiu ch . Mi ch nh vy c khai bo

v dng s nh hng n hot ng ca cc khi chc nng, cng nh cc chn

ca vi iu khin. V vy, i vi mi ng dng, ta phi khai bo cu hnh cho

ph hp.

Trong v d trn, khai bo cu hnh cho b dao ng kiu HS, khng s dng

chc nng Watchdog Timer, v lp trnh in p thp.

3. Th ba l phn khai bo tn s ca thch anh dng cho ng dng, tc ny phi

ph hp vi thch anh ta dng trong mch.

# USE Delay(clock=tn s thch anh)

V d: # USE Delay(clock=4000000)// Khai bo dng thch anh 4 MHz

iu lu l chng ta ch dng c hm to thi gian tr delay_ms(),

delay_us() sau khi c khai bo ny trong chng trnh.

4. Ngoi ra, khi s dng bt c khi chc nng c bit no trong vi iu khin PIC

ta phi dng ch th tin x l #USE khai bo. Cc khi chc nng c bit l

RS232, PWM, SPI, I2C ..v.v

V d: #use rs232(baud=9600, xmit=PIN_C6,rcv=PIN_C7)

2.2.2.2 Phn khai bo bin ton cc:

Sau phn khai bo tin x l l phn khai bo bin ton cc nu c.

Cng nhc li bin ton cc l bin c s dng trong ton b chng trnh, c chng

trnh chnh v chng trnh con. iu ny khc vi bin cc b l bin c khai bo

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

trong cc chng trnh con, hm con, chng trnh chnh, cc bin ny ch c to ra v

s dng trong chnh mi chng trnh khai bo n.

Nhn y cng gii thiu qua dng d liu dng trong CCS. C mt s cc dng c bn

nh sau:

Khai bo bin:

Int1,short: dng logic 1,0

Int,Int8,byte: dng s nguyn 8 bit, nu khai bo dng s nguyn 8 bit c du thm signed

Int16,long: dng s nguyn 16 bit

Int32: dng s nguyn 32 bit

Char: dng k t 8 bit

Float: dng s thc 32 bit

V d: int8 a; // Khai bo a l bin s nguyn 8 bit

Khai bo hng s:

V d: int8 const a=231;

Khai bo mng hng s:

V d: int const a[5]= {1, 23, 3, 4, 5}

2.2.2.3 Phn khai bo, nh ngha cc chng trnh con:

Chng trnh con l chng trnh s c gi t chng trnh chnh hoc chng trnh

con khc.

Chng trnh con phi c khai bo v nh ngha trong mt file chng trnh ng

dng.

Phn khai bo phi t trc chng trnh chnh (trong file)

Phn nh ngha c th nh ngha ngay trong khai bo hoc c t bt k ni no sau

phn khai bo bin ton cc nu c.

Ngoi cc chng trnh con bnh thng ra, cn c chng trnh con phc v ngt c

t sau khai bo tin x l: # int_tn ngt. Phn ny s c bn k hn trong cc bi hc

sau.

2.2.2.3 Phn chng trnh chnh:

Bt u bng:

void main() {

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

}

Cng nhc li l trong mt chng trnh CCS , vi iu khin s chy t chng trnh

chnh, hay ni cch khc l t dng lnh u tin sau void main().

Cc chng trnh con ch c gi ti cc li gi chng trnh con trong chng trnh

chnh hoc t cc chng trnh con khc. Chng trnh con phc v ngt ch c chy

khi c ngt xy ra, v ngt c cho php (s bn k hn trong cc bi hc sau).

2.2.3 Cc cu trc thut ton ca ngn ng CCS:

Cu trc thut ton ca ngn ng CCS k tha 100% t ngn ng C. y xin nhc li

mt s cc cu trc hay dng:

-

Cu trc IF:

o If (biu thc)

Lnh1;

Else lnh2;

V d: if (x==25)

x=1;

else

x=x+1;

Cu trc lp While:

o While (biu thc)

{

Cc lnh;

}

V d: While (count<20)

{

Output_B(count);

Count=count+1;

}

Ch : while(1) s thc hin cc lnh trong khi while ny mi mi

Cu trc lp FOR:

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

o For (biu thc 1, biu thc 2, biu thc 3)

{

Cc lnh;

}

V d: for (i=1;i<=10;++i)

A=a+i;

-

Cu trc la chn SWITCH:

o SWITCH (bin)

{

Case gi tr 1: lnh 1;

Break;

Case gi tr 2: lnh 2;

Break;

Case gi tr n: lnh n

Break;

[default: lnh n+1; break;]

}

V d: switch (cmd)

{

case 0:printf("cmd 0");

break;

case 1:printf("cmd 1");

break;

default:printf("bad cmd");

break;

}

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

Ch : lnh break c dng thot lp tc khi mt vng lp For, While, Switch

2.2.4 Cc ton t c bn trong CCS:

Hon ton tng t trong C.

Nhc li mt s ton t hay dng:

- += ngha l cng thm mt gi tr v ly kt qu

V d: a+=2 ngha l a= a+2

Tng t i vi cc php ton tr, chia, nhn

-++ ngha l cng thm 1 n v vo bin

V d: a++; tc l a=a+1

- &&: php AND

- ||: php OR

- !: php NOT

- !=: khng bng

- >>n: dch tri n bit

- <<n: dch phi n bit

2.2.5 Cc hm s hc c bn trong CCS:

Hon ton ging trong C.

Nhc li mt s hm c bn:

Abs (): ly tr tuyt i

Ceil(): lm trn theo hng tng

Floor(): lm trn theo hng gim

Pow(): ly tha

Sqrt(): ly cn

Chi tit tra help CCS : trong tab contents, chn Built-In-Function

Ch l khi s dng cc hm ny cn khai bo file header tng ng

2.2.6 Cc hm vo ra c bn trong CCS:

-

Output_low (chn): cho chn xung mc logic thp (mc in p 0V), chn c

th l:

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

PIN_A0, PIN_A1, ..PIN_B0, PIN_B1,.. PIN_C0,..v.v Ni chung l cc chn c

tn trong file C:\Program Files\PICC\Devices\16f877a.h

V d: Output_low(PIN_D0) a chn RD0 ca PIC xung mc thp

-

Output_high(chn): cho chn ln mc logic thp (mc in p 0V), chn c th

l:

PIN_A0, PIN_A1, ..PIN_B0, PIN_B1,.. PIN_C0,..v.v Ni chung l cc chn c

tn trong file C:\Program Files\PICC\Devices\16f877a.h

V d: Output_high(PIN_a5) a chn Ra5 ca PIC ln mc cao

Output_bit(chn,gi tr): l lnh tng hp 2 lnh trn, xut gi tr ra chn. Gi

tr c th l 0 (mc thp) hoc l 1 (mc cao). Tn chn tng t nh 2 lnh trn

V d: output_bit(PIN_E0,1); a chn E0 ln mc 1

Output_X(gi tr): lnh ny a gi tr ra cng X. X c th l A, B, C, D, E.

V d: Output_A(0x21); a gi tr 0x21 ra cng A

Bin=Input_X(): a gi tr ca cng X vo Bin. X l A, hoc B, C, D, E

V d: bien1= Input_A()

Bin=Input(chn): lnh ny a gi tr ca chn vo bin. Chn tng t nh

trong cc lnh.

V d: bien2= Input(PIN_A2);

2.2.7 Cc hm to tr:

Cc hm to tr gm delay_cycles(), delay_us(), delay_ms. To mt khong thi gian tr

t lc lnh c thc hin. Ch l phi s dng khai bo tin x l # use

delay(clock=tn s) th mi dng c cc lnh ny.

-

delay_cycles(s chu k): to tr mt khong thi gian bng s chu k. S chu

k=0-255

delay_us(s micro giy): to tr s micro giy. S micro giy =0-65535

delay_ms(s mili giy): to tr s mili giy. S mili giy= 0-65535

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

II. PHN THC HNH

Mc tiu:

- Lm quen vi ngn ng lp trnh CCS, phn mm m phng Proteus, kit pht

trin

- Hiu c cc phn c bn ca mt mch thc thi vi iu khin PIC

- Hiu c vic xut nhp d liu trn cc chn vi iu khin

- n li t duy lp trnh, thut ton v cu trc mt chng trnh vit trn C

- Lm quen vi mt s lnh c bn trong CCS

Bi tp 1.1: Dng phn mm m phng Proteus thit k mch nh hnh v sau:

a. Vit chng trnh bt n led D1

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

b. Vit chng trnh bt n led D2, to tr 1s, tt n led D2, lp li qu trnh ny

c. Vit chng trnh bt n D1, D2, D7 theo gi tr ca cng B t 0x00 n 0xFF

ri lp li qu trnh .

d. Vit chng trnh bt cc n led theo trnh t nh sau: D1 sng, D1 tt ng thi

D2 sng, D2 tt ng thi D3 sng v.v. V lp li

Bi tp 1.2: Dng Proteus thit k mch nh hnh v

Vit chng trnh hin th cc led theo qui lut sau:

-

Ban u khng c n no sang

Mi ln bm vo phm bm ni vi chn RD0, n s sng theo s ln bm: bm

1 ln n D1 sng, bm 2 ln n D2 sng, bm 8 ln n D8 sng, bm 9 ln

quay li chu trnh trn.

Bi 1.3: Vit chng trnh m phng ho quang cha trong ngy l.

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

BI 2: CC PHNG PHP HIN TH TRONG CC

THIT B DNG VI IU KHIN

PHN L THUYT:

Hin nay, trong hu ht cc thit b nhng u c s dng cc khi hin th. Mc ch cho ngi

dng gim st, ci t v hin th cc thng s ca thit b cng nh i tng cn gim st iu

khin.

C rt nhiu phng php hin th, c th k ra nh sau:

-

Hin th cnh bo, bo li: thng thng dng led n. C th hin th theo kiu dng

nhiu mu khc nhau hoc bt tt v.v

Hin th s liu: dng led 7 on, LCD hoc LCD ha v.v

Hin th trn my tnh: dng cc phn mm iu khin gim st, kt ni thit b v my

tnh thng qua chun RS232 hoc cc chun mng (gim st t xa)

Trong bi ny s gii thiu 2 cch hin th u, phn hin th bng my tnh s c cp trong

bi hc v chun giao tip RS232.

2.1 Hin th bng led n:

y l cch hin th n gin nht.

Thng thng cch hin th ny dng bo mt trng thi no y ca thit b nh trng thi

lm vic ca ngun (li hoc khng li), cng nh cc khi chc nng khc.

C rt nhiu loi led n dng hin th. Phng php n gin nh sau:

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

Hnh 2.1: Hin th led n

Cc led ny sng khi c cp p c 2 V, dng 10-20mA.

Nu dng mt chn ra t vi iu khin bt tt led, phi dng thm in tr hn dng,hn p.

Tnh ton nh sau:

Mun bt n, ta cho chn ra vi iu khin ln mc cao ni vi u vo ca mch trn. Nh ta

bit, chn ra vi iu khin mc logic cao c in p 5V.

Cho in p ri trn led l 2V, dng qua l 15mA.

Suy ra, in p ri trn tr l 3V. Dng qua led chnh l dng qua in tr v bng 15mA.

Suy ra, in tr dng: R=3/15mA=200 ohm.

Chn in tr tiu chun 220 ohm

(in tr tiu chun: 10, 11, 12, 13, 15, 16, 18, 20, 22, 24, 27, 30, 33, 36, 39, 43, 47, 51, 56, 62,

68, 72, 82, 91 v cc bi s)

2.2 Hin th bng led by on- 7 segment led:

2.2.1 Cu to ca led 7 on:

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

Hnh 2.2: Led 7 on

Mt led 7 on thc ra l gm 7 led n ni vi nhau (8 led n nu c thm du chm-dp).

C 2 loi:

-

Chung catod: cc u catod (cc m) c ni chung vi nhau v ni vi t, cc u

anod a,b,c,d,e,f,g,h c a ra ngoi (cc chn) nhn tn hiu iu khin. Khi cp in

p 5v cho mi u anod, led tng ng vi u s sng

Chung anod: cc u anod (cc m) c ni chung vi nhau v ni vi ngun, cc u

catod a,b,c,d,e,f,g,h c a ra ngoi (cc chn) nhn tn hiu iu khin. Mun led n

no sng ch vic a chn catod ca led tng ng xung mc 0V.

Hnh 2.3: Cu to ca 2 loi led 7 on

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

2.2.2 Hin th 1 led 7 on dng vi iu khin:

Nh gii thiu phn trn, thc cht led 7 on gm 8 hoc 7 led n ni vi nhau. V vy

iu khin thanh led n sng, cch thc hin phn cng nh hnh 2.1.

C th hn, nh dng led chung anod nh hnh v trn. Mi u vo a,b,c,d,e,f,g,h c ni vi

mt chn ca vi iu khin, tng ng l RB0, RB1, ..RB7, thng qua cc in tr phn p 200

ohm, u anod chung c ni vi ngun. led n sng n gin ta a chn vi iu khin

ni vi led xung mc thp.

Nh trn hnh 2.4 trn, led 7 on hin th s 2 th cc led a,b,d,e,g sng; cc led c, f tt. Gi tr

sng tng ng chn vi iu khin ni vo mc 0, gi tr tt tng ng vi chn vi iu khin

ni vi mc 1.

Do ni dung ca thanh ghi PORTB l:

0

y l m led 7 on ca s 2

Nh vy, chng ta lu mt iu rng, d liu xut ra led 7 on l m led tng ng vi s cn

xut

M led tng ng vi cc s t 0 n 9 l:

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

0xC0,0xF9,0xA4,0xB0,0x99,0x92,0x82,0xF8,0x80,0x90

Cch iu khin led 7 on chung catod th ngc li.

2.2.3 Hin th nhiu led 7 on dng vi iu khin:

Trong thc t, ta phi dng nhiu led 7 on hin th.

Vy gii quyt vic hin th nhiu led nh th no?

V d: hin th s 35 bng 2 led 7 on.

i chiu vi cch hin th 1 led 7 on, ta ngh n gin ch l dng 1 cng hin th s 3, 1 cng

khc hin th s 5.

Nh vy ta mt 2 cng. Hin th 4 led th mt 4 cng => ton b chn trn vi iu khin dng cho

vic hin th ledKhng cn chn giao tip vi cc thit b khc nh bn phm, u vo s

khc v.v Khng kh thi!

Ta c phng php tit kim chn hn gii quyt:

Hnh 2.5: Hin th 2 led 7 on

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

Cc chn d liu (chn s nhn m led t vi iu khin) c ni tng ng vi nhau v ni vo

1 cng ca vi iu khin, chng hn nh cng B

Chn ngun ca 2 led c iu khin bi 2 chn trn vi iu khin, chng hn chn RA4 v

RA5 nh trn hnh, thng qua cc B ca 2 transistor pnp.

Qu trnh hin th con s 35 trn 2 led s nh sau:

-

Cho chn RA4 (chn ni vi led hng chc) xung mc thp, transistor th nht m do

tip gip BE thun, chn RA5 ln mc cao (chn ni vi led hng n v), transistor th

hai khng m. Vy ch c led hng chc c cp ngun.

Cho cng B xut d liu m led ca s 3. Ch c led hng chc c cp ngun nn ch

c led ny sng

To thi gian tr 10-20ms

iu khin tng t cho led hng n v c cp ngun, led hng chc khng cp

ngun, xut d liu m led s 5 ra cng B. Led n v hin th s 5.

To thi gian tr 10-20ms

Quay li bc th nht

Nh vy, s 3 hin th 10ms, s 5 hin th 10ms v quay vng nh vy. Thi gian ny rt nhanh,

do hiu ng ca mt, ta cm gic nh s 35 hin th cng lc. Bi ton c gii quyt, ta ch mt

c 10 chn iu khin 2 led.

Cch hin th nhiu led cng tng t nh vy.

Cng gii thch thm l do dng transistor ni vo RA4, RA5. Do chn vi iu khin c dng

khong vi chc mA, y l chn cp ngun cho led 7 on, mi led n trong Led 7 on mt

20mA vy c led 7 on mt trn 100mA. V vy ta phi dng transistor khuch i dng.

2.3 Hin th dng LCD:

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

7

8

9

10

11

12

13

14

D0

D1

D2

D3

D4

D5

D6

D7

RS

RW

E

4

5

6

1

2

3

VSS

VDD

VEE

LM016L

Hnh 2.6: Cc chn LCD

2.3.1 Cc chn c bn ca LCD 2 dng 16 k t:

VSS: Chn t

VCC: Chn ngun

VEE: Chn hiu chnh sng ca LCD

RS:

=0: LCD s nhn lnh t vi iu khin

=1: LCD s nhn k t t vi iu khin hin th

R/W:

=1: Vi iu khin c d liu t LCD

=0: Vi iu khin ghi d liu ln LCD

Thng thng Vi iu khin ch yu ghi d liu ln LCD nn chn ny thng ni t

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

E: Chn cho php (Enable). Sau khi lnh hoc d liu c chun b trn ng d

liu, to xung mc cao-mc thp s bt u qu trnh LCD nhn d liu hoc lnh t vi

iu khin.

D0-D7: cc chn d liu, ni vi iu khin truyn lnh hoc d liu ln LCD.

2.3.2 Khi to LCD:

LCD c nhiu lm vic, c th k ra nh sau:

-

Ch 1 dng hay 2 dng

Ch giao tip 4 bit hay 8 bit

Ch font 5*8 hoc 5*10

Ngoi ra cn c th thay i v tr hin th k t v.v

V vy, trc khi bt u qu trnh hin th mt chui k t no , ta cn qu trnh khi to

ci t cc ch ny. Vi iu khin thc hin qu trnh khi to ny bt cch ghi n LCD mt

chui cc lnh.

Cn c vo chc nng ca cc chn vi iu khin c gii thiu trn, ta a ra qui trnh ca

vic gi mt lnh t Vi iu khin n LCD:

-

Cho chn R/W=0 xc nh y l ghi xung LCD (thng thng chn ny c ni

t, nn mc nh chn ny mc 0, ta khng cn quan tm n na)

Cho chn RS=0 xc nh y l lnh m vi iu khin gi xung LCD (phn bit vi

RS=1, gi k t hin th)

Gi m lnh xung LCD theo cc ng d liu (RD0-RD7 nu dng ch 8 bit, R4R7 nu dng ch 4 bit)

a chn E (chn cho php- Enable) ln mc cao, mc 1

To tr vi chu k lnh

a chn E xung mc thp, mc 0

M lnh nh gii thiu trong phn trn ty thuc vo tng lnh, y gii thiu mt s lnh

c bn nh sau:

. Lnh ci t ch lm vic:

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

DL

I/D

DL:

= 1: 8 bit

= 0: 4 bit

= 1: 2 dng

= 0 1 dng

= 1: font 5x10 dot

= 0: font 5x8 dot

N:

F:

. Lnh t ch tng gim a ch:

0

I/D:

= 1 tng a ch

= 0 gim a ch

=1: Ci t di chuyn cng a ch

S:

. Lnh t ch hin th:

0

D: Cho php hin th

C: ci t hin th con tr

B: nhp nhy v tr k t

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

. Lnh t v tr hin th ca k t:

C

a ch dng 1: 00- 0F

a ch dng 2: 40-4F

V vy, mun hin th u dng th nht, m lnh s l 0x80

mun hin th u dng th hai, m lnh s l 0xC0

. Lnh xa mn hnh: m lnh 0x01

. Lnh tr v u dng th nht: m lnh 0x02

Chi tit c th xem datasheet i km

2.3.2 Ghi k t ln LCD hin th:

Sau khi thc hin qu trnh khi to gi cc lnh ci t ch lm vic ca LCD, k t s

c hin th ln LCD bt k khi no vi iu khin mun gi.

Qu trnh gi k t gm cc bc sau:

-

Cho chn R/W=0 xc nh y l ghi xung LCD (thng thng chn ny c ni

t, nn mc nh chn ny mc 0, ta khng cn quan tm n na)

Cho chn RS=1 xc nh y l k t m vi iu khin gi xung LCD (phn bit vi

RS=0, gi lnh)

Gi m ascii ca k t cn hin th xung LCD theo cc ng d liu (RD0-RD7 nu

dng ch 8 bit, R4-R7 nu dng ch 4 bit)

a chn E (chn cho php- Enable) ln mc cao, mc 1

To tr vi chu k lnh

a chn E xung mc thp, mc 0

2.4 Gii thiu mt th vin cho LCD 4 bit v bi tp ng dng:

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

File: LCD_lib_4bit:

#include <stddef.h>

#define LCD_RS

PIN_B2

#define LCD_EN

PIN_B3

#define LCD_D4

PIN_B4

#define LCD_D5

PIN_B5

#define LCD_D6

PIN_B6

#define LCD_D7

PIN_B7

#define Line_1

0x80

#define Line_2

0xC0

#define Clear_Scr

0x01

#separate void LCD_Init ();// ham khoi tao LCD

#separate void LCD_SetPosition ( unsigned int cX );//Thiet lap vi tri con tro

#separate void LCD_PutChar ( unsigned int cX );// Ham viet1kitu/1chuoi len LCD

#separate void LCD_PutCmd ( unsigned int cX) ;// Ham gui lenh len LCD

#separate void LCD_PulseEnable ( void );// Xung kich hoat

#separate void LCD_SetData ( unsigned int cX );// Dat du lieu len chan Data

//khoi tao LCD**********************************************

#separate void LCD_Init ()

{

LCD_SetData ( 0x00 );

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

delay_ms(20);

/*Cho cho lcd khoi tao */

output_low ( LCD_RS );// che do gui lenh

LCD_SetData ( 0x03 ); /* khoi tao che do 4 bit */

LCD_PulseEnable();

LCD_PulseEnable();

LCD_PulseEnable();

LCD_SetData ( 0x02 ); /* tao giao dien 4 bit */

LCD_PulseEnable();

/* send dual nibbles hereafter, MSN first */

LCD_PutCmd ( 0x2C ); /* function set (all lines, 5x7 characters) */

LCD_PutCmd ( 0x0C ); /* display ON, cursor off, no blink */

LCD_PutCmd ( 0x06 ); /* entry mode set, increment & scroll left */

LCD_PutCmd ( 0x01 ); /* clear display */

// Init for BarGraph

#separate void LCD_SetPosition ( unsigned int cX )

{

/* this subroutine works specifically for 4-bit Port A */

LCD_SetData ( swap ( cX ) | 0x08 );

LCD_PulseEnable();

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

LCD_SetData ( swap ( cX ) );

LCD_PulseEnable();

}

#separate void LCD_PutChar ( unsigned int cX )

{

/* this subroutine works specifically for 4-bit Port A */

output_high ( LCD_RS );

LCD_PutCmd( cX );

output_low ( LCD_RS );

}

#separate void LCD_PutCmd ( unsigned int cX )

{

LCD_SetData ( swap ( cX ) );

/* send high nibble */

LCD_PulseEnable();

LCD_SetData ( swap ( cX ) );

/* send low nibble */

LCD_PulseEnable();

}

#separate void LCD_PulseEnable ( void )

{

output_high ( LCD_EN );

delay_us ( 3 );

// was 10

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

output_low ( LCD_EN );

delay_ms ( 3 );

// was 5

}

#separate void LCD_SetData ( unsigned int CX )

{

output_bit ( LCD_D4, CX & 0x01 );

output_bit ( LCD_D5, CX & 0x02 );

output_bit ( LCD_D6, CX & 0x04 );

output_bit ( LCD_D7, CX & 0x08 );

}

Chng trnh ng dng:

LCD1

LM016L

C1

30pF

8

9

10

1

R9

RA0/AN0

RA1/AN1

RA2/AN2/VREF-/CVREF

RA3/AN3/VREF+

RA4/T0CKI/C1OUT

RA5/AN4/SS/C2OUT

RC0/T1OSO/T1CKI

RE0/AN5/RD

RC1/T1OSI/CCP2

RE1/AN6/WR

RC2/CCP1

RE2/AN7/CS

RC3/SCK/SCL

RC4/SDI/SDA

MCLR/Vpp/THV

RC5/SDO

RC6/TX/CK

RC7/RX/DT

4K

RD0/PSP0

RD1/PSP1

RD2/PSP2

RD3/PSP3

RD4/PSP4

RD5/PSP5

RD6/PSP6

RD7/PSP7

33

34

35

36

37

38

39

40

D0

D1

D2

D3

D4

D5

D6

D7

RB0/INT

RB1

RB2

RB3/PGM

RB4

RB5

RB6/PGC

RB7/PGD

7

8

9

10

11

12

13

14

2

3

4

5

6

7

OSC1/CLKIN

OSC2/CLKOUT

RS

RW

E

13

14

4

5

6

CRYSTAL

1

2

3

X1

C2

VSS

VDD

VEE

UDK

30pF

15

16

17

18

23

24

25

26

19

20

21

22

27

28

29

30

PIC16F877A

Hnh 2.7: V d v LCD

#include <16f877A.h>

#fuses HS, NOLVP, NOWDT, NOPROTECT

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

#use delay (clock=4000000) //Use built-in function: delay_ms() & delay_us()

#include "LCD_LIB_4BIT.c"

VOID MAIN()

{

LCD_INIT();

LCD_PUTCHAR('X');

DELAY_MS(1000);

LCD_PUTCHAR('I');

DELAY_MS(1000);

LCD_PUTCHAR('N');

DELAY_MS(1000);

LCD_PUTCHAR(' ');

DELAY_MS(1000);

LCD_PUTCHAR('C');

DELAY_MS(1000);

LCD_PUTCHAR('H');

DELAY_MS(1000);

LCD_PUTCHAR('A');

DELAY_MS(1000);

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

LCD_PUTCHAR('O');

PHN THC HNH:

Bi 2.2: Hin th 1 led 7 on

Bi 2.3: Thit k mch trn Proteus nh hnh 2.5

a. Lp trnh cho 2 led hin th s 35

b. Lp trnh hin th s m t 0-99

Bi 2.4 Thit k mch trn Proteus nh hnh 2.7

Lp trnh thc hin hin th h tn, thay i cc ch hin th bng cch gi lnh ln LCD

BI 3: B NH THI - TIMER

3.1 Gii thiu:

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

Trong cc ng dng ca vi iu khin trong thc t, vic nh thi (to mt khong thi gian gia

2 s kin) cc thao tc l vic thng xuyn xy ra.

thc hin vic ny, ta c 2 cch:

-

Dng cc lnh thc hin cc vng lp to ra khong thi gian. Nguyn tc to ra

khong thi gian ny n gin nh sau: nu vi iu khin mt mt khong thi gian x

thc hin mt lnh, vic lp li mt lnh n ln s mt n*x thi gian.

Trong chng trnh, cch ny c dng nhiu vi th hin l cc lnh Delay_ms(),

Delay_us()

Dng cc b nh thi Timer to ra khong thi gian tr.

Trong bi ny, ta s i vo nguyn cu cc b timer. Mt ch quan trng na ca Timer l khi

n hot ng nh b m. Trong ng dng ny, timer hot ng nh mt b m, c nhim v

m s cc xung i vo mt chn c th trn vi iu khin. Ch b m ny c nhiu ng

dng trong thc t nh m s vng quay ca ng c (phn hi t b o tc ng cencoder), m s sn phm trn mt dy chuyn v.v.

Vi iu khin PIC16F877A c 3 b Timer:

-

Timer0: 8 bit (s m ti a ca n l 255), hot ng 2 ch nh thi v b m.

Timer1: 16 bit (s m ti a ca n l 65535), hot ng 2 ch nh thi v b

m.

Timer2: 8 bit, hot ng phc v chc nng PWM (Pulse Width Modulation- iu ch

rng xung)

Trong bi ny ta i vo kho st 2 b Timer0 v Timer1, Timer2 s c kho st trong bi v

PWM.

tin cho vic kho st, ta i vo nguyn l hot ng c bn ca cc b timer hai ch :

nh thi v b m.

3.2 Nguyn l hot ng c bn ca mt b Timer:

3.2.1 Ch nh thi:

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

Mi b timer c mt hoc nhiu thanh ghi cha gi tr m ca n (ty thuc vo di ca

timer), ta gi s tn thanh ghi l TMR c di l n byte, hay gi tr m ti a l

. Khi

gi tr ca TMR t n gi tr ny, vi iu khin s set bit c ca b timer ln mc 1. Ngi

dng s bit c thi im ny bng cch kim tra bit c. ng thi TMR s t ng xa v gi

tr 0.

Khi c ci t hot ng trong ch nh thi, Gi tr ca thanh ghi TMR s t ng tng

ln 1 n v sau mi chu k lnh ca vi iu khin. Khi gi tr ca TMR t n gi tr ti a, bit

c ca Timer s c set ln mc 1 v TMR b xa, TMR=0.

Gi s vi iu khin dng thch anh tn s 4MHz, nh vy:

Chu k lnh= 4 chu k thch anh=

=1s

Vy TMR s t ng tng ln 1 n v sau 1s.

Nu ban u ta cho TMR= x. Th sau khong thi gian

ti a ca n l

(s) gi tr TMR s t gi tr

. Thi im ny c xc nh thng qua trng thi ca bit c.

Ngc li, ta mun thc hin nh thi khong thi gian t sau mt s kin 1 nh sau:

-

S kin 1

To khong thi gian tr t

S kin 2

Ta lm cc bc:

-

S kin 1

Gn gi tr ban u cho TMR =

Kim tra bit c

Khi bit c = 1, thc hin s kin 2.

Tht vy, sau 1 (s) TMR tng ln 1 n v, tng gi tr cho TMR t

ti a

(khi bit c c set ln 1) mt

n gi tr

-t) = t (s)

Vy khong thi gian t sau s kin 1 (khi TMR bt u c gn) n s kin 2 (ngay sau khi

bit c c set) l t ng nh yu cu ca ta.

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

V d: nh thi 200 (s) dng Timer0 (8 bit; n=1; gi tr ti a l 255) ta cho TMR0= 255200=55 ri bt u cho m ln.

3.2.2 Ch b m:

Khi c ci t trong ny, mt chn chc nng trn vi iu khin s tr thnh chn u vo xung

ca b m. V d: chn RA4 i vi Timer0 v RC0 i vi Timer1. Hot ng ca n c nt

ging vi ch nh thi.

Khi c ci t hot ng trong ch b m, Gi tr ca thanh ghi TMR s t ng tng ln

1 n v khi c mt xung vo chn u vo xung ca timer . Khi gi tr ca TMR0 t n gi

tr ti a, bit c ca Timer s c set ln mc 1 v TMR b xa, TMR=0.

Nh vy, v cch hot ng trong ch ny ch khc vi ch nh thi ch, thay v TMR t

ng tng ln sau mi chu k lnh, th TMR tng ln khi c mt xung i vo chn u vo xung

ca Timer .

Dng xung c xc nh l sn m hay sn dng ph thuc vo vic ci t bit chn dng

xung tng ng trn thanh ghi ca vi iu khin.

Nguyn l hot ng nh thi v b m ny cng ng vi cc b vi iu khin, vi x l khc.

Ta i vo kho st c th 2 Timer0 v Timer1 ca vi iu khin PIC.

3.3 Timer 0:

3.3.1 Nguyn l hot ng:

Timer 0 c di 8 bit Thanh ghi cha gi tr m l TMR0 (s m ti a l 255). Hot ng

2 ch l nh thi v b m.

hot ng ch nh thi, ta cho bit T0CS (bit 5 ca thanh ghi Option_Reg) mc 0. Khi

, gi tr ca thanh ghi TMR0 s t ng tng ln 1 n v sau mi chu k lnh ca vi iu khin.

hot ng ch b m, ta cho bit T0CS (bit 5 ca thanh ghi Option_Reg) mc 1. Khi

, gi tr ca thanh ghi TMR0 s t ng tng ln 1 n v sau khi c mt xung i vo chn RA4

ca vi iu khin. Vic chn xung l dng sn ln hay sn xung ph thuc vo bit T0SE (bit 4

ca thanh ghi Option_Reg l 0 hay 1.

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

Khi gi tr TMR0 t n gi tr ti a 255 (0xFF) n s b xa v 0 ng thi bit c TMR0IF

(bit 5 ca thanh ghi INTCON ) c set ln 1, bo cho chng trnh bit c s trn TMR.

Lu l ngi lp trnh phi xa TMR0IF bng chng trnh ( ghi nhn ng cc ln trn k

tip).

Ngoi ra, tng thi gian nh thi hoc s xung m u vo ti a ca Timer 0, vi iu khin

cn cho php vic la chn t l Prescale cho u vo ca Timer 0 bng 3 bit PS2-PS0 (bit 2-0

ca thanh ghi

Option_ Reg). T l nh sau:

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

Ta c th hiu n gin nh sau:

Nu t l Prescale l 1:64 th:

-

Trong ch nh thi, TMR0 s tng ln 1 n v sau 64 chu k lnh

Trong ch nh thi, TMR0 s tng ln 1 n v sau khi c 64 xung i vo chn RA4

Nh vy, thi gian nh thi ti a cng nh s xung m c khi TMR0 trn s tng ln 64 ln.

Tng t vi cc t l khc.

Thc ra, Timer 0 chia s b chia tn s Prescale vi mt ch khc ca vi iu khin- ch

Watchdog Timer. Vic chn ch ny c thc hin khi cho bit PSA (bit 3 ca thanh ghi

Option_Reg) gi tr 0. Ch ny s c nghin cu sau. y ta ch quan tm n b chia tn

s dnh cho Timer 0 khi PSA=1. V vy trong s trn ta ch quan tm n cc ng n ghi

ch thm bng ng thng mng.

3.3.2 Cc thanh ghi lin quan:

Thanh ghi TMR0 (a ch 01h):

Cha gi tr m hin ti ca Timer 0

Thanh ghi Option_Reg (a ch 81h):

T0CS: Bit chn ch

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

= 0: TMR0 hot ng ch nh thi

= 1: TMR0 hot ng ch b m

T0SE: Bit chn dng xung cho ch b m

= 0: Xung sn ln

= 1: Xung sn xung

PSA: Bit chn ch cho b chia tn s PresCale l WatchDog_Timer hay Timer 0.

= 0: B chia tn s dnh cho Timer 0

= 1: B chia tn s dnh cho Watch_Dog Timer

PS2-PS0: 3 bit chn t l chia tn s nh gii thiu phn trn

Thanh ghi INTCON (0Bh):

Bit TMR0IE: Bit ny bng 1 cho php ngt Timer 0. S kin ngt xy ra khi c s trn

TMR0 t 255 xung 0.

Bit TMR0IF: Bit c xc nhn gi tr TMR0 b trn t 255 v 0

3.3.3 Cc lnh CCS dng cho thanh ghi Timer 0:

Lnh ci t ch : Setup_timer_0 (ch |t l chia tn s)

Ch c th l mt trong nhng t sau:

-

RTCC_INTERNAL: ch nh thi

RTCC_EXT_L_TO_H: ch b m vi xung dng sn ln

RTCC_EXT_H_TO_L: ch b m vi xung dng sn xung

T l chia tn s l mt trong nhng t sau:

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

RTCC_DIV_2, RTCC_DIV_4, RTCC_DIV_8, RTCC_DIV_16, RTCC_DIV_32,

RTCC_DIV_64, RTCC_DIV_128, RTCC_DIV_256: tng ng vi t l chia

Lnh gn gi tr u cho thanh ghi TMR0: Set_timer_0 (gi tr)

Gi tr nm trong khong t 0-255

Lnh c gi tr hin ti ca thanh ghi TMR0: bin = Get_timer_0()

3.4 Timer 1:

3.4.1 Nguyn l hot ng:

Timer 1 c di 16 bit. Gi tr ca b m timer 1 c lu trong 2 thanh ghi 8 bit TMR1H v

TMR1L. Timer 1 cng c 2 ch c ci t bi bit TMR1CS (bit 1 ca thanh ghi T1CON):

-

TMR1CS = 0: Ch nh thi

TMR1CS = 1: Ch b m. C 2 dng c phn bit bi bit T1SYNC (bit 2 ca

T1CON)

o

T1SYNC = 0: B m ng b

T1SYNC = 1: B m khng ng b

Trong ch b m, u vo cho xung c th ni vo chn RC0 hoc RC1 ty thuc vo bit

T1OSCEN (bit 3 ca T1CON)

-

T1OSCEN = 1: u vo xung ni vi RC1

T1OSCEN = 0: u vo xung ni vi RC0

Ch l khc vi Timer 0, u vo xung Timer 1 phi c dng sn xung.

Ch ng b ca ch b m ngha l nu nh vi iu khin ang ch ng th gi tr

ca thanh ghi TMR1L v TMR2L khng tng ln.

T l b chia tn s Prescal ca timer 1 c chn bi 2 bit T1CKPS1-T1CKPS0 (Bit 5-4 ca

T1CON). T l chia ln nht l 1:8.

3.4.2 Cc thanh ghi lin quan:

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

Thanh ghi TMR1L (a ch 0Eh) v TMR1H (a ch 0Fh):

Thanh ghi cha 8 bit thp v 8 bit cao ca gi tr m 16 bit ca timer 1.

Thanh ghi iu khin Timer 1- T1CON (a ch 10h):

- - T1CKPS1 T1CKPS0 T1OSCEN T1SYNC TMR1CS TMR1ON

T1CKPS1-T1CKPS0: Chn t l b chia tn s:

T1CKPS1-T1CKPS0

T l chia tn s

00

1:1

01

1:2

10

1:4

11

1:8

T1OSCEN: bit chn u vo xung l RC1 hay RC0

-

=1: RC1

=0: RC0

T1SYNC: bit chn ch b m ng b

-

=1: Khng ng b

=0: Khng ng b

TMR1CS: bit chn ch nh thi hay ch b m

-

=1: Ch b m

=0: Ch b nh thi

TMR1ON: bit bt hay tt Timer 1

-

=1: Bt Timer 1

=0: Tt Timer 1

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

Thanh ghi PIR1:

Kqt

Kqt

kqt kqt

Kqt

kqt

kqt TMR1IF

Bit TMR1IF l bit c ca timer 1. Bit c set ln gi tr 1 khi xy ra trn 2 thanh ghi TMR1L v

TMR2H t 65535 v 0.

3.4.3 Cc lnh CCS lin quan n Timer 1:

Lnh ci t ch : Setup_timer_1 (ch |t l chia tn s)

Ch c th l mt trong nhng t sau:

-

T1_DISABLE: khng s dng, tt Timer 1

T1_INTERNAL: ch nh thi

T1_EXTERNAL: ch b m khng ng b

T1_EXTERNAL_SYNC: ch b ng b

T l chia tn s l mt trong nhng t sau:

-

T1_DIV_1, T1_DIV_2, T1_DIV_4, T1_DIV_8: tng ng vi t l chia

Lnh gn gi tr u cho cp thanh ghi TMR1L v TMR1H: Set_timer_1 (gi tr)

Gi tr nm trong khong t 0-65535

Lnh c gi tr hin ti ca cp thanh ghi TMR1L v TMR1H: bin = Get_timer_1()

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

BI TP:

3.1 Cho s mch nh sau:

C1

30pF

X1

C2

CRYSTAL

30pF

U1

13

14

OSC1/CLKIN

OSC2/CLKOUT

RB0/INT

RB1

RB2

RA0/AN0

RB3/PGM

RA1/AN1

RB4

RA2/AN2/VREF-/CVREF

RB5

RA3/AN3/VREF+

RB6/PGC

RA4/T0CKI/C1OUT

RB7/PGD

RA5/AN4/SS/C2OUT

RC0/T1OSO/T1CKI

RE0/AN5/RD

RC1/T1OSI/CCP2

RE1/AN6/WR

RC2/CCP1

RE2/AN7/CS

RC3/SCK/SCL

RC4/SDI/SDA

MCLR/Vpp/THV

RC5/SDO

RC6/TX/CK

RC7/RX/DT

2

3

4

5

6

7

8

9

10

R9

4K

RD0/PSP0

RD1/PSP1

RD2/PSP2

RD3/PSP3

RD4/PSP4

RD5/PSP5

RD6/PSP6

RD7/PSP7

33

34

35

36

37

38

39

40

R1

268

R2

220

15

16

17

18

23

24

25

26

R3

222

R4

220

19

20

21

22

27

28

29

30

R5

220

R6

220

PIC16F877A

R7

220

Q1

R8

PNP

4K

R10

Q2

PNP

10k

a. 2 led 7 on hin th s m, gi tr s m t ng tng ln t 0-99 sau khong thi

gian nh thi bi Timer 0

b. Tng thi gian nh thi bng cch s dng Timer 1

c. nh thi 1 s dng Timer 1

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

3.2 Cho s mch nh sau:

C1

30pF

X1

CRYSTAL

C2

30pF

U1

13

14

2

3

4

5

6

7

RC

4K

8

9

10

R9

4K

OSC1/CLKIN

OSC2/CLKOUT

RB0/INT

RB1

RB2

RB3/PGM

RB4

RB5

RB6/PGC

RB7/PGD

RA0/AN0

RA1/AN1

RA2/AN2/VREF-/CVREF

RA3/AN3/VREF+

RA4/T0CKI/C1OUT

RA5/AN4/SS/C2OUT

RC0/T1OSO/T1CKI

RE0/AN5/RD

RC1/T1OSI/CCP2

RE1/AN6/WR

RC2/CCP1

RE2/AN7/CS

RC3/SCK/SCL

RC4/SDI/SDA

MCLR/Vpp/THV

RC5/SDO

RC6/TX/CK

RC7/RX/DT

RD0/PSP0

RD1/PSP1

RD2/PSP2

RD3/PSP3

RD4/PSP4

RD5/PSP5

RD6/PSP6

RD7/PSP7

33

34

35

36

37

38

39

40

R1

268

R2

220

15

16

17

18

23

24

25

26

R3

222

R4

220

19

20

21

22

27

28

29

30

R5

220

R6

220

PIC16F877A

R7

220

Q1

R8

PNP

4K

Q2

R10

PNP

10k

Trong phm bm ni vi chn u vo xung ca Timer 0, RA4.

2

led by on hin th s ln bm phm

3.3 Cho s mch o tc ng c nh sau:

C1

30pF

X1

C2

CRYSTAL

30pF

LCD1

U1

8

9

10

1

R9

4K

LM016L

RD0/PSP0

RD1/PSP1

RD2/PSP2

RD3/PSP3

RD4/PSP4

RD5/PSP5

RD6/PSP6

RD7/PSP7

15

16

17

18

23

24

25

26

+12v

RV?

1k

+88.8

19

20

21

22

27

28

29

30

PIC16F877A

ng c c thay i tc nh bin tr. Tc ng c c o bi encoder nm

ngay trong ng c v tn hiu c truyn ti chn RA4, chn u vo xung ca Timer

0. Dng Timer 0 ch b m, Timer 1 ch nh thi c tc ng c.

Gi tr c c hin th ln LCD.

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

D0

D1

D2

D3

D4

D5

D6

D7

RS

RW

E

+12v

7

8

9

10

11

12

13

14

RA0/AN0

RA1/AN1

RA2/AN2/VREF-/CVREF

RA3/AN3/VREF+

RA4/T0CKI/C1OUT

RA5/AN4/SS/C2OUT

RC0/T1OSO/T1CKI

RE0/AN5/RD

RC1/T1OSI/CCP2

RE1/AN6/WR

RC2/CCP1

RE2/AN7/CS

RC3/SCK/SCL

RC4/SDI/SDA

MCLR/Vpp/THV

RC5/SDO

RC6/TX/CK

RC7/RX/DT

33

34

35

36

37

38

39

40

VSS

VDD

VEE

RB0/INT

RB1

RB2

RB3/PGM

RB4

RB5

RB6/PGC

RB7/PGD

4

5

6

2

3

4

5

6

7

OSC1/CLKIN

OSC2/CLKOUT

1

2

3

13

14

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

BI 4: NGT

4.1 Ngt l g:

Ngt hiu theo ngha n gin l cc s kin ngu nhin lm gin on qu trnh ca mt s kin

ang xy ra. c th d hiu khi nim mi ny ta cng a ra mt v d trong thc t nh sau:

V d: Trong gi hc trn lp, ta ang hc bi, c chung in thoi hoc c bn gi, ta phi

dng hot ng hc bi li tr li in thoi hoc ra gp bn. S kin in thoi reo chung,

hay bn b gi c gi l s kin ngt, vic ta tr li in thoi hay ra gp bn l chng trnh

phc v ngt. Vic ang hc bi c xem l chng trnh chnh.

Ngt c thc hin khi v ch khi ci t cho php n. Nh trong v d trn, nu s kin ngtin thoi reo xy ra, nu gio vin v bn thn ta cho php mnh tr li in thoi khi ang hc

bi th khi c in thoi ta mi nghe.

Vi iu khin cng c ngt. Cch x l ca n cng tng t nh v d trn.

C th hot ng ca vi iu khin khi c s kin ngt xy ra v ngt c cho php:

-

Thc hin nt lnh ang thc hin

Dng chng trnh ang thc hin

Lu li a ch ca lnh k tip trong chng trnh ang thc hin vo b nh stack

Nhy ti a ch 0x04 trong b nh chng trnh

Ti y, vi iu khin s thc hin chng trnh con phc v ngt do ngi lp trnh

lp trnh t trc.

Sau khi thc hin xong chng trnh con phc v ngt, vi iu khin ly li a ch ca

lnh k tip c lu v thc hin tip chng trnh ang thc hin d lc cha c

ngt

Nh vy, cch phn ng ca vi iu khin l kh tng ng vi cch x l ca con ngi trong

thc t. Nh trong v d trn, khi ta ang hc bi, khi c ngt, tc c in thoi-s kin ngt, ta

c nt t cui cng, nh dng ang c trang th my, nh du, tr li in thoi (chng

trnh con phc v ngt), tr li xong ta tr li hc bi dng, trang c nh du.

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

Ti y ta tng hp li cc thut ng dng cho x l ngt trong vi iu khin:

-

Ngun ngt: ngun ngt l nguyn nhn gy ra ngt. Nh trong v d trn, ngun ngt c

th

L in thoi gi hoc bn gi

S kin ngt: khi ngun ngt xy ra

Chng trnh con phc v ngt: l chng trnh vi iu khin x l khi c s kin ngt

xy ra do ngi lp trnh lp trnh ra

V d nh ta tr li hoc chy ra khi phng gp bn

Vecto ngt: tc a ch 0x04 ni vi iu khin chy ti sau khi lu a ch tr v

Bit cho php ngt: tc vic cho php vi iu khin chy chng trnh con phc v ngt

khi c s kin ngt xy ra. Trong vi iu khin PIC, mi ngt c bit cho php ca n. Bit

ny tn cng bng ch E (enable), nm trong cc thanh ghi chuyn dng. Mun cho php

ngt , ta phi a bit cho php ngt tng ng ln gi tr 1. Ngt ch thc s c cho

php ngt khi ta cho bit cho php ngt ton cc GIE (Global Interrupt Enable) ln mc 1.

Ta hnh dng nh sau: khi c s kin ngt- in thoi gi, nu ta cho php mnh nghe

in thoi (tc bit cho php ngt ca ngt c set ln 1) ng thi thy gio cho php

(bit cho php ngt ton cc GIE c ln mc 1) th ta mi nghe in thoi (cho chng

trnh con phc v ngt hot ng).

Mt s cc ngt khc, nh cc ngt ngoi vi bao gm ADC, PWM v.v Mun cho php n

cn phi a bit cho php ngt ngoi vi ln mc 1.

C ngt: l bit phn nh trng thi ca s kin ngt. Mi ngt c mt bit c. Khi bit c

ny bng 1 ngha l s kin ngt tng ng vi c xy ra. Ta hnh dung nh ting

chung ca in thoi l c ngt, chung rung bo c s kin ngt- c in thoi xy ra.

Cc bit ny tn cng bng t F (Flag- c). Lu l d mt ngt c c cho php hay

khng th c ngt vn c set ln 1 khi c s kin ngt xy ra. (D ta c c php nghe

in thoi hay khng th chung in thoi vn c reo).

4.2 Cc ngt trong vi iu khin PIC16F877A:

Vi iu khin PIC16F877A c 15 ngun ngt. c chia lm 2 lp ngt:

-

Lp ngt c bn: bao gm cc ngt c bn nh ngt trn timer 0, ngt ngoi, ngt thay

i trng thi ca cc chn PortB (RB4-RB7). Bit cho php ngt v bit c tng ng l

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

TMR0IE,TMR0IF; INTE, INTF; RBIE v RBIF. l cho php ngt thc s xy ra

phi c bit cho php ngt ton cc GIE.

-

Lp ngt ngoi vi: bao gm cc ngt ngoi vi nh ngt trn timer 1 (TMR1IE,

TMR1IF), ngt trn Timer 2(TMR2IE, TMR2IF), ngt hon thnh vic chuyn i ADC

(ADCIE, ADCIF), ngt hon thnh vic nhn k t trong truyn thng RS232 (RCIE,

RCIF), ngt hon thnh vic truyn k t trong truyn thng RS232 (TXIE, TXIF) v.v

l mun thc s cho php cc ngt ny ngoi bit cho php ngt ton cc c set phi

set c bt cho php ngt ngoi vi PEIE.

4.3 Vit chng trnh x l ngt bng CCS:

V d mt chng trnh c ngt nh sau:

#INCLUDE <16F877A.H>

#FUSES NOLVP, NOWDT, HS

#USE DELAY(CLOCK=8000000)

BYTE CONST MAP[10] = {0xC0,0xF9,0xA4,0xB0,0x99,0x92,0x82,0xF8,0x80,0x90};

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

VOID HIENTHI(INT A);

INT SODEM;

//CHUONG TRINH CON PHUC VU NGAT DAT SAU #INT_EXT

#INT_EXT

VOID NGATNGOAI()

{

// XOA CO NGAT NGOAI

CLEAR_INTERRUPT(INT_EXT);

// CAM NGAT TRONG CHUONG TRINH CON PHUC VU NGAT

DISABLE_INTERRUPTS(GLOBAL);

SODEM++;

// CHO PHEP NGAT TOAN CUC

ENABLE_INTERRUPTS(GLOBAL);

}

VOID HIENTHI(INT A)

{

INT HC, HDV;

HC=A/10;

HDV=A%10;

OUTPUT_LOW(PIN_A4);

OUTPUT_D(MAP[HC]);

DELAY_MS(15);

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

OUTPUT_HIGH(PIN_A4);

OUTPUT_LOW(PIN_A5);

OUTPUT_D(MAP[HDV]);

DELAY_MS(15);

OUTPUT_HIGH(PIN_A5);

}

VOID MAIN()

{

// CAI DAT VAO RA CHO CONG B

SET_TRIS_B(0xFF);

// CHO PHEP NGAT NGOAI

ENABLE_INTERRUPTS(INT_EXT);

// CAI DAT SUON NGAT

EXT_INT_EDGE(H_TO_L);

// CHO PHEP NGAT TOAN CUC

ENABLE_INTERRUPTS(GLOBAL);

// VONG LAP DOI NGAT

WHILE(1)

{

HIENTHI(SODEM);

}

}

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

Nh vy, lc vit chng trnh c dng ngt bng CCS, ta c nhng lu sau:

-

Trong chng trnh chnh (main), chng ta ci t ngt: cho php ngt c th, cho php

ngt ton cc. i ngt

Chng trnh con x l ngt l chng trnh con nm ngay sau ch th bin dch

#INT_XXX, trong XXX l tn ca ngt c th. V d: #INT_EXT: ngt ngoi

Trong chng trnh con x l ngt: xa c ngt, cm ngt ton cc phng khi ang x

l ngt c ngt xy ra. Sau khi x l d liu trong chng trnh con x l ngt, ta cho

php ngt ton cc li.

Tn mt s ngt ca PIC nh sau:

-

INT_EXT: ngt ngoi

INT_TIMER0: ngt timer 0

INT_TIMER1: ngt timer 1

INT_TIMER2: ngt timer 2

INT_RDA: ngt nhn k t trong truyn thng my tnh

INT_RB: ngt thay i trng thi cc chn RB7-RB4

Trong phn tip theo, ta s kho st mt s ngt tiu biu nh ngt ngoi INT, ngt thay i trng

thi cc chn cao PORTB, ngt trn Timer 0, ngt trn Timer 1. Cc ngt ngoi vi khc s c

nhc n khi nghin cu cc modun ngoi vi ny.

4.4 Ngt ngoi:

4.4.1 Hot ng:

-

Ngun ngt: l xung i vo chn RB0 ca vi iu khin PIC

S kin ngt: s kin ngt xy ra khi c xung i vo chn RB0 ca vi iu khin. Xung l

xung sn dng hay sn m ph thuc bit ci t chn dng xung, bit INTEDG ( bit 6

ca thanh ghi PTION_REG) l 1 hay khng.

Bit cho php ngt: cho php ngt ngoi, bit cho php ngt ngoi INTIE (bit 4 ca

thanh ghi INTCON) phi c set ln 1. Ngoi ra, bit cho php ngt ton cc GIE (bit 7

ca thanh ghi INTCON) cng phi c set ln 1.

C ngt: bit c ngt ngoi l bit INTIF (bit 1 ca thanh ghi INTCON) c t ng set

ln 1 khi c s kin ngt ngoi xy ra. C ny phi c xa bng chng trnh (c th l

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

trong chng trnh con phc v ngt) vi iu khin qun l chnh xc cc ln ngt k

tip.

4.4.2 Qun l ngt ngoi trong chng trnh CCS:

Trong chng trnh chnh, ci t ngt:

-

Ci t chn RB0 l chn vo: SET_TRIS_B(0x01)

Ci t dng xung u vo l sn dng hay sn m: EXT_INT_EDGE(H_TO_L)

hoc EXT_INT_EDGE(L_TO_H)

Cho php ngt ngoi: ENABLE_INTERRUPTS(INT_EXT)

Cho php ngt ton cc: ENABLE_INTERRUPTS(GLOBAL)

Chng trnh con phc v ngt t sau ch nh bin dch #INT_EXT:

#INT_EXT

nh ngha chng trnh con

Trong chng trnh con phc v ngt:

-

Xa c ngt: CLEAR_INTERRUPT(INT_EXT)

Cm ngt ton cc, phng lc ang x l ngt, li c ngt xy ra:

DISABLE_INTERRUPTS(GLOBAL)

X l ngt : ty thuc vo ca ngi lp trnh

Cho php ngt ton cc: ENABLE_INTERRUPTS(GLOBAL)

4.5 Ngt Thay i Trng Thi Cc Chn RB7-RB4:

4.5.1 Hot ng:

-

Ngun ngt: l trng thi ca mt trong cc chn RB7-RB4 ca vi iu khin PIC

S kin ngt: s kin ngt xy ra khi c s thay i trng thi (1-0 hay 0-1) ca mt trong

cc chn RB7-RB4 ca PortB

Bit cho php ngt: cho php ngt ny, bit cho php ngt RBIE (bit 3 ca thanh ghi

INTCON) phi c set ln 1. Ngoi ra, bit cho php ngt ton cc GIE (bit 7 ca thanh

ghi INTCON) cng phi c set ln 1.

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

C ngt: bit c ngt ngoi l bit RBIF (bit 0 ca thanh ghi INTCON) c t ng set

ln 1 khi c s kin ngt ngoi xy ra. C ny phi c xa bng chng trnh (c th l

trong chng trnh con phc v ngt) vi iu khin qun l chnh xc cc ln ngt k

tip.

Lu quan trng: Khi s dng ngt ny trong cc ng dng x l cc xung u vo RB4-RB7, v

d nh phm bm chng hn, ta cn lu im sau. Gi s nh ban u phm bm cha bm, u

vo RB mc 1, khi bm phm RB xung mc 1, nh vy c 1 s kin ngt xy ra. Tuy nhin,

khi th phm bm ra, RB ln mc 1, tc cng c mt s thay i trng thi ca chn RB7-RB4,

nn cng c ngt xy ra. V vy, vic n v nh phm bm c tnh 2 ln ngt. Cn iu ny

khi lp trnh.

Vn th 2 l cn s dng mt lnh c cng B loi b trng thi mismatch lc xy ra ngt

cc chn ny.

4.5.2 Qun l ngt RB trong chng trnh CCS:

Trong chng trnh chnh, ci t ngt:

-

Ci t chn RB4-RB7 l chn vo: SET_TRIS_B(0xF0)

Cho php ngt RB: ENABLE_INTERRUPTS(INT_RB)

Cho php ngt ton cc: ENABLE_INTERRUPTS(GLOBAL)

Chng trnh con phc v ngt t sau ch nh bin dch #INT_RB:

#INT_RB

nh ngha chng trnh con

Trong chng trnh con phc v ngt:

-

Xa c ngt: CLEAR_INTERRUPT(INT_RB)

Cm ngt ton cc, phng lc ang x l ngt, li c ngt xy ra:

DISABLE_INTERRUPTS(GLOBAL)

oc cng B loi b trng thi mismatch

X l ngt : ty thuc vo ca ngi lp trnh, ch n s ln ngt

Cho php ngt ton cc: ENABLE_INTERRUPTS(GLOBAL)

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

4.6 Ngt Timer 0:

4.6.1 Hot ng:

-

Ngun ngt: l trng thi trn ca thanh ghi b m timer 0, TMR0 vi iu khin PIC

S kin ngt: s kin ngt xy ra khi c s trn ca TMR0, tc l khi TMR0=255 ri b

xa

Bit cho php ngt: cho php ngt ny, bit cho php ngt TMR0IE (bit 5 ca thanh ghi

INTCON) phi c set ln 1. Ngoi ra, bit cho php ngt ton cc GIE (bit 7 ca thanh

ghi INTCON) cng phi c set ln 1.

C ngt: bit c ngt ngoi l bit TMR0IF (bit 2 ca thanh ghi INTCON) c t ng set

ln 1 khi c s kin ngt ngoi xy ra. C ny phi c xa bng chng trnh (c th l

trong chng trnh con phc v ngt) vi iu khin qun l chnh xc cc ln ngt k

tip.

4.6.2 Qun l ngt Timer 0 trong chng trnh CCS:

Trong chng trnh chnh, ci t ngt:

-

Gn gi tr ban u cho thanh ghi TMR0, ty thuc vo thi gian m ngi lp trnh

mun (xem li bi 3): SET_TIMER0(gi tr)

Cho php ngt timer 0: ENABLE_INTERRUPTS(INT_TIMER0)

Cho php ngt ton cc: ENABLE_INTERRUPTS(GLOBAL)

Chng trnh con phc v ngt t sau ch nh bin dch #INT_TIMER0:

#INT_TIMER0

nh ngha chng trnh con

Trong chng trnh con phc v ngt:

-

Xa c ngt: CLEAR_INTERRUPT(INT_TIMER0)

Cm ngt ton cc, phng lc ang x l ngt, li c ngt xy ra:

DISABLE_INTERRUPTS(GLOBAL)

X l ngt : ty thuc vo ca ngi lp trnh, ch n s ln ngt

Gn li gi tr ban u cho thanh ghi TMR0 (ty thuc vo ca ngi lp trnh):

SET_TIMER0(gi tr)

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

Cho php ngt ton cc: ENABLE_INTERRUPTS(GLOBAL)

BI TP:

4.1 Cho s mch nh hnh v:

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

R11

10K

U1

13

14

2

3

4

5

6

7

8

9

10

1

OSC1/CLKIN

OSC2/CLKOUT

RB0/INT

RB1

RB2

RB3/PGM

RB4

RB5

RB6/PGC

RB7/PGD

RA0/AN0

RA1/AN1

RA2/AN2/VREF-/CVREF

RA3/AN3/VREF+

RA4/T0CKI/C1OUT

RA5/AN4/SS/C2OUT

RC0/T1OSO/T1CKI

RE0/AN5/RD

RC1/T1OSI/CCP2

RE1/AN6/W R

RC2/CCP1

RE2/AN7/CS

RC3/SCK/SCL

RC4/SDI/SDA

MCLR/Vpp/THV

RC5/SDO

RC6/TX/CK

RC7/RX/DT

RD0/PSP0

RD1/PSP1

RD2/PSP2

RD3/PSP3

RD4/PSP4

RD5/PSP5

RD6/PSP6

RD7/PSP7

33

34

35

36

37

38

39

40

R1

268

R2

220

15

16

17

18

23

24

25

26

R3

222

R4

220

19

20

21

22

27

28

29

30

R5

220

R6

220

PIC16F877A

R7

220

Q1

R8

PNP

4K

R10

Q2

PNP

10k

Lp trnh mch hot ng nh sau: 2 led 7 on hin th s ln phm bm

4.2 Cho s mch nh sau:

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

C1

R11

R12

10K

10K

30pF

X1

C2

CRYSTAL

30pF

U1

13

14

2

3

4

5

6

7

8

9

10

R9

4K

OSC1/CLKIN

OSC2/CLKOUT

RB0/INT

RB1

RB2

RB3/PGM

RB4

RB5

RB6/PGC

RB7/PGD

RA0/AN0

RA1/AN1

RA2/AN2/VREF-/CVREF

RA3/AN3/VREF+

RA4/T0CKI/C1OUT

RA5/AN4/SS/C2OUT

RC0/T1OSO/T1CKI

RE0/AN5/RD

RC1/T1OSI/CCP2

RE1/AN6/WR

RC2/CCP1

RE2/AN7/CS

RC3/SCK/SCL

RC4/SDI/SDA

MCLR/Vpp/THV

RC5/SDO

RC6/TX/CK

RC7/RX/DT

RD0/PSP0

RD1/PSP1

RD2/PSP2

RD3/PSP3

RD4/PSP4

RD5/PSP5

RD6/PSP6

RD7/PSP7

33

34

35

36

37

38

39

40

D1

R1

268

LED-RED

D2

R2

220

LED-RED

15

16

17

18

23

24

25

26

19

20

21

22

27

28

29

30

PIC16F877A

D3

R3

222

LED-RED

D4

R4

220

LED-RED

D5

R5

220

LED-RED

D6

R6

220

LED-RED

D7

R7

220

LED-RED

2 led 7 on hin th s ln phm bm

4.3 Lm li cc bi tp 3.1, 3.2, 3.3 nhng s dng ngt.

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

BI 5: IU CH RNG XUNG-PWM

5.1 Nguyn l hot ng:

B iu ch rng xung to xung hnh ch nht trn 2 chn RC1/CCP2 v RC2/CCP1gi tr xung 2 chn l ngc nhau (b nhau). Thc ra y l mt chc nng ca modun

CCP gm 3 chc nng: Comparation, Capture, PWM.

Nguyn l to xung nh sau:

Khi Thanh ghi b m ca b nh thi Timer 2 t gi tr bng gi tr ca thanh ghi PR2,

u ra xung RC2/CCP1 c set ln mc cao. TMR2 c reset v 0, sau m ln,

khi TMR2 t gi tr bng rng xung, chn RC2/CCP1 c reset v 0. TMR2 tip tc

m ln cho n khi bng gi tr PR2 th chu trnh s lp li nh lc u. Xung ra chn

RC1/CC21 l b ca xung trn chn RC2/CCP1 .

5.2 Chu k xung:

xc nh chu k xung ta a ra phn tch nh sau:

Nh tm hiu v cch lm vic ca cc b timer, ta bit: sau mi chu k lnh gi tr ca

TMR2 s tng ln 1 n v. Nu dng b chia tn s, gi s l 1: N th sau N chu k lnh

gi tr ca TMR2 mi tng ln 1 n v.

Mi chu k lnh gm 4 chu k xung.

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

Chu k xung chnh l khong thi gian t lc TMR2=0 cho n khi TMR2=PR2. Suy ra,

tng PR2 n v, hay chnh l chu k xung s bng:

y, Tosc l chu k xung ca vi iu khin hay chu k ca thch anh

N l t l chia tn s.

V d: vi thch anh Fosc=4Mhz, N=4, ta c chu k xung ti a t c l khi PR2=255

(PR2 l thanh ghi 8 bit)

T=(255+1)*4*(1/4Mhz)*4=1024s

Tc tn s xung l: F=1/T=976Hz= 1KHz.

5.3 rng xung:

rng xung l gi tr 10 bit : trong 8 bit cao c ghi vo thanh ghi CCPR1L, v 2

bit thp ghi vo 2 bit 5 v 4 ca thanh ghi CCP1CON :

rng xung PWM c xc nh theo cng thc:

PWM Duty Cycle= (CCPR1L:CCP1CON<5:4>)*Tosc*N

Trong , CCPR1L l thanh ghi 8 bit, CCP1CON<5:4> l 2 bit 5 v 4 ca thanh ghi iu

khin CCP1CON. N l t l chia tn s.

5.4 Qui trnh thc hin xut xung PWM:

Gm cc bc:

-

Ci t modun CCP chc nng PWM: setup_CCP1(CCP_PWM)

Ci t Timer 2: setup_timer_2 (mode, period, 1)

Trong , mode c th l: T2_DISABLED, T2_DIV_BY_1, T2_DIV_BY_4,

T2_DIV_BY_16, ngha l tt Timer2 hoc nh t l b chia tn s

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

Period chnh l gi tr ca thanh ghi PR2 xc nh chu k ca xung

-

Ci t rng xung: set_pwm1_duty(value);

Trong , value l gi tr CCPR1L:CCP1CON<5:4>

V rng xung c tnh theo cng thc:

PWM Duty Cycle= value*Tosc*N

5.5 ng dng PWM trong iu khin tc ng c 1 chiu:

C1

30pF

X1

R9

RV1

10K

RD0/PSP0

RD1/PSP1

RD2/PSP2

RD3/PSP3

RD4/PSP4

RD5/PSP5

RD6/PSP6

RD7/PSP7

4K

33

34

35

36

37

38

39

40

LCD1

LM016L

15

16

17

18

23

24

25

26

D0

D1

D2

D3

D4

D5

D6

D7

RB0/INT

RB1

RB2

RA0/AN0

RB3/PGM

RA1/AN1

RB4

RA2/AN2/VREF-/CVREF

RB5

RA3/AN3/VREF+

RB 6/PGC

RA4/T0CKI/C1OUT

RB 7/PGD

RA5/AN4/SS/C2OUT

RC0/T1OSO/T1CKI

RE0/AN5/RD

RC1/T1OSI/CCP2

RE1/AN6/WR

RC2/CCP1

RE2/AN7/CS

RC3/SCK/SCL

RC4/SDI/SDA

MCLR/Vpp/THV

RC5/SDO

RC6/TX/CK

RC7/RX/DT

RS

RW

E

8

9

10

+5V

OSC1/CLKIN

OSC2/CLKOUT

7

8

9

10

11

12

13

14

2

3

4

5

6

7

VSS

VDD

VEE

30pF

UDK

13

14

4

5

6

CRYSTAL

1

2

3

C2

19

20

21

22

27

28

29

30

PIC16F877A

+12V

R6

U2

2K2

1

6

5

Q5

R5

NPN

1K

OPTOCOUPLER-NPN

Q2

NPN

R7

10k

+12V

R1

1

R11

10k

D32

U1

2K2

DIODE

6

+12V

5

2

Q?

R2

4

MPSA05

1K

OPTOCOUPLER-NPN

R3

10K

RL?

OMI-SH-205D

D1

DIODE

+88.8

BI TP:

1. Lp trnh xut xung PWM c tn s l 1KHZ, rng xung l 50%

2. ng dng PWM

CHNG TRNH BN PHM

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

#include <16F877A.h>

#fuses HS,NOWDT,NOPROTECT,NOLVP

#device *=16 adc=10

#use delay(clock=4000000)

#include <lcd_lib_4bit.c>

//#INCLUDE <KBD.C>

#define col0 PIN_B4

#define col1 PIN_B5

#define col2 PIN_B6

#define col3 PIN_B7

#define row0 PIN_B0

#define row1 PIN_B1

#define row2 PIN_B2

#define row3 PIN_B3

// Keypad layout:

char const KEYS[4][4] = {{'0','1','2','3'},

{'4','5','6','7'},

{'8','9','A','B'},

{'C','D','E','F'}

};

#define KBD_DEBOUNCE_FACTOR 100 // Set this number to apx n/333 where

// n is the number of times you expect

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

// to call kbd_getc each second

#SEPARATE void kbd_init() {

}

short int ALL_ROWS (void)

{

if (input (row0) & input (row1) & input (row2) & input (row3))

return (0);

else

return (1);

}

char kbd_getc( ) {

static byte kbd_call_count;

static short int kbd_down;

static char last_key;

static byte col;

byte kchar;

byte row;

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

kchar='\0';

if(++kbd_call_count>KBD_DEBOUNCE_FACTOR) {

switch (col) {

case 0 :

output_low(col0);

output_high(col1);

output_high(col2);

output_high(col3);

//DELAY_MS(1000);

break;

case 1 : output_high(col0);

output_low(col1);

output_high(col2);

output_high(col3);

break;

case 2 : output_high(col0);

output_high(col1);

output_low(col2);

output_high(col3);

break;

case 3 : output_high(col0);

output_high(col1);

output_high(col2);

output_low(col3);

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

break;

}

if(kbd_down)//NEU LAN TRUOC DO DA CO MOT PHIM DUOC BAM

{

if(!ALL_ROWS())//DOI CHO DEN KHI PHIM DUOC NHA RA

{

kbd_down=false;

kchar=last_key;

last_key='\0';

}

}

else //NEU KHONG CO PHIM NAO BAM TRUOC DO

{

if(ALL_ROWS())//NEU CO PHIM BAM

{

if(!input (row0))

row=0;

else if(!input (row1))

row=1;

else if(!input (row2))

row=2;

else if(!input (row3))

row=3;

last_key =KEYS[row][col];

kbd_down = true;

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

}

else // NEU KHONG CO PHIM NAO BAM, CHUYEN SANG QUET COT TIEP THEO

{

++col;

if(col>=4)

col=0;

}

}

kbd_call_count=0;//SAU 1 LAN QUET RESET KBD_CALL_COUNT VE 0, DE DOI LAN

QUET TIEP

}

return(kchar);

}

void main()

{

INT C;

INT16 value;

SET_TRIS_D(0X00);

SET_TRIS_B(0X0F);

lcd_putcmd(0x80);

lcd_init();

delay_ms(200);

OUTPUT_B(0XF0);

PRINTF(LCD_PUTCHAR,"PHIM BAM: ");

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

while( TRUE )

{

C=KBD_GETC();

IF (C!='\0')

{

LCD_PUTCMD(0X01);

PRINTF(LCD_PUTCHAR,"%C",C);

}

Chng trnh nhp s:

void main()

{

INT C;

INT16 DAT_THU;

INT16 value;

SET_TRIS_D(0X00);

SET_TRIS_B(0X0F);

lcd_putcmd(0x80);

lcd_init();

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

delay_ms(200);

PRINTF(LCD_PUTCHAR,"PHIM BAM: ");

WHILE( TRUE )

{

DAT_THU=0;

DO

{

C=KBD_GETC();

IF (C!='\0'& c!='A'&C!='B'& c!='C'&C!='D'& c!='D'&C!='E'&C!='F')

{

DAT_THU =DAT_THU*10;

DAT_THU=DAT_THU+C-0X30;

LCD_PUTCHAR(C);

}

}WHILE(C!='E');

LCD_PUTCMD(0X01);

PRINTF(LCD_PUTCHAR,"GIA TRI PHIM BAM:");

LCD_PUTCMD(0XC2);

PRINTF(LCD_PUTCHAR,"%6LU",DAT_THU);

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

HNG DN LP TRNH VI IU KHIN PIC VI PHN MM CCS

CNG TY TNHH CNG NGH CAO ATECKO

www.atecko.com.vn

You might also like

- Cac Lenh Lien Quan Ccs Hoc Pic PDFDocument116 pagesCac Lenh Lien Quan Ccs Hoc Pic PDFXuan Tien VuNo ratings yet

- GT Vixuly Vidieukhien PDFDocument131 pagesGT Vixuly Vidieukhien PDFPhạm Đắc NinNo ratings yet

- (123doc) - Do-An-Vi-Xu-Ly-Va-Vi-Dieu-Khien-Thiet-Ke-Bo-Dieu-Khien-Toc-Do-Cua-Dong-Co-Mot-Chieu-Su-Dung-Hop-Ngu-AssemblyDocument37 pages(123doc) - Do-An-Vi-Xu-Ly-Va-Vi-Dieu-Khien-Thiet-Ke-Bo-Dieu-Khien-Toc-Do-Cua-Dong-Co-Mot-Chieu-Su-Dung-Hop-Ngu-AssemblyDu DinhNo ratings yet

- Huong Dan Lap Trinh PIC 16F877ADocument26 pagesHuong Dan Lap Trinh PIC 16F877Angocthieu50% (2)

- Giáo Trình Vi Điều Khiển AVRDocument72 pagesGiáo Trình Vi Điều Khiển AVRVanHieu LuyenNo ratings yet

- Bài 1: Hướng dẫn lập trình cho PIC bằng CCS ver3.242: 1. Tổng quan về CCS 1.1. Vì sao ta sử dụng CCS?Document100 pagesBài 1: Hướng dẫn lập trình cho PIC bằng CCS ver3.242: 1. Tổng quan về CCS 1.1. Vì sao ta sử dụng CCS?Anonymous BrUMhCjbiBNo ratings yet

- VI ĐIỀU KHIÊN PIC16F877ADocument15 pagesVI ĐIỀU KHIÊN PIC16F877ATường Vy100% (1)

- Lich Van Niên Dùng PICDocument23 pagesLich Van Niên Dùng PICThanhha NguyenNo ratings yet

- Chuong 2 - Vi Điều Khiển Pic 18F4550Document38 pagesChuong 2 - Vi Điều Khiển Pic 18F4550hoangphi09016289No ratings yet

- Bai 001 VXL Pic CautrucDocument12 pagesBai 001 VXL Pic CautrucMinh Tien LeNo ratings yet

- Giao Trinh Vi Dieu Khien Pic 16F877A PDFDocument117 pagesGiao Trinh Vi Dieu Khien Pic 16F877A PDFHoai Duc0% (1)

- (Lập trình PIC) Bộ Chuyển Đổi ADC - Các Hàm Vào - Ra trong CCS - Linh Kiện Điện Tử- Thiết Kế Mạch Điện Tử Theo Yêu Cầu!Document12 pages(Lập trình PIC) Bộ Chuyển Đổi ADC - Các Hàm Vào - Ra trong CCS - Linh Kiện Điện Tử- Thiết Kế Mạch Điện Tử Theo Yêu Cầu!Chu Đình HiếuNo ratings yet

- Bai 1 - Tong Quan Vi Dieu Khien PIC18F4550Document66 pagesBai 1 - Tong Quan Vi Dieu Khien PIC18F4550Bùi BắcNo ratings yet

- Kien Thuc Gop Nhat y Kien Cac Dien Dan-PicDocument5 pagesKien Thuc Gop Nhat y Kien Cac Dien Dan-PicNguyen HaNo ratings yet

- Pic Là GìDocument248 pagesPic Là GìTrần Thái PhongNo ratings yet

- Ccs Phu Luc PicDocument34 pagesCcs Phu Luc PicÂu Đức QuyềnNo ratings yet

- DK Den GiaothongDocument33 pagesDK Den GiaothongNguyễn Đức LễNo ratings yet

- Báo Cáo - Pic16f877a - LM35 - LCDDocument20 pagesBáo Cáo - Pic16f877a - LM35 - LCDTuan QuocNo ratings yet

- Dùng 8051 điều khiển chạy chữ trên màn hình LCDDocument186 pagesDùng 8051 điều khiển chạy chữ trên màn hình LCDNguyenVanHaindNo ratings yet

- Giao Trinh VI Dieu Khien Pic 16f877apdf PDFDocument117 pagesGiao Trinh VI Dieu Khien Pic 16f877apdf PDFNguyễn Minh TuấnNo ratings yet

- MôDocument7 pagesMô21161251No ratings yet

- (Gửi Cho Sv) Đề Cương Ôn Tập Vi Điều Khiển Ứng Dụng Trong Đo Lường Và Điều Khiển k12Document6 pages(Gửi Cho Sv) Đề Cương Ôn Tập Vi Điều Khiển Ứng Dụng Trong Đo Lường Và Điều Khiển k12Bao AnhNo ratings yet

- BTL Nhom 1 1 1Document20 pagesBTL Nhom 1 1 1Đăng Nguyễn HảiNo ratings yet

- UntitledDocument35 pagesUntitled0225Nguyễn Phi HùngNo ratings yet

- Truyen Thong USB PIC18f2550Document32 pagesTruyen Thong USB PIC18f2550Thang Le QuyetNo ratings yet

- Sach PICDocument21 pagesSach PICapi-3714448100% (2)

- DA - CDT1 - Lê Văn KhoaDocument43 pagesDA - CDT1 - Lê Văn KhoaĐô NguyễnNo ratings yet

- Ngon Ngu Lap Trinh VĐKDocument82 pagesNgon Ngu Lap Trinh VĐKkien le trungNo ratings yet

- Lap Trinh Avr Voi C WWW - Eeelabs.org Chuong1Document19 pagesLap Trinh Avr Voi C WWW - Eeelabs.org Chuong1spy004No ratings yet

- ĐK tốc độ quạt làm mát nhiệt độ phòngDocument47 pagesĐK tốc độ quạt làm mát nhiệt độ phòngHo PhuNo ratings yet

- BC VDKDocument15 pagesBC VDKNghiep Pham Nguyen BaNo ratings yet

- Mạch Đo Nhiệt Độ Sử Dụng LM35Document11 pagesMạch Đo Nhiệt Độ Sử Dụng LM35Duc Vuong LyNo ratings yet

- BaitaplonvxlDocument16 pagesBaitaplonvxlNguyễn Vũ Minh ViệtNo ratings yet

- Bai 004 VXL Pic PortDocument20 pagesBai 004 VXL Pic Porthoangtuongckd08No ratings yet

- Code mẫu cho PIC - Đo nhiệt độ, Hiển thị lên LCD 16x2 - Điện Tử Máy Tính - Kỹ Thuật Điện Tử - Vi Xử Lý - Lập Trình Nhúng - Công Nghệ Thông TinDocument4 pagesCode mẫu cho PIC - Đo nhiệt độ, Hiển thị lên LCD 16x2 - Điện Tử Máy Tính - Kỹ Thuật Điện Tử - Vi Xử Lý - Lập Trình Nhúng - Công Nghệ Thông TinCảnh ManuNo ratings yet

- Chapter 5 Led Button LCDDocument70 pagesChapter 5 Led Button LCDquangthanhlop10a9No ratings yet

- Chương 1: Hệ Thống Vi Xử Lý Và Vi Điều Khiển 1.1. Kiến trúc bộ vi xử lýDocument31 pagesChương 1: Hệ Thống Vi Xử Lý Và Vi Điều Khiển 1.1. Kiến trúc bộ vi xử lýQuang Le MinhNo ratings yet

- 2Document8 pages2Quang Le MinhNo ratings yet

- Vi điều khiển At89s52Document29 pagesVi điều khiển At89s52To CuongNo ratings yet

- ĐỒ ÁN KỸ THUẬT VI XỬ LÝ NHÓM 1Document21 pagesĐỒ ÁN KỸ THUẬT VI XỬ LÝ NHÓM 1Nguyễn KhoaNo ratings yet

- MSP430Document30 pagesMSP430Minh Thang VuNo ratings yet