Professional Documents

Culture Documents

Triode Emulator by Dimitri Danyuk

Uploaded by

t_caCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Triode Emulator by Dimitri Danyuk

Uploaded by

t_caCopyright:

Available Formats

Audio Engineering Society

Convention Paper 6008

Presented at the 116th Convention 2004 May 811 Berlin, Germany

This convention paper has been reproduced from the author's advance manuscript, without editing, corrections, or consideration by the Review Board. The AES takes no responsibility for the contents. Additional papers may be obtained by sending request and remittance to Audio Engineering Society, 60 East 42nd Street, New York, New York 10165-2520, USA; also see www.aes.org. All rights reserved. Reproduction of this paper, or any portion thereof, is not permitted without direct permission from the Journal of the Audio Engineering Society.

Triode Emulator

Dimitri Danyuk Digital Research Labs, Haverhill, MA 01832, USA ddanyuk@usa.net

ABSTRACT The design for a low-noise amplifier is presented. The amplifier has a tube-like transfer characteristic and produces harmonic distortion components that are similar to triode preamplifier.

0 INTRODUCTION The static transfer characteristics of the vacuum tube follow the three halves power law. This determines the distortion characteristics of tube amplifier. Modest amount of feedback does not allow one to achieve good linearity in many tube amplifiers. This is especially true when triode-based musical instrument preamplifiers without overall feedback are taken into consideration. Harmonic analysis for such amplifiers shows regularity in the production of each successive harmonic [1,2]. The second harmonic usually dominates, followed closely by the third. The higher harmonics rise with input level running parallel to the second and the third. There is a close relation between tube amplifier distortion and musical tone coloration [1]. A spectrum of harmonics, generated by a tube amplifier before the clipping region gives a full-bodied quality of sound. The audible difference between tube and solid-state amplifiers when they are clipped will not be discussed in this paper. That difference is described in [3]. The

tube 'sound' and tube amplifiers 'musicality' is the phenomenon that has a real existence [4]. In this paper consideration is given to a voltage amplifier employing a common source gain stage with local current feedback, and a highly linear current-to-voltage converter. It will be demonstrated that it is possible to construct an amplifier with a tube-like transfer characteristic. 1 TUBE DISTORTION The following equation for the vacuum triode plate current can be found in textbooks:

I p = k (V p + V g )

where I p - is plate voltage,

(1)

V g - is negative grid voltage,

D.Danyuk

Triode Simulator_ 0. At positive input voltages the grid current starts to flow. The analysis (Fig.2) shows the regularity in the production of each successive harmonic in plate current. It is very similar to the measured data [2] for the triode single stage design without feedback. The calculated data were obtained with V p =300V, =80, , DC grid voltage is equal to -1.875 V. These values are typical for low power triodes.

- is amplification factor and

k - is dependent on tube geometry.

k = 1 A V

Fig.1. Typical vacuum triode transfer characteristic. The typical transfer characteristic is presented in Fig.l. When V g = V p the plate current I p becomes equal to zero and the tube cuts off. If a triode stage with a resistive load is taken into account then V p = E p I p R p . Combining this with Eq.1 one can get a system of nonlinear equations for feedback stage [5]. With high plate load resistance the internal feedback [5] will be effective and will linearize ideal three halves law. It is instructive to plot individual distortion curves for triode plate current in the assumption of ideal power law dependence (Eq.l). The input level is normalized on the maximum input grid AC voltage when plate current reaches zero. The working point is chosen exactly in the center of the input working range. The range is bounded by V g = V p , below which the tube cuts-off and

Fig.2. Calculated distortion products for vacuum triode plate current, assuming an ideal three-halves power law transfer characteristic. 2 FET DISTORTION A field-effect transistor (FET) follows the parabo1ic relationship, as illustrated in Fig.3 (curve 1)

I d = I dss (V gs V( p ) gs 1) 2

where I d - is drain current,

(2)

V gs - is gate to source voltage,

V( p ) gs - is pinch-off voltage and

I dss - is drain current with gate and source tied

together.

AES 116th Convention, Berlin, Germany, 2004 May 811

Page 2 of 8

D.Danyuk

Triode Simulator_

2 V gs

+ (I dss Rs Vin ) = 0

denoting

2I R I dss Rs + V gs 1 dss s V( p ) gs V(2 ) gs p

+

(5)

V( p ) ss 2 I dss Rs

= for the simplicity

+ 2 4 V gs = Vin V gs Rs

I dss Rs (I dss Rs Vin ) V(2p ) gs

I dss Rs V(2p ) gs = I dss Rs (I dss Rs Vin ) V(2p ) gs I dss Rs2 V(2p ) gs

(6)

Id =

Fig.3. Transfer characteristics of a JFET. (1) - nearly ideal parabolic relationship without source resistor. (2) with local current feedback. Value of the source resistor is equal to 0.83V( p ) gs I dss = 250 .

V = in + Rs

2 4

(7)

By applying negative feedback to a single FET stage, it is possible to linearize the transfer characteristic. With an increase in loop gain the resultant transfer function becomes more linear. If a moderate amount of feedback is applied, a certain part of the FET stage transfer function will follow the three-halves power law. This is the intermediate case between ideal parabola and perfect straight line. For the FET stage with source resistor Rs one can write

It seems informative to plot the normalized drain current versus normalized input voltage for different values of Rs . The resulting set of curves is shown in Fig.4. Horizontal scale is the normalized input voltage

Vin V( p ) gs I dss Rs V( p ) gs

Vin V( p ) gs I dss Rs V( p ) gs Vin V( p ) gs I dss Rs V( p ) gs Vin V( p ) gs

= 0 , when Vin = V( p ) gs and = 1 , when V gs = 0 ( Vin = I dss Rs ).

I d = I dss (V gs V( p ) gs 1) 2

(3) (4)

Vin = I d Rs + V gs

The drain-source voltage is assumed rather high to ensure FET to operate in the saturation region. Resolving the system (3,4) one can get:

Within this input rage the JFET gate is reverse biased.

I dss Rs V( p ) gs

1 is a dc working point. 2

AES 116th Convention, Berlin, Germany, 2004 May 811

Page 3 of 8

D.Danyuk

Triode Simulator_ If Eq.8 holds, then the dc gate voltage relative to ground is nearly zero and the input range of the FET stage is nearly symmetrical and bounded by V( p ) gs and

Vertical scale is the normalized drain current

Id : I dss

Id I = 0 , when I d = 0 and d = 1 , I dss I dss when I d = I dss .

+ V( p ) gs (Fig.3, curve 2).

Fig.5. The exponent value n of the power Fig.4. Normalized transfer characteristics of a JFET with source resistor, with k = Rs dependence I d = (Vin ) , with

n

k = Rs

I dss as parameter. V( p ) gs

I dss as V( p ) gs

parameter. The transfer characteristic corresponds most closely to three-halves (1.4 1.6) power law within one-third of the range of input signal when

Let us assume that for the small deviations the drain current deviation I d raised in the n power of input

n

Rs = 0.83

V( p ) gs I dss

voltage deviation Vin : I d = (Vin ) . To obtain the

required exponent value one can take the double logarithm of the normalized transfer characteristics (Fig.4) and then differentiate them. The result is shown in Fig.5 It is clear from Fig.5, that the transfer characteristic of JFET common source stage with a local feedback resistor Rs , connected between FET source and ground will be described by the three-halves power law in the vicinity of the dc working point when

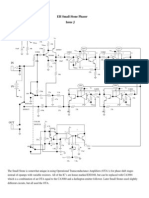

Log-antilog techniques and analog multipliers are the alternative approaches to the construction of a gain stage with the tube-like transfer characteristic. Several circuits based on these principles have been built and tested. Poor noise performance and excessive level of high-order distortion products are their drawbacks. 3 CIRCUIT DESCRIPTIONS AND MEASURED PERFORMANCE The complete circuit of the simulator is shown in Figs.8 and 9. The signal first passes through the input gain stage [6] and proceeds both to summing amplifier and FET common source stage. VR1 allows the gain to be adjusted to suit the level coming from the source before

Rs = 0.83

V( p ) gs I dss

(8)

AES 116th Convention, Berlin, Germany, 2004 May 811

Page 4 of 8

D.Danyuk reaching the clipping point of the FET stage. The input stage gain can be varied with the LEVEL control from 8 dB to 28 dB.

Triode Simulator_ sinks [9] (R8, R14, R21). The peak level detector (Fig.9) makes it possible to achieve maximum available rating from the FET stage and ensures that clipping is avoided. The simulator can be inserted between a preamp1ifier and power amplifier or in the tape/effect send/return connection. The essentials are the LEVEL and the GAIN controls. At first the signal should be adjusted with the LEVEL potentiometer just before the LED begins to flash. After setting the output level with the GAIN control, the EFFECT control can be adjusted to add some amount of distortion to the original program material. In the end, the listener should judge the measure of sound coloration.

Fig.6. Common source FET stage loaded by I-V converter. Operational amplifiers IC2 and IC3 form a highly linear current-to-voltage converter (Fig.6), which acts as a load to the FET stage and sets the gain. As the drain voltage of the FET is held at a constant level, the non1inearities associated with FET output network and gate-to-drain capacitance vanish. JFET has enough voltage across it to operate in the saturation region, while not that much to generate excessive noise due to reverse gate current. IC3 is used as a noninverting integrator in a servo feedback loop to ensure that the dc voltage at the output of the current-to-voltage converter remains close to the desired zero level. The IC3 stage works also as current source referring to the inverting input of IC2. The noise gain of IC2 in this case is equal to unity, as distinct from a previous circuit [7], where the noise contribution of IC2 was noticeable. The output from the FET stage is mixed with a dry input signal in the output summing stage. The summing stage inputs come from highly correlated signal sources, it was designed with criterion that at the center of the EFFECT potentiometer (VR4) there would be no error in the sum of the source levels [8]. The output stage gain can be varied with the GAIN control from -32 dB to +8 dB. Special care was taken to minimize the residual distortion of operational amplifiers. Their output stages operate in class A due to resistor current

Fig.7. Measured results for Fig.6 circuit. Several circuits were made in the form of tube simulator (Figs.8,9), active front-end electronics (Fig.6) [6] for various pick-ups (lead, bass guitar, etc ) and microphone amplifiers (by addition the input transformer to Fig.6 circuit). Fig.7 displays the measured amplitude levels of the individual harmonics normalized to the fundamental for various input levels for the circuit shown in Fig.6. The FET parameters are V( p ) gs = -3V, I dss = 10mA, fundamental frequency 1 kHz. Notice that each harmonic dominates the next one with a higher number and each harmonic is reproduced with a regular rate of decrease. This effectively matches the estimated (Fig.2) and measured [1,2] data for vacuum triode stages. Subjective testing has confirmed the psychoacoustic effect is tubelike. The reproduction of the sound of

AES 116th Convention, Berlin, Germany, 2004 May 811

Page 5 of 8

D.Danyuk acoustic guitars and violins has an impressive reality. One of a musicians reported that there is certain quality a tube amplifier must have and this design has not. It is the tubes. The reviewer could not peer inside the ventilation windows in the case and watch the tubes glow. 4 CONCLUSION The design of a low-noise tube simulator is presented. An advantage of the region of the transfer function of the FET stage with local current feedback, which is closest to the three-halves power law, is taken. The design exhibits the tube-like transfer characteristics and the weighting of harmonics that are similar to those estimated and measured for triode type amplifiers. The circuit seems to be suitable for such application in the audio world as instrument/microphone amplifiers and special effect processors like aural stimulators. 5 ACKNOWLEDGEMENT The author would like to thank the anonymous reviewers from JAES who helped to improve the final version of this paper. 6 REFERENCES [1] R.O.Hamm, "Tubes Versus Transistors - is there an Audible Difference," Journal of the Audio Eng. Soc., vol.21, pp.267-273, (1973 April). [2] J.Hiraga, "Amplifier Harmonic Distortion Spectrum Analysis," Hi-Fi News and Record Review, vol.22, pp.41,43,45 (1977 March). [3] B. Santo, Volume cranked up in amp debate, EE Times, iss.817, 1994 (Oct. 3). [4] D.R.G.Self, "Science versus Subjectivism in Audio Engineering," Electronics and Wireless World, vol.94, pp.692-696 (1988 July). [5] H.Stockman, Inherent Feedback in Triodes, Wireless Engineer, April 1953. [6] R.Williamson, "Volume Control Attenuates to Zero," Electronics World and Wireless World, vol.97, p.29 (1991 Jan.). [7] D.Danyuk and G.Pilko, "Active Guitar Electronics," Electronics Australia, 1994, May, p.65. [8] R.Orban, "Notes on Panpots," Journal of the Audio Eng. Soc., vol.19, pp.936-939 (1971 Dec). [9] E.F.Tailor, "Distortion in Low-noise Amplifiers," Wireless World, vol.83, Pt.l, pp.28-32 (1977 Aug.), Pt.2, pp.55-59 (1977 Sept).

Triode Simulator_ APPENDIX Table 1 - Parts list Resistors R1 56 kOhm R2, R7, R16, R17, R18, 10 kOhm R19, R23, R24, R25 R3, R8, R14, R21 2.2 kOhm R4 820 Ohm R5, R6, R12 100 kOhm R9 180 Ohm R10 100 Ohm R11, R22 390 Ohm R13, R15, R27 1.6 Mohm R20 4.7 kOhm R26 1.6 kOhm Al1 resistors 1/4 W 5%. Capacitors C1, C7 10 uF, 50 V, nonpolar electrolytic C2 100 uF, 25 V, electrolytic C3 20 pF, 10%, ceramic C4 560 pF, 10%, ceramic C5, C6, 0.68 uF, 10%, 63 V, polyester C9 C8 5.1 pF, 10%, ceramic Diodes Dl, D2, D3, D4 1N914 Z1 Zener 8 V Z2 Zener 4.7 V Transistors Q1 2N4416, 2N5270, 2N5459 or any small signal low-noise JFET Q2 BC182 or any small-signal, low noise, n-p-n BJT Integrated Circuits IC1,IC2, LF351A (TL071C) IC3,IC4 IC5 LM311 IC6 4069 hex CMOS invertor Miscellaneous VR1 47 kOhm, dual linear pot VR2 470 Ohm, multiturn trimpot VR3 2 kOhm, multiturn trimpot VR4 1 kOhm dual linear pot VR5 470 kO dual linear pot VR6, VR7 10 kOhm, multiturn trimpot

AES 116th Convention, Berlin, Germany, 2004 May 811

Page 6 of 8

D.Danyuk

Triode Simulator_

Fig.8. Triode simulator.

AES 116th Convention, Berlin, Germany, 2004 May 811

Page 7 of 8

D.Danyuk

Triode Simulator_

Fig.9. Overload detector. Adjustment procedure For the given FET two quantities should be measured: V( p ) gs - gate-source cut-off voltage and I dss - drain current with source short-circuited to gate. Then by VR2 the sum of VR2 and R9 is adjusted to be equal

0.83

V( p ) gs I dss

. VR3 allows achieving the overall unity

gain in FET stage, and the negative voltage on the slider of VR6 (VR7) is set to be equal V( p ) gs for the reliable peak overload detection.

Kiev, 1994 Cincinnati, 2003

AES 116th Convention, Berlin, Germany, 2004 May 811

Page 8 of 8

You might also like

- Class AB Push-Pull Vacuum Tube Guitar Amplifier Analysis, Design, and ConstructionDocument14 pagesClass AB Push-Pull Vacuum Tube Guitar Amplifier Analysis, Design, and ConstructiontekellamerZ aka tekellamer100% (2)

- Audio IC Circuits Manual: Newnes Circuits Manual SeriesFrom EverandAudio IC Circuits Manual: Newnes Circuits Manual SeriesRating: 5 out of 5 stars5/5 (1)

- Triodes at Low Voltages BlencoweDocument5 pagesTriodes at Low Voltages Blencowexri.beneNo ratings yet

- Push-Pull Valve Amp DesignDocument4 pagesPush-Pull Valve Amp DesignDiego García MedinaNo ratings yet

- Preamp PDFDocument9 pagesPreamp PDFjohandry84No ratings yet

- Negative Feedback Tone Control Circuit Provides Independent Bass and Treble AdjustmentDocument7 pagesNegative Feedback Tone Control Circuit Provides Independent Bass and Treble AdjustmentmichaelbrendenNo ratings yet

- FET Amp With Valve Sound by B. KainkaDocument5 pagesFET Amp With Valve Sound by B. Kainkat_ca100% (4)

- Tim Mellow 25w OTL Tube Amplifier PDFDocument6 pagesTim Mellow 25w OTL Tube Amplifier PDFpravin jadav100% (3)

- Transistor Driver For Valve AmplifiersDocument5 pagesTransistor Driver For Valve Amplifiersstefan100% (2)

- Design of Tube Amplifiers in LT SpiceDocument33 pagesDesign of Tube Amplifiers in LT SpiceGaetanoCirillo100% (1)

- The Ultra-Linear Power Amplifier - An Adventure Between Triode and Pentode - Rudolf Moers (About 2010)Document88 pagesThe Ultra-Linear Power Amplifier - An Adventure Between Triode and Pentode - Rudolf Moers (About 2010)jimmy67musicNo ratings yet

- Tube Amps MathDocument47 pagesTube Amps MathДавид МаћејNo ratings yet

- Push-Pull Amplifier Transformers PDFDocument3 pagesPush-Pull Amplifier Transformers PDFjimmy67music100% (1)

- El34 Parallel Single Ended SchematicDocument4 pagesEl34 Parallel Single Ended SchematicFrancisco100% (1)

- The Triode ValveDocument6 pagesThe Triode ValveAhmedNo ratings yet

- Acrosound Transformers 1955 CatalogDocument16 pagesAcrosound Transformers 1955 CatalogKelvin Kwong100% (1)

- Tone Stack Reference DesignDocument35 pagesTone Stack Reference DesignRicardo Costa RosaNo ratings yet

- Modern High End Valve Amplifiers by Menno Van Der Veen - Vacuum Tube - AmplifierDocument8 pagesModern High End Valve Amplifiers by Menno Van Der Veen - Vacuum Tube - AmplifierMiare RetardareNo ratings yet

- Basic Principles of Vacuum Tube Logic CircuitsDocument191 pagesBasic Principles of Vacuum Tube Logic Circuitswbblair3100% (5)

- Elektor PPP 2001.májusDocument11 pagesElektor PPP 2001.májussoyagurt100% (1)

- wcp32 - Vacuum Tube Tester Final PresentationDocument30 pageswcp32 - Vacuum Tube Tester Final Presentationapi-343159889No ratings yet

- Single Ended vs. Push Pull (Parts 1&2) - Eddie VaughnDocument18 pagesSingle Ended vs. Push Pull (Parts 1&2) - Eddie Vaughnjimmy67music100% (1)

- Common Gain StageDocument37 pagesCommon Gain StageVincent ClaesNo ratings yet

- Basic Tube Power SuppliesDocument21 pagesBasic Tube Power SuppliesElaine MoratoNo ratings yet

- Compact Hi-Fi Power AmplifierDocument2 pagesCompact Hi-Fi Power Amplifiernaval_architectNo ratings yet

- Measuring an Audio Transformer's Electrical CharacteristicsDocument4 pagesMeasuring an Audio Transformer's Electrical Characteristicsjimmy67music100% (2)

- Selecting A Valve Audio Output TransformerDocument8 pagesSelecting A Valve Audio Output Transformerjimmy67musicNo ratings yet

- Modern High End Valve Amplifiers by Menno Van Der Veen PDFDocument254 pagesModern High End Valve Amplifiers by Menno Van Der Veen PDFjano2358j100% (2)

- Hybrid Feedbacks For Power Amplifiers (Acrosound Ultra-Linear II) - Herbert I. Keroes (Audio, Sep 1958)Document6 pagesHybrid Feedbacks For Power Amplifiers (Acrosound Ultra-Linear II) - Herbert I. Keroes (Audio, Sep 1958)jimmy67musicNo ratings yet

- Class A Tube Buffer Using 6DJ8-6922-6N11-1Document6 pagesClass A Tube Buffer Using 6DJ8-6922-6N11-1Huynh Hai Son100% (1)

- Morgan Jones Building Valve AmplifiersDocument3 pagesMorgan Jones Building Valve AmplifiersSimon Uka0% (2)

- 100 Amplifiers - Part 3, 1955 - 59 - Lilienthal EngineeringDocument58 pages100 Amplifiers - Part 3, 1955 - 59 - Lilienthal Engineeringgheo23No ratings yet

- Modifying Guitar Amp Preamp CircuitryDocument9 pagesModifying Guitar Amp Preamp CircuitryRui Oliveira100% (2)

- Must Have Tube Electronics BooksDocument3 pagesMust Have Tube Electronics BooksCarlos Molina100% (2)

- Tube Amp TheoryDocument15 pagesTube Amp TheoryNemanja100% (1)

- Valve & Amplifier Design, EL34 (6CA7) Data, Mullard ValvesDocument17 pagesValve & Amplifier Design, EL34 (6CA7) Data, Mullard ValvesValve DataNo ratings yet

- Analisis de Circuito Big MuffDocument10 pagesAnalisis de Circuito Big MuffNacho ConsolaniNo ratings yet

- Amp ScrapbookDocument10 pagesAmp Scrapbookarturxox1zNo ratings yet

- Tube Terminology For DummiesDocument4 pagesTube Terminology For DummiesAdrian BacilioNo ratings yet

- GGG Bsiab2 ModsDocument1 pageGGG Bsiab2 ModsgustavoNo ratings yet

- Servo BiasDocument3 pagesServo Biasdcastrelos2000No ratings yet

- Mu Stage Philosophy: Alan KimmelDocument10 pagesMu Stage Philosophy: Alan KimmelbigpriapNo ratings yet

- Tone ControlsDocument24 pagesTone Controlsdebass3No ratings yet

- 6AS7 PP Elektor PDFDocument7 pages6AS7 PP Elektor PDFmundomusicalmeriaNo ratings yet

- 5 Watt Class-A Audio Amplifier Circuit Circuit Diagram and InstructionsDocument2 pages5 Watt Class-A Audio Amplifier Circuit Circuit Diagram and InstructionszeljkokerumNo ratings yet

- 12AX7 6V6 Single Ended Class A Tube Amplifier Design and ConstructionDocument11 pages12AX7 6V6 Single Ended Class A Tube Amplifier Design and ConstructionOz Heat86% (7)

- EH Small Stone Phaser Issue J DIY ThereminDocument141 pagesEH Small Stone Phaser Issue J DIY ThereminAnonymous vKD3FG6RkNo ratings yet

- Rca - Hifi Tube Amp CircuitsDocument28 pagesRca - Hifi Tube Amp Circuitsretkitter100% (2)

- Circuit Guide Vemuram Jan RayDocument1 pageCircuit Guide Vemuram Jan Raybenoi31No ratings yet

- The TAB Guide to Vacuum Tube Audio: Understanding and Building Tube AmpsFrom EverandThe TAB Guide to Vacuum Tube Audio: Understanding and Building Tube AmpsNo ratings yet

- AsdasdDocument1 pageAsdasdt_caNo ratings yet

- Blank Page NoticeDocument1 pageBlank Page Noticet_caNo ratings yet

- FET Amp With Valve Sound by B. KainkaDocument5 pagesFET Amp With Valve Sound by B. Kainkat_ca100% (4)

- Negative Feedback Tone Control Circuit Provides Independent Bass and Treble AdjustmentDocument7 pagesNegative Feedback Tone Control Circuit Provides Independent Bass and Treble AdjustmentmichaelbrendenNo ratings yet

- Punch For Portables: AmplifierDocument3 pagesPunch For Portables: Amplifiert_caNo ratings yet

- NotblankDocument1 pageNotblankt_caNo ratings yet

- Champion 600 SchematicDocument2 pagesChampion 600 Schematict_caNo ratings yet

- The Anode Follower by Charles P. BoegliDocument4 pagesThe Anode Follower by Charles P. Boeglit_caNo ratings yet

- NotblankDocument1 pageNotblankt_caNo ratings yet

- 0.5, ... 4 Push-Pull AmplifiersDocument3 pages0.5, ... 4 Push-Pull Amplifierst_caNo ratings yet

- Demidovich Problems in Mathematical AnalysisDocument495 pagesDemidovich Problems in Mathematical Analysisjwcstar7985100% (5)

- Transistor Audio and Radio Circuits - Mullard (1 Watt Amplifier)Document4 pagesTransistor Audio and Radio Circuits - Mullard (1 Watt Amplifier)t_caNo ratings yet

- Handbook - Transistor CircuitsDocument2 pagesHandbook - Transistor Circuitst_caNo ratings yet

- NotblankDocument1 pageNotblankt_caNo ratings yet

- Mullard/Deacy AmplifierDocument2 pagesMullard/Deacy Amplifiert_caNo ratings yet

- User Manual YAESU FT 8500 EDocument2 pagesUser Manual YAESU FT 8500 EMaurizio De MarchisNo ratings yet

- Siddaganga Institute of Technology, Tumakuru - 572 103: Usn 1 S I 7EC04Document2 pagesSiddaganga Institute of Technology, Tumakuru - 572 103: Usn 1 S I 7EC04nirikshith pNo ratings yet

- Gabs SSR Maxis - Bar1p1 - Rev ADocument20 pagesGabs SSR Maxis - Bar1p1 - Rev AShashank PrajapatiNo ratings yet

- CIM Course OverviewDocument2 pagesCIM Course OverviewbalakaleesNo ratings yet

- T6M ControllerDocument2 pagesT6M ControllerDenny Rachmad Atthahary50% (2)

- Presentation of DesignDocument31 pagesPresentation of DesignReymar CTabingNo ratings yet

- BTS and Antenna Connection PDFDocument19 pagesBTS and Antenna Connection PDFsurma12No ratings yet

- Microwave Link DesignDocument68 pagesMicrowave Link DesignMatthew CarterNo ratings yet

- Review and Analysis of Microstrip Patch Array Antenna With Different ConfigurationsDocument6 pagesReview and Analysis of Microstrip Patch Array Antenna With Different ConfigurationsysrilathaNo ratings yet

- AUDIO System For Santro Xing GL PlusDocument3 pagesAUDIO System For Santro Xing GL PlusvisvanthNo ratings yet

- Digital Microwave Communication Principles-ZTE PDFDocument113 pagesDigital Microwave Communication Principles-ZTE PDFRahul DeshwalNo ratings yet

- Delta Ia-Cta Cta Um en 20070509 PDFDocument25 pagesDelta Ia-Cta Cta Um en 20070509 PDFWan ShahmisufiNo ratings yet

- AIUB Faculty of Engineering - Analog Electronics Lab Experiment Report on LM311 Precision Comparator and Triangular Wave GeneratorDocument3 pagesAIUB Faculty of Engineering - Analog Electronics Lab Experiment Report on LM311 Precision Comparator and Triangular Wave Generatormrana_56No ratings yet

- Angle / Exponential Modulation Lecture - 1: Dr. M. Venu Gopala Rao, Professor, Dept. of ECE, KL UniversityDocument12 pagesAngle / Exponential Modulation Lecture - 1: Dr. M. Venu Gopala Rao, Professor, Dept. of ECE, KL Universitysurya tejaNo ratings yet

- VSX-820 OperatingInstructions031011 PDFDocument228 pagesVSX-820 OperatingInstructions031011 PDFJulienRoyNo ratings yet

- EHV AC & HVDC TransmissionDocument1 pageEHV AC & HVDC TransmissionRavi SharmaNo ratings yet

- List of Abbreviations in PhotographyDocument3 pagesList of Abbreviations in PhotographyAlokdev Mishra0% (1)

- Marine Radar Safety InstructionsDocument52 pagesMarine Radar Safety InstructionsGonzalo Villalobos SanchezNo ratings yet

- Changing The Operating Frequency of An RF Power Amplifier CircuitDocument5 pagesChanging The Operating Frequency of An RF Power Amplifier CircuitArun KumarNo ratings yet

- Dacapl - DLL, A Capl DLL To Use Iocab With Canalyzer: Author: Status: Customer: Printing DateDocument15 pagesDacapl - DLL, A Capl DLL To Use Iocab With Canalyzer: Author: Status: Customer: Printing DatehdgdhNo ratings yet

- Install and configure DSE334 wiring diagram and instructionsDocument2 pagesInstall and configure DSE334 wiring diagram and instructionsLuisNo ratings yet

- VLSI Technology and DesignDocument2 pagesVLSI Technology and DesignJigar PatelNo ratings yet

- Amphenol - HT4C6318X000 - Specifications SheetDocument2 pagesAmphenol - HT4C6318X000 - Specifications SheetLevin McCall BornNo ratings yet

- Stepper Motor Driver Considerations Common ProblemsDocument12 pagesStepper Motor Driver Considerations Common ProblemsErnesto Salomon Jaldín MendezNo ratings yet

- Avr 5000Document58 pagesAvr 5000Nenugr GrNo ratings yet

- Viewsonic Vx2240w-4 Service ManualDocument53 pagesViewsonic Vx2240w-4 Service Manualpaco37No ratings yet

- Samsung GT-N8000 Galaxy Note 10.1 800 08 Level 3 Repair - Block-, PCB Diagrams, Flow Chart of TroubleshootingDocument56 pagesSamsung GT-N8000 Galaxy Note 10.1 800 08 Level 3 Repair - Block-, PCB Diagrams, Flow Chart of TroubleshootingVictor van Herpt100% (2)

- Grundfosliterature 4347893Document40 pagesGrundfosliterature 4347893antonioNo ratings yet

- Unit 3 Slides PSK - QAMDocument87 pagesUnit 3 Slides PSK - QAMSam JonesNo ratings yet

- User Manual f4mc EsDocument12 pagesUser Manual f4mc Estoni_trs_kiroNo ratings yet