Professional Documents

Culture Documents

ESD With PIC MCU-2009 - P1

Uploaded by

tonybinh2011Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ESD With PIC MCU-2009 - P1

Uploaded by

tonybinh2011Copyright:

Available Formats

05-Apr-11

ESD with PIC MCU Part 1

Chapter 1

A VERY BRIEF HISTORY OF MICROPROCESSORS & MICROCONTROLLERS

05-Apr-11

05-Apr-11

05-Apr-11

Chapter 2 PIC Peripheral Interface Controller

05-Apr-11

A generic microcontroller

10

05-Apr-11

11

Advantages of PIC

It is a RISC (Reduced Instruction Set Computer) design Only thirty seven instructions to remember Its code is extremely efficient, allowing the PIC to run with typically less program memory than its larger competitors. It is low cost, high clock speed

12

05-Apr-11

Harvard Architecture

13

Von-Neumann Architecture

14

05-Apr-11

Complex Instruction Set Computer (CISC)

15

PICs and most Harvard chips are RISC

16

05-Apr-11

Family Core Architectural Differences

17

Family Core Architectural Differences ..

18

05-Apr-11

19

The PIC Family: Program Memory

20

10

05-Apr-11

The PIC Family: Data Memory

21

The PIC Family: Control Registers

22

11

05-Apr-11

The PIC Family: Peripherals

23

PIC Peripherals: Ports (Digital I/O)

24

12

05-Apr-11

Comparison of PIC families

25

Some members of the PIC 16 Series family

26

13

05-Apr-11

Some members of the PIC 16 Series family ..

27

The PIC 16F84A pin connection diagram

28

14

05-Apr-11

PIC16C8X PINOUT DESCRIPTION

29

PIC16C8X PINOUT DESCRIPTION ..

30

15

05-Apr-11

Block diagram of the 16F84A (supplementary labels in shaded boxes added by the author)

31

W Register

32

16

05-Apr-11

The 16F84A Status register

33

The PIC16F84 Status register

Unlike most MCUs, there are no instructions to specifically clear or set a flag, such as sec for SEt Carry (MC6800). However, as the Status register is accessible as a file in the Data store, then any instruction that can alter the contents of a file can potentially change the state of a flag.

34

17

05-Apr-11

16F84A memory features

35

The 16F84A program memory and Stack

36

18

05-Apr-11

Data memory and Special Function Register map of the 16F84A

37

16F84A Configuration Word

38

19

05-Apr-11

The EECON1 Special Function Register (address 88H)

39

Data EEPROM

The PIC16F84 has a blockof 64 bytes of data that does not require power to retain its contents. This non-volatile memory is not part of the (volatile) Data store and is accessed through SPRs as a peripheral device. Any byte can be addressed and then read from or written to via the EEDATA register as addressed by the EEADR register and controlled by the EECON1 and EECON2 control file registers. Data EEPROM has a minimum endurance of 1,000,000 writes and such data is retained for upwards of 40 years. Some typical uses of a non-volatile depository would be to hold the number of pages printed in a laser printer or total miles/kilometers travelled in a car. 40

20

05-Apr-11

EEPROM

To read an EEPROM location, the required address must be placed in EEADR and the RD bit set in EECON1. The data in that memory location is then copied to the EEDATA register and can be read immediately. To write to an EEPROM location, the required data and address must be placed in EEDATA and EEADR respectively. The write process is enabled by the WREN (Write Enable) bit being set high, followed by the bytes 55H followed by AAH being sent to the EECON2 register. The built-in requirement for these codes helps to ensure that accidental writes do not take place, for example on power-up or down. The WR bit is then set high and writing actually commences. The write completion is signalled by the setting of bit EEIF in EECON1.

41

EEPROM Read & Write

42

21

05-Apr-11

Clock oscillator and instruction cycle

43

Microcontroller oscillator generator circuits

44

22

05-Apr-11

Three ways to provide the clock signal to a PIC

45

Pipelining

The combination of the RISC instruction set and the Harvard memory map used by PIC microcontrollers has an added advantage: instructions can be pipelined. Every instruction in a computers program memory has first to be fetched and then executed. In many CPUs these two steps are done one after the other first the CPU fetches and then it executes. If, however, program memory has its own address and data bus, separate from data memory (i.e. a Harvard structure), then there is no reason why a CPU cannot be designed so that while it is executing one instruction, it is already fetching the next. This is called pipelining.

46

23

05-Apr-11

Power-up and Reset

R = 10100 k

In the 16F84A there is a Reset input, MCLR (Master Clear, on pin 4). As long as this is held low, the microcontroller is held in Reset. When it is taken high, program execution starts. If the pin is taken low while the program is running, then program execution stops immediately and the microcontroller is forced back into Reset mode.

47

Some ways to power a PIC

The last one is only for a PIC that is not powering an LED or other high-current load.

48

24

05-Apr-11

The 16F84A on-chip reset circuit

49

Addressing Modes

50

25

05-Apr-11

DIRECT/INDIRECT ADDRESSING

51

Data store memory map.

52

26

05-Apr-11

Direct address mode

Indirect address mode

53

54

27

05-Apr-11

55

PIC18Fxx2 MCU

56

28

05-Apr-11

PIC18Fxx2 Simplified Block Diagram

57

PIC18Fxx2 Memory Organization

58

29

05-Apr-11

PIC18Fxx2 Data Memory Organization

59

PIC18Fxx2 Accessing Data Memory

60

30

05-Apr-11

61

62

31

05-Apr-11

63

PORTA and TRISA Registers

PORTA is a 5-bit wide latch. RA4 is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers) which can configure these pins as output or input. Setting a TRISA bit (=1) will make the corresponding PORTA pin an input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a TRISA bit (=0) will make the corresponding PORTA pin an output, i.e., put the contents of the output latch on the selected pin. Reading the PORTA register reads the status of the pins whereas writing to it will write to the port latch. All write operations are readmodify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch. The RA4 pin is multiplexed with the TMR0 clock input.

64

32

05-Apr-11

PORTA and TRISA Registers

65

Logic circuit diagram for pins RA0 to RA3

66

33

05-Apr-11

PORTB and TRISB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. A '1' on any bit in the TRISB register puts the corresponding output driver in a hi-impedance mode. A '0' on any bit in the TRISB register puts the contents of the output latch on the selected pin(s). Each of the PORTB pins have a weak internal pull-up. A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (OPTION_REG<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset. Four of PORTBs pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The pins value in input mode are compared with the old value latched on the last read of PORTB. The mismatch outputs of the pins are ORed 67 together to generate the RB port change interrupt.

68

34

05-Apr-11

69

Parallel input/output with PORTA & PROTB

70

35

You might also like

- Application of The Fractional Fourier TransformDocument47 pagesApplication of The Fractional Fourier Transformtonybinh2011No ratings yet

- Digital Modulation and Mobile RadioDocument15 pagesDigital Modulation and Mobile RadiolongthanxmNo ratings yet

- HSPA SystemsDocument69 pagesHSPA Systemstonybinh2011No ratings yet

- 18F4520Document392 pages18F4520amit_k25No ratings yet

- MPLAB C18 Users Guide 51288jDocument136 pagesMPLAB C18 Users Guide 51288jnvt1No ratings yet

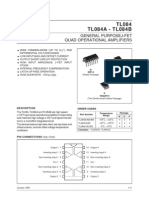

- TL084Document11 pagesTL084Jose Adrian MarquezNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5784)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Machine-dependent and independent assembler featuresDocument66 pagesMachine-dependent and independent assembler featuresUnvss PrasadNo ratings yet

- Ect206-Qp June21Document2 pagesEct206-Qp June21Rajeena VasudevanNo ratings yet

- Canon IR 2018 ManualDocument2 pagesCanon IR 2018 Manuald_k3moyNo ratings yet

- 8086 Microprocessor Interrupts ExplainedDocument4 pages8086 Microprocessor Interrupts ExplainedNonononoNo ratings yet

- End Semester Examination: January, 2022 Digital Electronics and Computer OrganizationDocument3 pagesEnd Semester Examination: January, 2022 Digital Electronics and Computer OrganizationFFFNo ratings yet

- L2 - 8086 Instruction SetDocument27 pagesL2 - 8086 Instruction Setwaheed azizNo ratings yet

- Advanced Vehicle Security System With Theft Control and Accident NotificationDocument70 pagesAdvanced Vehicle Security System With Theft Control and Accident NotificationVaibhav AwasthiNo ratings yet

- Problem Problem-Solving and and Program DesignDocument20 pagesProblem Problem-Solving and and Program DesignRiah TiffanyNo ratings yet

- Computer Organization Questions on CISC and RISC ProcessorsDocument3 pagesComputer Organization Questions on CISC and RISC ProcessorsEmilia KullutweNo ratings yet

- Visit:: Join Telegram To Get Instant Updates: Contact: MAIL: Instagram: Instagram: Whatsapp ShareDocument137 pagesVisit:: Join Telegram To Get Instant Updates: Contact: MAIL: Instagram: Instagram: Whatsapp SharebgbdbdfNo ratings yet

- ICS 2101 Course OutlineDocument6 pagesICS 2101 Course OutlineAlly Sallim0% (1)

- How microprocessor clocks keep everything synchronizedDocument3 pagesHow microprocessor clocks keep everything synchronizedM.Owais AbbasiNo ratings yet

- Coa UNIT-1 NotesDocument11 pagesCoa UNIT-1 NotesHarshitha KANKANALANo ratings yet

- ETI Unit 2 MCQDocument25 pagesETI Unit 2 MCQPooja AbhangNo ratings yet

- Cs-II Year BlownUp Syllabus2019-20Document39 pagesCs-II Year BlownUp Syllabus2019-20Kuldeep SinghNo ratings yet

- ADDRESSING MODES 8-bit Microprocessor Addressing ModesDocument17 pagesADDRESSING MODES 8-bit Microprocessor Addressing ModesNic JonesNo ratings yet

- VLSI Project PresentationDocument23 pagesVLSI Project PresentationAhmedEssa89No ratings yet

- 1 Introducing Embedded Systems and The MicrocontrollersDocument23 pages1 Introducing Embedded Systems and The Microcontrollersedemsa tvNo ratings yet

- HCS12 Controller-2Document20 pagesHCS12 Controller-2HaxfNo ratings yet

- 9608 s19 QP 31Document16 pages9608 s19 QP 31faizan majidNo ratings yet

- Introduction to Computing Homework GuideDocument3 pagesIntroduction to Computing Homework GuideLuân NguyễnNo ratings yet

- Can Bus MicrocontrollersDocument28 pagesCan Bus MicrocontrollersFrank CollinsNo ratings yet

- HCIA-AI V3.5 Version InstructionsDocument2 pagesHCIA-AI V3.5 Version InstructionsEsraa AliNo ratings yet

- Examples of Machine Language Instruction SetDocument10 pagesExamples of Machine Language Instruction Setعبدالرحيم اودينNo ratings yet

- Adding 16-bit Hexadecimal Numbers with CarryDocument4 pagesAdding 16-bit Hexadecimal Numbers with CarrySudhanshu ShekharNo ratings yet

- CSA - Chapter 1Document39 pagesCSA - Chapter 1Nikita vermaNo ratings yet

- Emulate Rslogix5000Document60 pagesEmulate Rslogix5000simplementemoiNo ratings yet

- Beta Hardware CPU DesignDocument13 pagesBeta Hardware CPU DesignBrian PaciaNo ratings yet

- Lecture 02 Introduction To ARM7 ProcessorDocument29 pagesLecture 02 Introduction To ARM7 ProcessorDhruv GuptaNo ratings yet

- Changing Trends in Computer ArchitectureDocument13 pagesChanging Trends in Computer ArchitectureFiromsa Osman BuniseNo ratings yet