Professional Documents

Culture Documents

Cmos01 1up

Uploaded by

Kritika NimeshOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cmos01 1up

Uploaded by

Kritika NimeshCopyright:

Available Formats

ECE 733 Class Notes

Digital Circuit Design CMOS Basics

Dr. Paul D. Franzon Outline

1. 2. 3. 4. MOSFETs Parasitics Basic Circuits Analytic circuit analysis

References

Dally & Poulton, Chapters 4, 12.1 Kang & Leblecici, Chs 3-7

2003, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

MOS Transistors

N-channel Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET): Simplest Equivalent Circuit:

Voltage controlled switch Majority carrier gate

Structure:

Designer determines length and width Nodes: G, S, B, D

Materials

Gate : Polysilicon Drain, Source : diffused silicon

2003, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

Operation

Gate Voltage modulates channel and determines current.

(a) (b) Resistive (linear) region : (c) Saturation region :

I DS

W 2 = nCox ((VGS VT )VDS VDS / 2) L

I DS

kn W (VGS VT ) 2 = 2 L

Cox = Gate capacitance per unit area (r0/tox) kn = nCox = Process transconductance (A/V2) n = electron mobility n = kn(W/L) = device transconductance VT = Threshold (turn-on) voltage

3

2003, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

Gate Design

Add pMOS FET to deliver complementary FETs (CMOS) Negative gate voltage turns gate on Majority carriers = holes

p 0.3 0.5 n

Entire Process: n Well process Parasitic PNP bipolar transistor Diode PNPN SCR

2003, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

Other Effects

Channel-length modulation Depletion region around pn junction becomes significant part of channel length More important for short-channel devices Determines slope in saturation region Body Effect Threshold voltage changes with VSB Velocity Saturation I stops increasing with field (VDS) at high VDS=Vsat Enters saturation for lower VDS Sub-Threshold Conduction VDS lowers barrier to conduction Important in Dynamic Circuits

2003, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

Typical I-V Curves

Saturation (Vsat=1V)

Channel Length Modulation (=0.1)

p<n

2003, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

Other Effects

Short Channel Effects Channel length shortening

Leff < Ldrawn Velocity Saturation decreases VDS(linear-sat) and IDS(sat)

Mobility decreases with increasing VGS Threshold volage reduced due to increased relative size of depletion region Hot Carrier Effects High E fields can inject hot electrons into gate oxide, causing damage and degrading transconductance

2003, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

Sample Parameters

2003, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

Device Parasitics

Important in determining performance

Gate Capacitance:

Drops around VT

Thin-Ox capacitor

CGS dominates

Miller effect issue X = VDS/(VGS-VT)

2003, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html 9

ECE 733 Class Notes

Other Parastitics

CSB and CDB: Reverse biased diode depletion region 0.25 0.5 CG Device Resistances normally small Drain/Source capacitance and parasitic resistances reduced through good layout:

2003, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

10

ECE 733 Class Notes

Sample Models

2003, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

11

ECE 733 Class Notes

Example

Example using these equations (0.35 m technology)

Assume = 0.2 m (gate is 0.4 m as drawn) 0.4 m (2) 0.8 m (4) 0.2 m () 0.6 m (3)

0.8 m (4)

Drain or Source Capacitance = area * CJ + gate-perimeter * CGSO + other-perimeter * CJSW = (0.6*0.2 + 0.8*0.8)E-12 * 5E-4 + 0.6E-6 * 1E-10 + (0.8*3+0.2)E-6 * 2E-10 = 0.38 + 0.06 + 0.52 = 1.5 fF Gate Capacitance (Leff = 0.35 m) = 0.35*0.6E-12*3.9*8.85e-12/70e-10 = 10 Ff (C0=4.9E-3 F/m2)

12

2003, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

ECE 733 Class Notes

Example

VDD = 3.3 V What is the gate on resistance in the linear region?

1 / Ron = I DS / VDS

Ron = 570

= 600E-4 * 4.9E-3 * 0.6/0.35 (3.3 - 0.5)

W = nCox (VGS VT ) L

Ignoring short-channel effects, what is the saturation current?

I DS

kn W (VGS VT ) 2 = 2 L

= 600E-4 * 4.9E-3 *0.6/0.35 * (3.3-0.5)2 = 4 mA

2003, Dr. Paul D. Franzon, www.ece.ncsu.edu/erl/faculty/paulf.html

13

You might also like

- Fundamentals of Fault Current and Grounding in Electrical SystemsFrom EverandFundamentals of Fault Current and Grounding in Electrical SystemsRating: 4 out of 5 stars4/5 (3)

- Grounding & Bonding FundamentalsDocument52 pagesGrounding & Bonding Fundamentalsasuntha50% (2)

- This Set of VLSI Multiple Choice QuestionsDocument20 pagesThis Set of VLSI Multiple Choice QuestionsSujith Mrinal100% (3)

- Electromagnetic Shielding of Cables and ConnectorsDocument30 pagesElectromagnetic Shielding of Cables and ConnectorsA. VillaNo ratings yet

- Practical Methods for Analysis and Design of HV Installation Grounding SystemsFrom EverandPractical Methods for Analysis and Design of HV Installation Grounding SystemsRating: 4.5 out of 5 stars4.5/5 (2)

- Insulation Co-ordination in High-voltage Electric Power SystemsFrom EverandInsulation Co-ordination in High-voltage Electric Power SystemsRating: 4.5 out of 5 stars4.5/5 (5)

- ElectromagneticCompatibilityMethodsAnalysisCircuitsandMeasurementThirdEdition 1 PDFDocument1,151 pagesElectromagneticCompatibilityMethodsAnalysisCircuitsandMeasurementThirdEdition 1 PDFjotaruiz30No ratings yet

- 1992SGSDesignersGuidetoPowerProductsApplicationManual2Ed 1182713547Document1,298 pages1992SGSDesignersGuidetoPowerProductsApplicationManual2Ed 1182713547analog changeNo ratings yet

- Analog Layout Design: Kanazawa University Microelectronics Research Lab. Akio KitagawaDocument48 pagesAnalog Layout Design: Kanazawa University Microelectronics Research Lab. Akio Kitagawaaminkhan83No ratings yet

- MOS Integrated Circuit DesignFrom EverandMOS Integrated Circuit DesignE. WolfendaleNo ratings yet

- BAI Free Spanning PipelineDocument42 pagesBAI Free Spanning PipelineElendu Emmanuel ChigozieNo ratings yet

- KotlerDocument44 pagesKotlerDilip Tirkey100% (11)

- IC Custom Layout DesignDocument10 pagesIC Custom Layout DesignSuresh KumarNo ratings yet

- IMCORP TDR ProcedureDocument9 pagesIMCORP TDR ProcedurelatifNo ratings yet

- Measurement While Drilling: Signal Analysis, Optimization and DesignFrom EverandMeasurement While Drilling: Signal Analysis, Optimization and DesignNo ratings yet

- Why Electric Vehicles Are Better Than Gas CarsDocument12 pagesWhy Electric Vehicles Are Better Than Gas CarsPrateek PandeyNo ratings yet

- (MWJ0306) RF Test Fixture BasicsDocument6 pages(MWJ0306) RF Test Fixture BasicsGhulam MehdiNo ratings yet

- SMART SENSOR Seminar ReportDocument19 pagesSMART SENSOR Seminar ReportSurangma Parashar100% (2)

- Part 4Document33 pagesPart 4bhushanchittaragiNo ratings yet

- VLSI Design Margin and Reliability ScalingDocument17 pagesVLSI Design Margin and Reliability ScalingRapolu SushmaNo ratings yet

- Trends in IC TechnologyDocument26 pagesTrends in IC Technologyhale_209031335No ratings yet

- Interconnect-Trns Line TerminationDocument84 pagesInterconnect-Trns Line TerminationMohammad JoharNo ratings yet

- Lecture17 4Document5 pagesLecture17 4tekellamerZ aka tekellamerNo ratings yet

- VLSI CAT2 SolvedDocument13 pagesVLSI CAT2 SolvedTrinayan PathakNo ratings yet

- Flexible PVDF CombsDocument6 pagesFlexible PVDF CombscgbostanNo ratings yet

- 279 E317 PDFDocument6 pages279 E317 PDFJubin JainNo ratings yet

- Novel Decoupling Capacitor Designs For Sub-90nm CMOS TechnologyDocument6 pagesNovel Decoupling Capacitor Designs For Sub-90nm CMOS TechnologyNitin SonuNo ratings yet

- A Report: Verilog-A Implementation of The EKV v2.6 Long and Short Channel MOSFET ModelsDocument43 pagesA Report: Verilog-A Implementation of The EKV v2.6 Long and Short Channel MOSFET ModelsDilan ByteNo ratings yet

- Ring Oscillator Metastable Based Digital Fingerprint CircuitDocument16 pagesRing Oscillator Metastable Based Digital Fingerprint CircuitHimanshu kesarwaniNo ratings yet

- N Channel MOSFET BSIM3 ModelDocument4 pagesN Channel MOSFET BSIM3 ModelKyusang ParkNo ratings yet

- Peter H ChenDocument10 pagesPeter H ChenYunping HuangNo ratings yet

- Filter Design PDFDocument11 pagesFilter Design PDFarunkr1No ratings yet

- Bsim4 ManualDocument168 pagesBsim4 ManualRafael Della GiustinaNo ratings yet

- Ec6601 Vlsi QBW (R2013)Document20 pagesEc6601 Vlsi QBW (R2013)Bharath PonNo ratings yet

- On Chip VariationDocument4 pagesOn Chip VariationsarvoscribNo ratings yet

- Gate Oxide Leakage Current Analysis and Reduction For VLSI CircuitsDocument12 pagesGate Oxide Leakage Current Analysis and Reduction For VLSI CircuitsNK NKNo ratings yet

- 2011 Scaling CPLDocument5 pages2011 Scaling CPLankushwreNo ratings yet

- Low-Power Circuits Using Dynamic Threshold DevicesDocument5 pagesLow-Power Circuits Using Dynamic Threshold DevicesGiang Nguyễn VănNo ratings yet

- DecapDocument6 pagesDecapayyannagaraga1No ratings yet

- A Study On Multi Material Gate All Around SOI MOSFETDocument5 pagesA Study On Multi Material Gate All Around SOI MOSFETeditor_ijtelNo ratings yet

- BSIM4 ManualDocument188 pagesBSIM4 ManualAnitha MariappanNo ratings yet

- Design and Analysis of Phase Locked Loop in 90mm CmosDocument7 pagesDesign and Analysis of Phase Locked Loop in 90mm CmosabhishekNo ratings yet

- Kds Tutorial GIS SubstationDocument357 pagesKds Tutorial GIS SubstationmkbpgcilNo ratings yet

- VLF 50-0-1Hz ComparisionDocument10 pagesVLF 50-0-1Hz ComparisionnrasoolNo ratings yet

- A Fully Integrated CMOS DCS-1800 Frequency Synthesizer: Jan Craninckx,, and Michel S. J. SteyaertDocument12 pagesA Fully Integrated CMOS DCS-1800 Frequency Synthesizer: Jan Craninckx,, and Michel S. J. SteyaertgopipatNo ratings yet

- EuroCorr 2011 Paper No 1022 Harald OsvollDocument25 pagesEuroCorr 2011 Paper No 1022 Harald OsvollHedi Ben MohamedNo ratings yet

- Process Variations Impact VLSI Design PerformanceDocument8 pagesProcess Variations Impact VLSI Design PerformanceMunish JainNo ratings yet

- A New Low Leakage Power Flip-Flop Based On RatioedDocument7 pagesA New Low Leakage Power Flip-Flop Based On RatioedxmzbiskydemrfuvsjvNo ratings yet

- Engineering Diagnostic Tools EEEM 513 - (5) Transformer Advanced Electrical DiagnosticDocument58 pagesEngineering Diagnostic Tools EEEM 513 - (5) Transformer Advanced Electrical DiagnostichuazadNo ratings yet

- S.S. Yu Et Al - HIF Driver Point DesignsDocument30 pagesS.S. Yu Et Al - HIF Driver Point DesignsCola7890No ratings yet

- Bsim330 ManualDocument200 pagesBsim330 ManualThanh RamseyNo ratings yet

- Low Power Design and Simulation of 7T SRAM Cell Using Various Circuit TechniquesDocument6 pagesLow Power Design and Simulation of 7T SRAM Cell Using Various Circuit TechniquesseventhsensegroupNo ratings yet

- Interpretation of Dielectric Spectroscopy Results in Time and Frequency Domains For Power CablesDocument7 pagesInterpretation of Dielectric Spectroscopy Results in Time and Frequency Domains For Power CablesOrlandoNo ratings yet

- ECEN689: Special Topics in High-Speed Links Circuits and Systems Spring 2011Document28 pagesECEN689: Special Topics in High-Speed Links Circuits and Systems Spring 2011api-127299018No ratings yet

- Appnd ADocument17 pagesAppnd Afrostyfoley100% (1)

- CMOS logic gate design for enhanced aging robustnessDocument5 pagesCMOS logic gate design for enhanced aging robustnessAdip ChyNo ratings yet

- Koneru Lakshmaiah Education Foundation: Department of Electronics and Communication EngineeringDocument11 pagesKoneru Lakshmaiah Education Foundation: Department of Electronics and Communication EngineeringLakshmi JagupillaNo ratings yet

- SONETDocument60 pagesSONETECE DEPARTMENTNo ratings yet

- Internal Partial Discharge in Cavity of Polyurethane: SciencedirectDocument5 pagesInternal Partial Discharge in Cavity of Polyurethane: SciencedirectRavi KankaleNo ratings yet

- Technical Note - Shortening Calculation of PT Floor SystemsDocument13 pagesTechnical Note - Shortening Calculation of PT Floor SystemsHuy Nguyen VanNo ratings yet

- Millimeter-Wave Digitally Intensive Frequency Generation in CMOSFrom EverandMillimeter-Wave Digitally Intensive Frequency Generation in CMOSNo ratings yet

- 2004 CrosonGomesMcGinnNoth PDFDocument34 pages2004 CrosonGomesMcGinnNoth PDFKritika NimeshNo ratings yet

- Tandberg RX1290 v8Document3 pagesTandberg RX1290 v8Kritika Nimesh100% (1)

- Workplace LearningDocument16 pagesWorkplace LearningKritika NimeshNo ratings yet

- Mealy Moore MachinesDocument5 pagesMealy Moore MachinesKritika NimeshNo ratings yet

- How GPS Works: A Concise Guide to the Global Positioning SystemDocument35 pagesHow GPS Works: A Concise Guide to the Global Positioning SystemKritika NimeshNo ratings yet

- FSM TutorialDocument4 pagesFSM Tutorialrajishkrishna88No ratings yet

- Simetrix ManualDocument419 pagesSimetrix ManualLuke Austin VargasNo ratings yet

- Power ElectronicsDocument86 pagesPower ElectronicsMuhammad Ali Johar100% (1)

- DE LA SALLE UNIVERSITY EXAM REVIEWDocument6 pagesDE LA SALLE UNIVERSITY EXAM REVIEWSahara MalabananNo ratings yet

- 13 Circuit Descriptions: 13-1 Overall Block Structure Power TreeDocument8 pages13 Circuit Descriptions: 13-1 Overall Block Structure Power TreeJoseni FigueiredoNo ratings yet

- Resonant Converter Topologies: Application NoteDocument5 pagesResonant Converter Topologies: Application Notesatyam swarup dubeyNo ratings yet

- M.tech Thesis VarunDocument78 pagesM.tech Thesis VarunAppala Naidu GottapuNo ratings yet

- 1.7 KW 2 Single Channel Class D Audio Power Amplifier Using The IRS2092S and IRFB4227 1422001499Document39 pages1.7 KW 2 Single Channel Class D Audio Power Amplifier Using The IRS2092S and IRFB4227 1422001499Viorel Aldea0% (1)

- A Low Phase Noise Voltage Controlled Ring Oscillator Using Subharmonic Injection Locking Mechanism in 90nm CMOS ProcessDocument7 pagesA Low Phase Noise Voltage Controlled Ring Oscillator Using Subharmonic Injection Locking Mechanism in 90nm CMOS ProcessManoj BoraNo ratings yet

- Ee 211 Chapter 3Document19 pagesEe 211 Chapter 3RickNo ratings yet

- Comparisons of BJT and MOSFETDocument7 pagesComparisons of BJT and MOSFETFrank WanderiNo ratings yet

- 1EDN7550 and 1EDN8550: Feature ListDocument21 pages1EDN7550 and 1EDN8550: Feature ListЕвгений ИвановNo ratings yet

- FDD8424H-92711 - Transistor de Efeito de CampoDocument12 pagesFDD8424H-92711 - Transistor de Efeito de CampoTiago LeonhardtNo ratings yet

- CPEDRF - Modeling Logic Gates in LTSpiceDocument7 pagesCPEDRF - Modeling Logic Gates in LTSpiceRodolfo Jr DoromalNo ratings yet

- Physical Handout NotesDocument121 pagesPhysical Handout NotesJimmy MachariaNo ratings yet

- Design and Implementation of 4-Bit Alu Using Finfet TechnologyDocument12 pagesDesign and Implementation of 4-Bit Alu Using Finfet TechnologyDinesh Kumar J RNo ratings yet

- 3+1 Voltage Regulator For Imvp-7/Vr12™ Cpus: FeaturesDocument42 pages3+1 Voltage Regulator For Imvp-7/Vr12™ Cpus: FeaturesMagarishi TechNo ratings yet

- PSIM ManualDocument154 pagesPSIM ManualXtian F. PereaNo ratings yet

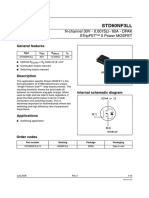

- Std60Nf3Ll: N-Channel 30V - 0.0075 - 60A - Dpak Stripfet™ Ii Power MosfetDocument13 pagesStd60Nf3Ll: N-Channel 30V - 0.0075 - 60A - Dpak Stripfet™ Ii Power MosfetFransiskus Galih SumartonoNo ratings yet

- FetDocument132 pagesFetHafidz Pratama100% (1)

- Lesson Plan-VLSI DesignDocument6 pagesLesson Plan-VLSI DesignChetan GowdaNo ratings yet

- M 136Document6 pagesM 136vinoth kumarNo ratings yet

- LTC8205ADocument8 pagesLTC8205AChispi LoudenNo ratings yet

- ST Micro Interview Questions For Circuit DesignDocument10 pagesST Micro Interview Questions For Circuit DesignvenegallaraghuNo ratings yet

- VLSI DesignDocument31 pagesVLSI DesignSenthil GanesanNo ratings yet

- 607 Lect 8 Bulk Driven Circuits 2009Document57 pages607 Lect 8 Bulk Driven Circuits 2009Avinash B RajNo ratings yet

- Gateway TutorialDocument7 pagesGateway TutorialSubir MaityNo ratings yet