Professional Documents

Culture Documents

LVDS-18 User Guide Summary

Uploaded by

crnisaleOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

LVDS-18 User Guide Summary

Uploaded by

crnisaleCopyright:

Available Formats

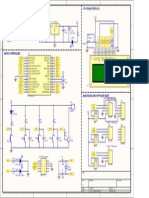

LVDS-18: USER GUIDE Ver 0.

1

The LVDS-18 are designed to work with ICP JUKI-710,JUKI-740E,JUKI-745E, NOVA-600,NOVA-7896,NOVA-3710,NOVA-7895 ..etc. single board computers 50-pin LCD interface. The LVDS-18 supports the TFT LCD which equipped the 1 pixels/clock for LVDS interface.

1.

Connector description

J4: Power Connector for backlight inverter (JST:B8B-PH-K or equivalent) 1 2 3 4 5 6 7 8 +12V +12V +12V FPVEE/ENABKL NC GND GND GND

FPVEE/ENABKL: Power sequencing control for panel bias voltage FPVEE may also be configured as ENABKL JP2: LVDS CONNECTOR (Hirose DF14A-20P-1.25H) 1 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 PLCD PLCD GND GND TX0TX0+ GND TX1TX1+ GND TX2TX2+ GND TXCTXC+ GND TX3TX3+ GND GND

Warning!

Notice the pin order when cabling. Improper sequence might damage the LCD!

20

PLCD: Power supply from CPU board which can be configured as +5V or +3V supply. Please refer to the CPU board manual.

2.

Jumper setting

J2:

1 2

1 2

PDATA SHFCLK

J2 Open : for TFT application (default)

3.

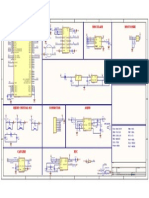

Signal Description: 24bit color TFT a. LVDS interface

24bit color routing table of

SAMSUNG TFT-LCD Model No.: LTM150XH-L04 CHI MEI TFT-LCD Model No.:M150X3-L01

P16(R0) P17(R1) P18(R2) P19(R3) P20(R4) P21(R5) P8(G0) P9(G1) P10(G2) P11(G3) P12(G4) P13(G5) P0 (B0) P1 (B1) DCLK P2(B2) P3(B3) P4(B4) P5(B5) LP FLM M P22(R6) P23(R7) P14(G6) P15(G7) P6(B6) P7(B7) Reserved

TX0TX0+

TX2TX2+

TX1TX1+

TX3TX3+

TXCTXC+ 2

b. Reference J5: Panel Signal from CPU board (reference)

Signal Name VPCLK P34 1

Pin # 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 45 47 49

Pin # 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 46 48 50

Signal Name P33 P31 P32 P28 P27 P26 P21 P22 P20 P18 P14 P12 P11 P10 PLCD P8 P6 P5 P1 P0 ENABKL FLM LP GND +12V

P35 P30 P29 P25 P24 P23 P16 P17 P19 P13 P15 P7 PLCD P9 P4 50 P3 P2 M SHFCLK FPVDD FPVEE GND +12V

49

SHFCLK: Shift Clock. Pixel clock for flat panel data. FLM: First Line Marker.Flat Panel equivalent of VSYNC. LP: Latch Pulse(may also be called CL1). M: M signal for panel AC drive control (may also be called ACDCLK). Enablk: power sequencing control for enabling the backlight FPVEE: Power sequencing control for panel bias voltage VEE. May also be configured as ENABKL

Panel interface reference table(C&T65555) A

Pin# Pin Name 40 P0 38 P1 37 P2 35 P3 33 P4 36 P5 34 P6 27 P7 32 P8 31 P9 28 P10 26 P11 24 P12 23 P13 22 P14 25 P15 17 P16 19 P17 20 P18 21 P19 18 P20 14 P21 16 P22 15 P23 13 P24 11 P25 12 P26 10 P27 8 P28 9 P29 7 P30 4 P31 6 P32 2 P33 3 P34 5 P35 41 SHFCLK Pixels/Clock 8 : Mono SS 8-bit8-bit P0 P1 P2 P3 P4 P5 P6 P7 Mono DD 8 bit UD3 UD2 UD1 UD0 LD3 LD2 LD1 LD0 Mono DD 16 bit UD7 UD6 UD5 UD4 UD3 UD2 UD1 UD0 LD7 LD6 LD5 LD4 LD3 LD2 LD1 LD0 Color TFT 9/12/16 bit B0 B1 B2 B3 B4 G0 G1 G2 G3 G4 G5 R0 R1 R2 R3 R4 Color TFT 24bit 18bit B0 B1 B2 B3 B4 B5 B6 B7 G0 G1 G2 G3 G4 G5 G6 G7 R0 R1 R2 R3 R4 R5 R6 R7

B0 B1 B2 B3 B4 B5 G0 G1 G2 G3 G4 G5 R0 R1 R2 R3 R4 R5

SHFCLK 8 F: First

SHFCLK 16 S: Second

SHFCLK 1 U: Upper

SHFCLK 1 L: Lower

SHFCLK 1

R: Red G: Green B: Blue FLM : first line marker

SHFCLK: Shift Clock. Pixel clock for panel data LP : latch pulse (may also be called CL1) M: M signal for panel AC drive control (may also be called ACDCLK) Enablk: power sequencing control for enabling the backlight

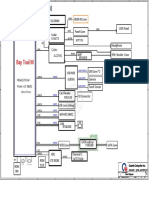

Panel interface reference table(C&T65555) B

Pin# Pin Name 40 P0 38 P1 37 P2 35 P3 33 P4 36 P5 34 P6 27 P7 32 P8 31 P9 28 P10 26 P11 24 P12 23 P13 22 P14 25 P15 17 P16 19 P17 20 P18 21 P19 18 P20 14 P21 16 P22 15 P23 13 P24 11 P25 12 P26 10 P27 8 P28 9 P29 7 P30 4 P31 6 P32 2 P33 3 P34 5 P35 41 SHFCLK Pixels/Clock: Color TFT 36-bit FB0 FB1 FB2 FB3 FB4 FB5 SB0 SB1 SB2 SB3 SB4 SB5 FG0 FG1 FG2 FG3 FG4 FG5 SG0 SG1 SG2 SG3 SG4 SG5 FR0 FR1 FR2 FR3 FR4 FR5 SR0 SR1 SR2 SR3 SR4 SR5 SHFCLK 2 Color TFT HR 18/24 bit FB0 FB1 FB2 FB3 SB0 SB1 SB2 SB3 FG0 FG1 FG2 FG3 SG0 SG1 SG2 SG3 FR0 FR1 FR2 FR3 SR0 SR1 SR2 SR3 Color STN SS 8-bit (46p) R1 B1 G2 R3 B3 G4 R5 B5 Color STN SS 16-bit (46p) R1 G1 B1 R2 G2 B2 R3 G3 B3 R4 G4 B4 R5 G5 B5 R6 Color STN DD 8-bit (46p) UR1 UG1 UB1 UR2 LR1 LG1 LB1 LR2 Color STN DD 16-bit (46p) UR0 UG0 UBO UR1 LR0 LG0 LB0 LR1 UG1 UB1 UR2 UG2 LG1 LB1 LR2 LG2 Color STN DD 24-bit UR0 UG0 UB0 LR0 LG0 LB0 UR1 UG1 UB1 LR1 LG1 LB1 UR2 UG2 UB2 LR2 LG2 LB2 UR3 UG3 UB3 LR3 LG3 LB3

SHFCLK 2 F: First

SHFCLK 2-2/3

SHFCLK 5-1/3

SHFCLK 2-2/3

SHFCLK 5-1/3

SHFCLK 8

R: Red G: Green B: Blue FLM : first line marker

S: Second

U: Upper

L: Lower

SHFCLK: Shift Clock. Pixel clock for panel data LP : latch pulse (may also be called CL1) M: M signal for panel AC drive control (may also be called ACDCLK) Enablk: power sequencing control for enabling the backlight

You might also like

- LVDS-02-USER-GUIDEDocument3 pagesLVDS-02-USER-GUIDEn_hakimNo ratings yet

- Toshiba TV LCD Training 32wl36pDocument61 pagesToshiba TV LCD Training 32wl36pLuis RugNo ratings yet

- Piq102 Piq103 Piq103 Piq102: Pir702 Pir701 Pir1002 Pir702Document7 pagesPiq102 Piq103 Piq103 Piq102: Pir702 Pir701 Pir1002 Pir702xacdinhdiNo ratings yet

- 3pi SchematicDocument1 page3pi SchematicKevin JeromeNo ratings yet

- Stm32f4discovery LCD UserguideDocument6 pagesStm32f4discovery LCD UserguideAmil CuryNo ratings yet

- TV Solutions Guide Articles 2006jul PDF ToshibaDocument23 pagesTV Solutions Guide Articles 2006jul PDF ToshibasontuyeNo ratings yet

- Rca rs2625Document5 pagesRca rs2625luis urrozNo ratings yet

- LCD Display: Power Supply 2 16 Character LCDDocument1 pageLCD Display: Power Supply 2 16 Character LCDSyahmi Hasan100% (1)

- MJoy 16 C 1Document2 pagesMJoy 16 C 1Edilberto SantosNo ratings yet

- Kodak Dryview 6800 LASER IMAGER System Block DiagramDocument4 pagesKodak Dryview 6800 LASER IMAGER System Block DiagramDaiane SantosNo ratings yet

- Sanyo 17mb22 TrainingDocument16 pagesSanyo 17mb22 TrainingTony BinghamNo ratings yet

- Daewoo DPC 7900Document39 pagesDaewoo DPC 7900dmst622No ratings yet

- Thomson Chassis Lcd12b 20lb120s4Document18 pagesThomson Chassis Lcd12b 20lb120s4vascoalmNo ratings yet

- HP 1X Train PackDocument34 pagesHP 1X Train Packdann222No ratings yet

- Schematic DiagramDocument13 pagesSchematic DiagramSas WajiNo ratings yet

- Mjoy AVR USB JoystickDocument9 pagesMjoy AVR USB JoysticklakilukilukNo ratings yet

- Schaltplan CPU Wheelie-II v2.7Document2 pagesSchaltplan CPU Wheelie-II v2.7Stacy MorrowNo ratings yet

- Sony Aa CDX-CA680X CDX-L580XDocument8 pagesSony Aa CDX-CA680X CDX-L580XБорис ДидорукNo ratings yet

- Sim BP FpgaDocument2 pagesSim BP Fpgailker_osmanNo ratings yet

- SRT 4155 and SRT4355 - ServicemanualDocument40 pagesSRT 4155 and SRT4355 - ServicemanualMohamed MakiNo ratings yet

- Panel AU Optronics B133XN03 V3 0 (DS)Document21 pagesPanel AU Optronics B133XN03 V3 0 (DS)เกียรติศักดิ์ ภูมิลาNo ratings yet

- Wistron 91.4U301.001 SchematicDocument44 pagesWistron 91.4U301.001 SchematicAbubakar Siddiq HolmNo ratings yet

- Monitor Sony Cpd-101vsDocument28 pagesMonitor Sony Cpd-101vspepitito22No ratings yet

- Dell Studio XPS 1645 Quanta RM5 Calpella Intel Discrete RevD3ADocument59 pagesDell Studio XPS 1645 Quanta RM5 Calpella Intel Discrete RevD3AHans PeterNo ratings yet

- PE4H VER24 SchematicDocument2 pagesPE4H VER24 SchematicB Huerta MuñozNo ratings yet

- Pololu Wixel Schematic DiagramDocument1 pagePololu Wixel Schematic DiagramGustavo CervantesNo ratings yet

- Sony cfd-v10 SMDocument50 pagesSony cfd-v10 SMFerran AlfonsoNo ratings yet

- Datasheet Micro M65582AMF-105FPDocument46 pagesDatasheet Micro M65582AMF-105FPsel_mor100% (1)

- SMD Code BookDocument111 pagesSMD Code BookEnzo Auditore50% (2)

- 7-Inch LCD Monitor & DVD Player Specs and TroubleshootingDocument42 pages7-Inch LCD Monitor & DVD Player Specs and TroubleshootingЕвгений СафоновNo ratings yet

- Can Bus SCHDocument1 pageCan Bus SCHhoangdai100% (3)

- Ponyprog Circuit For AVR& PIC16F84Document6 pagesPonyprog Circuit For AVR& PIC16F84tiensinh1No ratings yet

- Sony DVP-NS305 - 310 - 315 - 405 - 410 - 415 PDFDocument47 pagesSony DVP-NS305 - 310 - 315 - 405 - 410 - 415 PDFZbigniew SzaryczNo ratings yet

- Fpga 04 Lab ManualDocument81 pagesFpga 04 Lab Manualkumaragurusakthivel100% (1)

- PROF 7500 V31.2 DVB-S2 Tuner Receiver Box SchematicsDocument3 pagesPROF 7500 V31.2 DVB-S2 Tuner Receiver Box SchematicsavrelecNo ratings yet

- Connecting Ethernet Interface With LPC2000: Rev. 01 - 7 February 2007 Application NoteDocument21 pagesConnecting Ethernet Interface With LPC2000: Rev. 01 - 7 February 2007 Application NoteJorBS57No ratings yet

- Intermarine 23 INCH Monitor DipSwitch SettingDocument2 pagesIntermarine 23 INCH Monitor DipSwitch SettingChristos SavvidisNo ratings yet

- st2 SchematicDocument2 pagesst2 SchematicDaniel Marquez MuroNo ratings yet

- Schematic diagram of DTMF signal generator circuitDocument2 pagesSchematic diagram of DTMF signal generator circuitThắng HoàngNo ratings yet

- Daewoo HC-6120 6220 Home Teather Con DVD Diagramas PCBDocument27 pagesDaewoo HC-6120 6220 Home Teather Con DVD Diagramas PCBJavier Silva AlanisNo ratings yet

- Philips Dvp-3010 SCHDocument17 pagesPhilips Dvp-3010 SCHnike03No ratings yet

- Arduino Mega2560 R3 SchematicDocument1 pageArduino Mega2560 R3 Schematichenriquezrs100% (3)

- Car Monitoring System IPADocument42 pagesCar Monitoring System IPASaleh AlsaqerNo ratings yet

- Swm3 Cpu Schematic PartslistDocument4 pagesSwm3 Cpu Schematic PartslistAriel BecerraNo ratings yet

- Tvar 145Document1 pageTvar 145Marcos PiazzollaNo ratings yet

- Smp8654 Dev Board: 922Reva3ADocument15 pagesSmp8654 Dev Board: 922Reva3AМихаил ГудковNo ratings yet

- CCTV Surveillance: Video Practices and TechnologyFrom EverandCCTV Surveillance: Video Practices and TechnologyRating: 4 out of 5 stars4/5 (1)

- Exploring Arduino: Tools and Techniques for Engineering WizardryFrom EverandExploring Arduino: Tools and Techniques for Engineering WizardryRating: 4.5 out of 5 stars4.5/5 (5)

- Mega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3From EverandMega Drive Architecture: Architecture of Consoles: A Practical Analysis, #3No ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Radio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142From EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual Catalog Numbers: 26-1140, 26-1141, 26-1142No ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINo ratings yet

- AO4916Document8 pagesAO4916crnisaleNo ratings yet

- An 1088Document18 pagesAn 1088crnisaleNo ratings yet

- Pioneer Plasma PDP-502MX - ARP3037Document78 pagesPioneer Plasma PDP-502MX - ARP3037littlem2aNo ratings yet

- L5A Service ManualDocument33 pagesL5A Service ManualradumiraNo ratings yet

- AlfaFiatLancia 19JTD EDC15Document3 pagesAlfaFiatLancia 19JTD EDC15crnisaleNo ratings yet

- Laptop & CCTV 23 November 2017Document1 pageLaptop & CCTV 23 November 2017lanetNo ratings yet

- Q9T4-FP91G-engineering Specification PDFDocument14 pagesQ9T4-FP91G-engineering Specification PDFfarkasediNo ratings yet

- M.2 SATA SSD Qualified Vendor ListDocument1 pageM.2 SATA SSD Qualified Vendor ListDan CooperNo ratings yet

- HP ProBook 650 G1 Inventec 6050A2566401-MB-A03 SchematicsDocument90 pagesHP ProBook 650 G1 Inventec 6050A2566401-MB-A03 SchematicsSiay Blackthorn100% (1)

- Asus X540uv Rev2.0Document64 pagesAsus X540uv Rev2.0George SalinasNo ratings yet

- 250GB 860 PRO 256GB 512GB 1TB 500GB: 860 Evo SSDDocument8 pages250GB 860 PRO 256GB 512GB 1TB 500GB: 860 Evo SSDkolattacNo ratings yet

- 5-1. Wiring DiagramDocument9 pages5-1. Wiring DiagramSlawqo Brakło Mi AtramentuNo ratings yet

- Ata Ide and EideDocument8 pagesAta Ide and EideCarolina CastanedaNo ratings yet

- Item ListDocument1 pageItem ListDiane BacalsoNo ratings yet

- Computer Parts Pricelist IndiaDocument4 pagesComputer Parts Pricelist Indiamanikg_8No ratings yet

- Msi MS1422 PDFDocument45 pagesMsi MS1422 PDFCesar AugustoNo ratings yet

- Hdmi2 Hdmi1: IT6633P IT6633PDocument6 pagesHdmi2 Hdmi1: IT6633P IT6633PJose BonillaNo ratings yet

- SBC-456/456E: Half-Size 486 CPU Card With Flat Panel/CRT SVGA InterfaceDocument98 pagesSBC-456/456E: Half-Size 486 CPU Card With Flat Panel/CRT SVGA Interfacerad_01No ratings yet

- Inspiron 3043 DAQF2AMB6A0 Foxglove MB A00 0328Document47 pagesInspiron 3043 DAQF2AMB6A0 Foxglove MB A00 0328Khánh Gia100% (1)

- Inventory List of Used Office Equipment Advertised on My AccountDocument3 pagesInventory List of Used Office Equipment Advertised on My Accountcaptain animeNo ratings yet

- Cyclone eMMCDocument1 pageCyclone eMMCCesarSNo ratings yet

- Mil STD 681 Color Code ChartDocument1 pageMil STD 681 Color Code ChartKemal YıldırımNo ratings yet

- Input Output Revision QuestionsDocument18 pagesInput Output Revision Questionsdevdan030% (1)

- 001 Bizgram Asia Pricelist January 25aDocument17 pages001 Bizgram Asia Pricelist January 25aArjun KharidehalNo ratings yet

- Interaction Aci ImprimirDocument96 pagesInteraction Aci ImprimirWillygan Pm100% (1)

- Parts of Computer: Output DevicesDocument15 pagesParts of Computer: Output DevicesRamanjotNo ratings yet

- Marvel Catalog V3Document18 pagesMarvel Catalog V3Ray FlorezNo ratings yet

- HDRM OverviewsDocument8 pagesHDRM OverviewsHeri SetyantoNo ratings yet

- Academic Writing CSC134Document7 pagesAcademic Writing CSC134nurain fasihahNo ratings yet

- Sony ProjectorDocument4 pagesSony ProjectorchanchaldattaNo ratings yet

- Apple Macbook M42BDocument83 pagesApple Macbook M42BtragictwinkNo ratings yet

- GA24-3332-6 Reference Manual Model 29 Card Punch Jun70Document49 pagesGA24-3332-6 Reference Manual Model 29 Card Punch Jun70kgrhoadsNo ratings yet

- Product Sheet - Devastator 3Document1 pageProduct Sheet - Devastator 3andtheclubteddysNo ratings yet

- Debug 1214Document3 pagesDebug 1214Ce' WatNo ratings yet

- System Block Diagram: Schematic DiagramsDocument45 pagesSystem Block Diagram: Schematic DiagramsMatias MareNo ratings yet