Professional Documents

Culture Documents

L17 2 f10

Uploaded by

kitamielOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

L17 2 f10

Uploaded by

kitamielCopyright:

Available Formats

EECS 247 Lecture 17: Data Converters 2010 Page 1

EE247

Lecture 17

Administrative issues

Midterm exam postponed to Thurs. Oct. 28th

o You can only bring one 8x11 paper with your

own written notes (please do not photocopy)

o No books, class or any other kind of

handouts/notes, calculators, computers, PDA,

cell phones....

o Midterm includes material covered to end of

lecture 14

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 2

EE247

Lecture 17

ADC Converters

Sampling (continued)

Sampling switch considerations

Clock voltage boosters

Sampling switch charge injection & clock feedthrough

Complementary switch

Use of dummy device

Bottom-plate switching

Track & hold

T/H circuits

T/H combined with summing/difference function

T/H circuit incorporating gain & offset cancellation

T/H aperture uncertainty

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 3

Practical Sampling

Summary So Far!

2

2

2

12

B

B

FS

C k T

V

>

( ) 1 for

in

ON o o ox DD th

DD th

W V

g g g C V V

V V

L

| |

= =

|

\ .

0.72

s

R

B f C

<<

kT/C noise

Finite R

sw

limited bandwidth

g

sw

= f (V

in

) distortion

Allowing long enough settling time reduce distortion due to

switch non-linear behavior

v

IN

v

OUT

C

M1

|

1

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 4

Constant V

GS

Sampling Circuit

VP1

100ns

M12

M8

M9

M6

M11

VS1

1.5V

1MHz

Chold

P

C1 C2

M1

M2

VDD=3V

M3

C3

M5

M4

P

This Example: All device sizes:W/L=10/0.35

All capacitor size: 1pF (except for Chold)

Note: Each critical switch requires a separate clock booster

P

_

N

Vg

Va Vb

Sampling switch & C

PB

Ref: A. Abo et al, A 1.5-V, 10-bit, 14.3-MS/s CMOS Pipeline Analog-to-Digital Converter, JSSC May

1999, pp. 599.

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 5

Clock Voltage Doubler

C1 C2

M1

M2

VP1

Clock period: 100ns

PB

P_Boost

VDD

2VDD

0

VDD=3V

R1 R2

*R1 & R2=1GOhm

dummy resistors added for simulation only

P

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 6

Constant V

GS

Sampler: u Low

Sampling switch M11

is OFF

C3 charged to ~VDD

Input voltage

source

M3

Triode

C3

M12

Triode

M4

OFF

VS1

1.5V

1MHz

Chold

1pF

~ 2 VDD

(boosted clock)

VDD

VDD

OFF M11

OFF

Device

OFF

VDD=3V

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 7

Constant V

GS

Sampler: u High

C3 previously

charged to VDD

M8 & M9 are on:

C3 across G-S of M11

M11 on with constant

VGS = VDD

Mission accomplished!?

C3

1pF

M8

M9

M11

VS1

1.5V

1MHz

Chold

VDD

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 8

Constant V

GS

Sampling

Input Switch V

Gate

Input Signal

Chold Signal

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 9

Constant V

GS

Sampling?

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 10

During the time period:

V

in

< V

out

V

GS

=constant=V

DD

Larger V

GS

-V

th

compared to no boost

V

GS

=cte and not a

function of input voltage

Significant linearity

improvement

During the time period:

V

in

>V

out

:

V

GS

= V

DD

- IR

Larger V

GS

-V

th

compared to

no boost

V

GS

is a function of IR and

hence input voltage

Linearity improvement not

as pronounced as for V

in

< V

out

IR

Constant V

GS

Sampling?

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 11

Boosted Clock Sampling

Design Considerations

Ref: A. Abo et al, A 1.5-V, 10-bit, 14.3-MS/s CMOS Pipeline Analog-to-Digital Converter, JSSC

May 1999, pp. 599.

Choice of value for C3:

C3 too large large charging

current large dynamic power

dissipation

C3 too small

(Vgate-Vs)

M11

=

VDD.C3/(C3+Cx)

Loss of VGS

M11

due to low

ratio of C3/Cx

Cx includes C

GS

of M11 plus

all other parasitics caps.

C3

M8

M9

M11

Vin

Chold

VDD

Cx

Boosted Clock Sampling

Design Considerations

Reliability issues:

Avoid having any of the G-S and G-D, and D-S

terminal voltages for ALL circuit devices exceed

the maximum V

DD

prescribed by the SI

processing firm.

In particular, the thin MOS device gate oxide could

gradually sustain damage through getting exposed

to higher than prescribed voltage.

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 12

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 13

Boosted Clock Sampling

Complete Circuit

Ref: A. Abo et al, A 1.5-V, 10-bit, 14.3-MS/s CMOS Pipeline Analog-to-Digital Converter, JSSC

May 1999, pp. 599.

Clock Multiplier

Switch

M7 & M13 for

reliability

Remaining issues:

-V

GS

constant only

for V

in

<V

out

-Nonlinearity due to

Vth dependence of

M11on body-

source voltage

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 14

Advanced Clock Boosting Technique

Ref: M. Waltari et al., "A

self-calibrated pipeline

ADC with 200MHz IF-

sampling frontend,"

ISSCC 2002, Dig.

Tech. Papers, pp. 314

Sampling

Switch

Two floating voltages sources generated and connected to Gate and S & D

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 15

Advanced Clock Boosting Technique

clklow

Capacitors C1a & C1b charged to VDD

MS off

Hold mode

Sampling

Switch

clklow

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 16

Advanced Clock Boosting Technique

Sampling

Switch

clkhigh

Top plate of C1a & C1b connected to gate of sampling switch

Bottom plate of C1a connected to V

IN

Bottom plate of C1b connected to V

OUT

VGS & VGD of sampling switch (MS) both @ VDD & ac signal on G of MS

average of V

IN

& V

OUT

clkhigh

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 17

Advanced Clock Boosting Technique

Gate tracks average of input and output, reduces effect of IR drop at

high frequencies

Bulk also tracks signal reduced body effect (technology used allows

connecting bulk to S)

Reported measured SFDR = 76.5dB at f

in

=200MHz

Ref: M. Waltari et al., "A

self-calibrated pipeline

ADC with 200MHz IF-

sampling frontend,"

ISSCC 2002, Dig.

Tech. Papers, pp. 314

Sampling

Switch

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 18

Constant Conductance Switch

Ref: H. Pan et al., "A 3.3-V 12-b 50-MS/s A/D converter in 0.6um CMOS with over 80-dB

SFDR," IEEE J. Solid-State Circuits, pp. 1769-1780, Dec. 2000

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 19

Constant Conductance Switch

Ref: H. Pan et al., "A 3.3-V 12-b 50-MS/s A/D converter in 0.6um CMOS with over 80-dB

SFDR," IEEE J. Solid-State Circuits, pp. 1769-1780, Dec. 2000

OFF

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 20

Constant Conductance Switch

Ref: H. Pan et al., "A 3.3-V 12-b 50-MS/s A/D converter in 0.6um CMOS with over 80-dB

SFDR," IEEE J. Solid-State Circuits, pp. 1769-1780, Dec. 2000

ON

M2Constant current

M1replica of M2

& same VGS

as M2

M1 also

constant current

Note: Authors report requirement

of 280MHz GBW for the opamp for

12bit 50Ms/s ADC

Also, opamp common-mode

compliance for full input range

required

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 21

Switch Off-Mode Feedthrough Cancellation

Ref: M. Waltari et al., "A self-calibrated pipeline ADC with 200MHz IF-sampling frontend,"

ISSCC 2002, Dig. Techn. Papers, pp. 314

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 22

Practical Sampling

Issues

v

IN

v

OUT

C

M1

|

1

Switch induced noise due to M1 finite channel resistance

Clock jitter

Finite R

sw

limited bandwidth finite acquisition time

R

sw

= f(V

in

) distortion

Switch charge injection & clock feedthrough

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 23

Sampling Switch Charge Injection & Clock Feedthrough

Switching from Track to Hold

V

i

V

O

C

s

M1

V

G

First assume V

i

is a DC voltage

When switch turns off unwanted offset voltage induced on C

s

Why ?

V

G

t

V

H

V

i

V

L

V

i

+V

th

V

O

V

i

t

off

AV

t

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 24

Sampling

Switch Charge Injection

Channel distributed RC network formed between G,S, and D

Channel to substrate junction capacitance distributed & voltage dependant

Drain/Source junction capacitors to substrate voltage dependant

Over-lap capacitance C

ov

= L

D

.W.C

ox

associated with G-S & G-D overlap

MOS xtor operating in triode region

Cross section view

Distributed channel resistance &

gate & junction capacitances

S

G

D

B

L

D

L

C

ov

C

ov

C

j

db

C

j

sb

C

HOLD

W

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 25

Switch Charge Injection

Slow Clock

Slow clockclock fall time >> device speed

During the period (t- to t

off

) current in channel discharges channel

charge into low impedance signal source

Only source of error Clock feedthrough from C

ov

to C

s

V

G

t

V

H

V

i

V

L

V

i

+V

th

t

off

t-

Device still

conducting

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 26

Switch Clock Feedthrough

Slow Clock

V

G

t

V

H

V

i

V

L

V

i

+V

th

V

O

V

i

t

off

AV

t

D

C

ov

V

G

t-

C

s

( )

( )

( ) ( )

( )

( )

ov

i t h L

ov s

ov

i t h L

s

o i

ov ov ov

o i i t h L i t h L

s s s

o i os

ov ov

os t h L

s s

C

V V V V

C C

C

V V V

C

V V V

C C C

V V V V V V 1 V V

C C C

V V 1 V

C C

where ; V V V

C C

c

c

A = +

+

~ +

= +A

| |

= + =

|

|

\ .

= + +

= =

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 27

Switch Charge Injection & Clock Feedthrough

Slow Clock- Example

V

G

t

V

H

V

i

V

L

V

i

+V

th

V

O

V

i

t

off

AV

t

V

i

V

O

C

s

=1pF

M1

V

G

10/0.18

t-

( )

' 2

ov

ox t h L

ov

s

ov

os t h L

s

C 0. 1f F / C 9 f F / V 0. 4V V 0

C 10 x0. 1f F /

. 1%

C 1pF

Al l owi ng 1/ 2LSB ADC resol ut i on ~ 9bi t

C

V V V 0. 4mV

C

c

c

= = = =

= = =

= <

= =

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 28

Switch Charge Injection & Clock Feedthrough

Fast Clock

V

G

t

V

H

V

i

V

L

V

i

+V

th

V

O

V

i

t

off

AV

t

V

i

V

O

C

s

=1pF

M1

V

G

Sudden gate voltage drop no gate voltage to establish current in channel

channel charge has no choice but to escape out towards S & D

Q

ch

mQ

ch

nQ

ch

n+m=1

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 29

For simplicity it is assumed channel charge divided equally between S & D

Source of error channel charge transfer + clock feedthrough via C

ov

to C

s

V

G

t

V

H

V

i

V

L

V

i

+V

th

V

O

V

i

t

off

AV

t

Switch Charge Injection & Clock Feedthrough

Fast Clock

Clock Fall-Time << Device Speed:

( )

( )

( ) ( )

( )

( )

( )

ov ch

o H L

ov s s

ox H i t h ov

H L

ov s s

o i os

ox

s

ox H t h ov

os H L

s s

C 1 Q

V V V

C C 2 C

WC L V V V C 1

V V

C C 2 C

V V 1 V

1 WC L

where

2 C

WC L V V C 1

V V V

C 2 C

c

c

A =

+

~

+

= + +

=

=

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 30

Switch Charge Injection & Clock Feedthrough

Fast Clock- Example

V

i

V

O

C

s

=1pF

M1

V

G

10 /0.18

( )

( )

ov ox t h DD L

2

2

ox

s

ox H t h ov

os H L

s s

f F f F

C 0. 1 , C 9 , V 0. 4V,V 1. 8V, V 0

WLC 10 x0. 18 x9 f F /

1/ 2 1. 6% ~ 5 bi t

C 1pF

WC L V V C 1

V V V 1. 8mV 14. 6mV 16. 4mV

C 2 C

c

= = = = =

= = =

= = =

V

G

t

V

H

V

i

V

L

V

i

+V

th

V

O

V

i

t

off

AV

t

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 31

Switch Charge Injection & Clock Feedthrough

Example-Summary

Error function of:

Clock fall time

Input voltage level

Source impedance

Sampling capacitance size

Switch size

Clock fall/rise should be controlled not to be faster (sharper)

than necessary

Clock fall time

c

V

OS

Clock fall time

1.6%

.1%

16mV

0.4mV

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 32

Switch Charge Injection

Error Reduction

How do we reduce the error?

Reduce switch size to reduce channel charge?

Reducing switch size increases t increased distortion not a viable solution

Small t and small AV use minimum chanel length (mandated by technology)

For a given technology t x AV ~ constant

( )

( )

( ) ( )

ch

o

s

s s

ON s

ox GS t h

ox GS t h

s

o s ox H i t h

2

1 Q

V

2 C

C T

R C ( not e : k

W

2

C V V

L

Consi der t he f i gure of meri t (FOM):

W

C V V

1 C

L

FOM 2

V C WC L V V V

FOM L

)

t t

t

A = +

= = | =

= ~

A

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 33

Sampling Switch Charge Injection & Clock Feedthrough

Summary

Extra charge injected onto sampling capacitor @

switch device turn-off

Channel charge injection

Clock feedthrough to C

s

via C

ov

Issues due to charge injection & clock feedthrough:

DC offset induced on hold C

Input dependant error voltage distortion

Solutions:

Slowing down clock edges as much as possible

Complementary switch?

Addition of dummy switches?

Bottom-plate sampling?

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 34

Switch Charge Injection & Clock Feedthrough

Complementary Switch

In slow clock case if area of n & p devices & widths are equal

(W

n

=W

p

)effect of overlap capacitor for n & p devices to first order

cancel (cancellation accuracy depends on matching of n & p width and

overlap length L

D

)

Since in CMOS technologies

n

~2.5

p

choice of W

n

=W

p

not optimal

from linearity perspective (W

p

>W

n

preferable)

|

1

|

1B

|

1

|

1B

V

G

t

V

H

V

i

V

L

|

1

|

1B

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 35

Switch Charge Injection

Complementary Switch

Fast Clock

In fast clock case

To 1

st

order, offset due to overlap caps

cancelled for equal device width

Input voltage dependant error worse!

|

1

|

1B

V

G

t

V

H

V

i

V

L

( )

( )

( )

ch n n ox n H i t h n

t h p ch p p ox p i L

ch p ch n

o

s s

o i os

n ox n p ox p

s

Q W C L V V V

V Q W C L V V

Q 1 Q

V

2 C C

V V 1 V

1 W C L W C L

2 C

c

c

=

=

| |

A ~ |

|

\ .

= + +

+

~

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 36

Switch Charge Injection

Dummy Switch

V

i

V

O

C

s

t

V

H

V

i

V

L

V

G V

GB

W

M2

=1/2W

M1

V

G

V

G

M1

M2

Q

1 Q

2

M1 M1

1 ch ov

M2 M2

2 ch ov

M1 M2

M2 M1 2 1 ov ov

1

Q Q Q

2

Q Q 2Q

1

For W W Q Q & Q 2Q

2

~ +

~ +

= = =

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 37

Switch Charge Injection

Dummy Switch

V

i

V

O

C

s

t

V

H

V

i

V

L

V

G V

GB

Dummy switch same L as main switch but half W

Main device clock goes low, dummy device gate goes high dummy

switch acquires same amount of channel charge main switch needs to

lose

Effective only if exactly half of the charge stored in M1 is transferred to M2

(depends on input/output node impedance) and requires good matching

between clock fall/rise

W

M2

=1/2W

M1

V

G

V

GB

M1

M2

Q

1 Q

2

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 38

Switch Charge Injection

Dummy Switch

V

i

V

O

M1

V

G

M2

V

GB

To guarantee half of charge goes to each sidecreate the same

environment on both sides

Add capacitor equal to sampling capacitor to the other side of the switch

+ add fixed resistor to emulate input resistance of following circuit

Issues: Degrades sampling bandwidth

C

s C

s

R

W

M2

=1/2W

M1

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 39

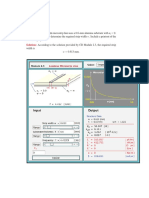

Dummy Switch Effectiveness Test

Ref: L. A. Bienstman et al, An Eight-Channel 8 13it Microprocessor Compatible NMOS D/A

Converter with Programmable Scaling, IEEE JSSC, VOL. SC-15, NO. 6, DECEMBER 1980

Dummy switch

W=1/2W

main

As Vin is

increased Vc1-Vin

is decreased

channel charge

decreasedless

charge injection

Note large Ls

good device

area matching

EECS 247 Lecture 17: Data Converters- ADC Design, Sampling 2010 Page 40

Switch Charge Injection

Differential Sampling

V

i+

V

O+

V

i-

V

O-

To 1

st

order, offset terms cancel

Note gain error c still about the same

Has the advantage of better immunity to

noise coupling and cancellation of even

order harmonics

|

Cs

Cs

( )

( )

( )

( )

o o od i i i d

o o i i

oc i c

o i 1 os1

o i 2 os2

1 2

od i d i d 1 2 i c os1 os2

V V V V V V

V V V V

V V

2 2

V V 1 V

V V 1 V

V V V V V V

2

c

c

c c

c c

+ +

+ +

+ +

= =

+ +

= =

= + +

= + +

+

= + + +

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 41

Avoiding Switch Charge Injection

Bottom Plate Sampling

Switches M2 opened slightly earlier compared to M1

Injected charge due to turning off M2 is constant since its GS voltage

is constant & eliminated when used differentially

Since C

s

bottom plate is already open when M1 is switched off:

No signal dependant charge injected on C

s

|

1

V

H

V

L

t

|

1D

V

i

V

O

M1

|

1D

|

1

M2

Cs

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 42

Flip-Around Track & Hold

v

IN

v

OUT

C

S1A

|

1D

S2

|

2

S2A

|

2

S3

|

1D

|

1 S1

v

CM

Concept based on bottom-

plate sampling

|

1

|

2

|

1D

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 43

Flip-Around T/H-Basic Operation

|

1

high

v

IN

v

OUT

C

S1A

|

1D

S2

|

2

S2A

|

2

S3

|

1D

|

1 S1

v

CM

Charging C

|

1

|

1D

|

2

Note: Opamp has to be

stable in unity-gain

configuration

Q

|1

=V

IN

xC

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 44

Flip-Around T/H-Basic Operation

|

2

high

v

IN

v

OUT

C

S1A

|

1D

S2

|

2

S2A

|

2

S3

|

1D

|

1 S1

v

CM

Holding

|

1

|

2

|

1D

Q

|2

=V

OUT

xC

V

OUT

= V

IN

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 45

Flip-Around T/H - Timing

S1 opens earlier than S1A

No resistive path from C

bottom plate to Gnd charge

can not change

"Bottom Plate Sampling"

v

IN

v

OUT

C

S1A

|

1D

S2

|

2

S2A

|

2

S3

|

1D

|

1 S1

v

CM

|

1

|

2

|

1D

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 46

Charge Injection

At the instant of transitioning from track to hold

mode, some of the charge stored in sampling

switch S1 is dumped onto C

With "Bottom Plate Sampling", only charge

injection component due to opening of S1 and

is to first-order independent of v

IN

Only a dc offset is added. This dc offset can be

removed with a differential architecture

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 47

Flip-Around T/H

v

IN

v

OUT

C

S1A

|

1D

S2

|

2

S2A

|

2

S3

|

1D

|

1 S1

v

CM

Constant switch V

GS

to minimize distortion

Note: Among all switches

only S1A & S2A

experience full

input voltage swing

|

1

|

2

|

1D

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 48

Flip-Around T/H

S1 is chosen to be an n-channel MOSFET

Since it always switches the same voltage, its on-

resistance, R

S1

, is signal-independent (to first order)

Choosing R

S1

>> R

S1A

minimizes the non-linear

component of R = R

S1A

+ R

S1

Typically, S1A is a wide (much lower resistance than S1) &

constant V

GS

switch

In practice size of S1A is limited by the (nonlinear) S/D

capacitance that also adds distortion

If S1As resistance is negligible delay depends only on S1

resistance

S1 resistance is independent of V

IN

error due to finite

time-constant independent of V

IN

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 49

Differential Flip-Around T/H

Choice of Sampling Switch Size

Ref: K. Vleugels et al, A 2.5-V SigmaDelta Modulator for Broadband Communications

Applications IEEE JSSC, VOL. 36, NO. 12, DECEMBER 2001, pp. 1887

THD simulated w/o sampling switch boosted clock -45dB

THD simulated with sampling switch boosted clock (see graph)

C

s

=7pF

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 50

Differential Flip-Around T/H

Ref: W. Yang, et al. A 3-V 340-mW 14-b 75-Msample/s CMOS ADC With 85-dB SFDR at Nyquist Input,

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 36, NO. 12, DECEMBER 2001 1931

Offset voltage associated with charge injection of S11 & S12 cancelled by differential

nature of the circuit

During input sampling phaseamp outputs shorted together

S11

S12

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 51

Differential Flip-Around T/H

Gain=1

Feedback factor=1 high operating speed

|

1

|

1

|

2

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 52

Differential Flip-Around T/H

Issues: Input Common-Mode Range

AV

in-cm

=V

out_com

-V

sig_com

Drawback: Amplifier needs to have large input common-mode

compliance

VCM=1.5V

1.7V

1.3V

1V

1V

1V

1.2V

0.8V

0.5V

AV

in-cm

=1-1.5= - 0.5V

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 53

Input Common-Mode

Cancellation

Ref: R. Yen, et al. A MOS Switched-Capacitor Instrumentation Amplifier, IEEE JOURNAL OF

SOLID-STATE CIRCUITS, VOL. SC-17, NO. 6,, DECEMBER 1982 1008

Note: Shorting switch M3 added

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 54

Input Common-Mode Cancellation

Track mode (| high)

V

C1

=V

I1

, V

C2

=V

I2

V

o1

=V

o2

=0

Hold mode (| low)

V

o1

+V

o2

=0

V

o1

-V

o2

= -(V

I1

-V

I2

)(C

1

/(C

1

+C

3

))

Input common-mode level removed

1V+0.2V

1V-0.2V

+ 1.2 -

+ 0.8 -

+ 0.1 -

- 0.1 +

-0.1

+0.1

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 55

Switched-Capacitor Techniques Combining

Track & Hold with Other Functions

T/H + Charge redistribution amplifier

T/H & Input difference amplifier

T/H & summing amplifier

Differential T/H combined with gain stage

Differential T/H including offset cancellation

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 56

T/H + Charge Redistribution Amplifier

Track mode: (S1, S3 on S2off)

V

C1

=V

os

V

IN

, V

C2

=0

V

o

=V

os

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 57

T/H + Charge Redistribution Amplifier

Hold Mode

Hold/amplify mode (S1, S3 off S2on)

Offset NOT cancelled, but not amplified

Input-referred offset =(C

2

/C

1

) x V

OS

, & often C

2

<C

1

2

1

2

S1 & S3 open

S2 closed

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 58

T/H & Input Difference Amplifier

Sample mode:

(S1, S3 on S2off)

V

C1

=V

os

V

I1

, V

C2

=0

V

o

=V

os

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 59

Input Difference Amplifier

Contd

Subtract/Amplify mode (S1, S3 off S2on)

During previous phase:

V

C1

=V

os

V

I1

, V

C2

=0

V

o

=V

os

1

Offset NOT cancelled, but not amplified

Input-referred offset =(C

2

/C

1

)xV

OS

, & C

2

<C

1

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 60

T/H & Summing Amplifier

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 61

T/H & Summing Amplifier

Contd

Sample mode (S1, S3, S5on S2, S4off)

V

C1

=V

os

V

I1

, V

C2

=V

os

-V

I3

, V

C3

=0

V

o

=V

os

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 62

T/H & Summing Amplifier

Contd

Amplify mode (S1, S3, S5off, S2, S4on)

3

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 63

Differential T/H Combined with Gain Stage

Ref: S. H. Lewis, et al., A Pipelined 5-Msample/s 9-bit Analog-to-Digital Converter IEEE

JSSC, VOL. SC-22,NO. 6, DECEMBER 1987

Employs the previously discussed technique to eliminate the problem associated

with high common-mode voltage excursion at the input of the opamp

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 64

Ref: S. H. Lewis, et al., A Pipelined 5-Msample/s 9-bit Analog-to-Digital Converter IEEE

JSSC, VOL. SC-22,NO. 6, DECEMBER 1987

Differential T/H Combined with Gain Stage

|1 High

EECS 247 Lecture 17: Data Converters- Track & Hold- ADC Design 2009 Page 65

Ref: S. H. Lewis, et al., A Pipelined 5-Msample/s 9-bit Analog-to-Digital Converter IEEE

JSSC, VOL. SC-22,NO. 6, DECEMBER 1987

Gain=4C/C=4

Input voltage common-mode level removed opamp can have low input

common-mode compliance

Amplifier offset NOT removed

Differential T/H Combined with Gain Stage

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- SweRV Core Roadmap White PaperDocument8 pagesSweRV Core Roadmap White PaperThi NguyenNo ratings yet

- Fundamentals of Electronics, Book - 1 PDFDocument319 pagesFundamentals of Electronics, Book - 1 PDFjramongv83% (12)

- L13 2 f10Document36 pagesL13 2 f10kitamielNo ratings yet

- 169 T562Document5 pages169 T562kitamielNo ratings yet

- Diode Equation ModelsDocument24 pagesDiode Equation ModelsJayann GonzalesNo ratings yet

- La Place TransformDocument35 pagesLa Place TransformAhmed Sakr (أحمد صقر)No ratings yet

- COROMETRICSDocument440 pagesCOROMETRICSANELYNo ratings yet

- The University of Lahore, Islamabad Campus Course: Power System Protection Lab Work Sheet 4Document8 pagesThe University of Lahore, Islamabad Campus Course: Power System Protection Lab Work Sheet 4Hayat AnsariNo ratings yet

- Gecko Drive g340 - 815e28e418 PDFDocument7 pagesGecko Drive g340 - 815e28e418 PDFRemus PopescuNo ratings yet

- Input Output InterfacingDocument48 pagesInput Output InterfacingLokesh Kumar ChoudharyNo ratings yet

- Matching transmission line to antenna impedanceDocument19 pagesMatching transmission line to antenna impedanceNguyen Thanh HungNo ratings yet

- Driver Backlight PSP 2000Document12 pagesDriver Backlight PSP 2000Jhonny GuillermoNo ratings yet

- Feedback Amplifiers and Oscillators PDFDocument2 pagesFeedback Amplifiers and Oscillators PDFAmy100% (2)

- Panasonic Cq-Rx400uDocument37 pagesPanasonic Cq-Rx400uAle Hdz0% (1)

- Pioneer 1005 SMDocument22 pagesPioneer 1005 SMe2140r03No ratings yet

- 24T Adder PDFDocument4 pages24T Adder PDFJatinKumarNo ratings yet

- 11 Instruction Set of 8086Document61 pages11 Instruction Set of 8086kingmeno0% (1)

- ELX304 Topic1 Lesson 1 Pr2Document22 pagesELX304 Topic1 Lesson 1 Pr2Mahesvaran SubramaniamNo ratings yet

- CAMPVS2580Document3 pagesCAMPVS2580xdsmNo ratings yet

- CST Application Note - Dual Band GSM Antenna PDFDocument6 pagesCST Application Note - Dual Band GSM Antenna PDFTDMA2009No ratings yet

- 101 Q&PDocument2 pages101 Q&PCorn Deleon MacapagalNo ratings yet

- Question Bank Unit - V: Registers & Counters Part - A (Each Question Carries 1 Mark)Document9 pagesQuestion Bank Unit - V: Registers & Counters Part - A (Each Question Carries 1 Mark)Nithya SNo ratings yet

- PMU Lecture 6 - The Impedance Model and ZbusDocument17 pagesPMU Lecture 6 - The Impedance Model and ZbusPoor AdamNo ratings yet

- MATV Division 16781Document37 pagesMATV Division 16781Sachin MohiteNo ratings yet

- PC Wor X LaptopsDocument16 pagesPC Wor X LaptopsEva HubadNo ratings yet

- Exp 6Document12 pagesExp 6Laura AcaciaNo ratings yet

- 05 - List of SymbolsDocument6 pages05 - List of Symbolsrajath RaviNo ratings yet

- SW-TM4C-RLN-2 1 0 12573Document36 pagesSW-TM4C-RLN-2 1 0 12573trungkiena6No ratings yet

- Ug471 7series SelectIO PDFDocument188 pagesUg471 7series SelectIO PDFDlishaNo ratings yet

- HP 4520s - h9265-4Document62 pagesHP 4520s - h9265-4Đnn WankaNo ratings yet

- Applications of GSM Module in Wireless ECGDocument7 pagesApplications of GSM Module in Wireless ECGAbd TashNo ratings yet

- Aligning Dual-Polarized AntennasDocument3 pagesAligning Dual-Polarized Antennasespiar_016No ratings yet

- GT Full Catalogue WebDocument314 pagesGT Full Catalogue WebJose Rhey OsabalNo ratings yet

- Register Transfer Level Design With Verilog: Verilog Digital System Design Z. Navabi, Mcgraw-Hill, 2005Document77 pagesRegister Transfer Level Design With Verilog: Verilog Digital System Design Z. Navabi, Mcgraw-Hill, 2005I am number 4No ratings yet