Professional Documents

Culture Documents

Architecture D'ordinateurs

Uploaded by

Mourad WorksOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Architecture D'ordinateurs

Uploaded by

Mourad WorksCopyright:

Available Formats

ARCHITECTURE ET TECHNOLOGIE

DES ORDINATEURS

Sylvain TISSERANT

Universit de la Mditerrane

Ecole Suprieure dIngnieurs de Luminy - Dpartement dinformatique

2003

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 2

Introduction

I.1 Architecture des ordinateurs

I.1.a L'informatique aujourd'hui

Apparue au milieu du 20

me

sicle, l'informatique a connu et connat une volution

extrmement rapide. A sa motivation initiale qui tait de faciliter et d'acclrer le calcul, se sont

ajoutes de nombreuses fonctionnalits, comme l'automatisation, le contrle et la commande de

pratiquement tout processus, la communication ou le partage de l'information. Dans nos socits

occidentales elle omniprsente. Aprs avoir t un outil rserv aux centres de recherche, elle

s'est implante dans l'industrie et depuis les annes 80 elle envahit nos foyers. Au dpart nous

n'avions que des systmes centraux, puis sont apparus les postes de travail individuels, trs

rapidement relis en rseaux locaux. Tous, ou presque, sont maintenant connects la "Toile".

Nombreux sont les projets actuels d'utilisation et de gestion d'une puissance de calcul norme

distribue sur un grand nombre de sites dissmins de par le monde. L'informatique est en grande

partie responsable de la profonde transformation que connat actuellement la civilisation des pays

riches.

Les volutions techniques sont telles que la dure de vie des matriels est relativement

courte. Le march est extrmement instable et en permanente volution. La position des

constructeurs est presque remise en cause chaque jour. Face cette situation, aprs une premire

priode de systmes propritaires, dans lesquels un client de pouvait en pratique s'approvisionner

qu'auprs d'un seul constructeur, nous sommes passs aux systmes ouverts. Cela sous-entend des

architectures normalises pour lesquelles les lments peuvent provenir de plusieurs

constructeurs. En parallle, du ct logiciel un accent important est mis sur la rutilisation des

produits, qui doit permettre de suivre ces volutions au prix d'un effort moindre, sans avoir

repartir de zro chaque passage sur une nouvelle plate-forme par exemple. Cela explique

l'mergence des technologies "Orientes Objets" et du "Gnie Logiciel". Il est remarquer que

cela se fait souvent avec une perte d'efficacit, masque par l'volution des performances au

niveau technique.

Face cette situation trs volatile, nous constatons tout de mme que les concepts de base

introduits par les pionniers perdurent, mme s'ils peuvent se dcliner de faons trs diffrentes.

Pour viter d'avoir rcrire ce cours d'Architecture des Ordinateurs tous les ans, j'ai donc pris le

parti de principalement dvelopper et expliquer ces concepts et les technologies de base.

L'architecture du PC servira parfois dexemple. Ce choix me semble tre aujourd'hui (en l'an

2003) incontournable. Il y a quelques annes j'aurais sans doute choisi les architectures RISC des

stations de travail. Je ne prendrai pas le risque de prdire quel sera l'exemple choisir dans cinq

ou dix ans.

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 3

I.1.b Architecture gnrale et blocs fonctionnels

Initialement un ordinateur tait un calculateur numrique. C'est aujourd'hui une machine

de traitement de l'information. Il est capable d'acqurir et de stocker des informations, d'effectuer

des traitements et de restituer des informations. L'informatique, contraction d'information et

automatique, est devenue la science du traitement de l'information.

Un ordinateur peut tre dcoup en blocs fonctionnels. Le traitement de l'information est

fait au niveau d'un processeur. Les actions que celui-ci doit effectuer sont dfinies par des

instructions. Pour tre accessible au processeur les donnes traiter et les instructions doivent

tre stockes dans une mmoire. Le processeur et la mmoire sont relis par un bus. Par ailleurs il

faut que l'utilisateur puisse fournir l'ordinateur des donnes et les instructions suivre, tout

comme il doit avoir connaissance des rsultats. Il faut donc des dispositifs d'entre et de sortie.

Chaque bloc fonctionnel peut lui-mme tre dcrit par un ensemble d'units

fonctionnelles. On parle alors de l'architecture du processeur, de l'architecture de la mmoire, etc.

Par ailleurs on peut tudier l'architecture d'un rseau rassemblant plusieurs ordinateurs.

On voit ainsi apparatre la notion de niveaux de reprsentation. A chaque niveau un objet

considr est dcrit comme un ensemble de blocs interconnects. Au niveau suivant chacun de

ces blocs est son tour dcrit comme un ensemble de blocs interconnects et ainsi de suite. Cette

dcomposition hirarchique en niveaux dpend des besoins de la conception ou des outils

utiliss : elle n'est ni fige, ni unique. Nous pouvons, par exemple, descendre au niveau des portes

logiques et mme au niveau des transistors qui composent ces portes.

L'architecture d'un ordinateur constitue la reprsentation de ses units fonctionnelles et de

leurs interconnexions. Le choix d'une architecture est toujours le rsultat d'un compromis :

- entre performances et cots;

- entre efficacit et facilit de construction;

- entre performances d'ensemble et facilit de programmation;

- etc

Chaque solution adopte pour une machine donne, un instant donn et pour un march donn,

pourra trs vite tre remise en cause par un nouveau progrs technologique. De mme, des

architectures proposes un moment donn, puis abandonnes pour des raisons techniques ou

conomiques, peuvent un jour tre nouveau employes.

Quelle que soit sa dimension (mini, micro, super, hyper, etc.) on retrouve toujours dans un

ordinateur les mmes blocs fonctionnels :

- une ou plusieurs units de traitement;

- de la mmoire;

- un ou plusieurs disques durs, constituant une mmoire permanente;

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 4

- des dispositifs de communication avec loprateur : un cran, un clavier, trs souvent une

souris ;

- des dispositifs de communication avec lextrieur comme une imprimante ;

- des dispositifs permettant larchivage : disquette, bande magntique, disque optique;

- etc.

relis par des bus, des liaisons ou des rseaux. L'informatique se trouve galement tre

embarque dans un grand nombre de dispositifs de la vie courante, aussi varis que machines

laver, distributeurs de boissons, voitures ou cartes bancaires. Si, par rapport un ordinateur

classique, les tches raliser ne sont pas aussi polyvalentes et si les contraintes sont diffrentes,

on y retrouve cependant les mmes briques. Partant des portes logiques, nous allons essayer

d'tudier dans ce cours les principes de base de chacun de ces composants.

D'autre part, il est important de raliser que matriel et logiciel sont indissociables, en

particulier au niveau de la conception de tout systme informatique. Nous rencontrerons dans ce

cours un ou deux exemples de l'imbrication du logiciel et du matriel. Pour ce qui concerne le

logiciel nous nous limiterons quelques considrations simples sur le langage machine.

Mais avant d'aborder l'tude des portes logiques, puis des premires units fonctionnelles

remontons dans le temps.

I.2 Un peu d'histoire

I.2.a Le calcul mcanique

Pour rsumer l'histoire de l'informatique ou des ordinateurs, il souvent ncessaire de

schmatiser. Pour chaque invention, nous ne retenons en gnral qu'un nom. Mais souvent cette

invention concrtise une dmarche collective qui s'est tale sur plus ou moins de temps. Trs

souvent aussi des prdcesseurs ont t oublis. Je vais ici rsumer l'histoire de l'informatique en

m'appuyant sur quelques dates clefs les plus frquemment cites.

De tout temps l'homme a eu besoin de moyens de calcul. Citons titre d'exemple le mot

mme, dont l'tymologie calculi signifie cailloux en latin (utiliss sur les abaques des Romains),

ou encore la numrotation dcimale lie la technologie de la premire calculatrice de poche : la

main. Calcul digital signifiait alors compter sur ses doigts.

Par ailleurs, toutes les grandes civilisations de l'Antiquit avaient leurs symboles pour

coder les nombres et compter. Au dbut il s'agissait de signes simples (comme un trait)

correspondant chacun au nombre 1. Un symbole reprsentant le nombre 10 est apparu en Egypte

vers 3400 av. J.-C.. Il tait ainsi possible d'crire les nombres de manire un peu plus compacte.

D'autres symboles spciaux ont ensuite reprsent les nombres 100, 1000 et 10000. La

numration cuniforme de Babylone utilisait un systme sexagsimal (base 60). Le premier

systme binaire connu remonte 3000 ans av. J.-C. environ. Il s'agit du Yin et du Yang chinois.

On en trouve trace sur les figures magiques de l'empereur Fou-Hi, comme l'octogone trigramme

o les huit premiers nombres sont reprsents sous forme binaire :

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 5

Figure 1

Les civilisations ont galement cherch des outils pour faciliter et acclrer les calculs

ncessaires leur dveloppement. Ce furent par exemple les bouliers en Chine et les abaques

dans le Monde Mditerranen.

Une innovation trs importante fut l'emploi de la notation positionnelle, qui confre des

valeurs diffrentes aux symboles numriques selon leur position dans le nombre crit. Cette

notation positionnelle n'est possible qu'avec un symbole pour le zro. Grce au symbole 0, il

devint possible de diffrencier 11, 101 et 1 001 sans recourir des symboles supplmentaires.

Cette notation a t introduite en Europe par l'intermdiaire des Arabes, l'Islam s'tendant alors

des frontires de la Chine l'Espagne. Le systme dit arabe avait t dvelopp en Inde environ

300 ans av. J-C. Cette introduction s'est faite grce notamment la traduction, vers 820 apr. J-C,

des ouvrages du mathmaticien de Bagdad Al-Khuwarizmi, dont le titre d'un des livres (al jabr)

est l'origine du mot algbre. Les premiers documents attestant de l'utilisation du systme arabe

en Europe datent de 976, mais il faut attendre le XIV

me

sicle pour qu'il remplace totalement la

numrotation romaine. Non seulement l'criture des nombres devint plus compacte, mais les

calculs crits ont t largement simplifis.

Il faut ensuite sauter au XVII

me

sicle pour voir apparatre les premiers systmes

mcaniques de calcul, bass sur les roues dentes mises en uvre depuis longtemps dans les

horloges, automates, etc. On fait gnralement commencer cette nouvelle priode en 1614, date

laquelle John Napier (ou Neper), mathmaticien cossais, inventa les premiers logarithmes. Il

ramenait ainsi les oprations de multiplication et de division de simples additions ou

soustractions. Napier inventa galement des machines multiplier bases sur le dplacement de

tiges : les Btons ou Os de Napier. Par ailleurs, il fut l'un des premiers (le premier ?) utiliser le

point dcimal.

La rgle calcul, base sur le principe des logarithmes, fut conue par William Oughtred

en 1622. Sa prcision sera suffisante pour les calculs scientifiques jusqu' la premire moiti du

20

me

sicle. Par contre elle ne peut tre utilise en comptabilit.

En 1623, Wilhelm Schickard inventa pour Kepler une "horloge calculante" destine

calculer les phmrides. Il utilisait des roues dentes et il avait abord le problme du report de

retenue. Mais cette machine a disparue en 1624 dans les ravages de la Guerre de Trente Ans en

Allemagne du Sud. Elle a t reconstruite en 1960 d'aprs les plans originaux.

En 1642, 19 ans, Blaise Pascal construisit, pour aider son pre commissaire pour l'impt

Rouen, une "machine arithmtique" capable de traiter des additions et des soustractions six

chiffres. La Pascaline est considre comme le premier additionneur retenue automatique. A

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 6

chaque chiffre correspond une roue avec dix crans. Lorsqu'une roue a effectu un tour complet

(passage de 9 0), elle dcale d'un cran la roue suprieure. Chaque chiffre est lu dans une fentre

au-dessus de la roue. Les multiplications taient possibles par l'excution d'additions rptitives,

comme l'a montr en 1666 Moreland.

En 1673, Gottfried Leibniz amliora la Pascaline en lui ajoutant un chariot et un tambour

dents ingales. Cela permit d'automatiser, au moyen d'une manivelle, les additions et les

soustractions rptitives ncessaires aux multiplications et divisions. Leibniz inventa galement

le systme binaire et montra la simplicit de l'arithmtique binaire. Il l'appliqua l'analyse des

octogones de Fou-Hi.

En 1728, le mcanicien franais Falcon construit le premier mtier tisser dont il

commande le fonctionnement avec une planchette en bois perce de trous. C'est la premire

machine commande par un programme. Ce systme fut perfectionn par Joseph-Marie Jacquard

en 1805. La planchette de bois fut remplace par des cartes en carton perfores articules, comme

on peut encore en voir dans les orgues portatifs. Les mcanismes d'excution et les mcanismes

de contrle taient spars. Ce systme permettait de reproduire des motifs compliqus avec une

qualit gale, mais il supprimait galement cinq ouvriers par mtier tisser. Cela dclencha une

raction violente des canuts de Lyon. Il s'agit sans doute d'un des premiers exemples de l're

industrielle du remplacement d'hommes par des machines automatiques. Cependant ds 1812 on

comptait 10000 de ces mtiers tisser.

En 1820 apparat le premier "Arithmomtre" de Charles Xavier-Thomas de Colmar, sur la

base de la machine de Leibniz. Il pouvait excuter les quatre oprations arithmtiques (addition,

soustraction, multiplication, division). La premire version de disposait que de 3 chiffres pour les

oprandes et 6 pour le totaliseur. Mais cette capacit augmenta progressivement jusqu' 30

chiffres. Sa facilit d'emploi assura son succs jusqu' la Premire Guerre Mondiale.

Jusqu'alors les calculateurs mcaniques taient capables d'excuter des oprations une

une. Dans les annes 1820 et 1830, un mathmaticien anglais, Charles Babbage, rapprocha les

machines calculer et les systmes de commande de Jacquard dans le but d'effectuer des calculs

complexes ncessitant l'excution en squence de plusieurs oprations arithmtiques. Il a d'abord

tent de raliser une "machine diffrences" destine au calcul de tables de navigation ou de tir.

Il parviendra construire un prototype partiel. Mais les difficults techniques ralentissent son

projet, qu'il devra abandonner aprs une dizaine d'annes de travail, faute de moyens financiers

suffisants. Il eut alors l'ide d'une machine plus universelle : la "machine analytique" capable

d'enchaner l'excution d'oprations arithmtiques en fonction d'instructions donnes par

l'utilisateur. Cette machine contenait les concepts de base qui se retrouvent dans les ordinateurs

modernes : une unit de traitement (le moulin) commande par une unit de contrle, une

mmoire (le magasin), une unit d'entre pour recevoir des cartes perfores (oprations et

nombres) et une unit de sortie pour imprimer ou perforer le rsultat. Charles Babbage a t aid

dans la conception de cette machine par sa collaboratrice Ada Lovelace (fille du pote Lord

Byron). Elle a en particulier dfini le principe de l'enchanement d'itrations successives pour la

ralisation d'une opration, baptis algorithme en l'honneur du mathmaticien arabe Al-

Khuwarizmi. Cette machine tait cependant trop ambitieuse pour la technologie de l'poque. Un

exemplaire fut partiellement construit par son fils en 1888.

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 7

En 1854 George Boole propose sa formulation mathmatique des propositions logiques

qui applique au systme binaire est la base du fonctionnement des ordinateurs.

I.2.b Le calcul lectromcanique

En 1890, Hermann Hollerith construisit un calculateur de statistiques qui fut utilis pour

le recensement amricain. Il s'agissait d'une machine lectromcanique plus performante que les

machines mcaniques. Il dveloppa cette occasion la carte perfore et inventa le systme de

codage des informations qui porte son nom. La dtection de la prsence ou de l'absence d'un trou

se faisait au moyen d'aiguilles qui traversaient les trous et fermaient chacune un circuit lectrique

en trempant dans un godet de mercure. Par ailleurs la plupart des questions du recensement

taient poses sous forme binaire : premier exemple de l'imbrication de l'architecture matrielle et

de l'organisation des donnes. Hollerith fonda en 1896, la Tabulating Machine Company pour

produire ses cartes et machines mcanographiques. En 1924, celle-ci devint l'International

Business Machines Corporation : IBM.

En 1914, Leonardo Torres y Quevedo proposa de raliser une version lectromcanique

de la machine de Babbage. Faute de moyens ce fut un chec.

En 1930, Vannemar Bush construisit au MIT un analyseur diffrentiel, capable de

rsoudre des quations diffrentielles rencontres dans l'tude des circuits lectriques. La mme

anne, Georges Stibitz ralisa un additionneur binaire relais, le "Modle K", s'appuyant sur les

travaux de Boole.

Les annes 30 virent galement de nombreux progrs sur le plan thorique. Par exemple,

en 1936 Alan Turing nonce le principe d'une machine (virtuelle), qui pouvait en thorie raliser

tous les calculs mathmatiques, avec en particulier des instructions conditionnelles. En 1938,

dans sa thse, Claude Shannon reprenant les travaux de Leibniz et Boole, mis en vidence une

analogie entre l'algbre binaire et les circuits lectriques. Il montra plus tard que tout calcul

logique ou arithmtique peut tre ralis avec uniquement les trois oprations logiques

fondamentales : ET, OU et NON. Il est galement l'inventeur du terme bit pour binary digit pour

dsigner le chiffre binaire.

En 1938, Konrad Zuse cra avec des moyens modestes un ordinateur binaire

programmable mcanique, le Z1. En 1939, il perfectionna sa machine en remplaant une partie

des pices mcaniques par des relais lectromcaniques (Z2). Le Z3 et le Z4, virent le jour en

1941 et furent utiliss pour des calculs aronautiques. En 1939, John Atanasoff et Clifford Berry

ralisrent un additionneur binaire 16 bits. Ils furent les premiers utiliser des tubes vide.

Parmi les derniers calculateurs lectromcaniques il nous faut citer le Mark 1 ou ASCC

(Automatic Sequence Controlled Calculator), dvelopp en 1941 conjointement par IBM et

Harward, sous la direction de Howard Aiken. Il s'agissait d'une norme machine de 5 tonnes,

couvrant 25 m

2

et consommant 25 kW. Il comptait 3000 relais et 760000 pices mcaniques. Le

programme tait lu sur une bande de papier, les donnes partir d'une seconde bande de papier

ou d'un lecteur de cartes. A l'origine les sauts conditionnels taient impossibles. Par la suite il fut

quip de plusieurs lecteurs de cartes pour permettre ces sauts conditionnels et l'excution de

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 8

sous-programmes. En 1945, un insecte (bug) coince un relais, provoquant un dysfonctionnement

de cette machine analytique.

I.2.c L're de l'lectronique

Egalement en 1941, John Atanasoff et Clifford Berry construisirent le premier ordinateur

binaire lampes : l'ABC (Atanasoff-Berry Computer). Il comportait une mmoire de 60 mots de

50 bits et une unit arithmtique et logique. Bien que le programme ne fut pas stock en

mmoire, l'ABC est souvent considr comme le premier vrai ordinateur.

L'anne 1945 vit la mise en service de l'ENIAC (Electronic Numerical Integrator And

Calculator) propos en 1942 par Presper Eckert et John Mauchly. Il tait compos de 19000

tubes, 1500 relais, consommait 170 kW, pesait 30 tonnes et couvrait une surface de 72 m

2

. Il tait

environ 500 fois plus rapide que le Mark 1 (environ 330 multiplications par seconde). Cependant

sa programmation s'effectuait l'aide de fiches brancher dans un tableau de connexions. Le

travail de programmation pouvait prendre plusieurs jours. A la fin de cette mme anne, John von

Neumann, consultant sur l'ENIAC, proposa de coder le programme sous forme numrique et de

l'enregistrer en mmoire, avec un gain en souplesse et rapidit. Il jetait ainsi les bases de

l'architecture de l'ordinateur moderne. Il ne fut cependant pas le premier raliser cette machine.

Des querelles entre Eckert, Mauchly et von Neumann portant notamment sur la paternit de l'ide

et des brevets retardrent le projet EDVAC (Electronic Discret VAriable Computer). Celui-ci fut

devanc en 1948 par un prototype, appel Manchester Mark 1, puis en 1949 par l'EDSAC

(Electronic Delay Storage Automatic Computer) premire machine oprationnelle construite par

Maurice Wilkes.

En 1948, William Shockley, John Bardeen et Walter Brattain inventrent le transistor

bipolaire. Celui-ci remplaa rapidement les lampes apportant fiabilit et rapidit aux ordinateurs

de seconde gnration.

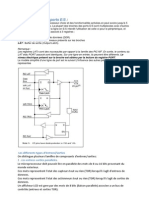

Figure 2

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 9

La taille et la consommation diminurent sensiblement. Le premier ordinateur utilisant des

transistors fut le TRADIC en 1955. A la mme poque, IBM commercialisa le premier disque dur

(5 disques de 61 cm de diamtre pour 5 Mo). Les mmoires tore de ferrite taient galement

disponibles. Le PDP-8 de DEC fut le premier mini-ordinateur tre diffus en grande srie

(50000 exemplaires).

La troisime gnration, partir de 1970, correspond l'utilisation des circuits intgrs.

L'Intel 4004, le premier microprocesseur 4 bits, fut en 1971 le premier circuit intgr incorporant

unit de calcul, mmoire et gestion des entres-sorties. Il comportait 2300 transistors. Le 8008

sortit un an plus tard. Le premier micro-ordinateur, le Micral N, fut construit en 1973 par une

entreprise franaise R2E. Depuis le dbut des annes 1980, le niveau d'intgration des puces

ayant largement progress en surface et en densit, on parle de quatrime gnration.

I.3 Quelques gnralits sur les architectures

I.3.a Architecture de Von Neumann

Cette architecture est caractrise par un processeur et une mmoire relis par un bus :

P M

B

Figure 3

Les instructions et les donnes sont stockes dans la mmoire. Pour accder une information

contenue en mmoire le processeur affiche sur le bus l'adresse de celle-ci. Aprs un certain temps

le contenu demand est affich par la mmoire sur le bus.

On constate immdiatement que la rapidit d'une machine sera limite par l'lment le

plus lent. Il ne sert rien de fabriquer un processeur trs rapide si la mmoire n'est pas capable de

lui fournir un rythme suffisant les instructions excuter, ni les donnes traiter. De manire

gnrale lorsqu'on amliore les performances d'un lment de la machine il faut s'assurer que les

autres lments qui lui sont connects seront capables de supporter des dbits plus levs. Dans le

cas contraire il peut tre favorable de revoir l'architecture de la machine. L'efficacit d'un

ordinateur est directement lie au dbit des informations (instructions et donnes) qui circulent

entre les diffrents lments. La conception d'une architecture a pour but d'optimiser ce dbit, en

prenant en compte des contraintes financires, commerciales et techniques.

La machine de base, dite de Von Neumann, que nous venons de dcrire ne prsenterait

aucun intrt sans au moins un dispositif d'entres/sorties pour permettre une communication

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 10

avec l'extrieur. Pour une machine aussi simple il existe au moins trois mthodes pour installer un

tel dispositif :

- Interface directement relie au processeur :

P M

B

E/S

Figure 4

La communication est ralise l'aide d'instructions spcialises ou par l'intermdiaire de

registres spcialiss.

- Interface connecte au bus commun :

P M

B

E/S

Figure 5

Un fil spcialis du bus indique si le processeur s'adresse la mmoire ou l'interface d'E/S.

- Interface vue par le processeur comme une partie de la mmoire :

P M

B

E/S

Figure 6

L'interface est sur le bus commun, le choix de l'adresse indique si le processeur s'adresse la

mmoire ou l'interface. Si sur le plan du matriel ces deux solutions peuvent tre trs

diffrentes, sur le plan du concept elles sont comparables : un fil supplmentaire correspond de

fait un bit. Dans les deux cas la mmoire et le dispositif dentres/sorties sont identifis par des

espaces dadressage diffrents.

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 11

I.3.b Architecture de Harvard

Dans cette architecture on spare physiquement la mmoire des instructions et la mmoire

de donnes. Chacune de ces mmoires est accessible par un bus diffrent. Il est alors possible

d'accder simultanment aux instructions et aux donnes, ce qui permet d'augmenter le flux des

informations. En premire approximation il est donc possible de multiplier la vitesse de la

machine par deux, en multipliant par deux la vitesse du processeur tout en conservant le mme

type de mmoire. En pratique il peut tre moins onreux de mettre deux bus dans une machine

que de doubler la vitesse de la mmoire.

P

BI BD

MD MI

Figure 7

Cette architecture a t exprimente trs tt, puis abandonne pendant une vingtaine d'annes.

Elle est nouveau employe dans certains micro-ordinateurs. Elle est galement reprise par

l'intermdiaire de deux caches mmoires dans larchitecture de microprocesseurs. Le 68030 fut

lun des premiers disposer de deux caches consacrs lun aux instructions et lautre aux

donnes.

Chercher pouvoir effectuer plusieurs oprations (ici transferts des instructions et des

donnes) en parallle est un principe trs souvent mis en uvre en architecture des ordinateurs.

Par exemple, pour permettre aux interfaces d'E/S de lire ou d'crire des donnes en mmoire

pendant que le processeur effectue des calculs sur les donnes prcdentes, il est intressant

d'utiliser une mmoire de donnes accessible depuis deux ports diffrents.

BI BD1 BD2

MI P MD E/S

Figure 8

De cette faon le processeur et l'interface peuvent chacun accder alternativement une moiti

diffrente de la mmoire :

Phase 1 : le processeur lit des donnes provenant de la premire moiti de la mmoire pendant

que l'interface d'Entres/Sorties range de nouvelles donnes dans la seconde moiti.

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 12

Phase 2 : le processeur accde aux donnes transfres par l'interface lors de la phase 1 et

l'interface crit dans la premire moiti de la mmoire.

BI BD1 BD2

MI P E/S

BI BD1 BD2

MI P E/S

Phase 1

Phase 2

Figure 9

I.3.c Processeur

Sans dvelopper ici les principes de fonctionnement d'un processeur, nous pouvons dj

dire que l'excution des instructions peut se dcouper en grandes tapes :

- chargement de l'instruction excuter;

- dcodage de l'instruction;

- localisation dans la mmoire des donnes utilises par l'instruction;

- chargement des donnes si ncessaire;

- excution de l'instruction;

- sauvegarde des rsultats leurs destinations respectives;

- passage l'instruction suivante.

A chacune de ces tapes peut correspondre une unit fonctionnelle. Cette squence simple peut se

compliquer, en particulier si la machine possde des instructions de longueur variable : certaines

instructions tant codes sur un mot de la mmoire et d'autres sur plusieurs. Dans ce cas l'unit

charge de la recherche et du chargement de l'instruction doit tre capable de reconnatre (ou de

pr-dcoder) le type de l'instruction pour dterminer s'il lui faut aller chercher la suite. Dans la

plupart des processeurs, l'unit centrale de traitement se dcompose en :

l'unit de commande qui contient un dispositif de dcodage des instructions (dcodeur) et

un squenceur qui contrle les circuits ncessaires l'excution de l'instruction en cours;

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 13

l'unit arithmtique et logique (UAL ou ALU : Arithmetic and Logical Unit) qui excute

des oprations arithmtiques comme l'addition, la soustraction, des dcalages, des

oprations boolennes (ET, OU, etc), des comparaisons, etc

les registres : mmoire locale trs rapide qui permet de stocker des rsultats temporaires

ou des informations de commande. Parmi ceux-ci on distingue les registres arithmtiques

qui servent aux oprations arithmtiques. D'autres registres ont des fonctions particulires.

On trouve par exemple :

- le compteur ordinal (CO) qui pointe sur la prochaine instruction excuter;

- le registre d'instruction (RI) qui contient l'instruction en cours d'excution;

- le registre d'tat (PSW : Processor Status Word) qui indique l'tat du systme :

dpassement, retenue, etc

- une pile et un pointeur de pile (SP : Stack Pointer);

des chemins de donnes.

Toutes ces units fonctionnent au mme rythme, une cadence impose par une horloge,

gnralement externe l'unit centrale. A chaque cycle d'horloge, chaque unit va ouvrir ou

fermer certaines portes pour dplacer, lire, crire, comparer, additionner des bits. Ceci se fait en

fonction d'ordres donns par l'unit de contrle. Ces ordres dpendent videmment de

l'instruction excuter.

Le tableau suivant rappelle quelques units utilises pour exprimer la frquence de

fonctionnement d'un processeur et la dure correspondante des cycles. Ainsi un processeur

fonctionnant 250 MHz a un cycle de 4 ns.

Frquence Prfixe Hz Cycle Prfixe s

1 kHz kilo 10

3

1 ms mili 10

-3

1 MHz mga 10

6

1 s micro 10

-6

1 GHz giga 10

9

1 ns nano 10

-9

Table 1

Nous verrons qu'une manire d'amliorer les performances d'une unit centrale est de faire

fonctionner ses diverses units fonctionnelles en parallle. Cela signifie aller chercher

l'instruction suivante alors que le dcodeur travaille sur l'instruction en cours. Il y a anticipation.

Il faut pour pouvoir profiter de cette technique il faut que les instructions soient excutes en

squence et donc viter les ruptures. Il faut donc que la programmation soit adapte

l'architecture des machines. Il peut galement tre possible d'excuter la mme instruction

simultanment sur plusieurs donnes. Il suffit d'une seule unit de commandes associe

plusieurs units de traitement.

I.3.d Mmoires

Nous appelons mmoire tout dispositif capable de stocker des informations (instructions

et donnes) de telle sorte que l'organe qui les utilise puisse n'importe quel moment accder

l'information qu'il demande.

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 14

Les informations peuvent tre crites ou lues. Il y a criture lorsqu'on enregistre des

donnes en mmoire, lecture lorsqu'on sort des informations prcdemment enregistres. La

lecture peut tre destructive (l'information lue n'est plus en mmoire) ou non. Le temps d'accs

est le temps qui s'coule entre l'instant o a t lance une opration de lecture en mmoire et

l'instant o la premire information est disponible. Le temps de cycle reprsente l'intervalle

minimum qui doit sparer deux demandes successives de lecture ou d'criture. Le temps de cycle

est gal ou suprieur au temps d'accs. On appelle cadence de transfert ou dbit d'une mmoire, le

nombre maximum d'informations lues ou crites par unit de temps.

Une mmoire est forme d'un certain nombre de cellules, ou cases, contenant chacune une

information. Chaque cellule a un numro qui permet de la rfrencer et de la localiser. Ce numro

est son adresse. Avec une adresse de n bits il est possible de rfrencer directement au plus 2

n

cellules. La capacit d'une mmoire est le nombre total de cellules qu'elle contient. Elle s'exprime

en nombre de bits, d'octets (bytes) ou de mots (words). Compte tenu de l'adressage binaire, les

capacits des mmoires s'expriment en puissances de deux ou en multiples de 2

10

= 1024. La

table 2 explicite les units utilises.

Symbole Prfixe Dcimal Binaire

1 k kilo

10

3

2

10

= 1024

1 M mga

10

6

2

20

= 1048576

1 G giga

10

9

2

30

= 1073741824

1 T tra

10

12

2

40

= 1099511627776

Table 2

Dans une mmoire semi-conducteur, on accde directement n'importe quelle

information dont on connat l'adresse, le temps pour obtenir l'information ne dpend pas de

l'adresse. On dira que l'accs une telle mmoire est alatoire, direct ou encore slectif. A

l'inverse pour accder une information sur bande magntique il faut drouler la bande en

reprant tous les enregistrements jusqu' ce que l'on trouve celui que l'on adresse. On dit alors

que l'accs l'information est squentiel. Le temps d'accs est variable selon la position de

l'information recherche. L'accs peut encore tre semi-squentiel : combinaison des accs direct

et squentiel. Pour un disque magntique par exemple l'accs la piste est direct, puis l'accs au

secteur est squentiel. Les mmoires associatives permettent l'accs par le contenu.

L'information stocke est volatile si elle risque d'tre altre par un dfaut d'alimentation

lectrique et non volatile dans le cas contraire.

En ce qui concerne les mmoires le problme essentiel du constructeur est celui du prix.

En effet un instant donn ce sont toujours les mmoires d'accs le plus rapide qui sont les plus

onreuses et en gnral le prix augmente plus vite que la vitesse. Or, comme nous l'avons vu, la

vitesse d'accs la mmoire conditionne, dans une large mesure les performances globales d'une

machine. C'est pourquoi les ordinateurs actuels sont dots de plusieurs types de mmoires de

tailles et de vitesses diffrentes.

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 15

On trouve d'abord des mmoires trs rapides (les plus chres), en petit nombre,

accessibles immdiatement par le processeur. Ce sont les registres. On trouve ensuite le cache ou

ant-mmoire. Accessible en quelques cycles d'horloge (1 ou 2 en gnral) il contient quelques

dizaines de milliers de mots. On a ensuite la mmoire principale ou mmoire centrale. On dispose

parfois d'une mmoire d'appui ou d'arrire-plan, intermdiaire entre la mmoire centrale et les

mmoires auxiliaires. Elle est constitue de circuits semi-conducteurs de faible prix, dont la

vitesse est faible pour des circuits de mmoire mais cent fois plus leve que celle des disques

magntiques. Toutes ces mmoires sont volatiles.

Les disques magntiques forment le niveau suivant (mmoires auxiliaires ou mmoires de

masse) et constituent une mmoire permanente dont les donnes restent valides quand on coupe

l'alimentation lectrique. Le dernier niveau correspond l'archivage des donnes. Jusqu' prsent

ce domaine tait l'exclusivit des bandes magntiques. Ces dernires annes ont vu apparatre un

nouveau produit qui peut dans certains cas fournir une alternative pour l'archivage. Il s'agit du

disque optique numrique. Celui-ci a des densits de stockage de 10

2

10

4

fois suprieures

celles des supports magntiques, pour des temps d'accs cinq dix fois plus grand.

La figure suivante schmatise cette hirarchie des mmoires :

mmoire centrale

mmoire d'appui

bande magntique disque optique

registres

cache

mmoire permanente : disque dur

cot

capacit

Figure 10

I.3.e Bus : le squelette des ordinateurs

Un bus est un moyen de communication entre les diffrents lments constituant une

machine. Il s'agit en gnral d'un ensemble de fils lectriques. Les diffrents lments sont relis

au bus par des connecteurs, dont l'ensemble constitue un fond de panier. Chaque emplacement

(slot) du fond de panier (backplane) peut recevoir une carte lectronique (board). Sur un bus

circulent diffrents types de signaux : adresses, donnes, contrle, alimentations, etc

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 16

I.3.f Entres/Sorties

Pour pouvoir excuter une tche, l'ordinateur doit disposer du programme et des donnes

(s'il y a lieu) qui s'y rfrent. Ds que le travail est accompli, les rsultats du traitement sont

communiqus l'utilisateur. Les techniques d'change d'informations entre l'ordinateur et son

environnement externe sont appeles techniques d'Entres/Sorties (E/S ou I/O pour

Input/Output). L'ordinateur change des informations non seulement avec des oprateurs

humains, par l'intermdiaire de terminaux de communication (consoles avec clavier, souris,

imprimantes, lecteurs, etc), mais galement avec des dispositifs varis : appareils de mesures,

capteurs, etc

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 17

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 18

Portes logiques et algbre de Boole

II.1 Systmes binaires

Actuellement, alors que les ordinateurs analogiques restent du domaine de la recherche,

les informations traites par les systmes informatiques sont codes sous forme binaire. Un

systme binaire (signal, circuit, etc) est un systme qui ne peut exister que dans deux tats

autoriss. Le circuit de la figure 1 est un exemple plus que simpliste de circuit binaire : selon que

l'interrupteur S est ouvert ou ferm la tension V

0

ne peut tre gale qu' +5 V ou 0 V.

R

+5V

S

V

0

Figure 1

La ralit technique est un peu plus complexe avec des interrupteurs commands raliss par des

transistors. Diverses notations peuvent tre utilises pour reprsenter ces deux tats :

numrique : 1 et 0 (bit : binary digit)

logique : vrai et faux (true et false)

oui et non (yes et no)

physique : ouvert et ferm

ON et OFF

haut et bas (HI et LO, H et L, H et B)

Pour tudier les fonctions de variables binaires on utilise une algbre dveloppe au

XIX

me

sicle par un mathmaticien anglais : Georges Boole. Dans ce chapitre nous nous

proposons de prsenter les fonctions de base de l'algbre boolenne ainsi que leurs

reprsentations symboliques en lectronique. Nous rappellerons galement, sans prtendre la

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 19

rigueur mathmatique, les quelques notions lmentaires ncessaires l'tude des circuits

lectroniques.

L'algbre de Boole concerne la logique des systmes binaires. Une variable boolenne ne

peut prendre que deux valeurs possibles 0 ou 1. En lectronique les deux tats d'une telle variable

peuvent tre associs deux niveaux de tension : V(0) et V(1) pour les tats 0 et 1

respectivement. On distingue les logiques positive et ngative selon que V(1) > V(0) ou

V(1) < V(0). Ce que nous pouvons rsumer dans la table suivante donnant la signification logique

des niveaux physiques :

Niveau Logique positive Logique ngative

H 1 0

L 0 1

Table 1

En pratique un niveau est dfini par un domaine en tension ou en courant. Par exemple en

technologie TTL, un niveau sera dit haut s'il est compris entre +2 V et +5 V et un niveau sera bas

s'il est infrieur +0.8 V. Dans la plage intermdiaire, ltat est indtermin. Si les transitions

sont invitables, il est indispensable de traverser cette plage intermdiaire le plus rapidement

possible. Dautre part, les signaux doivent tre stabiliss avant dtre pris en compte par les

circuits. Il y a donc des contraintes temporelles, spcifies par les chronogrammes des feuilles de

donnes (data sheets) fournis par les constructeurs. Dans ce cours, destin des informaticiens,

nous naborderons que trs peu cet aspect pratique de llectronique.

V(1)

V(0)

V(1)

V(0)

Logique positive Logique ngative

"0"

"1" "0"

"1"

Figure 2

Nous verrons que dans certains cas (supports magntiques, lignes de transmission, disques

optiques, etc.) linformation peut tre porte par les transitions entre deux tats.

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 20

II.2 Porte OU (inclusif)

L'opration OU (OR), encore appele addition logique, a au moins deux entres. La sortie

d'une fonction OU est dans l'tat 1 si au moins une de ses entres est dans l'tat 1. La fonction

OU, note +, est reprsente par le symbole indiqu sur la figure 3 et est dfinie par la table de

vrit suivante :

A B Y = A + B

0 0 0

0 1 1

1 0 1

1 1 1

Table 2

Une table de vrit donne pour toutes les combinaisons possibles des variables logiques en entre

X, ici X = (A, B), la valeur de la fonction logique f (X).

A

B

Y

Figure 3

Il est facile de vrifier les proprits suivantes de la fonction OU :

(A + B) + C = A + (B + C) = A + B + C Associativit

A + B = B + A Commutativit

A + A = A Idempotence

A + 0 = A Elment neutre

A + 1 = 1 Elment absorbant

II.3 Porte ET

L'opration ET (AND), encore dnomme produit logique ou intersection, a au moins

deux entres. La sortie d'une fonction AND est dans l'tat 1 si et seulement si toutes ses entres

sont dans l'tat 1. La fonction ET, note , est reprsente par le symbole indiqu sur la figure 4 et

est dfinie par la table de vrit suivante :

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 21

A B Y = A B

0 0 0

0 1 0

1 0 0

1 1 1

Table 3

A

B

Y

Figure 4

Il est facile de vrifier les proprits suivantes de la fonction ET :

(A B) C = A (B C) = A B C Associativit

A B = B A Commutativit

A A = A Idempotence

A 1 = A Elment neutre

A 0 = 0 Elment absorbant

D'autre part, les oprations ET et OU sont distributives l'une par rapport l'autre :

A (B + C) = (A B) + (A C) Distributivit du ET sur le OU

A + (B C) = (A + B) (A + C) Distributivit du OU sur le ET

Mentionnons galement les proprits dabsorption :

A + (A B) = A

A (A + B) = A

En effet :

A + (A B) = (A 1) + (A B) = A (1 + B) = A 1 = A

A (A + B) = (A A) + (A B) = A + (A B) = A

II.4 Inverseur : porte NON

L'opration NON (NOT) a une seule entre et une seule sortie. La sortie d'une fonction

NON prend l'tat 1 si et seulement si son entre est dans l'tat 0. La ngation logique est

symbolise par un petit cercle dessin l'endroit o une ligne en entre ou en sortie rejoint un

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 22

symbole logique, comme par exemple sur la figure 5. La table 4 donne la table de vrit

correspondante.

A

Y = A

0 1

1 0

Table 4

A Y

Figure 5

A partir des dfinitions des fonctions NON, OU et ET nous pouvons dduire :

( ) B A B A A

0 A A

1 A A

A A

+ = +

=

= +

=

II.5 Thormes de De Morgan

De Morgan a exprim deux thormes qui peuvent se rsumer sous la forme suivante :

... C B A ... C B A

... C B A ... C B A

= + + +

+ + + =

Pour vrifier le premier thorme nous remarquons que si toutes les entres sont 1 les deux

membres de l'quation sont nuls. Par contre si une au moins des entres est 0 les deux membres

de l'quation sont gaux 1. Il y a donc galit quels que soient les tats des diverses entres. Le

second thorme se vrifie de la mme manire : si toutes les entres sont 0 les deux membres

de l'quation sont 1, par contre si au moins une des entres est 1 les deux expressions sont 0.

Les thormes de De Morgan montrent qu'une fonction ET peut tre fabrique partir des

fonctions OU et NON. De mme une fonction OU peut tre obtenue partir des fonctions ET et

NON. La figure 6 montre la conversion d'une porte OU en porte ET et rciproquement, utilisant

le fait que :

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 23

B A B A B A

B A B A B A

= = +

+ = + =

De mme, partir des thormes de De Morgan nous pouvons montrer qu'une porte ET en

logique positive fonctionne comme une porte OU en logique ngative et vice versa.

A+B

A

B

A

B

A.B

A

B

A.B

A

B

A+B

Figure 6

II.6 Portes NON ET et NON OU

Une porte NON ET (NAND : NOT AND) est constitue par un inverseur la sortie d'une

porte ET (fig. 7). Une ngation la sortie d'une porte OU constitue une fonction NON OU

(NOR : NOT OR) symbolise sur la figure 8. Leurs tables de vrit respectives sont donnes par

les tables 5 et 6 :

A B

B A Y =

A B

B A Y + =

0 0 1 0 0 1

0 1 1 0 1 0

1 0 1 1 0 0

1 1 0 1 1 0

Table 5

Table 6

A

B

Y

Figure 7

A

B

Y

Figure 8

Comme les transistors qui interviennent comme lments de base des portes sont par

essence des inverseurs, les portes NAND et NOR sont trs usites dans la ralisation des circuits

logiques. Grce aux lois de De Morgan il est possible de raliser des systmes logiques avec

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 24

uniquement des portes NAND ou NOR. La figure 9 montre, par exemple, comment les portes

NOT, OR et AND peuvent tre obtenues partir de portes NOR.

Y=A.B

A

B

A Y=A

A

B

Y=A+B

Figure 9

II.7 Porte OU exclusif

La sortie d'une fonction OU exclusif (XOR) deux entres est dans l'tat 1 si une entre et

seulement une est dans l'tat 1. La reprsentation symbolique d'une fonction XOR (note ) est

donne sur la figure 10 et sa table de vrit est la suivante :

A B B A Y =

0 0 0

0 1 1

1 0 1

1 1 0

Table 7

A

B

Y

Figure 10

Nous pouvons formuler de diverses manires la dfinition prcdente : Y est gal 1 si

et seulement si A = 1 ou B = 1 mais pas simultanment. Ce que nous pouvons crire :

B A =

) B A ( ) B A ( B A + =

Nous pouvons encore dire est gal 1 si A = 1 et B = 0 ou si B = 1 et A = 0. Soit : B A Y =

) A B ( ) B A ( B A + =

Une fonction XOR fournit un comparateur d'ingalit : B A Y = ne vaut 1 que si A et B sont

diffrents. Si A et B sont gaux 1 ou si A et B sont gaux 0 alors Y = 0. Ce qui s'crit :

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 25

) B A ( ) B A ( B A + =

La fonction B A Y Z = = correspond un dtecteur d'galit. Nous avons encore la relation

suivante qui peut tre dmontre en utilisant les thormes de De Morgan :

) B A ( ) B A ( B A + + =

A ces quatre relations logiques correspondent quatre circuits ralisant la fonction XOR partir de

portes OR et AND.

A

B

A

B

A

B

A

B

Figure 11

Mentionnons galement quelques proprits faciles vrifier :

B A B A B A

B A B A

A 1 A

A 0 A

1 A A

0 A A

= =

=

=

=

=

=

II.8 Porte Trois Etats

La porte "3 tats", ou "tri-state", n'est pas une porte logique au sens strict. Elle est

principalement utilise pour connecter une sortie sur une ligne commune plusieurs circuits (un

bus par exemple). Elle remplace gnralement une porte ET. En effet, la mise en parallle sur une

mme ligne de plusieurs portes ET introduit des capacits parasites. Ceci augmente les constantes

de temps et a pour effet de dtriorer les fronts de monte et de descente des signaux. Cela peut

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 26

perturber le fonctionnement d'un systme. Une porte 3 tats est schmatise sur la figure

suivante :

A Y

C

Figure 12

C A Y sortie

1 0 0 faible impdance

1 1 1 faible impdance

0 X 0 haute impdance

Table 8

Lorsque la commande C est 0 l'impdance de sortie est trs grande : pratiquement dconnecte.

D'autre part, ces portes "3 tats" fournissent une amplification de puissance.

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 27

II.9 Rsum des identits boolennes de base

Il est possible de montrer que toute fonction boolenne d'un nombre quelconque de

variables peut s'crire avec les trois fonctions de base ET, OU et NON. Nous avons rassembl

dans la table 9 des relations de base de l'algbre de Boole qui nous seront utiles par la suite.

OU (A + B) + C = A + (B + C) = A + B + C

A + B = B + A

A + A = A

A + 0 = A

A + 1 = 1

Associativit

Commutativit

Idempotence

Elment neutre

Elment absorbant

ET (A B) C = A (B C) = A B C

A B = B A

A A = A

A 1 = A

A 0 = 0

Associativit

Commutativit

Idempotence

Elment neutre

Elment absorbant

Distributivit A (B + C) = (A B) + (A C)

A + (B C) = (A + B) (A + C)

NON

A A =

1 A A = +

0 A A =

A + (A B) = A

A (A + B) = A

A ) B A ( ) B A ( = + +

B A ) B A ( A + = +

De Morgan

... C B A ... C B A

... C B A ... C B A

= + + +

+ + + =

OU exclusif

) B A ( ) B A ( B A + =

) A B ( ) B A ( B A + =

) B A ( ) B A ( B A + =

) B A ( ) B A ( B A + + =

B A B A B A

B A B A

A 1 A

A 0 A

1 A A

0 A A

= =

=

=

=

=

=

Table 9

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 28

II.10 Ecritures canoniques d'une fonction logique

II.10.a Somme canonique de produits

Considrons trois variables boolennes x, y et z. A partir de ces trois variables nous

pouvons construire huit produits logiques (ou minterms) P

i=0,7

faisant intervenir x ou x , y ou y

et z ou z . Pour chacune des huit combinaisons C

i=0,7

(000, 001, 010, etc) des variables x, y et

z, nous pouvons calculer les valeurs de ces produits. Celles-ci sont rassembles dans la table 10.

Chacun de ces produits prend la valeur 1 pour une et une seule combinaison : P

i

vaut 1

uniquement pour la combinaison C

i

et 0 pour les autres combinaisons.

P

0

P

1

P

2

P

3

P

4

P

5

P

6

P

7

C

i

x y z

z y x

z y x

z y x

z y x

z y x

z y x

z y x

z y x

0 0 0 0 1 0 0 0 0 0 0 0

1 0 0 1 0 1 0 0 0 0 0 0

2 0 1 0 0 0 1 0 0 0 0 0

3 0 1 1 0 0 0 1 0 0 0 0

4 1 0 0 0 0 0 0 1 0 0 0

5 1 0 1 0 0 0 0 0 1 0 0

6 1 1 0 0 0 0 0 0 0 1 0

7 1 1 1 0 0 0 0 0 0 0 1

Table 10

Pour toute fonction logique de trois variables x, y et z, nous pouvons crire sa table de

vrit, c'est--dire expliciter sa valeur pour chacune des huit combinaisons C

i

. Considrons, par

exemple, la fonction F dont la table de vrit est donne dans la table 11 :

C

i

x y z F P

1

+ P

3

+ P

4

0 0 0 0 0 0

1 0 0 1 1 1

2 0 1 0 0 0

3 0 1 1 1 1

4 1 0 0 1 1

5 1 0 1 0 0

6 1 1 0 0 0

7 1 1 1 0 0

Table 11

Cette fonction F prend la valeur 1 pour la combinaison C

1

comme le produit P

1

, la combinaison

C

3

comme P

3

et la combinaison C

4

comme P

4

. La fonction F prenant la valeur 0 pour toutes les

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 29

autres combinaisons comme les produits P

1

, P

3

, P

4

, nous pouvons donc crire que F est gale la

fonction :

F = P

1

+ P

3

+ P

4

Nous pouvons vrifier cette identit dans la table 11. Nous pouvons donc exprimer F en fonction

des variables x, y et z sous la forme :

z y x z y x z y x F + + =

Cette faon, trs gnrale, d'crire une fonction boolenne est appele somme canonique de

produits.

II.10.b Produit canonique de sommes

Soient encore trois variables binaires x, y et z. Nous pouvons dfinir huit sommes

logiques des trois variables faisant intervenir x ou x , y ou yet z ou z . La table 12 donne les

tables de vrit de ces sommes. Nous constatons que chacune de ces fonctions prend la valeur 0

pour une et une seule combinaison.

S

0

S

1

S

2

S

3

S

4

S

5

S

6

S

7

C

i

x y z

z y x + +

z y x + + z y x + + z y x + + z y x + + z y x + +

z y x + +

z y x + +

0 0 0 0 0 1 1 1 1 1 1 1

1 0 0 1 1 0 1 1 1 1 1 1

2 0 1 0 1 1 0 1 1 1 1 1

3 0 1 1 1 1 1 0 1 1 1 1

4 1 0 0 1 1 1 1 0 1 1 1

5 1 0 1 1 1 1 1 1 0 1 1

6 1 1 0 1 1 1 1 1 1 0 1

7 1 1 1 1 1 1 1 1 1 1 0

Table 12

Reprenons l'exemple prcdent de la fonction F. Celle-ci vaut 0 pour les combinaisons

C

0

, C

2

, C

5

, C

6

et C

7

en mme temps que S

0

, S

2

, S

5

, S

6

et S

7

. La fonction F peut donc tre vue

comme le produit logique de ces cinq sommes, ce qui est vrifi dans la table 13. Nous pouvons

donc exprimer la fonction F sous la forme suivante :

) z y x ( ) z y x ( ) z y x ( ) z y x ( ) z y x ( F + + + + + + + + + + =

Cette criture est appele produit canonique de sommes. Celle-ci est moins utilise que la somme

canonique de produits.

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 30

C

i

x y z F S

0

S

2

S

5

S

6

S

7

0 0 0 0 0 0

1 0 0 1 1 1

2 0 1 0 0 0

3 0 1 1 1 1

4 1 0 0 1 1

5 1 0 1 0 0

6 1 1 0 0 0

7 1 1 1 0 0

Table 13

II.11 Simplification de l'criture des fonctions logiques

II.11.a Simplification algbrique

Simplifier une expression boolenne c'est lui trouver une forme plus condense, faisant

intervenir moins d'oprateurs et conduisant une ralisation matrielle plus compacte. On peut

simplifier une fonction par manipulation algbrique en utilisant par exemple les relations

rassembles dans la table 9. Considrons la fonction F dfinie par la table de vrit suivante :

x y z F

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 1

1 1 1 1

Table 14

Nous en dduisons sa forme canonique somme de produits :

z y x z y x z y x z y x F + + + =

Nous pouvons crire :

x z z y y x

) z z ( y x ) y y ( z x ) x x ( z y

) z y x z y x ( ) z y x z y x ( ) z y x z y x (

z y x z y x z y x z y x F

+ + =

+ + + + + =

+ + + + + =

+ + + =

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 31

Cependant cette mthode, qui demande astuce et chance, n'est pas toujours trs aise mettre en

uvre. Nous allons maintenant dcrire une mthode graphique trs utile pour un nombre de

variables infrieur 6.

II.11.b Tableaux de Karnaugh

La mthode de simplification de Karnaugh repose sur l'identit :

A ) B B ( A ) B A ( ) B A ( = + = +

Elle est base sur l'inspection visuelle de tableaux disposs de faon telle que deux cases

adjacentes en ligne et en colonne ne diffrent que par l'tat d'une variable et une seule.

Si une fonction dpend de n variables il y a 2

n

produits possibles. Chacun de ces produits

est reprsent par une case dans un tableau. Les figures suivantes donnent la structure des

tableaux de Karnaugh pour 2, 3, 4 et 5 variables. Observez comment sont numrotes les lignes et

les colonnes : d'une case sa voisine une seule variable change d'tat. Pour 5 variables, deux

reprsentations sont possibles. Dans ce cas le tableau de Karnaugh peut tre trait comme deux

tableaux 4x4 superposs (fig. 15) ou un seul tableau de 4x8 (fig. 16).

0 1

0

1

x

y

Tableau 2 variables

Figure 13

xy

z 00 01 11 10

0

1

Tableau 3 variables

Figure 14

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 32

xy

zt 00 01 11 10

00

01

11

10

Tableau 4 variables

Figure 15

00

01

11

10

00 01 11 10 zt

xy

00

01

11

10

00 01 11 10 zt

xy

u

0 1

Tableau 5 variables

Figure 16

xyz

tu 000 001 011 010 110 111 101 100

00

01

11

10

Tableau 5 variables

Figure 17

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 33

Chaque case d'un tableau correspond au seul minterm prenant la valeur 1 pour la combinaison

identifie par la ligne et la colonne. Par exemple les trois cases colories dans les tableaux de la

figure 18 correspondent respectivement aux produits suivants :

t z y x et t z y x , t z y x

Il faut comprendre chaque ligne et chaque colonne comme une structure cyclique continue :

chaque case a toujours quatre voisins qu'il faut ventuellement chercher l'autre extrmit de la

ligne ou de la colonne. Les tableaux de la figure 18 illustrent ce concept, les croix y matrialisent

les voisins des cases colories :

00

01

11

10

00 01 11 10 zt

xy

00

01

11

10

00 01 11 10 zt

xy

00

01

11

10

00 01 11 10 zt

xy

Figure 18

Dans le cas de 5 variables chaque case possde cinq voisins. Dans la reprsentation en

tableaux superposs, quatre voisins se situent dans le mme plan et le cinquime " la verticale"

dans l'autre plan. Pour la reprsentation plane de 8 colonnes il faut "replier" le tableau par rapport

la ligne mdiane sparant les colonnes 010 et 110, qui dfinit un axe de symtrie. La figure 19

illustre les 5 cases voisines de la case 10101.

xyz

tu 000 001 011 010 110 111 101 100

00

01

11

10

Figure 19

Le passage de la table de vrit au tableau de Karnaugh consiste remplir chaque case

avec la valeur de la fonction pour le produit correspondant. Il est possible de ne copier que les 1.

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 34

La mthode de simplification de Karnaugh consiste rassembler les cases adjacentes

contenant des 1 par groupes de 2, 4 ou 8 termes. Considrons en effet le groupement vertical de

deux cases, en rouge, de la figure 20. Il correspond la somme de deux termes :

t y x t y x G + =

Il est possible de factoriser le produit x y :

y x ) t t ( y x G = + =

La variable t qui prend les deux valeurs 0 et 1 dans le groupement disparat. Il ne reste que le

produit des variables x et y, qui gardent ici la valeur 1.

Dans un groupement de deux termes on limine donc la variable qui change d'tat et on

conserve le produit des variables qui ne changent pas. Dans un groupement de quatre on limine

les deux variables qui changent d'tat. Dans un groupement de huit on limine trois variables,

etc

On cherche avoir le minimum de groupements, chaque groupement rassemblant le

maximum de termes. Une mme case peut intervenir dans plusieurs groupements car C + C = C.

C'est le cas de la case jaune sur la figure 20.

Pour les cases isoles on ne peut liminer aucune variable. On conserve donc le produit

caractrisant la case. L'expression logique finale est la runion des groupements aprs limination

des variables qui changent d'tat.

Reprenons l'exemple de la fonction F dfinie par la table de vrit 14. La figure 20 donne

le tableau de Karnaugh correspondant :

xy

t

0

1

00 01 11 10

1 1

1

1 xt

yt

xy

Figure 20

Nous y observons trois groupements de deux termes, nous pouvons crire pour la fonction :

x z z y y x F + + =

Nous retrouvons le rsultat prcdent.

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 35

Considrons une autre fonction F de quatre variables x, y, z et t dfinie par la table 15. La

figure 21 donne le tableau de Karnaugh quivalent. Sur cette figure nous avons galement

matrialis les trois groupements possibles : deux groupements de quatre termes, dont un

contenant les quatre coins, et un groupement de deux termes. Cette mthode nous permettent

d'crire :

t z y t y y x F + + =

x y z t F

0 0 0 0 1

0 0 0 1 0

0 0 1 0 1

0 0 1 1 0

0 1 0 0 0

0 1 0 1 1

0 1 1 0 0

0 1 1 1 0

1 0 0 0 1

1 0 0 1 1

1 0 1 0 1

1 0 1 1 1

1 1 0 0 0

1 1 0 1 1

1 1 1 0 0

1 1 1 1 0

Table 15

00 01 11 10

00

01

11

10

xy

zt

1

1

1

1

1

1 1

1

Figure 21

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 36

II.12 Symboles logiques normaliss IEEE/ANSI

Nous utilisons dans ce cours les symboles logiques standards encore trs frquemment

rencontrs dans lindustrie de llectronique numrique. Cependant un ensemble de nouveaux

symboles normaliss a t introduit en 1984. Il sagit de la norme IEEE/ANSI 91-1984. Cette

nouvelle norme a pour objectif de faciliter la reprsentation de circuits intgrs plus compliqus

que les simples portes que nous utilisons ici.

Pour tre le plus complet possible nous prsentons ici un extrait de ces symboles normaliss :

Porte OU

1

Porte ET

&

Porte NON

1

Porte OU exclusif

= 1

Figure 22

II.13 Entre trigger de Schmitt

Nous avons mentionn au dbut de ce chapitre que les niveaux haut et bas sont souvent

caractriss par deux seuils en tension et sont spars par une bande indtermine. Les fronts

montants et descendants des signaux doivent alors tre suffisamment rapides de manire

traverser cette zone de basculement le plus vite possible. Sinon nous pouvons observer des

indterminations avec des oscillations. Cest ce que nous observons sur le chronogramme

schmatis sur la figure 24. Il reprsente la variation de la sortie Y (en bas) en fonction du signal

dentre X (en haut) dun circuit logique trs simple. Nous avons schmatis des fronts lents et

des parasites. Le signal de sortie ne correspond pas ce que nous voudrions.

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 37

X Y

Figure 23

P

I P I

Figure 24

Pour viter ces problmes nous pouvons utiliser un "Trigger de Schmitt" qui dclenche sur deux

seuils diffrents selon que le signal monte ou descend. Cest ce que nous avons schmatis sur la

figure 25. La transition 0 1 du signal de sortie est provoque par un signal en entre montant et

passant au-dessus du seuil haut V

H

. La transition 1 0 du signal de sortie est provoque par un

signal en entre descendant et passant au-dessous du seuil bas V

B

. De cette faon nous obtenons

un signal de sortie conforme nos vux et exempt de parasites.

Figure 25

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 38

Les circuits logiques pour lesquels les entres sont filtres par un trigger de Schmitt sont

identifis par le symbole prsent sur la figure 26. Celui-ci est ajout lintrieur du symbole de

la porte considre.

X Y

Figure 26

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 39

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 40

Logique combinatoire

Dans ce chapitre nous nous intressons une famille de circuits logiques pour lesquels la

sortie dpend uniquement des tats des entres.

III.1 Addition binaire

III.1.a Demi-additionneur

Addition et soustraction sont deux oprations arithmtiques de base. Commenons par

l'addition de deux nombres binaires, la soustraction sera tudie dans le prochain paragraphe. En

base 2 l'addition de deux bits s'crit :

= +

= +

= +

= +

10 1 1

01 0 1

01 1 0

00 0 0

Comme en dcimal, nous devons donc tenir compte d'une ventuelle retenue (carry). La figure 1

montre la dcomposition de l'addition de deux nombres binaires de quatre bits.

a

3

a a a

0 1 2

b b b b

3 2 1 0

s

3 2 1 0

s s s

r

3 2 1 0

r r r

nombre A

nombre B

somme : S = A + B

retenues

+

Figure 1

L'addition des deux bits de plus bas poids (LSB : Least Significant Bit) a

0

et b

0

, donne un rsultat

partiel s

0

et une retenue r

0

. On forme ensuite la somme des deux bits a

1

et b

1

et de la retenue r

0

.

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 41

Nous obtenons un rsultat partiel s

1

et une retenue r

1

. Et ainsi de suite, nous obtenons un rsultat

sur quatre bits S et une retenue r

3

.

Considrons la cellule symbolise sur la figure 2, comptant deux entres A et B, les deux bits

sommer, et deux sorties D le rsultat de la somme et C la retenue.

A B

HA

C D

Figure 2

Ce circuit, qui permettrait d'effectuer l'addition des deux bits de plus bas poids est appel demi-

additionneur (Half-Adder). Ecrivons la table de vrit de celui-ci :

A B C D

0 0 0 0

0 1 0 1

1 0 0 1

1 1 1 0

Table 1

Si nous crivons ces deux fonctions sous leur forme canonique il vient :

=

+ =

B A C

B A B A D

Nous reconnaissons pour la sortie D une fonction OU exclusif, donc :

=

=

B A C

B A D

Ce qui peut tre ralis par le circuit schmatis sur le logigramme de la figure 3.

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 42

A

B

D

C

Figure 3

III.1.b Additionneur

Il faut en fait tenir compte de la retenue des bits de poids infrieurs, un circuit

additionneur doit donc comporter trois entres et deux sorties, comme reprsent sur la figure 4.

A B

FA

C S

R

Figure 4

Ce serait possible en combinant deux demi-additionneurs comme prsent par la figure 5. En

pratique pour minimiser le nombre de composants, ou de portes dans un circuit intgr, un tel

additionneur est ralis directement.

HA

HA

C

2

C

S

1

1

R

A

B

S

C

Figure 5

Les entres A et B reprsentent les bits additionner et R le report de la retenue de l'addition des

bits de poids infrieurs. La sortie S reprsente le rsultat de la somme et C la retenue. La table de

vrit de ce circuit est la suivante :

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 43

A B R S C

0 0 0 0 0

0 0 1 1 0

0 1 0 1 0

0 1 1 0 1

1 0 0 1 0

1 0 1 0 1

1 1 0 0 1

1 1 1 1 1

Table 2

A partir de cette table nous pouvons crire pour S et C les expressions boolennes suivantes :

+ + + =

+ + + =

R B A R B A R B A R B A C

R B A R B A R B A R B A S

Nous pouvons simplifier l'expression de C en utilisant un tableau de Karnaugh :

AB

R 00 01 11 10

0

1 1

1

1 1

Figure 6

Nous en dduisons :

C = A B + A R + B R

Le bit de carry est gal 1 si au moins deux des entres sont 1. D'autre part, nous pouvons

remarquer qu'intervertir les 0 et les 1 dans la table 2 revient permuter les lignes 1 et 8, 2 et 7, 3

et 6, 4 et 5. La table de vrit reste globalement invariante par inversion des entres et des sorties,

nous avons donc :

R B R A B A C + + =

A partir de cette relation, qui peut galement tre dmontre en appliquant lalgbre de Boole,

nous pouvons crire :

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 44

=

+ + = + + =

=

R B A C R

R B A R B A R B A C ) R B A ( R B A C B

R B A C A

Ce qui nous permet de rcrire l'expression de S :

R B A C ) R B A ( S + + + =

La figure 7 donne un exemple de ralisation d'un additionneur 1 bit bas sur deux portes AOI

(AND OR INVERT), c'est--dire un ensemble de portes ET suivies d'une porte NON-OU.

A B R

S

C

Figure 7

III.1.c Addition en parallle

L'addition de nombres comptant plusieurs bits peut se faire en srie (bit aprs bit) ou en

parallle (tous les bits simultanment). La figure 8 montre l'exemple d'un additionneur 4 bits

comptant quatre "Full Adders", comparables celui schmatis figure 7, monts en parallle ou

en cascade. Chaque additionneur FA

i

est affect l'addition des bits de poids i. L'entre

correspondant au report de retenue pour FA

0

est impose 0 (en logique positive). La retenue

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 45

finale C indique un dpassement de capacit si elle est gale 1. Le temps d'tablissement du

rsultat correspondant au temps de propagation des retenues au travers des diverses cellules. Si t

est le temps rponse d'une cellule, la sortie S

0

et la retenue R

0

sont valables aprs un retard t, la

sortie S

1

et la retenue R

1

ne sont correctes qu'aprs un retard 2 t, et ainsi de suite. La figure 9

prsente un exemple de ralisation logique d'un additionneur de deux mots de 2 bits.

A B

FA

C S

3

3 3

3

FA

2

FA

1

FA

0

A A A

2 1 0

B B B

2 1 0

S S S

0 1 2

Figure 8

R A B

0 0

A

1 1

B

S

0

S

1

C

1

Figure 9

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 46

III.1.d Addition squentielle

Dans un additionneur squentiel chacun des nombres A et B est reprsent par un train

d'impulsions (figure 10) synchrones par rapport un signal d'horloge. L'ordre chronologique

d'arrive des impulsions correspond l'ordre croissant des poids : le bit le moins significatif se

prsentant le premier. Ces impulsions sont injectes sur les deux lignes d'entre d'un additionneur

(figure 11). A chaque cycle d'horloge, la retenue provenant des bits de poids infrieurs doit tre

mmorise (par exemple, l'aide d'une bascule D qui sera tudie dans le chapitre suivant).

Un additionneur parallle est plus rapide mais ncessite plus de composants.

A = 01101

B = 01011

D = 11000

LSB

2

0

2 2 2 2

2 3 4 1

t

Figure 10

A B

FA

C S

R

TD

Figure 11

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 47

III.2 Soustraction

III.2.a Demi-soustracteur

La table de vrit pour un demi-soustracteur (ne tenant pas compte d'une ventuelle

retenue provenant des bits de poids infrieurs) est la suivante :

A B D C

0 0 0 0

0 1 1 1

1 0 1 0

1 1 0 0

Table 3

O D reprsente le rsultat de la soustraction A B et C la retenue. Nous en dduisons les

expressions logiques dfinissant D et C :

=

= + =

B A C

B A B A B A D

et le schma correspondant :

A

B

D

C

Figure 12

Nous pourrions maintenant tudier un soustracteur prenant en compte la retenue. Nous

allons plutt tirer parti de certaines proprits de la numration binaire pour traiter de la mme

manire l'addition et la soustraction.

III.2.b Additionneur-soustracteur

Nous savons qu'avec un mot de n bits nous pouvons reprsenter un entier positif dont la

valeur est comprise entre 0 et 2

n

1. Le complmentaire d'un mot de n bits est obtenu entre

prenant le complment de chacun des n bits. Ainsi, si nous sommons un nombre et son

complment nous obtenons un mot dont tous les bits sont 1. C'est--dire :

1 2 A A

n

= +

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 48

Attention : dans ce paragraphe le signe + reprsente l'opration addition et non la fonction logique

OU. Nous pouvons encore crire :

n

2 1 A A + =

Mais sur n bits l'entier 2

n

est identique 0 :

) bits n ( 0 2

n

C'est--dire qu'il est possible dcrire un nombre entier ngatif comme le "complment 2" de sa

valeur absolue :

1 A A + =

Nous reviendrons sur les divers codages des entiers signs plus tard. Nous pouvons utiliser cette

proprit pour crire la soustraction de deux mots de n bits sous la forme suivante :

) bits n ( 1 B A 2 1 B A B A

n

+ + + + =

Ce rsultat conduit au schma de principe prsent sur la figure 13 combinant les fonctions

addition et soustraction. Celui-ci est bas sur l'emploi d'un additionneur n bits et d'un

multiplexeur deux lignes d'entre. Nous tudierons ce type de circuit un peu plus loin dans ce

chapitre. Selon le code opration O (0 pour une addition et 1 pour une soustraction) ce

multiplexeur permet de slectionner une des deux entres, B ou son complmentaire. Le code

opration est galement inject sur l'entre report de retenue de l'additionneur. Pour simplifier le

schma et viter de reprsenter n lignes de connexion parallles, on ne matrialise qu'une seule

ligne. Celle-ci est barre et accompagne d'une valeur qui indique le nombre rel de connexions.

n

n

n

n

n

n

1

0

C

D A

B

O

A

D

D

Figure 13

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 49

III.3 Comparaison

On rencontre trs souvent la ncessit de comparer deux entiers (A = B, A > B ou A < B).

Ecrivons la table de vrit correspondant ces trois fonctions de comparaison de 2 bits. La

fonction C doit tre gale 1 si et seulement si A > B, la fonction D si et seulement si A < B et la

fonction E si et seulement si A = B. Ce qui nous donne :

A B C (A > B) D (A < B) E (A = B)

0 0 0 0 1

0 1 0 1 0

1 0 1 0 0

1 1 0 0 1

Table 5

Nous en dduisons les expressions logiques de C, D et E :

+ = + = =

=

=

D C B A B A B A E

B A D

B A C

La figure 14 prsente le diagramme d'un bloc logique comparant deux bits A et B.

A

B

C

E

D

Figure 14

III.4 Contrle de parit

La parit d'un mot binaire est dfinie comme la parit de la somme des bits, soit encore :

- parit paire (ou 0) : nombre pair de 1 dans le mot;

- parit impaire (ou 1) : nombre impair de 1 dans le mot.

La fonction OU-exclusif donne la parit d'un sous-ensemble de deux bits. Le contrle de parit

est bas sur la constatation que le mot de n+1 bits form en adjoignant un mot de n bits son bit

de parit est toujours de parit 0. La figure 15 reprsente le diagramme logique d'un gnrateur-

S. Tisserant ESIL Architecture et Technologie des Ordinateurs - 2003 50

contrleur de parit pour 4 bits. Si l'entre P' est impose 0 ce circuit fonctionne comme

gnrateur de parit : la sortie P reprsente la parit du mot compos par les bits A, B, C et D.

P

A

B

C

D

P'

Figure 15

Le contrle de la parit est utilis, par exemple, pour augmenter la fiabilit d'un systme

de transmission ou de stockage de donnes. La figure 16 montre l'utilisation du circuit prcdent

en gnrateur de parit du ct de l'mission et contrleur de parit du ct de la rception. La

sortie P

2

doit tre 0 pour chaque mot transmis, sinon cela indique un problme de transmission.

Emetteur

A