Professional Documents

Culture Documents

500w Power Amplifier Circuit Diagram

Uploaded by

João AlbertoOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

500w Power Amplifier Circuit Diagram

Uploaded by

João AlbertoCopyright:

Available Formats

Single-Cycle Control Technique sets new Industry Standard for Continuous Conduction Mode PFC Controllers

Frank Athari, Ron Brown, Stephen Oliver International Rectifier, El Segundo, USA.

as presented at PCIM Europe 03

Abstract This paper presents a novel approach for control of high performance Boost

Power Factor Correction (PFC) circuits operating at a fixed frequency in the continuous conduction mode. The complex multiplier and input line voltage sensing circuits required with traditional control methods are eliminated with the proprietary "Single-Cycle Control" (SCC) method where they are replaced with an integration reset technique. The benefits of overall system robustness, improved transient performance, and simplicity are complemented by a 75% reduction in pcb space and component count.

I. INTRODUCTION

Power Factor Correction (PFC) and harmonic current reduction are fast becoming standard requirements in most power supply designs today. The compelling environmental and economic benefits resulting from the use of Power Factor Correction in power supplies has encouraged governing bodies and end customers to demand more widespread use of PFC circuits across a much broader spectrum of power levels and product lines than ever before.

higher performance of the CCM topology with the system cost benefits typically associated with DCM PFC. Simple mathematical derivations will provide clear insight into the theory of the concept. The theory will

then be substantiated by lab results from both a

discrete controller and the first prototype silicon version of the controller. A close comparison of the Single Cycle Control

This is not particularly good news for Power Supply manufacturers given that the cost and complexity of high performance PFC circuits have not changed drastically since the introduction of the first commercially available Continuous Conduction Mode (CCM) PFC controllers. In fact, to this day, the mainstream controllers used in single phase boost (CCM) PFC circuits still use the same scheme developed many years ago. At lower powers or where low cost is critical, the lower efficiency, lower power density Discontinuous Current Mode (DCM) PFC technique is used [Ref 1]. This paper proposes a new industry standard for PFC named Single Cycle Control (SCC). The features of SCC (design simplicity, component count reduction and minimized pcb space) enable the

technique vs. the existing mainstream solution will also demonstrate the dramatic benefits in cost reduction, component count reduction, board space savings and reduced design effort and complexity. Finally a discussion for potential SCC products will be presented.

II. EXISTING SOLUTION

To understand the benefits of the Single Cycle Control scheme better, it is worthwhile to briefly review the existing (CCM) PFC solution. Below is a block diagram of the popular UC3854 controller [ref 2].

there is no sinusoidal current reference per se as the traditional solution.

INTEGRATOR RESET SWITCH CLOCK FLIP FLOP

Vref

VOLTAGE FEEDBACK ERROR AMPLIFIER

+ -

INTEGRATOR w/ RESET

+ + -

S

HIGH SPEED COMPARATOR

R

-

V Feedback

SINGLE CYCLE CONTROL SIMPLIFIED DIAGRAM

+ -

Fig 2 As seen in Fig 2, the heart of the Single Cycle Control is a new proprietary Integrator w/ Reset (IWR) circuit block. This block simply integrates the output voltage of the voltage error amplifier. This integrated ramp signal is then compared to an analog reference voltage generated from the sum of the current and the error voltage. When the integrator ramp reaches the limit set by this internally generated reference voltage, the PWM pulse is immediately terminated. At this time the integrator output is also discharged to zero and held low till the next clock pulse. The name Single Cycle Control simply refers to the cycle-by-cycle operation of the integrator and the generation of the reference signal during each switching cycle.

Fig 1. As seen in Fig 1 the heart of this existing PFC controller is an analog multiplier / divider. In order to force the input current to follow the input voltage, the multiplier circuit samples the rectified AC line voltage and creates a sinusoidal current reference signal. This signal then controls the duty cycle of the main PWM controller, forcing the input current of the Boost converter to follow the sinusoidal shape of the input voltage, thereby providing near unity power factor and reduced current harmonics. Given the sensitivity of the control loop and the multiplier block, any distortion or noise injected into the inputs can have a negative impact on the power factor and harmonic distortion of the input current. PCB layout issues also play an important role, as does the selection of the components and their optimum values. It is not uncommon to have several design iterations of the control circuit in order to get optimum performance throughout the full line and load range. A well-designed (CCM) PFC circuit requires strong power engineering background both in practice and theory.

IV. MATHEMATICAL DERIVATION

The essential goal of any PFC control system is to force the converter to appear as a resistive load across the AC Line. Following this simple derivation, it can be seen why the new solution is simpler, more robust, less noise sensitive and yet provides the same high level of performance as the older CCM designs. For the avid reader more extensive analysis and theory is available (Ref 3).

III. SINGLE CYCLE CONTROL

The proprietary SCC technique has an elegant and simplistic approach, which does not require a multiplier to create the current reference signal. In fact

SUMMING AMPLIFIER

CURRENT SENSE AMPLIFIER

Referring to Fig 3 we start by representing the converter as a simple resistor and expressing he t current and voltage relationships using simple Ohms law, (1) IIN = VIN / R E Where, IIN is the input current VIN is the input Voltage RE is the emulated resistance of converter

RECTIFIED AC IN

I IN

INTEGRATOR RESET SWITCH

CLOCK FLIP FLOP

Vref

VOLTAGE FEEDBACK ERROR AMPLIFIER

+

INTEGRATOR w/ RESET

+ +

S

HIGH SPEED COMPARATOR

R

-

V Feedback

OUTPUT BULK CAP "C O"

SUMMING AMPLIFIER

+

SINGLE CYCLE CONTROL SIMPLIFIED DIAGRAM

RETURN

During the Quasi-Steady State, the boost converter conversion ratio M(d) can be stated as (2) VO / VIN = M(d)

CURRENT SENSE RESISTOR "RS"

FIG 3. SINGLE CYCLE CONTROL BOOST PFC

V. EXPERIMENTAL RESULTS

Combining (1) and (2) and multiplying both sides with the current sense resistor R S gives us (3) RSIIN = vm / M (d) where, vm = R S* VO / R E RS is equivalent current sensing resistor M(d) is voltage conversion ratio of converter Rewriting Equation (3) yields, (4) R SIIN = vm*VIN / VO VO is assumed to remain constant over a line cycle if the output bulk capacitor CO is large enough. If vm is constant in that cycle, IIN is proportional to VIN thus making the converter appear as an emulated resistor. (5) R E = R SVO / vm Discrete Control Board A 1KW 100Khz fixed frequency Boost converter was built to verify the operation of the Single Cycle Control technique. A control board was fabricated using generic discrete components and the performance was validated at 500W and 1KW with 115V-230VAC 60Hz input. Power train components were independently optimized for both 500W and 1KW operation. The 500W breadboard was subsequently used to validate the prototype IRIS51xx silicon (IRIS = International Rectifier Integrated Switcher). The converter input current and voltage waveforms are shown below. THD results are summarized in Table 1 and 2.

FIG 4. INPUT VOLTAGE AND CURRENT 85VAC 500W

CURRENT SENSE AMPLIFIER

Discrete Control Board

In-circuit PF/THD Data w/ IRIS51xx (500W system) VAC 115 230 115 230 115 230 Pout (W) 75 75 150 150 300 300 Power Factor 0.968 0.917 0.988 0.948 0.996 0.978

Table 2.

THD (%) 17.5 21.25 10.5 17.3 5.5 15.4

FIG 5. INPUT VOLTAGE AND CURRENT 230VAC 1KW

Again, these results meet IEC1000-3-2. In-circuit PF / THD Data w/discrete Control VAC 115 230 115 230 Pout (W) 500 500 1000 1000 Power Factor 0.997 0.987 0.998 0.988 Table 1. These results exceed the IEC1000-3-2 specification requirements and show the near unity power factor. VI. EXPERIMENTAL RESULTS IRIS51xx SILICON THD (%) 4.98 9.1 4.75 8.9

VII. SYSTEM DESIGN COMPARISON

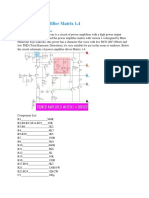

The advantages of the Single Cycle Control method, in terms of required board space, component count, and overall system cost become readily apparent when a side-by-side comparison of a conventional multiplier based solution and an integrated Single Cycle Control method is made as shown in the schematic diagrams below.

Fig 8. Typical UC3854 Application

L1 450UHY CR1 8ETH06 V OUT R4 249k

FIG 6. INPUT VOLTAGE AND CURRENT 85VAC 250W

BR1 BRIDGE 3

R5 249k

H/K

C1 0.47UF, 630V U1 4 2 5 Vcc ISNS COM SW+ VFB COMP 7 1 3

R6 249k

+ C2 470UF, 450V

AC

4

R7 249k

C15 tbd C9 tbd

C4 0.47UF

IRIS51050 + C3 220UF, 35V R9 82.5k

R8 5.23k RTN

R1 0.040, 3W

Fig 9. Typical IRIS51xx Application

Further benefit to the designer presents itself in the form of a simplified design process for the Single

FIG 7 INPUT VOLTAGE AND CURRENT 230V 250W

Cycle Control method. Basic power train selection and design criteria of the SCC IRIS51xx is identical to

that of the UC3854-based solution. The simplification of the design process is attributed to the elimination of the complex multiplier, error amplifier in current loop, and various line sense circuits from the system control loop. Comparison of the converter design procedure for the two methods highlights the true value of the Single Cycle Control methodology.

on the inputs of the m ultiplier and control loops throughout the full power range of the converter. With the new Single Cycle Control technique, the complexity of the multiplier circuit is eliminated and the implementation of the final circuit only requires entry-level understanding of PFC control design. The simplified design procedure is made even easier through the use of custom design software specifically developed for the new Single Cycle Control ICs. Below are typical screen shots of the design software developed for the controller.

VIII. DESIGN PROCEDURE COMPARISON

The comparison below highlights the critical design steps for both the UC3854 and the Single Cycle Control IC.

UC3854 DESIGN PROCEDURE

?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ?? ??

Design/select power circuit components Design/select current sense resistor Design resistive divider for peak current limit Design Enable circuit resistor divider Select IAC resistor, (multiplier setup) Design Vff divider, (multiplier setup) Select Rbias resistor, (multiplier setup) Select Rset resistor, (multiplier setup) Select Rmo resistor, (multiplier setup) Design current error amplifier compensation Design voltage error amplifier compensation Design output voltage feedback divider Design 2 cascaded pole feed forward filter

SINGLE CYCLE CONTROL DESIGN PROCEDURE

?? ?? ??

Design/select power circuit components Design/select current sense resistor Design voltage error amplifier compensation

Comparing the typical circuit schematics in FIG 8 and 9 it is easy to see why the new Single Cycle Control requires a fraction of the design effort compared to the UC3854 solution. Setting up the multiplier and associated control loop circuits is not a trivial task and often requires several iterations due to the interrelated component values in the feedback loop and the multiplier inputs. Once the circuit components are calculated and fully optimized, there still remains the question of layout and the elimination of noise pick up

IX. SINGLE-CYCLE CONTROL POTENTIAL The proprietary SCC PFC opens up an exciting array of possibilities for application developments. The SCC unit can be teamed up with power switches from several different technologies to achieve the optimum tradeoff between high performance and cost effectiveness. For example, at 100kHz, the most cost effective ($/Amp) device for hard switching PFC is an IGBT. If higher efficiencies are required, then HEXFET power MOSFETs or next-generation SuperJunction MOSFETs can be used. It should be noted that - as SCC uses a CCM PFC technique - the choice of boost diode (whether standard low cost ultrafast Si or new SiC devices) plays a major effect on PFC efficiency (due to the energy reflected into the PFC power switch). The SCC technique may be frequency-tuned for a wide variety of application cost and form -factor design parameters. For example, the SCC can be tuned to operate at 70kHz for immediate and easy use in existing low density PFC or the frequency may be increased to several hundreds of kHz to take full advantage of the higher frequency diode and MOSFET technologies, thereby reducing the size / increasing the power density of the application. The ease-of-design benefits (as shown in sections VII and VIII) are complemented by massive reductions in component count and pcb space required for SCC vs. the earlier PFC solutions. In the UC3854 comparison, SCC requires 75% fewer components and takes 75% less pcb space. These major savings also come to light when comparing SCC vs. low cost DCM PFC designs. In a 100W DCM design, the comparison resulted in savings of 60-65% in components and board space when using SCC. In summary, the paper has shown that the features of SCC (design simplicity, component count reduction and minimized pcb space) do indeed enable the higher performance of the CCM topology with the system cost benefits typically associated with DCM PFC.

X. REFERENCES 1. B.Sharifipour, J.S.Huang, P.Liao, L.Huber & M.Jovanovich. Manufacturing and Cost Analysis of power-Factor-Correction Circuits. IEEE 1998. 2. P.Todd. UC3854 Controlled Power Factor Correction Circuit Design. Unitrode Application Note. 3. Z.Lai & K.Smedley. A Family of Power-FactorCorrection Controllers. APEC97, New York. IEEE 1997

You might also like

- High Power Amplifier Matrix 1.4 GuideDocument5 pagesHigh Power Amplifier Matrix 1.4 GuideK Raja SekarNo ratings yet

- Horizontal Circuit TV AnalysisDocument3 pagesHorizontal Circuit TV AnalysiscassfaNo ratings yet

- Class D AmplifierDocument5 pagesClass D AmplifierkothuraNo ratings yet

- Stereo Amplifier Setup GuideDocument34 pagesStereo Amplifier Setup GuideАлександар СтојаноскиNo ratings yet

- Crown - K-Series - k1 - k2 - Full - SM - 2 - Cópia PDFDocument129 pagesCrown - K-Series - k1 - k2 - Full - SM - 2 - Cópia PDFEulerMartinsDeMello100% (1)

- Pa-9312 9324 9336Document2 pagesPa-9312 9324 9336cadatiNo ratings yet

- D2KFB VER.2a.REV.1 PDFDocument2 pagesD2KFB VER.2a.REV.1 PDFDevelop with AcelogicNo ratings yet

- JBL E150P Service ManualDocument28 pagesJBL E150P Service ManualMUHAMMAD SISWANTORO100% (4)

- How To Build The 200 Watts Home Inverter ProjectsDocument6 pagesHow To Build The 200 Watts Home Inverter Projectsgabrielamedelet100% (1)

- 1000 Watts AmpDocument8 pages1000 Watts AmpK Raja SekarNo ratings yet

- 500 Watt AmplifierDocument2 pages500 Watt AmplifierIslami Punjabi Bayan SM Hadi0% (1)

- Infinity BU-120/HTS-20 Powered Subwoofer Service ManualDocument35 pagesInfinity BU-120/HTS-20 Powered Subwoofer Service Manualcoolruler40100% (1)

- Onkyo HT-R 397, HT-S 3900, HTP-395Document82 pagesOnkyo HT-R 397, HT-S 3900, HTP-395testperdidaNo ratings yet

- Circuit Adjustable Bass Filter From 50 HZ To 150 HZ NE5532Document4 pagesCircuit Adjustable Bass Filter From 50 HZ To 150 HZ NE5532Javier Castellanos BarrazaNo ratings yet

- Acoustic Master Service ManualDocument10 pagesAcoustic Master Service Manualcaimanater100% (1)

- WR - DA7 Manual de ServicioDocument86 pagesWR - DA7 Manual de ServicioDanielNo ratings yet

- JL Audio 500 AmpDocument13 pagesJL Audio 500 AmpMarvin Vega100% (1)

- STK 415Document12 pagesSTK 415bbchacinNo ratings yet

- 500w Car Audio Amplifier Circuit DiagramDocument39 pages500w Car Audio Amplifier Circuit DiagrammpcdfNo ratings yet

- J6-S9014 DatasheetDocument2 pagesJ6-S9014 DatasheetOreolNo ratings yet

- Transistor Circuit Diagram of 2sa1943 and 2sc5200Document68 pagesTransistor Circuit Diagram of 2sa1943 and 2sc5200Eliecer GonzalezNo ratings yet

- Class D Ucd Beta01 06.12Document1 pageClass D Ucd Beta01 06.12luizcpimentaNo ratings yet

- 8 Catalogue - 2021 22Document152 pages8 Catalogue - 2021 22Yazhisai SelviNo ratings yet

- Yamaha pc4800n pc9500n PDFDocument86 pagesYamaha pc4800n pc9500n PDFMhooMOoChaappHteenNo ratings yet

- Ecler Pam1400 1000 600 300Document183 pagesEcler Pam1400 1000 600 300Lluis Reparacion ElectronicaNo ratings yet

- Skema Box Speaker LAVOCE - Sistema-F153.14NDocument23 pagesSkema Box Speaker LAVOCE - Sistema-F153.14NZaid DenieNo ratings yet

- Audio Pro AP3000 PDFDocument14 pagesAudio Pro AP3000 PDFCuthbert MarshallNo ratings yet

- MA5002VZ SM 130446-1amplificator ManualDocument140 pagesMA5002VZ SM 130446-1amplificator Manualtiganiada100% (1)

- 25 Watt Mosfet AmplifierDocument4 pages25 Watt Mosfet AmplifierCarlos Alberto NetoNo ratings yet

- HP Pro 3000 Service MapDocument3 pagesHP Pro 3000 Service Mapjeffcan0% (1)

- Roland TD-8 ManualDocument224 pagesRoland TD-8 ManualAnonymous cdQSIU03AQNo ratings yet

- 120 W X 2 Channel Class D Audio Power Amplifier Using IRS20955 and IRF6645Document43 pages120 W X 2 Channel Class D Audio Power Amplifier Using IRS20955 and IRF6645Mazariegôs JJNo ratings yet

- Inter M r150 r300 r500 Power Amplifier Service ManualDocument11 pagesInter M r150 r300 r500 Power Amplifier Service Manualn_hakimNo ratings yet

- Um XP600 1000 2000 2100 3000 3100 5000 5100 en EsDocument28 pagesUm XP600 1000 2000 2100 3000 3100 5000 5100 en EsVictorAlmarazNo ratings yet

- IRS2092 DatasheetDocument18 pagesIRS2092 DatasheetSergio Daniel BarretoNo ratings yet

- E515 IO MixerDocument2 pagesE515 IO MixerAudiotec ServiceNo ratings yet

- 90 W Audio Power Amplifier Based On Transistor - Amplifier Circuit DesignDocument7 pages90 W Audio Power Amplifier Based On Transistor - Amplifier Circuit DesignClaudio FernandesNo ratings yet

- Power AmplifierDocument6 pagesPower AmplifierYen Hugo MirtoNo ratings yet

- MSR100/SMS100: Powered SpeakerDocument32 pagesMSR100/SMS100: Powered SpeakerrzvNo ratings yet

- Professional VA Series Power Amplifiers with Class H+ DesignDocument4 pagesProfessional VA Series Power Amplifiers with Class H+ DesignarthurcraigNo ratings yet

- Technics SAAX 54 SchematicsDocument11 pagesTechnics SAAX 54 Schematicsarmas1No ratings yet

- 300 Watt MOSFET Real HI-FI Power AmplifierDocument3 pages300 Watt MOSFET Real HI-FI Power AmplifierMiguel MejíaNo ratings yet

- Sony HCD Rv222 Ver 1.1Document86 pagesSony HCD Rv222 Ver 1.1Carlos Raul100% (2)

- Speaker Protection CircuitDocument3 pagesSpeaker Protection Circuitsontuyet820% (2)

- JVC AV-21B117BDocument10 pagesJVC AV-21B117Bdoraemon007100% (1)

- Power Amp Super Bridge 120W by IC TDA2030 - EleccircuitDocument7 pagesPower Amp Super Bridge 120W by IC TDA2030 - EleccircuitmarcioulguimNo ratings yet

- 25W-500W Scalable Class D Audio AmplifierDocument42 pages25W-500W Scalable Class D Audio AmplifierPablo IgorNo ratings yet

- 1000W Driver Power Amplifier Namec TEF - Electronic CircuitDocument3 pages1000W Driver Power Amplifier Namec TEF - Electronic CircuitK Raja SekarNo ratings yet

- Crossoverdata1 24CX - 2Document1 pageCrossoverdata1 24CX - 2Stephen MarmelNo ratings yet

- Diagramas de Amplificadores Yiroshi 2 PDFDocument4 pagesDiagramas de Amplificadores Yiroshi 2 PDFRedel AlaNo ratings yet

- Instruction Manual Manual de Instrucciones Notice D'Emploi BedienungsanleitungDocument34 pagesInstruction Manual Manual de Instrucciones Notice D'Emploi BedienungsanleitungJorge GarciaNo ratings yet

- Yamaha psr550 Sevicemanual PDFDocument50 pagesYamaha psr550 Sevicemanual PDFAnand s100% (1)

- Service Manual DP750 - DP760 - ENG - Rev1 PDFDocument96 pagesService Manual DP750 - DP760 - ENG - Rev1 PDFДмитрий РазуваевNo ratings yet

- Class D Amplifier With Maximum Power Adjustable From 20W To 300WDocument13 pagesClass D Amplifier With Maximum Power Adjustable From 20W To 300Wramontv032428100% (1)

- Rockola Modified PDFDocument4 pagesRockola Modified PDFRoldão VianaNo ratings yet

- 4d4fe32593743 - SiA 208RDocument8 pages4d4fe32593743 - SiA 208RManoj VattavilaNo ratings yet

- Single-Phase SEPIC Based PFC Converter For PMBLDCM Drive in Air-Conditioning SystemDocument6 pagesSingle-Phase SEPIC Based PFC Converter For PMBLDCM Drive in Air-Conditioning Systemsarav03No ratings yet

- DC Ripple Current Reduction On A Single-Phase PWM Voltage-Source RectifierDocument11 pagesDC Ripple Current Reduction On A Single-Phase PWM Voltage-Source RectifierRajni YadavNo ratings yet

- Control Techniques For Power Factor CorrectionDocument9 pagesControl Techniques For Power Factor Correctionsatya_9145No ratings yet

- Designing PFC and PSFB Stages for EV Battery ChargersDocument5 pagesDesigning PFC and PSFB Stages for EV Battery ChargersThien DinhNo ratings yet

- Yamaha KX-W952 RS Manuel de ServiceDocument34 pagesYamaha KX-W952 RS Manuel de ServiceJoão AlbertoNo ratings yet

- US 224DPShortcutsDocument1 pageUS 224DPShortcutsJoão AlbertoNo ratings yet

- With TO-220C Package Complement To Type 2SB546 Collector Current I 2A Collector-Base Voltage V 200VDocument4 pagesWith TO-220C Package Complement To Type 2SB546 Collector Current I 2A Collector-Base Voltage V 200VJoão AlbertoNo ratings yet

- Tabela de Diodos ZenerDocument2 pagesTabela de Diodos ZenerJoão AlbertoNo ratings yet

- Ciclotron TIP2000 2AB IIDocument2 pagesCiclotron TIP2000 2AB IIJoão AlbertoNo ratings yet

- 2000 Watt Audio AmpDocument2 pages2000 Watt Audio AmpXxvic2rxX50% (2)

- GL-R - User Manual PDFDocument174 pagesGL-R - User Manual PDFGary MiltonNo ratings yet

- Materials System SpecificationDocument18 pagesMaterials System SpecificationEagle SpiritNo ratings yet

- 195 - EE8402, EE6402 Transmission and Distribution - Question Bank 2Document11 pages195 - EE8402, EE6402 Transmission and Distribution - Question Bank 2KrishNo ratings yet

- GFM Technical ManualDocument14 pagesGFM Technical ManualsaeedNo ratings yet

- Lab # 01: Introduction To NI Elvis KIT: Sukkur Institute of Business Administration UniversityDocument18 pagesLab # 01: Introduction To NI Elvis KIT: Sukkur Institute of Business Administration UniversityKashif Mujeeb Abdul MujeebNo ratings yet

- Wells-Gardner 6100 Vector Monitor FAQ and Guide March 1, 2002Document75 pagesWells-Gardner 6100 Vector Monitor FAQ and Guide March 1, 2002dtsirkinNo ratings yet

- Electronics & Telecom Engineering Details for Jalgaon PolytechnicDocument13 pagesElectronics & Telecom Engineering Details for Jalgaon Polytechnicpawankumar dhandeNo ratings yet

- DIY Bench Power Supply Using an Old PC Power SupplyDocument8 pagesDIY Bench Power Supply Using an Old PC Power SupplyMarius DanilaNo ratings yet

- LMX210BMWVCDocument153 pagesLMX210BMWVCJosé SidivaldoNo ratings yet

- Device Craft Wiper Motor SpecDocument15 pagesDevice Craft Wiper Motor SpecrogerroseNo ratings yet

- Power Supply: A Presentation By: Mr. Rohit V. KamalakarDocument19 pagesPower Supply: A Presentation By: Mr. Rohit V. KamalakarRohit Kamalakar100% (1)

- Programmable Controller: Matsushita Electric Works, LTDDocument18 pagesProgrammable Controller: Matsushita Electric Works, LTDRitesh SharmaNo ratings yet

- Service Manual: PhilipsDocument51 pagesService Manual: PhilipsIonel CociasNo ratings yet

- Esab Buddy Arc 145 Manual enDocument20 pagesEsab Buddy Arc 145 Manual enСтефан АнтонићNo ratings yet

- Manual de Aplicação EtherNet-IP Anybus Adapter RW 6.05Document50 pagesManual de Aplicação EtherNet-IP Anybus Adapter RW 6.05Diogo CampezattoNo ratings yet

- Preliminary Documentation PDFDocument63 pagesPreliminary Documentation PDFShirish GuravNo ratings yet

- Daikin RYYQ-T7Y1B DatabookDocument43 pagesDaikin RYYQ-T7Y1B Databooktyberius7No ratings yet

- Sitronix 65 x 132 Dot Matrix LCD Controller/Driver ST7565Document56 pagesSitronix 65 x 132 Dot Matrix LCD Controller/Driver ST7565Saurabh BhatiaNo ratings yet

- Comprehensive Che 1 HDMI Extender ManualDocument6 pagesComprehensive Che 1 HDMI Extender ManualandywanderNo ratings yet

- BB SEQUENCER GUIDEDocument7 pagesBB SEQUENCER GUIDEramona.sabou918No ratings yet

- AC Ripple Currents in UPS DC LinksDocument6 pagesAC Ripple Currents in UPS DC LinksVijit DubeyNo ratings yet

- Guia Controlador XEDocument136 pagesGuia Controlador XEmanuel solano gomez100% (3)

- TPRseries HanyoungDocument24 pagesTPRseries Hanyoungmaintenance sagaNo ratings yet

- Continuum NetController ReferenceDocument76 pagesContinuum NetController ReferencepujFierros100% (1)

- Arcoweld Arcotig LCD HF 315acdc Operation Manual November2019 OnlineDocument44 pagesArcoweld Arcotig LCD HF 315acdc Operation Manual November2019 OnlineJederson ColaresNo ratings yet

- Implementing Palletization Application of 4-Axis Igus Robot ManipulatorDocument20 pagesImplementing Palletization Application of 4-Axis Igus Robot ManipulatorKV SAI KIRANNo ratings yet

- 04 - FB200 Technical Specification, 003535, EN, 2013-10-03, V2.04 PDFDocument47 pages04 - FB200 Technical Specification, 003535, EN, 2013-10-03, V2.04 PDFpr3m4nNo ratings yet

- Unicont PMM-300Document2 pagesUnicont PMM-300Lucian AndriescuNo ratings yet

- Quidway 20S5300 20series 20ethernet 20switches 20hardware 20Document98 pagesQuidway 20S5300 20series 20ethernet 20switches 20hardware 20Hamza_yakan967No ratings yet

- Platform Guide VIPRION 2400Document86 pagesPlatform Guide VIPRION 2400Hasmadi HadiNo ratings yet