Professional Documents

Culture Documents

ch4 Microprocesseur PDF

Uploaded by

Sâkly ChihèbOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ch4 Microprocesseur PDF

Uploaded by

Sâkly ChihèbCopyright:

Available Formats

Partie 4 : Architecture de base d`un microprocesseur

I. Introduction.

Le processeur (microprocesseur) est le composant hardware le plus connu d'un ordinateur.

C'est l'unite intelligente de traitement des inIormations. Son travail consiste a lire des

programmes (des suites d'instructions), a les decoder et a les executer. Le premier

microprocesseur est apparu en 1972. A l'epoque, INTEL invente le 4004, destine a un

constructeur japonais de machine a calculer. Celui-ci le reIuse pour une taille (dimension)

excessive. INTEL le met alors sur le marche sans conviction mais avec le succes que l'on sait.

Les annees 80 voyaient l'emergence de ces circuits avec les Zylog Z80, 6800 de Motorola

(dont les suivants sont utilises encore par les MAC) et le 6500. Avec l'arrivee des PC-XT

d'IBM et l'utilisation du 8088, INTEL devenait matre du marche Iin des annees 80. Deux

types de processeurs sont Iabriques aujourd`hui, le microprocesseur et le microcontrleur.

Au niveau traitement des inIormations, les 2 sont pratiquement equivalents. La distinction

vient des Ionctionnalites internes. Un microcontrleur est dedie aux traitements des entrees /

sorties. De ce Iait, des ports sont rajoutes (parallele et / ou serie suivant les modeles) qui vont

permettre de recevoir ou d'envoyer des inIormations des peripheriques. On pourrait utiliser un

microprocesseur pour les mmes Ionctions mais ceci necessiterait de rajouter des composants

externes pour chaque port externe. Un microcontrleur inclut souvent la programmation de

maniere interne dans une memoire de type ROM et mme de la memoire de travail de type

RAM. Comme un microcontrleur gere des peripheriques lents, il n'est pas optimalise pour la

vitesse de traitement d'inIormations, ni mme pour gerer des quantites de memoire

importantes. L'interIaage du processeur avec l`exterieur necessite 3 bus: un bus de donnees,

un bus d'adresse et un bus de commande. Il existe des processeurs bases sur l'architecture

CISC et d`autres bases sur l`architecture RISC. Les processeurs 8086-8088 sont de types

CISC (Complex Instruction Set Computer). Les premiers concepteurs de processeurs

rajoutaient le plus d'instructions possibles pour permettre a l'utilisateur de peauIiner ses

programmes. Neanmoins, ces multiples instructions ralentissent le Ionctionnement du

microprocesseur et sont peu utilisees en pratique. Actuellement, on utilise de plus en plus de

processeurs RISC (Reduced Instruction Set Computer). Le nombre d'instructions est reduit,

mais executees nettement plus rapidement. Chaque instruction complexe peut tre

programmee par plusieurs instructions simples. La technique actuelle est de charger des

instructions CISC 8086-8088 pour les recoder en instructions RISC plus rapides.

Un processeur est constitue de:

une unite de commande qui lit les instructions et les decode;

une unite de traitement (UAL - unite arithmetique et logique) qui execute les instructions;

d`un ensemble de memoire appeles registres;

d`un bus de donnees externe;

d`un bus d`adresse externe;

d`un bus de commande externe;

d`un bus de donnees interne reliant l`unite de commande l`UAL et les registres.

Lorsque tous ces elements sont regroupes sur une mme puce, on parle alors de

microprocesseur. La Iigure ci dessous donne une idee sur l`architecture interne d`un

microprocesseur. Cette architecture presentee est dite "standard". Il en existe de multiples,

notamment les architectures a plusieurs bus internes ou a Pipeline.

Figure 4.1. Architecture de base de microprocesseur.

Sur cette Iigure nous pouvons voir les 3 bus qui permettent au microprocesseur de

communiquer avec l`exterieur.

II. Composants d`un microprocesseur.

II.1 Lunite de commande.

Elle permet de "sequencer" le deroulement des instructions. Elle eIIectue la recherche en

memoire de l'instruction, le decodage, l'execution et la preparation de l'instruction suivante.

L'unite de commande elabore tous les signaux de synchronisation internes ou externes (bus

des commandes) au microprocesseur.

II.2 Lunite arithmetique et logique (UAL).

C'est l'organe qui eIIectue les operations:

Arithmetiques : addition, soustraction, multiplication, ...

Logiques : et, ou, non, decalage, rotation, ....

Deux registres sont associes a l'UAL : l'accumulateur et le registre d'etat.

II.2.1 Laccumulateur (nomme . A).

C'est une des deux entrees de l'UAL. Il est implique dans presque toutes les operations

realisees par l'UAL. Certains constructeurs ont des microprocesseurs a deux accumulateurs

(Motorola : 6800).

Exemple : A etant l'accumulateur et B un registre, on peut avoir : AB (ADD A,B : addition

du contenu du registre A avec celui du registre B, le resultat etant mis dans A)

II.2.2 Le registre detat (Flags . F)

A chaque operation, le microprocesseur positionne un certain nombre de bascules d'etat. Ces

bascules sont appelees aussi indicateurs d'etat ou drapeaux (status, Ilags). Par exemple, si une

soustraction donne un resultat nul, l'indicateur de zero (Z) sera mis a 1. Ces bascules sont

regroupees dans le registre d'etat

On peut citer comme indicateurs:

- retenue (carry : C)

- retenue intermediaire (Auxiliary-Carry : AC)

- signe (Sign : S)

- debordement (OverIlow : O)

- zero (Z)

- parite (Parity : P)

II.2.2.1 Retenue . (carrv . C).

Exemple: addition de nombres binaire sur 8 bits

11111100 FCH

10000010 82H

carry : 1 01111110 carry : 1 7EH

Sur cet exemple, nous pouvons remarquer que le resultat sur 8 bits est Iaux (7EH). TouteIois

le bit de retenu expulse n`est pas deIinitivement perdu. Ce bit C (carry) est stocke dans le

registre d`etat est peut tre teste par l`utilisateur. De la mme maniere lors d'une operation de

decalage ou de rotation ce bit peut tre positionne en cas de debordement. Par exemple, soit le

decalage a gauche sur d'un bit de cet octet : 10010110, apres le decalage nous avons

00101100. En ce qui concerne le carry, il va tre positionne a 1, puisque le bit expulse est egal

a 1.

II.2.2.2 Retenue intermediaire . (Auxiliarv Carrv . AC).

Sur les operations arithmetiques, ce bit signale une retenue entre groupes de 4 bits (HalI-byte :

demi-octet) d'une quantite de 8 bits.

II.2.2.3 Signe. (S)

Ce bit est mise a 1 lorsque le resultat de l'operation est negatiI (bit de plus Iort poids du

resultat a 1).

II.2.2.4 Debordement . (overflow . O)

Cet indicateur est mis 1, lorsqu'il y a un depassement de capacite pour les operations

arithmetiques en complement a 2. Sur 8 bits, on peut coder de -128 (1000 0000) a 127 (0111

1111).

104 0110 1000 - 18 1110 1110

26 + 0001 1010 - 118 1000 1010

130 1000 0010 (-126) -136 0111 1000 (120) avec C1

Dans cet exemple et dans les deux cas de Iigure (operation a droite ou operation a gauche), le

bit O est positionne a 1. L'indicateur de debordement est une Ionction logique (OU exclusiI)

de la retenue (C) et du signe (S).

II.2.2.5 Le bit Zero . (Zero . Z)

Ce bit est mis a 1 lorsque le resultat de l'operation est nul.

II.2.2.6. Le bit de parite . (P)

Ce bit est mis a 1 lorsque le nombre de 1 de l'accumulateur est pair.

Remarque : La plupart des instructions modiIient le registre d'tat.

Exemple :

ADD A, B positionne les drapeaux : O, S, Z, A, P, C

OR B, C (B ou C -~ B) positionne S, Z, P tandis que

MOV A, B (Move, TransIerer le contenu de B dans A) n'en positionne aucun.

II.3 Les registres.

Il y`a deux type de registres : les registres d'usage general, et les registres d'adresses

(pointeurs).

II.3.1 Les registres dusage general.

Ce sont des memoires rapides, a l'interieur du microprocesseur, qui permettent a l'UAL de

manipuler des donnees a vitesse elevee. Ils sont connectes au bus de donnees interne au

microprocesseur. L'adresse d'un registre est associee a son nom (on donne generalement

comme nom une lettre) A, B,C...

Exemple : MOV C,B: transIert du contenu du registre B dans le registre C.

II.3.2 Les registres dadresses (pointeurs).

Ce sont des registres connectes sur le bus d`adresses. On peut citer comme registre:

- Le compteur ordinal (pointeur de programme PC) ;

- Le pointeur de pile (stack pointer SP) ;

- Les registres d'index (index source SI et index destination DI).

II.3.2.1 Le compteur ordinal (pointeur de programme PC.)

Il contient l'adresse de l'instruction a rechercher en memoire. L'unite de commande

incremente le compteur ordinal (PC) du nombre d'octets sur lequel l'instruction, en cours

d'execution, est codee. Le compteur ordinal contiendra alors l'adresse de l'instruction suivante.

Prenons l`exemple d`un microprocesseur 8086 de INTEL :

Exemple : (PC)10000H ; il pointe la memoire qui contient l'instruction MOV CX,BX qui

est codee sur deux octets (89 D9H) ; l'unite de commande incrementera de deux le contenu du

PC : (PC) 10002H (la memoire sera supposee tre organisee en octets).

Figure 4.2 Compteur de Programme (PC).

II.3.2.2 Le pointeur de plie (stack pointer SP).

Il contient l'adresse de la pile. Celle-ci est une partie de la memoire, elle permet de stocker des

inIormations (le contenu des registres) relatives au traitement des interruptions et des sous-

programmes. La pile est geree en LIFO : (Last IN First Out) dernier entre premier sorti. Le

Ionctionnement est identique a une pile d'assiettes. Le pointeur de pile SP pointe le haut de la

pile (31000H Iigure 4.3), il est decremente avant chaque empilement, et incremente apres

chaque depilement. Il existe deux instructions pour empiler et depiler: PUSH et POP.

exemple: PUSH A empilera le registre A et POP A le depilera. La Iigure suivante montre

l`evolution du pointeur de pile durant l`execution du programme commenant en 12E30H.

Figure 4.3. Principe de fonctionnement de la pile.

Sur cette Iigure le programme commence par sauvegarder le contenu de C dans la pile (PUSH

C). Pour cela (SP) est decremente de deux ((SP)31000H-230FFEH), puis on eIIectue

l'ecriture de (C) dans la memoire a l'adresse (SP) : (30FFEH) 6142H. Pour PUSH A on

obtient : (30FFCH)1234H, et pour PUSH B : (30FFAH)2D5AH. Pour l'instruction POP

B, (SP) est charge dans le registre B (SP30FFAH ; B2D5AH) puis (SP) est incremente de

deux (SP 30FFAH+230FFCH). EnIin, pour POP A on obtient : A1234H et

(SP30FFCH + 2 30FFEH).

II.3.2.3 Les registres dindex (index source SI et index destination DI).

Les registres d'index permettent de memoriser une adresse particuliere (par exemple : debut

d'un tableau). Ces registres sont aussi utilises pour adresser la memoire de maniere diIIerente.

C'est le mode d'adressage indexe.

Exemple :

MOV A,SI+10000H] place le contenu de la memoire d'adresse 10000H le contenu de SI,

dans le registre A.

Figure 4.4. Exemple d`opration sur le registre d'index.

III. Principe d`excution d'une instruction.

Dans cette architecture standard, l`execution d`une instruction se Iait en trois etapes:

-Recherche de l'instruction (Fetch) ;

-Decodage (decode) ;

-Execution (execute).

III.1 Recherche de linstruction.

Le contenu de PC (compteur ordinal) est place sur le bus d`adresse (c'est l'unite de commande

qui etablit la connexion). L'unite de commande (UC) emet un ordre de lecture

(READRD1). Au bout d'un certain temps (temps d'acces a la memoire), le contenu de la

case memoire selectionnee est disponible sur le bus des donnees. L'unite de commande charge

la donnee dans le registre d'instruction pour decodage. Le microprocesseur place le contenu

de PC (10000H) sur le bus d`adresse et met RD a 1 (cycle de lecture). La memoire met sur le

bus de donnees le contenu de sa memoire n 10000H (ici 89D9H qui est le code de

MOV C,B ). Le microprocesseur place dans son registre d'instruction le contenu du bus de

donnees (89D9H). L'unite de commande decode et execute l'instruction MOV C,B.

Figure 4.5 Compteur de Programme (PC).

III.2 Le Decodage de linstruction.

Le registre d'instruction contient maintenant le premier mot de l'instruction qui peut tre

codee sur plusieurs mots. Ce premier mot contient le code opratoire qui deIinit la nature de

l'operation a eIIectuer (addition, rotation,...) et le nombre de mots de l'instruction. L'unite de

commande decode le code operatoire et peut alors executer l'instruction.

III.3 Lexecution de linstruction.

Apres l`execution de l`instruction par micro-programme, les indicateurs sont positionnes (O,

S, Z, A, P, C). L'unite de commande positionne le compteur ordinal (PC) pour l'instruction

suivante.

IV. Les exceptions & Interruptions.

IJ.1 Introduction.

Nous etudions dans cette partie les interruptions materielles (ou externes), c'est a dire

declenchees par le materiel (hardware) exterieur au processeur. Les interruptions permettent

au materiel de communiquer avec le processeur. On peut distinguer deux sortes

d'interruptions. Les interruptions materielles et les interruptions logicielles. Les interruptions

internes, dues a l`execution du programme (division par zero, depassement de capacite d'un

registre, tentative d'acces a une zone memoire protegee, ..) sont considerees comme

interruptions logicielles. Ces interruptions sont souvent appelees exceptions. Les interruptions

ainsi que les exceptions sont toutes traitees de la mme Iaon. La diIIerence vient surtout de la

source d`enclenchement de l`interruption. En eIIet les interruptions materielles et les

exceptions peuvent se produire n'importe quand, tandis que les interruptions logicielles se

produisent a un endroit precis du code ou se trouve une des instructions int ou into ou trap

(a depend du microprocesseur). De plus, les interruptions materielles peuvent tre masquees

(interdites ou autorisees) a l'aide de l'indicateur IF (Registre d`etat). Une interruption externe

est signalee au processeur par un signal electrique sur une des ses pattes prevues pour ceci.

Lors de la reception de ce signal, le processeur ''traite'' l'interruption des la Iin de l'instruction

en cour d`execution. Ce traitement consiste a executer un programme qui est appele

automatiquement lorsque l`interruption survient. L'adresse de debut du programme doit tre

prealablement stockee dans une table dite des vecteurs d'interruptions. Lorsque la routine

d`interruption est executee une instruction IRE1 permet au processeur de reprendre l'execution

a l'endroit ou il avait ete interrompu. Il est aussi possible d'ignorer l`evenement et passer

normalement a l'instruction suivante dans le cas des interruptions masquables. Il est en eIIet

parIois necessaire de pouvoir ignorer les interruptions pendant un certain temps, pour

eIIectuer des traitements plus urgents. Lorsque le traitement est termine, le processeur

demasque les interruptions et les prend alors en compte. La procedure d`interruption est donc

une tache speciale associee a un evenement externe ou interne.

IJ.2 Les interruptions materielles.

IJ.2.1 Cas des processeurs de la famille INTEL.

Les interruptions materielles sont generees par les peripheriques : souris, clavier, disque,

horloge temps reel, etc. A la diIIerence des interruptions logicielles, elles peuvent tre

autorisees ou interdites au moyen de l`indicateur IF du registre d`etat EFLAGS . Comme

le Pentium n`a que deux entrees d`interruption materielle, NMI et INTR, on doit lui adjoindre

un contrleur d`interruption programmable aIin de pouvoir disposer de plusieurs sources

d`interruption avec une gestion de priorite. C`est le PIC (Programmable Interrupt Controler

8259A).

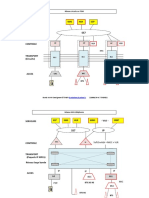

Figure 4.5 Le contrleur d'interruption PIC 8259A.

Figure 4. Schma interne du PIC 8259.

Le 8259A peut accepter les interruptions de 8 sources externes, et on peut gerer jusqu'a 64

sources diIIerentes en cascadant plusieurs 8259A. Il gere la priorite entre les interruptions

simultanees, interrompt le processeur et lui passe un code pour identiIier la source

d'interruption. Une source d'interruption est connectee a chacune des 8 entrees IR0 a IR7.

Selon sa priorite, et s'il n'y a pas d'autre interruption en cour, le PIC decide s'il peut

transmettre l'interruption au CPU. Si oui, il aIIirme la ligne INT, qui est connectee a l'entree

INTR (Interrupt Request) du CPU. Si le CPU est prt a accepter l'interruption, il repond au

PIC via la ligne INTA (Interrupt Acknowledge). Le PIC repond a son tour en envoyant le

numero d'interruption sur les lignes D0 a D7. Ce numero est un index dans la table des

vecteurs d'interruption. Le CPU est maintenant prt a appeler le sous-programme de

traitement d'interruption approprie. Quand le sous-programme de traitement d'interruption a

termine son execution, il en avertit le PIC pour qu'il puisse permettre a d'autres interruptions

d'atteindre le CPU. Les interruptions materielles servent a une gestion eIIicace des

peripheriques d'entree/sortie. Dans un ordinateur moderne, il y a continuellement des

interruptions materielles. Le temporisateur, l'horloge temps reel, les touches du clavier, les

mouvements et les clics de la souris, le modem, l'imprimante, les disques durs et souples, le

CDRom, sont tous des sources d'interruptions. Les circuits contrleurs de peripheriques

contiennent plusieurs registres d'interIace avec le CPU. Il y`a habituellement un registre de

contrle, un registre d'etat, et un ou plusieurs registres de donnees. Pour connatre l'etat d'un

peripherique, le CPU peut interroger le registre d'etat. L'approche des drapeaux (Ilags)

consiste a interroger de Iaon repetitive le registre d'etat, pour savoir ou le peripherique est

rendu dans le transIert des donnees. A-t-il reu une nouvelle donnee ? A-t-il termine la

transmission de la derniere donnee envoyee ? etc. Cette approche consomme trop de temps de

la part du processeur. L'approche interruption est beaucoup plus perIormante. Le peripherique

envoie une interruption materielle au processeur quand il a quelque chose a signaler. Le

processeur interrompt alors la tche en cour, enregistre en memoire l'etat de la machine, et

vient interroger le registre d'etat du peripherique, pour connatre la cause de l'interruption. Il

eIIectue ensuite le traitement approprie et elimine la source de l'interruption Ce traitement

consiste, par exemple, a lire la donnee reue dans le registre de reception et a l'inscrire en

memoire, ou a lire en memoire la prochaine donnee a transmettre et a l'inscrire dans le registre

de transmission du peripherique. Le processeur retourne ensuite a la tche interrompue apres

avoir restaure l'etat de la machine qu'il avait enregistre au moment de l'interruption.

Le sous-programme de traitement a donc 4 tches a executer :

-Sauvegarder l'etat de la machine en empilant les registres susceptibles d'tre modiIies dans le

sous-programme de traitement d'interruption (ISR). Ceci inclut EFLAGS (registre d`etat);

-Interroger le registre d'etat d u peripherique pour savoir quelle operation eIIectuer ;

-Eliminer la source de l'interruption en eIIectuant l'operation d'entree-sortie ;

-Restaurer l'etat de la machine et retourner a la tche interrompue en depilant les registres

empiles.

IJ.2.2 PIC dans le cas du PC.

L`architecture est partiellement Iigee dans le cas des PC (historique par rapport au 286). Le

PIC matre va vers le processeur et le PIC esclave sur la broche 2 du matre.

Figure 4.7 Cascade de deux contrleurs d'interruptions PIC 8259.

Depuis le premier 8088 qui a equipe les PC, les interruptions sont normalisees pour les

peripheriques standard. La derniere composante d'un systeme a microprocesseur est l'acces

direct a la memoire, le DMA (Direct Memory Access). Cette Ionction permet de demander au

processeur de se deconnecter des bus de donnees, adresse et contrle pendant qu'un

peripherique prend le contrle de la memoire. L'arrivee du pseudo Plug & Play de Windows

95/98 et Win2000 couple avec le plug & Play du Bios Iacilite dans certains cas le parametrage

des interruptions, mais il est parIois necessaire de reprendre les conIigurations manuellement

lorsque le nombre de peripheriques augmente. Un peripherique est donc determine de maniere

hardware par une plage d'adresses (parIois une seule adresse), une interruption et

eventuellement un canal DMA. Le 8088-8086 utilisait un 8259 d'INTEL, avec 8 niveaux

d'interruptions notees de IRQ0 a IRQ7. Le 80286 jusqu'aux 486 utilisaient 2 contrleurs 8259

chanes ce qui permet d`avoir 16 sources d`interruptions. Ils sont notes de IRQ0 a IRQ15,

mais avec l'IRQ9 reservee pour le chanage. Depuis les Pentium (et un nouveau circuit

gestionnaire d'interruptions), cette IRQ9 est accessible aux peripheriques, mais ceci explique

que peu de peripheriques ne se branchent par deIaut sur ce niveau d'interruption.

L'interruption non masquable (NMI) est egalement utilisee pour des erreurs de parite ou

erreurs de connecteurs entrees / sorties. Le tableau ci-dessous reprend l'ensemble des adresses

et interruptions normalisees du PC, melangees avec les interruptions utilisees par deIaut

actuellement.

Fonction IRQ Adresse Commentaires

Horloge systeme 0 Ne peut tre modiIie

Clavier 1 Ne peut-tre modiIie

Contrleur d'IRQ programmable 2 Ne peut tre modiIie

Com 2

Com 4

3

2F8-2FF

2E8 - 2EF

ModiIiable avec prudence

Com 1

Com 3

4

3F8-3FF

3E8-3EF

ModiIiable avec prudence

Libre 5

Generalement utilise par la carte son,

egalement LPT2 en 278

Contrleur lecteur de disquette 6 ModiIiable avec prudence

LPT 1

LPT 2

7

378 37A

(pour les produits

de marque)

278 27A

ModiIiable avec prudence. On peut

mettre LPT1 et LPT2 sur la mme

interruption, mais pas d'impressions

simultanees

Horloge: date et heure 8 Pas modiIiable

9

Libre en Pentium et suivant, utilise en

parallele avec IRQ2 dans les 486.

Souvent utilise par les cartes sons

10 (A) Libre

11 (B) Libre

12 (C) Libre

Coprocesseur mathematique 13 (D) Ne peut tre modiIie

14 (E) Libre, generalement IDE 1

15 (F) Libre, generalement IDE 2

1ableau 2. Ensemble des interruptions normalises du PC

Souvent les interruptions 14 et 15 sont utilisees par le contrleur de disque dur (une par port

IDE). L'interruption 12 est utilisee par la souris PS2. Le port USB utilise egalement par deIaut

cette interruption 12. Neanmoins, le port USB passe en 11 si une souris PS2 est connectee.

Ces interruptions peuvent tre veriIiees par les outils Iournis par les systemes d'exploitation et

pour certaines, elles sont aIIichees lors du demarrage de la majorite des PC. La veriIication

dans les PC sous DOS passe par le programme MSD.exe situe en c:\DOS. Dans le cas de

Windows cet utilitaire est situe dans le panneau de conIiguration. Il permet les mmes

veriIications, mais de maniere plus etendues. Depuis Win98, un nouvel utilitaire, Outils

systemes MicrosoIt, situe dans le dossier Outils Systeme du menu Demarrer permet une

meilleure connaissance sur le systeme en cour. En regardant ce tableau, si un PC manque

d'interruptions libre, il est possible d'en recuperer en supprimant des ports de communication.

Si vous n'utilisez pas de ports serie (uniquement USB), vous pouvez rendre inactiI COM 1 et

Com 2 (disabled) et recuperer les interruptions 3 et 4. Idem pour le port parallele. Si vous

utilisez 2 ports paralleles, vous pouvez mettre l'interruption de LPT2 en 5 (selon la norme) ou

en 7. Si vous utilisez des disques SCSI, pourquoi pas rendre inactiI les ports IDE 1 et IDE2

dans le BIOS (recuperation des INT 14 et 15), ... Comme les systemes d`exploitation

Windows NT, 2000 et XP sont des systemes d'exploitation pleinement proteges, les

application: en mode utilisateur ne peuvent acceder au materiel directement et doivent passer

par un pilote de peripherique Ionctionnant en mode noyau. C'est la couche HAL (Hardware

Abstraction Layer) de NT qui gere les interruptions. La realisation de tels pilotes de

peripheriques depasse touteIois le cadre de ce cours. Cependant, les VDD (Virtual Device

Drivers) emulent les applications 16 bits de MS-DOS. Ils piegent ce que l'application MS-

DOS croit tre des reIerences a des ports d'entree-sortie et les traduisent en Ionctions natives

d'entree-sortie Win32. L'application intitulee Invite de commande ou, en anglais, DOS

prompt, est un tel VDD. On peut y executer la plupart des programmes ecrits pour MS-DOS,

y compris certains qui utilisent des interruptions materielles. C'est le cas des exemples qui

suivent que vous pouvez compiler avec un assembleur tel que A86, MASM ou TASM. En

mode protege, le processeur va plutt lire la table des descripteurs d'interruption IDT

(Interrupt Descriptor Table). L'adresse de cette table est contenue dans le registre IDTR. Elle

contient des descripteurs de 64 bits pour les sous-programmes de traitement d'interruption.

Ces descripteurs sont appeles Trap Gates dans le cas d'interruptions logicielles. La procedure

qui veut utiliser ces instructions doit avoir un niveau de privilege lui permettant d'acceder au

descripteur d'interruption de la table IDT pour le numero de trappe en question. Ainsi, si une

application de niveau 3 veut executer int 47, il Iaut que le descripteur a IDT(47) ait DPL3.

Dans un systeme d'exploitation tel que Windows NT, la IDT se trouve en memoire protegee,

de sorte qu'il n`est pas possible d'aller ecrire un descripteur directement dans la IDT.

Windows NT ne supporte pas non plus les INT 0x21 de MS-DOS. TouteIois, Il est possible

de les essayer en ecrivant un programme assembleur et en l'executant dans la Ientre Invite

de commande (DOS prompt). En particulier, si nous desirons implanter notre propre sous-

programme de traitement d'interruption logicielle, l'appel systeme int 21h (33) Ionction 25h

permet de le Iaire Iacilement.

IJ.3 Les interruptions logicielles.

Comme nous l`avions ecrit plus haut, les interruptions logicielles, sont aussi appelees trappes

ou deroutements. Elles incluent aussi les Iautes et les arrts. Une Iaute se produit quand le

processeur detecte une erreur durant le traitement d'une instruction. Par exemple, division par

0, opcode invalide, etc. En mode reel (Mode 8086), quand le processeur rencontre une

instruction telle que int immed8 (immed8 : constante sur un octet), il va lire la table des

vecteurs d'interruption IVT (Interrupt Vector Table). Cette table de 1 Ko est situee a l'adresse

0000:0000. Chaque entree de la table contient le numero de segment de 16 bits et l'oIIset de

16 bits pour l'adresse d'un sous- programme de traitement d'interruption (Interrupt Service

Routine ou ISR). Immed8 est utilise comme indice dans cette table (on doit le multiplier par 4

pour avoir l'adresse physique correspondante). De plus, le registre d`etat FLAGS et les

registres de segment CS et d`instructions IP sont empiles dans cet ordre exact, puis les

indicateurs TF et IF sont mis a 0. Le sous-programme d'interruption devra se terminer par

l'instruction IRET, pour depiler correctement ces parametres. L'execution se poursuit ensuite

a l'adresse contenue dans la table. Par exemple, int 8 ira lire le vecteur situe a l'adresse 32

(0x20) et branchera a l'adresse qui y est contenue. A cette adresse doit debuter un sous-

programme de traitement d'interruption. Certaines ISR Iont partie du systeme d'exploitation et

sont deja deIinies, comme celles qui correspondent aux INT 0x21 de MS-DOS. Cette trappe y

sert de mecanisme d'appel au systeme d'exploitation. Si vous voulez deIinir votre propre sous-

programme de traitement d'interruption, il suIIit d'aller ecrire son adresse a l'endroit approprie

dans la table des vecteurs d'interruption avant de l'utiliser.

Figure 4.8 Principe d'excution des interruptions

Exemple 1 : Interruption logicielle pour ecrire une chane a l'ecran :

mov ah,09

mov dx, oIIset string

int 33

ou on a deIini la chane de caracteres string comme suit :

string db 'Toto':$'

Exemple 2: Interruption logicielle pour la lecture de l'horloge systeme.

L'horloge systeme interrompt le processeur 18,2 fois par seconde si l'indicateur d'interruption

IF est 1 (interruption materielle 08). Chaque Iois, le compteur de 32 bits situe aux adresses

0040:006C et 0040:006E est incremente de 1. Pour lire ce compteur, on peut utiliser

l'interruption logicielle int 0x1A (26).

mov ah, 0 ; mode lecture de l'horloge

int 26 ; appel a l'interruption d'horloge de MS-DOS

Apres l'instruction int 26,

cx TIMER-HIGH mot de poids Iort du compteur

dx TIMER-LOW mot de poids Iaible du compteur

Si al 0, on n'a pas depasse 24h depuis la derniere lecture

Si al > 0, on a depasse 24h depuis la derniere lecture.

Exemple 3: Interruption logicielle pour l`ecriture d`un programme resident et deviation de

l'interruption d'horloge temps reel.

Voici un exemple d'un programme resident qui utilise l'horloge temps reel et emet un bip

chaque 10 sec. La procedure de traitement de l'interruption 8 est deviee pour executer notre

sous-programme, puis continue avec l'ancienne procedure. Cette technique s'appelle un

hook.

start segment

org 100h

main: jmp short install

oldint8 dd ? ; espace pour ancien vecteur

counter dw 182 ; 182 * 54,94 ms 10 sec.

newint8 proc ; nouvellSR pour interruption 8

dec cs:counter ; decrementer compteur

jnz done ; on ne Iait rien tant que count ~ 0

mov cs:counter,182 ; reinitialiser compteur

mov ah, 0Eh ; emettre un bip

mov al, 7

int 10h

done: jmp cs:oldint8 ; continuer dans l'ancien vecteur

newint8 endp

; la partie suivante ne sera executee qu'une Iois, lors de l'installation

install proc near

mov ah, 35h ; charger CS:IP pour interruption 08

mov al, 08h ; IP va dans BX et CS dans ES

int 21 h

mov word ptr oldint8, bx ; enregistrer dans espace prevu

mov word ptr oldint82, es

mov dx, oIIset newint8 ; ou lea dx, newint8

mov ah, 25h ; deIinir CS:IP pour nouvelle

mov al, 08h ; interruption 8

int 21h ; DX IP, DS CS par deIaut

mov dx, (oIIset install -oIIset start) ; taille du progr. resident

add dx, 15 ; arrondir a multiple de 16

shr dx, 4 ; division par 16

mov ah,31h ; rendre resident

int 21 h

install endp

start ends

end main

V. Le logiciel.

J.1 Introduction.

Un langage informatique, par opposition aux langages naturels comme le Iranais ou

l'anglais, est un langage structure utilise pour decrire des actions (ou algorithmes) executables

par un ordinateur. La principale diIIerence entre les langages inIormatiques et les langues

naturelles reside dans l'absence d'ambigutes : alors que certaines phrases du Franais peuvent

tre interpretees diIIeremment par diIIerents auditeurs, tous seront d'accord pour dire ce que

Iait un programme donne. Historiquement, le premier langage inIormatique a ete l'assembleur.

Or, la programmation en assembleur est souvent Iastidieuse, surtout pour des programmes

importants. Plus grave, un programme ecrit en assembleur depend etroitement du type de

machine pour lequel il a ete ecrit. Si l'on desire l'adapter a une autre machine (''porter'' le

programme), il Iaut le reecrire entierement. C'est pour repondre a ces problemes qu'ont ete

developpes des les annees 50 des langages de plus haut niveau. Dans ces langages, le

programmeur ecrit selon des regles strictes mais dispose d'instructions et de structures de

donnees plus expressives qu'en assembleur. Par exemple, dans certains langages comme

MATLAB, on pourra ecrire en une ligne que l'on desire multiplier deux matrices, alors que le

programme correspondant en assembleur prendrait quelques centaines de lignes. On distingue

grossierement deux Iamilles de langages inIormatiques, les langages interpretes et les

langages compiles. Un programme en langage interprete va tre traduit au Iur et a mesure de

son execution par un interpreteur. Un interpreteur est un programme charge de decoder

chaque instruction du langage et d'executer les actions correspondantes. Dans le cas de

programmes compiles, la traduction en langage machine a lieu une Iois pour toute. Le

compilateur (traducteur) traduit chaque instruction du langage en une suite plus ou moins

complexe d'instructions en langage machine. Les programmes compiles s'executent ainsi plus

rapidement que les programmes interpretes, car la traduction est deja Iaite. On perd cependant

en souplesse de programmation, car les types de donnees doivent tre connus au moment de la

compilation. Un compilateur traduit un programme source ecrit dans un langage de haut

niveau (par exemple C) en un autre programme dans un langage de bas niveau (par exemple

l'assembleur). Cette operation de traduction est assez complexe; les compilateurs sont des

programmes sophistiques, qui ont beaucoup progresse ces dernieres annees. Les principaux

langages compiles sont :

C/C programmation systeme et scientiIique;

ADA logiciels embarques;

Cobol gestion;

Fortran calcul scientiIique;

Pascal enseignement.

1ableau 3. Quelques langages compils.

BASIC bricolage;

LISP ''Intelligence ArtiIicielle'';

Prolog idem;

Perl traitement de Iichier textes;

Python programmation systeme, internet;

Java ''applets'' internet;

MATLAB calcul scientiIique;

Mathematica idem.

1ableau 4. Quelques langages interprts.

Notons que la distinction compile/interprete est parIois Iloue. Certains langages, comme

LISP, Java ou Python, peuvent subir une premiere phase de compilation vers un langage

intermediaire (bvtecode), qui sera lui mme interprete.

J.2 Les langages primitifs.

Toutes les inIormations manipulees par le micro-ordinateur sont codees sous la Iorme de mots

binaires (Iormats courants 8, 16 bits, 32 bits) Voici par exemple a quoi peut ressembler un

programme en langage machine: A1 01 10 03 06 01 12 A3 01 14.

Il s'agit de la representation hexadecimale d'un programme permettant d'additionner les

valeurs de deux cases memoire et de stocker le resultat dans une troisieme case. Il est evident

que ce type d'ecriture est diIIicilement lisible par nous, humains. Ainsi, puisque toutes les

instructions que le processeur peut eIIectuer sont associees a une valeur binaire chacune, on

utilise une notation symbolique sous Iorme textuelle qui correspond a chaque Ionction, c'est

ce que l'on appelle le langage assembleur. Dans l'exemple precedent la sequence A1 01 10

signiIie copier le contenu de la memoire a l'adresse 0110h dans le registre AX du processeur.

Cela se note en langage assembleur: MOV AX, 0110h]

Toutes les instructions ont une notation symbolique associee (Iournie par le Iabricant du

processeur). L'utilisation du langage assembleur consiste donc a ecrire sous Iorme symbolique

la succession d'instructions (precedees de leurs adresses pour pouvoir reperer les instructions

et passer Iacilement de l'une a l'autre). Ces instructions sont stockees dans un Iichier texte (le

Iichier source) qui, grce a un programme speciIique (appele "assembleur") sera traduit en

langage machine. Le programme precedent ecrit en langage assembleur donnerait:

Adresse de

l'instruction

Instruction en

langage machine

Instruction en

langage assembleur

Commentaires sur l'instruction

0100 A1 01 10 MOV AX, |0110h|

Copier le contenu de 0110h dans

le registre AX

0103 03 06 01 12 ADD AX, |0112h|

Ajouter le contenu de 0112h a

AX et mettre le resultat dans AX

0107 A3 01 14 MOV |0114h|, AX

Stocker AX a l'adresse memoire

0114h

L'ecriture en langage assembleur, bien que restant rebutante, est beaucoup plus

comprehensible pour un humain, car on a generalement moins de mal a retenir un nom qu'un

numero... Le programme doit tre saisi dans un Iichier texte non Iormate (c'est-a-dire sans

caracteres en gras, souligne, avec des polices de caracteres de diIIerentes tailles, ...) appele

Iichier source. En eIIet, l'assembleur (le programme permettant de Iaire la traduction du

langage assembleur en langage machine) permet uniquement de creer un Iichier assemble a

partir du Iichier source (il devra comporter l'extension .ASM, en s'appelant par exemple

source.asm ou n'importe quel autre nom suivi de l'extension .asm). L'assembleur va Iournir un

fichier obfet (dont l'extension est .obj) qui va contenir l'ensemble des instructions traduites en

instructions machines. Ce Iichier .OBJ ne pourra touteIois pas s'executer directement car il

Iaut encore lier les diIIerents Iichiers. En eIIet il est possible de construire un executable a

partir de plusieurs Iichiers sources (a partir d'un certain niveau de programmation il devient

interessant de creer des Iichiers contenant des Ionctions...). Ainsi, mme si nous avons un seul

Iichier objet il nous Iaudra utiliser un programme (appele editeur de liens) qui va nous

permettre de creer un Iichier executable (dont l'extension sera .exe). Comme dans tout

programme le Iichier source doit tre saisi de maniere rigoureuse. Chaque deIinition et chaque

instruction doivent ainsi s'ecrire sur une nouvelle ligne (pour que l'assembleur puisse les

diIIerencier). Le Iichier source contient:

- Des deIinitions de donnees declarees par des directives (mots speciaux interpretes par

l'assembleur, nous les etudierons plus tard, le but est ici de donner une idee de ce a quoi

ressemble un Iichier source). Celles-ci sont regroupees dans le segment de donnees delimite

par les directives SEGMENT et ENDS ;

- Puis sont placees les instructions (qui sont en quelques sortes le cour du programme), la

premiere devant tre precedee d'une etiquette, c'est-a-dire un nom qu'on lui donne. Celles-ci

sont regroupees dans le segment dinstructions delimite par les directives SEGMENT et

ENDS ;

- EnIin le Iichier doit tre termine par la directive END suivi du nom de l'etiquette de la

premiere instruction (pour permettre au compilateur de connatre la premiere instruction a

executer ;

Les points-virgules marquent le debut des commentaires, c'est-a-dire que tous les caracteres

situes a droite d'un point virgule seront ignores. Voici a quoi ressemble un Iichier source

(Iichier .ASM):

donnees SEGMENT ; voici le segment de donnees dont l'etiquette est donnees

;Placez ici les declarations de donnees

donnees ENDS ; ici se termine le segment de donnees

ASSUME DS:data, CS: code

instr SEGMENT ; voici le segment d'instructions dont l'etiquette est instr

;placez ici votre premiere instruction avec une etiquette

debut

debut :

;Placez ici vos instructions

instr ENDS ; Iin du segment d'instructions

END debut ; Iin du programme suivie de l'etiquette de la premiere instruction

J.2.1 La declaration dun segment.

Comme nous le verrons plus loin, les donnees sont regroupees dans une zone de la memoire

appele segment de donnees, tandis que les instructions se situent dans un segment

dinstructions. Le registre DS (Data Segment) contient le segment de donnees, tandis que le

registre CS (Code Segment) contient le segment d'instructions. C'est la directive ASSUME

qui permet d'indiquer a l'assembleur ou se situe le segment de donnees et le segment de code.

Puis il s'agit d'initialiser le segment de donnees:

MOV AX, nomdusegmentdedonnees

MOV DS, AX

J.2.2 A quoi ressemble une instruction?

L'instruction est l'element cle de l'ordinateur car c'est elle qui permet de speciIier au

processeur l'action a eIIectuer. Toutes les instructions sont stockees en memoire et un

compteur dans le processeur permet de passer de l'une a l'autre. Une instruction est composee

de deux elements:

le code operation: action a eIIectuer par le processeur;

le champ operande: donnee ou bien adresse de la case memoire contenant une donnee.

La taille d'une instruction, c'est-a-dire le nombre de bits qu'elle occupe en memoire depend de

l'instruction et de l'operande, elle est generalement de quelques octets (1 a 4). L'octet est

l'unite qui est utilisee generalement car elle est pratique pour le stockage de certaines donnees

(notamment les caracteres).

J.2.3 Les tvpes dinstructions.

code operation champ operande

L'ensemble des instructions est appele feu dinstruction. On peut les repartir selon plusieurs

categories selon le type d'action que son execution declenche.

J.2.3.1 Instructions daffectation.

Les instructions d'aIIectations permettent de Iaire des transIerts de donnees entre les registres

et la memoire, c'est-a-dire:

soit une ecriture (du registre vers la memoire)

soit une lecture (de la memoire vers un registre)

J.2.3.2 Instructions arithmetiques et logiques.

Ce type d'instructions porte sur le registre AX (l'accumulateur). Elles permettent d'eIIectuer

une operation entre le registre AX et une donnee puis stocker le resultat dans AX. Ces

instructions sont:

- l'addition: AX AX donnee

- la soustraction: AX AX - donnee

- incrementation: AX AX 1

- decrementation: AX AX - 1

- decalage a gauche

- decalage a droite

J.2.3.3 Instructions de comparaison.

Permet de comparer le registre AX a une donnee. Le resultat de la comparaison est indiquee

par les indicateurs (registre d`etat : Flags). Ces instructions (ainsi que les instructions de

branchements) sont necessaires pour permettre une "interactivite", c'est-a-dire qu'en Ionction

de certains parametres le programme va pouvoir avoir divers comportements. Sans ces

indicateurs les programmes auraient un comportement determine et le programme Ierait

constamment les mmes actions.

J.2.3.4 Les modes dadressage.

On appelle "mode d'adressage" la maniere dont la donnee est speciIiee dans une instruction.

Selon le mode d'adressage la taille de l'instruction peut varier de 1 a 4 octets.

Il existe 5 modes d'adressage:

le mode d'adressage implicite

le mode d'adressage immdiat

le mode d'adressage relatif

le mode d'adressage direct

le mode d'adressage indirect

J.2.3.4.1 Le mode dadressage implicite.

Le mode d'adressage implicite correspond a une instruction ne comportant pas d'operande.

L'instruction est composee du code operation uniquement et sa taille peut varier entre 1 octet

et 2 octets selon l'operation.

code operation (1 ou 2 octets)

Ce type d'instructions porte generalement sur des registres. Les operations d'incrementation

ou de decrementation d'un registre on un mode d'adressage implicite.

J.2.3.4.2 Le mode dadressage immediat.

On parle de mode d'adressage immediat lorsque le code operande contient une donnee. La

taille de la donnee peut varier entre 1 et 2 octets.

code operation (1 ou 2 octets) code operande (1 ou 2 octets)

Ce type d'instructions met en jeu un registre et une valeur (qu'il s'agisse d'une aIIectation, une

addition, une soustraction ou bien mme une comparaison), la taille de l'operande dependra

donc du type de registre mis en jeu (1 octet pour un registre 8 bits, 2 pour un registre de 16

bits).

Dans le cas de l'instruction MOJ BX,8 l'operande 8 sera codee sur 16 bits puisqu'il Iaut

l'aIIecter a un registre 16 bits (BX).

J.2.3.4.3 Le mode dadressage relatif.

Ce type de mode d'adressage met en jeu un champ operande contenant un entier relatiI (sa

taille est donc un octet).

code operation (1 octet) code operande (1 octet)

On l'utilise pour les operations de saut, l'entier relatiI est appele deplacement, il correspond a

la longueur du saut que le processeur doit eIIectuer dans les instructions.

J.2.3.4.4 Le mode dadressage direct.

Le code operande d'une instruction en mode d'adressage direct, contrairement au mode

d'adressage immediat, contient l'adresse d'une donnee en memoire (au lieu de contenir la

donnee). Une adresse etant codee sur 16 bits, la taille du champ operande est donc de 2 octets.

code operation (1 ou 2 octets) code operande (2 octets)

Il peut s'agir par exemple de l'aIIectation a un registre d'une donnee contenue dans une case

memoire. Ce mode d'adressage provoque un temps d'execution de l'instruction plus long car

l'acces a la memoire principale est plus long que l'acces a un registre.

J.2.3.4.5 Le mode dadressage indirect.

Le mode d'adressage indirect permet d'acceder a une donnee par l'intermediaire d'un registre

(par exemple le registre BX) qui contient son adresse. Son utilite n'est pas apparente a ce

stade, mais l'adressage indirect est tres utile lors de l'utilisation de tableaux (parcours des

cases d'un tableau) car il suIIit d'incrementer BX de la taille d'une case pour passer d'une case

a une autre...En adressage directe, on aIIecte directement au registre accumulateur (AX)

l'adresse d'une donnee : MOX AX, 110h] En adressage indirect, on aIIecte a AX l'adresse

contenue dans le registre BX : MOV AX, BX].

J.2.3.5 Instructions arithmetiques.

Les instructions arithmetiques et logiques sont eIIectuees par l'unite arithmetique et logique. Il

s'agit d`operations directement eIIectuees sur les bits de la donnee que l'on traite. Ces

instructions sont :

- les instructions d'addition;

- les instructions de soustraction;

- les instructions de decalage;

- les instructions de rotation;

- les instructions logiques (ET, OU, ...).

Toutes les operations arithmetiques et logiques modiIient l'etat des indicateurs.

J.2.3.5.1 Instructions daddition.

Les operations arithmetiques se Iont de la mme Iaon en binaire qu'en base decimale. C'est-

a-dire que lorsque l'on depasse la valeur maximale au niveau du bit n (lorsque l'on depasse la

valeur 1) on a une retenue ou un report au bit n1.

Voyons voir cela sur un exemple:

0001

0001

0010

Sur un exemple un peu plus complique:

0010

0011

- - - -

0101

J.2.3.5.2 Instructions de decalage et de rotation.

Ces instructions permettent de decaler d'un cte ou de l'autre les bits des registres

accumulateurs (AX et BX, et donc AH, AL, BH, BL). Cette operation qui semble inutile a en

Iait plusieurs applications tres interessantes, dont:

- permettre de lire un a un les bits du registre (car les bits sortant a gauche positionnent

l'indicateur de retenue CF : bit de retenu);

- permettre une multiplication par 2

n

(en eIIet le Iait de decaler un nombre binaire d'un chiIIre

a gauche le multiplie par 2, ainsi en eIIectuant cette operation n Iois on obtient une

multiplication par 2

n

). Par exemple:

00010 (2 en decimale)

00100 (on decale a gauche on obtient 4)

01000 (on decale a gauche encore une Iois on obtient 8)

- permettre une division par 2

n

(comme precedemment mais en eIIectuant une rotation sur la

droite);

Une opration de dcalage deplace chacun des bits d'un nombre binaire sur la gauche (ou la

droite), mais ceux-ci sortent, c'est-a-dire qu'ils sont deIinitivement perdus, lorsqu'ils arrivent

au bit de poids Iort (ou de poids Iaible). Par exemple:

0001110000 ;

0011100000 (on decale d'un bit a gauche);

0111000000 (on decale d'un bit a gauche);

1110000000 (on decale d'un bit a gauche);

1100000000 (on decale d'un bit a gauche);

1000000000 (on decale d'un bit a gauche).

Une opration de rotation agit comme une operation de decalage a la diIIerence pres que les

bits qui sortent d'un cte rentrent de l'autre. Par exemple:

0001110000 ;

0011100000 (on eIIectue une rotation d'un bit a gauche);

0111000000 (on eIIectue une rotation d'un bit a gauche);

1110000000 (on eIIectue une rotation d'un bit a gauche);

1100000001 (on eIIectue une rotation d'un bit a gauche);

1000000011 (on eIIectue une rotation d'un bit a gauche).

Les operations courantes de rotation et de decalage sont les suivantes:

- RCL registre, 1 (Rotate Carrv Left): EIIectue une rotation des bits sur la gauche en passant

par l'indicateur de retenue CF. Le contenu de CF est introduit a droite, puis le bit de poids Iort

est copie dans CF;

- RCR registre, 1 (Rotate Carrv Right): EIIectue une rotation des bits sur la droite en passant

par l'indicateur de retenue CF. Le contenu de CF est introduit a gauche, puis le bit de poids

Iaible est copie dans CF;

- ROL registre, 1 (Rotate Left): EIIectue une rotation des bits sur la gauche. Le bit de poids

Iort est copie dans CF et reintroduit a droite;

- ROR registre, 1 (Rotate Right): EIIectue une rotation des bits sur la droite. Le bit de poids

Iaible est copie dans CF et reintroduit a gauche;

- SHL registre, 1 (Shift Left): Decale les bits du registre indique de 1 bit vers la gauche. (Les

bits sortants sont transIeres dans l'indicateur de retenue CF mais ne sont pas reintroduits a

droite);

- SHR registre, 1 (Shift Right): Decale les bits du registre indique de 1 bit vers la droite. (Les

bits sortants sont transIeres dans l'indicateur de retenue CF mais ne sont pas reintroduits a

gauche);

Les instructions RCL et RCR permettent de Iaire une lecture bit-a-bit du contenu du registre.

Les instructions SHL et SHR permettent de Iaire respectivement une multiplication par 2

n

et

une division 2

n

, sur des entiers naturels en supposant que n est le nombre de decalages.

J.2.3.5.3 Instructions logiques.

Les instructions logiques sont au nombre de trois (ET, OU et OU ExclusiI). Elles permettent

de Iaire des operations bit-a-bit sur des nombres binaires (c'est-a-dire en considerant chacun

des bits independamment des autres, sans se soucier de la retenue). Ce type d'instruction se

note de la maniere suivante: INSTRUCTION destination, source. Avec destination designe

le registre ou l'adresse de la case memoire qui contiendra le resultat de l'operation et source

peut tre aussi bien un registre, une constante ou une adresse.

L'instruction AND (ET) multiplie les bits de mme poids deux a deux et stocke le resultat

dans le registre de destination. Cette instruction met donc le bit du resultat a 1 si les deux bits

de mme poids de la source et de la destination sont tous deux a 1, sinon il le met a zero. Par

exemple:

0101

ET 0110

- - - -

0100

L'instruction OR (OU) met le bit du resultat a 0 si les deux bits de mme poids de la source et

de la destination sont tous deux a 0, sinon il le met a un. Par exemple:

0101

OU 0110

- - - -

0111

L'instruction XOR (OU ExclusiI) met le bit du resultat a 1 si un des deux bits de mme poids

de la source et de la destination est egal a 1 (mais pas les deux), dans les autres cas il le met a

zero. Par exemple:

0101

0110

- - - -

0011

Chacune de ces instructions a de tres nombreuses applications, il serait impossible de toutes

les enumerer. En voici quelques unes:

- Masquage: Il est possible de masquer, c'est-a-dire mettre a zero tous les bits qui ne nous

interessent pas dans un nombre. Pour cela il Iaut creer une valeur masque: un nombre dont les

bits de poids qui nous interessent sont a 1, les autres a 0. Il suIIit alors de Iaire un AND entre

le nombre a masquer et le masque pour ne conserver que les bits auxquels on s'interesse. Par

exemple, imaginons que l'on veuille masquer les 4 bits de poids Iaible (les 4 derniers bits)

d'un nombre code sur 8 bits (par exemple 10110101). Il suIIit d'appliquer le masque

11110000, et l'on obtiendra 10110000. On ne conserve bien que les 4 premiers bits, les autres

sont mis a zero.

- Inversion: Il est possible d'inverser tous les bits d'un nombre en Iaisant un XOR avec un

nombre contenant que des 1.

J.2.3.6 Instructions de branchement.

On appelle saut (ou branchement) en assembleur le Iait de passer a une instruction autre que

celle qui suit celle en cour en memoire. En eIIet, en temps normal (c'est-a-dire sans

instruction contraire) le processeur execute les instructions sequentiellement, il execute

l'instruction situee a l'emplacement memoire suivant. C'est un registre special (le registre IP)

qui indique l'adresse de l'instruction suivante a executer. Dans certaines conditions il peut tre

interessant de "choisir" la prochaine instruction a eIIectuer. Ce type de condition peut

notamment se rencontrer dans les structures conditionnelles (saut si...) ou bien dans les

structures de boucle (en eIIet dans le cas ou on desire executer un grand nombre de Iois une

instruction il peut tre interessant d'utiliser une instruction de branchement, qui indique au

processeur l'adresse de la prochaine instruction a executer au lieu de gaspiller la memoire en

stockant plusieurs Iois la mme instruction en memoire). Lors de l'execution "normale" d'un

programme, le processeur lit l'adresse contenue dans le registre IP, incremente celui-ci pour

qu'il pointe vers l'instruction suivante, puis execute l'instruction contenue a l'adresse qu'il

vient de lire. Lorsqu'il rencontre une instruction de saut (ou branchement), celle-ci va lui Iaire

modiIier le contenu du registre IP pour qu'il pointe a l'adresse d'une autre instruction On

distingue ces instructions de saut en deux categories suivant que:

- le saut est eIIectue quoi qu'il arrive (saut inconditionnel);

- le saut est eIIectue ou non selon l'etat d'un registre (saut conditionnel).

J.2.3.6.1 Saut inconditionnel.

L'instruction JMP permet d'eIIectuer un saut inconditionnel, c'est-a-dire que cette instruction

va stocker dans le registre IP l'adresse de l'instruction que l'on veut executer. L'operande de

cette instruction (le parametre) est donc l'adresse de l'instruction a laquelle on veut sauter.

Une Iois l'instruction de branchement executee le processeur lit le contenu du registre IP et

saute donc directement a l'adresse de l'instruction que l'on vient de deIinir. On appelle

deplacement (en anglais offset) le nombre d'octets (car il s'agit d'un nombre entier relatiI code

sur 8 bits) qui separent l'instruction suivante de l'instruction visee. Voyons voir cela sur le

programme suivant:

Adresse

Instruction en

assembleur

Commentaire

0100H MOV AX, |120h|

copie le contenu de la case memoire a l'adresse 0120H dans

le registre AX.

0103H JMP 0100h saute a l'adresse 0100.

0104H MOV |120h|, BX instruction non executee a cause du saut precedent...

La valeur du deplacement est ici de: 0100H - 0104H -4.

J.2.3.6.2 Saut conditionnel.

Les instructions de saut conditionnel permettent d'eIIectuer un saut suivant une condition. Si

celle-ci est realisee le processeur saute a l'instruction demandee, dans le cas contraire il ignore

cette instruction et passe automatiquement a l'instruction d'apres, comme si cette instruction

n'existait pas. Les conditions pour chacune de ces instruction sont Ionction de l'etat de

registres speciIiques appeles indicateurs (en anglais flag, ce qui signiIie drapeau).

J.2.4 Les indicateurs.

Les indicateurs sont des registres dont l'etat est Iixe par l'UAL apres certaines operations. Les

indicateurs Iont partie de ce que l'on appelle le registre detat qui n'est pas directement

accessible par les autres instructions, seules des instructions speciIiques permettent de les

manipuler. Voyons voir certains de ces indicateurs:

- CF (Carry Flag):c'est l'indicateur de retenue. Il intervient lorsqu'il y a une retenue apres

une addition ou une soustraction entre des entiers naturels. Lorsqu'il y a une retenue il est

positionne a 1, dans le cas contraire a 0;

- OF (Overflow Flag):cet indicateur (indicateur de debordement: overflow debordement)

intervient lorsqu'il y a un debordement, c'est-a-dire lorsque le nombre de bits sur lesquels les

nombres sont code n'est pas suIIisant et que le resultat d'une operation n'est pas codable avec

le nombre de bit speciIie (il peut par exemple arriver dans ces conditions que la somme de

deux nombres positiIs donnent un nombre negatiI). Dans ce cas l'indicateur OF est positionne

a 1.

- SF (Sign Flag): c'est l'indicateur de signe. SF donne tout simplement le signe du bit de poids

Iort. Or, le bit de poids Iort donne le signe du nombre (1 si le signe est negatiI, 0 s'il est

positiI). Il simpliIie le test du signe d'un entier relatiI;

- ZF (Zero Flag): L'indicateur de zero permet de savoir si le resultat de la derniere operation

etait nul. En eIIet, dans ce cas, l'indicateur ZF est positionne a 1 (0 dans le cas contraire). Il

permet notamment de determiner si deux valeurs sont egales, en eIIectuant leur soustraction,

puis en observant l'etat de l'indicateur de zero;

Voyons voir les etats de ces indicateurs sur un exemple:

0110

0101

- - - -

1011

- OF1 (la somme de deux nombres positiIs est negative;

- ZF0 (le resultat 1011 n'est pas nul);

- SF1 (le signe du resultat est negatiI);

- CF0 (il n'y a pas de retenue.

Les instructions STC et CLC permettent de positionner "manuellement" l'indicateur de

retenue (CF). L'instruction STC (SeT Carry) positionne l'indicateur CF a 1. L'instruction CLC

(CLear Carry) positionne CF a 0.

J.2.4 Instruction de comparaison.

L'instruction CMP permet de tester la valeur d'un registre (Exemple AX) avec une autre

valeur. Sa seule action est de positionner l'indicateur ZF a 1 en cas d'egalite, ou plus

exactement lorsque la soustraction des deux valeurs donne un resultat nul. En ce sens il

eIIectue la mme chose que SUB a la seule diIIerence pres qu'il ne modiIie pas les operandes.

Par exemple, l'instruction: CMP AX, 2 positionne a 1 l'indicateur ZF si la valeur contenue

dans le registre AX vaut 2, dans le cas contraire il le met a zero.

J.2.5 Les instructions de sauts conditionnels.

Les branchements conditionnels (ou sauts conditionnels) permettent au processeur de traiter

l'instruction situee a un emplacement memoire indique si une certaine condition est veriIiee.

Dans le cas contraire (condition non realisee), le processeur ignorera cette instruction, il

traitera donc l'instruction suivante. La (ou les) condition(s) a satisIaire depend(ent) de l'etat

d'indicateurs. Ainsi les branchements conditionnels doivent generalement tre placee apres

une operation qui va modiIier l'etat d'un ou plusieurs indicateurs (une instruction CMP ou

autre). Selon l'intitule de l'instruction, les conditions a satisIaire sont diIIerentes:

- 1A(Jump if above, ce qui signiIie saute si au-dela)EIIectue un saut siZF0 et CF0;

- 1B(Jump if Below, ce qui signiIie saute si en-dea): EIIectue un saut siCF1;

- 1BE(Jump iI Below or Equal, ce qui signiIie saute si en-dea ou egal): EIIectue un saut s

ZF1 ou CF1;

- 1E(Jump iI Equal, ce qui signiIie saute si egalite EIIectue un saut siZF1;

- 1G(Jump if Greater, ce qui signiIie saute si superieur). EIIectue un saut siZF0 et

SFOF;

- 1LE(Jump iI Lower or Equal, ce qui signiIie saute si inIerieur ou egal): EIIectue un saut si

ZF1 ou SF diffrent de OF;

- 1NE(Jump iI Not Equal, ce qui signiIie saute si non-egalite): EIIectue un saut siZF0

J.3 Notion de procedure.

La notion de procedure en assembleur correspond a celle de Ionction en langage C, ou de

sous-programme dans d'autres langages.

Figure 4.9 Appel d'une procdure.

Dans cet exemple, la procedure est nommee calcul. Apres l'instruction B, le processeur passe

a l'instruction C de la procedure, puis continue jusqu'a rencontrer RET et revient a

l'instruction D. Une procedure est une suite d'instructions eIIectuant une action precise, qui

sont regroupees par commodite et pour eviter d'avoir a les ecrire a plusieurs reprises dans le

programme. Les procedures sont reperees par l'adresse de leur premiere instruction, a laquelle

on associe une etiquette en assembleur. L'execution d'une procedure est declenchee par un

programme appelant. Une procedure peut elle-mme appeler une autre procedure, et ainsi de

suite.

J.3.1 Instructions CALL et RET.

L'appel d'une procedure est eIIectue par l'instruction CALL. CALL adressedebutprocedure

L'adresse peut tre sur 16 bits, la procedure est donc dans le mme segment d'instructions ou

sur 32 bits lors d`un appel inter-segment (Far Call). La Iin d'une procedure est marquee par

l'instruction RET. Le processeur passe alors a l'instruction placee immediatement apres le

CALL. RET est aussi une instruction de branchement : le registre IP (pointeur d`instructions)

est modiIie pour revenir a la valeur qu'il avait avant l'appel par CALL. On peut avoir un

nombre quelconque d'appels imbriques, comme sur la Iigure ci dessous. L'adresse de retour,

utilisee par RET, est en Iait sauvegardee sur la pile par l'instruction CALL. Lorsque le

processeur execute l'instruction RET, il depile l'adresse sur la pile (comme POP), et la range

dans IP.

Figure 4.1 Plusieurs appels de procdures imbriqus.

L'instruction CALL eIIectue donc les operations :

- Empiler la valeur de IP. A ce moment, IP pointe sur l'instruction qui suit le CALL.

- Placer dans IP l'adresse de la premiere instruction de la procedure (donnee en argument).

Et l'instruction RET :

- Depiler une valeur et la ranger dans IP.

J.3.2 Declaration dune procedure.

L'assembleur possede quelques directives Iacilitant la declaration de procedures.

On declare une procedure dans le segment d'instruction comme suit :

Calcul PROC near ; procedure nommee Calcul

... ; instructions

RET ; derniere instruction

Calcul ENDP ; Iin de la procedure

Le mot cleI PROC commence la deIinition d'une procedure, near indiquant qu'il s'agit d'une

procedure situee dans le mme segment d'instructions que le programme appelant. L'appel

s'ecrit simplement :

CALL Calcul

En general, une procedure eIIectue un traitement sur des donnees (parametres) qui sont

Iournies par le programme appelant, et produit un resultat qui est transmis a ce programme.

Plusieurs strategies peuvent tre employees :

1. Passage par registre . les valeurs des parametres sont contenues dans des registres du

processeur. C'est une methode simple, mais qui ne convient que si le nombre de parametres

est petit (il y a peu de registres).

2. Passage par la pile . les valeurs des parametres sont empilees. La procedure lit la pile.

J.3.2.1 Passage de parametres par registres.

Exemple avec passage par registre : On va ecrire une procedure ''SOMME'' qui calcule la

somme de 2 nombres naturels de 16 bits. Convenons que les entiers sont passes par les

registres AX et BX, et que le resultat sera place dans le registre AX. La procedure s'ecrit alors

tres simplement :

SOMME PROC near ; AX - AX BX

ADD AX, BX

RET

SOMME ENDP

et son appel, par exemple pour ajouter 6 a la variable var :

MOV AX, 6

MOV BX, var

CALL SOMME

MOV var, AX

J.3.2.2 Passage de parametres par piles.

Exemple avec passage par la pile : Cette technique met oeuvre un nouveau registre, BP (Base

Pointer), qui permet de lire des valeurs sur la pile sans les depiler ni modiIier SP. Le registre

BP permet un mode d'adressage indirect special, de la Iorme :

MOV AX, BP+6]

Cette instruction charge le contenu du mot memoire d'adresse BP+6 dans AX. Ainsi, on lira le

sommet de la pile avec :

MOV BP, SP ; BP pointe sur le sommet

MOV AX, BP] ; lit sans depiler

et le mot suivant avec :

MOV AX, BP+2] ; 2 car 2 octets par mot de pile.

L'appel de la procedure ''SOMME2'' avec passage par la pile est :

PUSH 6

PUSH var

CALL SOMME2

La procedure SOMME2 va lire la pile pour obtenir la valeur des parametres. Pour cela, il Iaut

bien comprendre quel est le contenu de la pile apres le CALL :

SP IP (adresse de retour)

SP2 var (premier parametre)

SP4 6 (deuxieme parametre)

Le sommet de la pile contient l'adresse de retour (ancienne valeur de IP empilee par CALL).

Chaque element de la pile occupe deux octets.

La procedure SOMME2 s'ecrit donc :

SOMME2 PROC near ; AX - arg1 arg2

MOV BP, SP ; adresse sommet pile

MOV AX, |BP2| ; charge argument 1

ADD AX, |BP4| ; ajoute argument 2

RET

SOMME2 ENDP

La valeur de retour est laissee dans AX. La solution avec passage par la pile parait plus lourde

sur cet exemple simple. Cependant, elle est beaucoup plus souple dans le cas general que le

passage par registre. Il est tres Iacile par exemple d'ajouter deux parametres supplementaires

sur la pile. Une procedure bien ecrite modiIie le moins de registres possible. En general,

l'accumulateur est utilise pour transmettre le resultat et est donc modiIie. Les autres registres

utilises par la procedure seront normalement sauvegardes sur la pile. Voici une autre version

de SOMME2 qui ne modiIie pas la valeur contenue par BP avant l'appel :

SOMME2 PROC NEAR ; AX - arg1 arg2

PUSH BP ; sauvegarde BP

MOV BP, SP ; adresse sommet pile

MOV AX, |BP4| ; charge argument 1

ADD AX, |BP6| ; ajoute argument 2

POP BP ; restaure ancien BP

RET

SOMME2 ENDP

Noter que les index des arguments (BP4 et BP6) sont modiIies car on a ajoute une valeur

au sommet de la pile.

J.4 Traduction en assembleur du langage C sur PC.

Nous nous interessons dans cette section a la traduction en assembleur des programmes en

langage C sur PC (processeurs de la Iamille 80x86 que nous avons un etudie auparavant). Le

detail de cette traduction (ou compilation) depend bien entendu du compilateur utilise et du

systeme d'exploitation (DOS, Windows, UNIX,...). Il depend aussi de divers reglages

modiIiables par le programmeur : taille du type int (16 ou 32 bits), modele de memoire utilise

(pointeurs sur 16 ou 32 bits, donnees et code dans des segments diIIerents ou non, etc.).

Nous n'aborderons pas ces problemes dans ce cours (voir la documentation detaillee du

compilateur utilise si besoin), mais nous etudierons quelques exemples de programmes C et

leurs traductions. Le compilateur utilise est Turbo C version 3 (en mode ANSI C) sous

DOS, avec des entiers de 16 bits et le modele de memoire ''small''. Normalement, ce

compilateur genere directement du code objet (Iichier .OBJ) a partir d'un Iichier source en

langage C (Iichier .C ou .CPP). Il est cependant possible de demander l'arrt de la compilation

pour obtenir du langage assembleur (Iichier .ASM). Pour cela, utiliser sous DOS la

commande :

tcc -S exemple.c

Un Iichier exemple.asm est alors cree. Considerons le programme en langage C suivant :

/* Programme EXEMPLE1.c en langage C */

void main(void)

char X 11;

char C 'A';

int Res;

iI (X 0)

Res -1;

else

Res 1;

}

Trois variables, X, C et Res sont deIinies avec ou sans valeur initiale. Ensuite, on teste le

signe de X et range 1 ou -1 dans la variable Res.

Le programme suivant montre la traduction en assembleur eIIectuee par Turbo C.

TEXT SEGMENT byte public 'CODE'

;

; void main(void)

;

ASSUME cs:TEXT

main PROC near

PUSH bp

MOV bp,sp

SUB sp, 4

;

; char X 11;

;

MOV byte ptr |bp-1|, 11

;

; char C 'A';

;

MOV byte ptr |bp-2|, 65

;

; int Res;

; iI (X 0)

;

CMP byte ptr |bp-1|, 0

JGE 186

;

; Res -1;

;

MOV word ptr |bp-4|, 65535

JMP 1114

186:

;

; else

; Res 1;

;

MOV word ptr |bp-4|, 1

1114:

;

; }

;

MOV sp,bp

POP bp

RET

main ENDP

TEXT ENDS

END

Remarquons les points suivants :

1. La Ionction main() est consideree a ce stade comme une procedure ordinaire (PROC

near). C'est plus tard, lors de la phase d'edition de lien, qu'il sera indique que la Ionction

main() correspond au point d'entree du programme (premiere instruction a executer). La

Ionction est terminee par l'instruction RET.

2. On n'utilise pas ici de segment de donnees : toutes les variables sont allouees sur la pile.

3. L'allocation des variables sur la pile s'eIIectue simplement en soustrayant au pointeur SP le

nombre d'octets que l'on va utiliser (ici 4, car 2 variables X et C d'un octet, plus une variable

Res de 2 octets).

4. La ligne X 11 est traduite par :

MOV byte ptr |bp-1|, 11

Noter l'utilisation de byte ptr pour indiquer que BP contient ici l'adresse d'une donnee de taille

octet. Le test iI (X 0) est traduit par une instruction CMP suivie d'un branchement

conditionnel, utilisant une etiquette placee par le compilateur (d'ou son nom etrange :

1114). Chaque langage de programmation doit deIinir une convention de passage des

parametres lors des appels de procedures ou de Ionctions. Cette convention permet de prevoir

l'etat de la pile avant, pendant et apres un appel de Ionction (dans quel ordre sont empiles les

parametres ? Qui est responsable de leur depilement ? Comment est passee la valeur de

retour ?). Etudions a partir d'un exemple simple comment sont passes les parametres lors des

appels de Ionctions en langage C.

/* Programme EXEMPLE2.C */

int maIonction( int x, int y )

return x y;

}

void main(void)

int X 11;

int Y 22;

int Res;

Res maIonction(X, Y);

}

La traduction en assembleur de ce programme (eIIectuee par Turbo C) donne le programme

suivant :

TEXT SEGMENT byte public 'CODE'

;

; int maIonction( int x, int y )

ASSUME cs:TEXT

maIonction PROC near

PUSH bp

MOV bp,sp

;

; return x y;

;

MOV ax, |bp4|

ADD ax, |bp6|

; }

POP bp

RET

maIonction ENDP

;

; void main(void)

;

ASSUME cs:TEXT

main PROC near

PUSH bp

MOV bp,sp

SUB sp,6

; int X 11;

MOV |bp-2|, 11

; int Y 22;

MOV |bp-4|, 22

;

; int Res;

; Res maIonction(X, Y);

PUSH word ptr |bp-4|

PUSH word ptr |bp-2|

CALL maIonction

ADD sp, 4

MOV |bp-6|,ax

; }

MOV sp,bp

POP bp

RET

main ENDP

TEXT ENDS

En etudiant cet exemple, on constate que :

1. la Ionction C ma_fonction() a ete traduite par une procedure assembleur nommee

_ma_fonction, qui lit ses arguments sur la pile a l'aide de la technique que nous avons vue

plus haut.

2. la Ionction ne modiIie pas l'etat de la pile;

3. Avant l'appel de la Ionction (CALL ), les arguments sont empiles (PUSH). Apres le retour

de la Ionction, le pointeur SP est incremente pour remettre la pile dans son etat precedent

(ADD sp, 4 est equivalent a deux instructions POP 2 octets).

5. La valeur retournee par la Ionction est passee dans AX (d'ou l'instruction MOV bp-6], ax).

Le respect des conventions d'appel de procedures est bien entendu tres important si l'on desire

melanger des Ionctions C et des procedures en assembleur.

You might also like

- Raccourcis ClavierDocument3 pagesRaccourcis ClavierKhalid Mac100% (2)

- Cours Ipv6Document78 pagesCours Ipv6abdel dalilNo ratings yet

- TP ScalaDocument2 pagesTP ScalafafaNo ratings yet

- Support TP - Admin Rés Et Environnement Client ServeurDocument75 pagesSupport TP - Admin Rés Et Environnement Client ServeurEne Shi100% (1)

- Série D'exercices N°1 - Chimie - Notion D'avancement D'une Réaction Chimique - Bac M SC Exp (2009-2010) MR Soudani ElyesDocument2 pagesSérie D'exercices N°1 - Chimie - Notion D'avancement D'une Réaction Chimique - Bac M SC Exp (2009-2010) MR Soudani Elyesأبوأحمد الجزيري75% (8)

- Série D'exercices N°1 - Chimie - Notion D'avancement D'une Réaction Chimique - Bac M SC Exp (2009-2010) MR Soudani ElyesDocument2 pagesSérie D'exercices N°1 - Chimie - Notion D'avancement D'une Réaction Chimique - Bac M SC Exp (2009-2010) MR Soudani Elyesأبوأحمد الجزيري75% (8)

- Fiche Pedagogique Les Structures de DonnéesDocument6 pagesFiche Pedagogique Les Structures de DonnéesSâkly ChihèbNo ratings yet

- MahdiaSousse PDFDocument1 pageMahdiaSousse PDFعائشة بيوضNo ratings yet

- Chapitre 3 Cours 1Document33 pagesChapitre 3 Cours 1Rania AkrourNo ratings yet

- Raport de Stage Sur Présentation Siwtch 5500-1.2.3Document21 pagesRaport de Stage Sur Présentation Siwtch 5500-1.2.3Carol MarinhoNo ratings yet

- 6 Séance 3Document5 pages6 Séance 3Gregory CollinNo ratings yet

- 6.3.3.7 Lab - Configuring 802.1Q Trunk-Based Inter-VLAN RoutingDocument8 pages6.3.3.7 Lab - Configuring 802.1Q Trunk-Based Inter-VLAN Routingعاطف غضبانيNo ratings yet

- ZigBee 2PDocument21 pagesZigBee 2PAbdelkhalek BenhimaNo ratings yet

- TP2 Administration Du CME-VoIPDocument4 pagesTP2 Administration Du CME-VoIPkamdem bocheng joelNo ratings yet

- Administration Linux Partie IIIDocument77 pagesAdministration Linux Partie IIIrajae ansariNo ratings yet

- Introduction À L'asynchroneDocument2 pagesIntroduction À L'asynchroneYesmine MakkesNo ratings yet

- Documentation InterruptionsDocument14 pagesDocumentation Interruptionszbhp zNo ratings yet

- Adressage IP v4 - Routage 1 - Exercice Résolu - Sébastien Adam, Un Développeur Hors Du Commun PDFDocument2 pagesAdressage IP v4 - Routage 1 - Exercice Résolu - Sébastien Adam, Un Développeur Hors Du Commun PDFJeanNo ratings yet

- Allocation Dynamique de MémoireDocument43 pagesAllocation Dynamique de Mémoireebelle harryNo ratings yet

- TP HaproxyDocument3 pagesTP HaproxyBAILA ATHIMAN ROLANDNo ratings yet

- Cours TCP-IPDocument25 pagesCours TCP-IPArmos100% (1)

- TD Proc AssembleurDocument2 pagesTD Proc AssembleurWejdène GuedriNo ratings yet

- Examen TP 02-02-2011 CompressedDocument2 pagesExamen TP 02-02-2011 Compressedخالد خالدNo ratings yet

- Installation SAP GUI - WindowsDocument23 pagesInstallation SAP GUI - WindowsOussama LachhabNo ratings yet

- ITN Module 13 094452Document26 pagesITN Module 13 094452Ibrahima Sory BahNo ratings yet

- FR Notice D Utilisation Mapcarev2.476217Document6 pagesFR Notice D Utilisation Mapcarev2.476217Brian QuatreNo ratings yet

- ITE7 Chp10Document20 pagesITE7 Chp10Mamadou yahya BarryNo ratings yet

- Chapitre 9Document12 pagesChapitre 9Mich le TwinsNo ratings yet

- Schemas NGN 1Document8 pagesSchemas NGN 1Danra Emmanuel MarcusNo ratings yet

- Linux - Chap3 Gestion de FichiersDocument60 pagesLinux - Chap3 Gestion de FichiersOuerghiMohamedSaidNo ratings yet

- Projet ScientifiqueDocument18 pagesProjet ScientifiqueAmine LamaneNo ratings yet

- Main 1Document54 pagesMain 1Nejwa ParadNo ratings yet

- Sujet TP SambaDocument2 pagesSujet TP SambaImade EddineNo ratings yet

- Cluster Et Réplication - Les Moyens Techniques de La Haute DisponibilitéDocument6 pagesCluster Et Réplication - Les Moyens Techniques de La Haute Disponibilitékingmo644No ratings yet