Professional Documents

Culture Documents

ECE Department Objective Questions on VLSI Design Topics

Uploaded by

vikramvsuOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ECE Department Objective Questions on VLSI Design Topics

Uploaded by

vikramvsuCopyright:

Available Formats

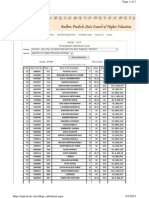

NARAYANA ENGINEERING COLLEGE::NELLORE/GUDUR DEPARTMENT OF ECE

ACADEMIC YEAR: 2012 2013 OBECTIVE QUESTIONS Subject: VLSI Design (R 09) ,Common to ECE &EIE Class : I11B.TECH. II SEM Faculty : K.Murali/ B. Gopichandra kumar/ R.Gunasekhar

UNIT - 1

Multiple choice 1. The speed power product of any MOS technology is measured in [ C ] a)KJ b) MW-sec c) PJ d) Joules 2. For depletion mode MOSFET, threshold voltage [ D ] a) 0.2 V DD b) -0.2 V DD c) 0.8 V DD d) -0.8 V DD 3. The technology which is characterized by high speed [ D ] a)CMOS b) BICMOS c) GaAs d)ECL 4. Latch up in CMOS device can be avoided by [ B ] A) Increasing temp b) doping control c) increasing the substrate resistance d)decreasing substrate doping level 5. Material used for metallization is [ A ] a)Aluminum b) copper c)silver d)tungsten 6. Material used for gate oxide in MOS technology. [ C ] a) Si b) Ge c) Sio2 d) AlO2 7. Poly silicon is a _________ material [ C ] a) Crystalline b) Amorphous c) Poly crystalline d) None 8. Silicide is combination of [ A ] a) Metal poly b) Metal-Silicon c) Metal-Ge d) Metal-SiO2 9. In modern CMOS fabrication, the pattern on each layer is created by a) Ion implantation b) Oxidation c) Photo lithography d) Encapsulation 10. The advantage of twin- tub process [ C ] a) Low complexity b) Low cost depletion c) Latch up immunity d) high mask count Fill in the blanks: 11. Expansion of CVD is ___chemical vapour deposition___________ 12.______Electron_______________ lithography is preferred in submicron device dimension 13. The kinetics of thermal oxidation is modeled by ___deal and groover___________________model. 14. The static power dissipation in CMOS technology is _____zero__________ 15. In normal mode of operation in CMOS, substrate terminal of NMOS is connected to ____vss_______ and substrate terminal of PMOS is connected to ___vdd________ 16. CMOS technology is high delay than ____bipolar_______________ Technology 17. The deficiency of MOS technology is ___limited load driving capacity_____________________ 18. Under DEPLETION mode NMOS is ____ON____________state. 19. NMOS FETs are ___faster_________than PMOS FETs 20. Power dissipation in NMOS technology is ____high_______compared to CMOS technology.

UNIT - 2

Multiple choice 1. MOSFET operated in saturation when [ C ] (a) Vds = vgs-vt (b) vds < vgs-vt (c) Vds > vgs-vt (d) Vds < vt 2. For faster NMOS circuits, one would choose the following type of substrate [ B ] (a) 110 Oriented n - type substrate (c) 111 Oriented p - type substrate (b) 100 oriented p - type substrate (d) 111 oriented n- type substrate 3. Pull up to pull down ratio for n MOS inverter driven by another n MOS inverter is [ D ] (a) 4:4 (b) 4:1 (c) 1:4 (d) 8:1

4. The following device is less likely to suffer latch up [ C ] (a)n MOS (b) CMOS (c) BICMOS (d) PMOS 5. In CMOS inverter if n=p & if Vtn =Vtp, then the logic levels are disposed about at a point where [ C ] (a)VIN = Vout = 0.1 VIN (b VIN = 0.5 VDD (c) VIN = Vout =0.5 VDD (d) VIN = Vout = VDD 6. The figure of merit of MOS transistor can be expressed as [ C ] a) g m Cg b)

cg gm

c)

gm cg

d) [ D ] c) 1250 cm2/V.sec

2

d) 480 cm2/V.sec

7. Typical mobility of holes (Bulk) is a) 650cm2/V.sec b) 240 cm2/V.sec

8. Pickup the true statement with respect to Bi-CMOS Inverter [ C ] a) Low input impedance b) High output impedance c) high noise margin d) Low driving capability 9. To achieve best performance NMOS inverter transfer characteristics, Zpu/Zpd ratio should be a) Zero b) One c) As low as possible d) As high as possible [ C ] 10. Number of transistors to implement three-input AND gate using pass transistor logic is a) 6 b) 3 c) 5 d) 9 [B ] Fill in the blanks: 11. An inverter driven through one or more pass transistor should have Zpu/Zpd ratio of_ _____8 : 1_______ 12. The threshold voltage is increased due to ___body effect_________________ 13. More lightly doped substrate ___________less___________ will be the body effect 14. The drain- source current (IDS) for NMOS under saturation can be expressed as___________ 15. Transconductance of MOS transistor (gm) is expressed as__________ 16. For devices of similar dimension n-channel is ___faster________ than the p channel 17. A simple BICMOS inverter has ___high____input impedance and__low____ output impedance 18. The power dissipation is ___low______in CMOS technology. 19. Bi-CMOS inverter has high driving capability than ___cmos____technology . 20. For high performance CMOS inverter

n p

should be__low______

UNIT 3

Multiple choices 1. The color encoding for polysilicon is [ A (a) Red (b) Green (c) Blue (d) Orange 2. The color encoding of VIA in double metal CMOS p-well process [ B a) Red b) Black c) Brown d) Yellow 3. Metal 1 to metal 1 spacing in layout design is [ C (a) 4 (b) 2 (c) 3 ( d) 1 4. The buried contact is made between [ B (a) Poly to metal (b) poly to diff (c) poly to diff using metal (d) Metal to metal 5.In NMOS layout design style, the colour of contact cut [ A ] a) Black b) Green c) Blue d) Red ] ] ] ]

6. What is color of metal 1 (CMOS encoding) [ B a) Black b) Blue c) Red d) Yellow 7. The p-type transistors are placed above the [ C a) Poly silicon b) diffusion c) Demarcation line d) metal 8. The minimum gap between diffusion and diffusion is [ A a) 2 b) 5 c) 7 d) 10 9. The size of a transistor is usually designed in terms of [ D a) Drain b) source c) metal d) channel length 10. According to 2m CMOS technology, the minimum separation between contact cuts a) 2 m b) 4 m c) 6 m d) 5 m [ B

] ] ] ] ]

Fill in the blanks 11. The layer preferred for global distribution of power buses is __METAL 2________________ 12._____STICK DIAGRAM___________________ is used to convey layer information. 13. For CMOS circuits stick encodings for demarcation line is ___BROWN________________in color. 14. The power and ground lines often called _______POWER RANGE__________ 15. The minimum width of metal 1 layer is _________3 _____________ 16. A __MOS TRANSISTOR_________is formed wherever polysilicon crosses Diffusion 17. Metal 1 for_____LOCAL DISTRIBUTION_______ and metal 2 for __GLOBAL DISTRIBUTION_______of power lines in stick notation 18. The minimum polysilicon width is______2 __________19. As fabrication technology improves, the heat sink size___REDUCES__________ 20. In CMOS design style, Demarcation line is shown by__DOTTED LINE__________

UNIT 4

Multiple choice 1. Power dissipation per unit area is scaled by (a) (b) (c) (d) [ A] d) 0.1x10 2 pF/m2 [ C ] 2. Typical value of Diffusion capacitor(C area ) in 5 m technology a) 1.0x10 4 pF/m2 b) 1.0X10 2 pF/m2= c) 0.1x10 4 pF/m2 3. The rise time of CMOS inverters is a) = (b) = (c) = b) = [ C ]

4. The typical value of load capacitance is [ D ] a) CL < 10 4 cg (b) CL 10 4 cg (c) CL = 10 14 cg (d) CL 10 14 cg 5. The characteristics of a metal layer are [A ] a) Low R; low C b) low R; moderate C c) Low R; moderate C d) moderate R; high C 6. The typical sheet resistance of polysilicon for 5m is [ D ] a) 0-10 b) 10-14 c) 120 to 140 d) 15 to 100 7. The overall delay Td for n sections is given by [ B ] a) Td= nrc ( ) b) Td= n2 rc( ) c) Td = n2r2 c( ) d) Td= n r2 c( ) 8. Deposition of the metal/silicon alloy prior to sintering may be done with [ A ] a) Sputtering b) diffusion c) Implantation d) Metallization 9. What is the formula for Rise-time estimation [ A ]

a) Tr=

3C

p V DD

b) Tr =

3C v

p

c) Tr =

3C

DD

p V DD 2

d) Tr =

C V DD

L p

10. The formula for fall-time estimation in CMOS inverter is 2 2 3C 3C L L 3 C L a) Tf = b) Tf = c) Tf = p v DD p V DD n V DD

[ C d)

3C V DD 2

L n

Fill in the blanks 11. The propagation delay of n sections is given by ________________________________ 12. The layer in which metal is deposited on poly silicon is called _____SILICIDE________________ 13. The sheet resistance of pdiff is _____2 : 5_________ times that of n-diffusion. 14. The values for N-diffusion region are___0.4_______ times the P-diffusion regions. 15. Bi-CMOS technology is reasonably good for__HIGH LOW DRIVING CAPABILITY____________ 16. Power consumption in CMOS circuits depends on __FREQUENCY_____________at which they operate. 17. ___METAL 1_____ layer is suitable for routing Vdd or Vss 18. The ___LARGE CAPACITIVE__________________load cant be driven by a single inverter. 19. In Bi-Polar transistor collector current depends ____EXPONENTIALY____________on Vbe. 20. The Delay for Bi-CMOS inverter is _______REDUCED____________by a factor of h f e compared with a CMOS Inverter.

You might also like

- Transportation Engineering: Key ConceptsDocument130 pagesTransportation Engineering: Key ConceptsDEEPU GNo ratings yet

- Introduction to Transportation Engineering ProposalDocument2 pagesIntroduction to Transportation Engineering ProposalRaheel ADNANNo ratings yet

- Right of Way Manual - City of AtlantaDocument59 pagesRight of Way Manual - City of Atlantawho__cares100% (1)

- What Is Highway EngineeringDocument4 pagesWhat Is Highway EngineeringNagesh SinghNo ratings yet

- Lecture # 11 ELENDocument17 pagesLecture # 11 ELENPhD EENo ratings yet

- GE8151 Python Programming - Unit I Question Bank With Sample CodeDocument25 pagesGE8151 Python Programming - Unit I Question Bank With Sample CodeN.Vivekananthamoorthy100% (1)

- Ses RowDocument4 pagesSes RowGilberto MejíaNo ratings yet

- EE-211 Circuit Analysis: Dr. Hadeed Ahmed SherDocument28 pagesEE-211 Circuit Analysis: Dr. Hadeed Ahmed SherHadeedAhmedSherNo ratings yet

- Engineers: Promoting the Public GoodDocument19 pagesEngineers: Promoting the Public Goodkristian prestin100% (1)

- Unit 1Document108 pagesUnit 1RAHUL R : ECE DEPTNo ratings yet

- Ec8452 Ec-Ii Unit-3Document69 pagesEc8452 Ec-Ii Unit-3Ananda Sailesh K100% (1)

- 0 4th Sem LIC Full Notes (6 Chapters) by Arunkumar G, Lecturer Dept. of E&C, STJIT RanebennurDocument520 pages0 4th Sem LIC Full Notes (6 Chapters) by Arunkumar G, Lecturer Dept. of E&C, STJIT RanebennurAmarjeet Kumar100% (5)

- POWER AMPLIFIERS: KEY TYPES AND APPLICATIONSDocument51 pagesPOWER AMPLIFIERS: KEY TYPES AND APPLICATIONSRiyaz Khan PathanNo ratings yet

- CVNG 3009 (Highway) 2009Document4 pagesCVNG 3009 (Highway) 2009Marly MarlNo ratings yet

- 077-04-26 Final Ashok SirDocument110 pages077-04-26 Final Ashok SirFg100% (1)

- MOSFET-Internal Capacitances PDFDocument11 pagesMOSFET-Internal Capacitances PDFJayanth Sriranga100% (1)

- CH6403Document7 pagesCH6403NikylNo ratings yet

- 1.2 - Highway ClassificationDocument65 pages1.2 - Highway ClassificationAbdullahi Abdi HashiNo ratings yet

- Chapter 04 PDFDocument30 pagesChapter 04 PDFRAHIM KNo ratings yet

- Dual Axis Solar Tracker With CleanerDocument6 pagesDual Axis Solar Tracker With CleanerIJRASETPublicationsNo ratings yet

- Rotary IntersectionDocument24 pagesRotary IntersectionPark Leo0% (1)

- 19-20 Lec 01 Traffic Engineering - Highway Classification and Vehicle CharacteristicsDocument34 pages19-20 Lec 01 Traffic Engineering - Highway Classification and Vehicle CharacteristicsDr Firas AsadNo ratings yet

- Reading Assignment: P. 45-72 (4 Ed.) p.45-75 (Previous Ed.) in Mannering TextbookDocument26 pagesReading Assignment: P. 45-72 (4 Ed.) p.45-75 (Previous Ed.) in Mannering TextbookMohamed Imbarek EsekbiNo ratings yet

- HGD QP SolutionDocument68 pagesHGD QP Solutionmomin sialNo ratings yet

- GTU Highway Engineering Subject GuideDocument3 pagesGTU Highway Engineering Subject GuideChitvan Bansal100% (1)

- DC Material PDFDocument149 pagesDC Material PDFCHARANNo ratings yet

- Lecture 3 Introduction To Traffic Control Devices IDocument59 pagesLecture 3 Introduction To Traffic Control Devices IAran AliNo ratings yet

- Ec8452 Ec-Ii Unit-1Document122 pagesEc8452 Ec-Ii Unit-1Ananda Sailesh KNo ratings yet

- Report On RoadsDocument12 pagesReport On RoadsHidayat UllahNo ratings yet

- Highway Engineering Section 1Document9 pagesHighway Engineering Section 1Eric NagumNo ratings yet

- Transportation - II: by Engr. Muhammad Waseem Lecturer Department of Civil Engineering UET, JalozaiDocument38 pagesTransportation - II: by Engr. Muhammad Waseem Lecturer Department of Civil Engineering UET, JalozaiShahid AliNo ratings yet

- CS8251-Programming in CDocument14 pagesCS8251-Programming in COmprakash DNo ratings yet

- ME Objective Paper 2 1017Document51 pagesME Objective Paper 2 1017Arunachalam NarayananNo ratings yet

- Operational Amplifier (Op-Amp)Document26 pagesOperational Amplifier (Op-Amp)Md ArifNo ratings yet

- Chemical Properties of Engineering MaterialsDocument29 pagesChemical Properties of Engineering MaterialsRomuel Villanueva AlmeydaNo ratings yet

- Ec8452 Ec-Ii Unit-2Document103 pagesEc8452 Ec-Ii Unit-2Ananda Sailesh KNo ratings yet

- GE8151 NotesDocument118 pagesGE8151 NotesriyaNo ratings yet

- 2015 Summer Model Answer PaperDocument21 pages2015 Summer Model Answer Paperabdul rehman syed parvez100% (1)

- Ce2255 Highway Engineering r8Document2 pagesCe2255 Highway Engineering r8Dhivya RaviNo ratings yet

- Seminar Report On Automated Highway System: Mudit Srivastava 11610040 6 Semester, C-3Document28 pagesSeminar Report On Automated Highway System: Mudit Srivastava 11610040 6 Semester, C-3Mudit SrivastavaNo ratings yet

- Traffic Analysis of Uncontrolled IntersectionDocument20 pagesTraffic Analysis of Uncontrolled IntersectionAyan ChatterjeeNo ratings yet

- CH 03 Characteristics of Road Users PDFDocument130 pagesCH 03 Characteristics of Road Users PDFChristian John SaludarNo ratings yet

- Industrial Training Report: Office Executive Engineer Provincial Division PWD (Aligarh)Document44 pagesIndustrial Training Report: Office Executive Engineer Provincial Division PWD (Aligarh)Anonymous wgEDZOBB7No ratings yet

- Traffic Congestion, Mitigation and Air QualityDocument19 pagesTraffic Congestion, Mitigation and Air QualitySivaiah GuttiNo ratings yet

- The Making of An Expert Engineer (Marked)Document591 pagesThe Making of An Expert Engineer (Marked)Fransisco Padilla AlmadaNo ratings yet

- VLSI Objective Questions and Answers 1Document7 pagesVLSI Objective Questions and Answers 1avinashrai92% (12)

- ESE Questions Bank CE SoilDocument11 pagesESE Questions Bank CE Soilzaidaan khanNo ratings yet

- JNTU MTech Transportation Engineering Course StructureDocument20 pagesJNTU MTech Transportation Engineering Course StructureSurender Reddy100% (1)

- 2 (1) - 1Document66 pages2 (1) - 1ahmed hotyNo ratings yet

- Transport Planning ProcessDocument46 pagesTransport Planning ProcessGoutham DevNo ratings yet

- Tutorial HighwayDocument17 pagesTutorial HighwayUjjval SolankiNo ratings yet

- Gian PPT 29oct15Document14 pagesGian PPT 29oct15Vikrant HaribhaktaNo ratings yet

- IRC Highway Research Journal January-June 2018 PDFDocument60 pagesIRC Highway Research Journal January-June 2018 PDFVinay YadavNo ratings yet

- Investigation of Connectivity Index for Wireless Network Partition DetectionDocument65 pagesInvestigation of Connectivity Index for Wireless Network Partition DetectionSatyanarayan Reddy KNo ratings yet

- Ec8501 Digital CommunicationDocument50 pagesEc8501 Digital CommunicationAnkur rathaurNo ratings yet

- Railroad Signal Specialist: Passbooks Study GuideFrom EverandRailroad Signal Specialist: Passbooks Study GuideNo ratings yet

- Vlsi DesignDocument67 pagesVlsi DesignramakrishnaNo ratings yet

- OBJECTIVE QUESTIONS ON VLSI TECHNOLOGYDocument18 pagesOBJECTIVE QUESTIONS ON VLSI TECHNOLOGYdycsteiznNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo ratings yet

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionFrom EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionNo ratings yet

- AjayDocument1 pageAjayvikramvsuNo ratings yet

- Vijaya Lakshmi Arikatla Resume @Document2 pagesVijaya Lakshmi Arikatla Resume @vikramvsuNo ratings yet

- Adil ResumeDocument2 pagesAdil ResumevikramvsuNo ratings yet

- I Types of AccountsDocument12 pagesI Types of AccountsvikramvsuNo ratings yet

- Accounting For Management: Instruction To CandidatesDocument2 pagesAccounting For Management: Instruction To CandidatesvikramvsuNo ratings yet

- A JyothiDocument35 pagesA JyothivikramvsuNo ratings yet

- Competitive Positioning of BrandsDocument2 pagesCompetitive Positioning of BrandsvikramvsuNo ratings yet

- Brand Equity Models ExplainedDocument7 pagesBrand Equity Models ExplainedvikramvsuNo ratings yet

- Brand Value ChainDocument1 pageBrand Value ChainvikramvsuNo ratings yet

- Brand Reinforcement and RevitalizationDocument2 pagesBrand Reinforcement and Revitalizationvikramvsu100% (1)

- Different Branding Strategies: Company Name, Individual, Attitude, Extension & Private LabelDocument2 pagesDifferent Branding Strategies: Company Name, Individual, Attitude, Extension & Private Labelvikramvsu100% (1)

- Accounting For ManagersDocument286 pagesAccounting For ManagersSatyam Rastogi100% (1)

- Ug C Revised Pay Scales GoDocument65 pagesUg C Revised Pay Scales GoVenugopal Reddyvari100% (1)

- Advt Appointment For Faculty PositionsDocument1 pageAdvt Appointment For Faculty PositionsvikramvsuNo ratings yet

- Accounting For Management: Total No. of Questions 17Document2 pagesAccounting For Management: Total No. of Questions 17vikramvsuNo ratings yet

- Svucsf McaDocument3 pagesSvucsf McavikramvsuNo ratings yet

- Pondicherry University Adhoc Recruitment NotificationDocument3 pagesPondicherry University Adhoc Recruitment NotificationvikramvsuNo ratings yet

- Research Methodology Paper-IDocument2 pagesResearch Methodology Paper-IvikramvsuNo ratings yet

- Vspu MBTDocument1 pageVspu MBTvikramvsuNo ratings yet

- Narendra MurkumbiDocument2 pagesNarendra MurkumbivikramvsuNo ratings yet

- Academic Consultants2016 17Document5 pagesAcademic Consultants2016 17vikramvsuNo ratings yet

- Advt Appointment For Faculty PositionsDocument1 pageAdvt Appointment For Faculty PositionsvikramvsuNo ratings yet

- I Semester ECDocument1 pageI Semester ECvikramvsuNo ratings yet

- AP Polycet 2015 Information BrochureDocument65 pagesAP Polycet 2015 Information BrochureNeepur GargNo ratings yet

- Vspu MbaDocument2 pagesVspu MbavikramvsuNo ratings yet

- Online Counseling Provisional Allotment ListDocument2 pagesOnline Counseling Provisional Allotment ListvikramvsuNo ratings yet

- Online Counseling Provisional Seat AllotmentDocument1 pageOnline Counseling Provisional Seat AllotmentvikramvsuNo ratings yet

- Online Web Counseling DetailsDocument3 pagesOnline Web Counseling Detailsvikramvsu100% (1)

- Svuc - S V U College of MNGT and Info Sci, Tirupathi Master of Computer Applications Show AllotmentsDocument1 pageSvuc - S V U College of MNGT and Info Sci, Tirupathi Master of Computer Applications Show AllotmentsvikramvsuNo ratings yet

- APICET Detailed NotificationDocument2 pagesAPICET Detailed NotificationvikramvsuNo ratings yet

- Danfoss VLT Gvac FC 102 PDFDocument86 pagesDanfoss VLT Gvac FC 102 PDFAbdou DENo ratings yet

- Main Substation Feeder and Ring Main Unit Protection Settings (LPN) PDFDocument14 pagesMain Substation Feeder and Ring Main Unit Protection Settings (LPN) PDFprseNo ratings yet

- 132/22kV Power TransformersDocument3 pages132/22kV Power TransformersDeepak DhakalNo ratings yet

- Wimshurst Machine: Description Operation See Also References External LinksDocument4 pagesWimshurst Machine: Description Operation See Also References External LinksAdenNo ratings yet

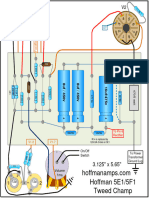

- Hoffman 5F1Document4 pagesHoffman 5F1samuel tassiniNo ratings yet

- Irlr 7843Document12 pagesIrlr 7843Idris LMNo ratings yet

- 11kv HT Cable Hi Pot MrsDocument9 pages11kv HT Cable Hi Pot Mrsjskrish56550% (2)

- Recloser Joongwon.2015Document4 pagesRecloser Joongwon.2015Adian Zahy Ardana100% (1)

- PG 83 - Fig 3 (Circuit-Dec 14) Automatic EveningDocument1 pagePG 83 - Fig 3 (Circuit-Dec 14) Automatic EveningsaurabhNo ratings yet

- Cutler-Hammer VacClad-W Arc Resistant Switchgear: Innovative Technology for SafetyDocument12 pagesCutler-Hammer VacClad-W Arc Resistant Switchgear: Innovative Technology for SafetyandrewNo ratings yet

- Mte Dialog: Instruction ManualDocument36 pagesMte Dialog: Instruction Manualalexandru lapusneanuNo ratings yet

- Mov-10Dxxxk Series - Metal Oxide Varistor: Features ApplicationsDocument4 pagesMov-10Dxxxk Series - Metal Oxide Varistor: Features ApplicationsNguyên NghĩaNo ratings yet

- Active 3000 ChlorideDocument60 pagesActive 3000 ChlorideTanveer AhmedNo ratings yet

- C5587 ToshibaSemiconductorDocument5 pagesC5587 ToshibaSemiconductormaka153No ratings yet

- Allen Bradley 100 C43ZJ10Document1 pageAllen Bradley 100 C43ZJ10Diana Cristina PereaNo ratings yet

- Installation Manual: International Power Machines'Document46 pagesInstallation Manual: International Power Machines'haNo ratings yet

- Transformer Voltage Withstand and Insulation TestsDocument7 pagesTransformer Voltage Withstand and Insulation Testskanchan206100% (1)

- Data SheetDocument6 pagesData SheetAshfaaq OchatoyaNo ratings yet

- L&T Fault Calculation-Sauni L2P6 PDFDocument4 pagesL&T Fault Calculation-Sauni L2P6 PDFElectrical RadicalNo ratings yet

- V 0226012420 0007 PDFDocument6 pagesV 0226012420 0007 PDFKhairulNo ratings yet

- Company Name Huawei Subject DurationDocument3 pagesCompany Name Huawei Subject DurationLikhith GowdruNo ratings yet

- Isc 2SC1970: Silicon NPN Power TransistorDocument2 pagesIsc 2SC1970: Silicon NPN Power TransistorJames RMNo ratings yet

- URE 440W FAM E8G-BB144CellDocument2 pagesURE 440W FAM E8G-BB144CellamitNo ratings yet

- Help For The High Frequency Transformer DesignDocument4 pagesHelp For The High Frequency Transformer DesignbudituxNo ratings yet

- Rme September 2019Document11 pagesRme September 2019Ryan Kim Patron0% (1)

- ATS Drawing (R0) 30-Oct-12Document16 pagesATS Drawing (R0) 30-Oct-12Shrikant KajaleNo ratings yet

- Wattstopper Sensor The Most Advanced Energy Saving TechnologyDocument7 pagesWattstopper Sensor The Most Advanced Energy Saving TechnologyDemo Only100% (1)

- 11KV Capacitor Bank - SPECDocument7 pages11KV Capacitor Bank - SPECNasaii RayNo ratings yet

- Agc 242 InstallationDocument57 pagesAgc 242 InstallationSandro Muniz100% (1)

- Service Manual: 26SL71 29SL81Document60 pagesService Manual: 26SL71 29SL81Anonymous uWAzUj42LNo ratings yet