Professional Documents

Culture Documents

SAP-1 Simple As Possible Computer With Discrete Component RAM

Uploaded by

pong74lsOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

SAP-1 Simple As Possible Computer With Discrete Component RAM

Uploaded by

pong74lsCopyright:

Available Formats

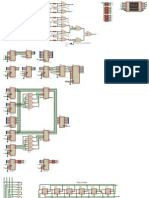

Data

Input

Program

Counter

Data

Output

W-Bus

T1

T2

T3

T4

T5

T6

Address

Input

VCC

U24:A

1

VCC

CLR

?

?

?

?

?

?

2

Cp

Ep

Lm

CE

Li

Ei

La

Ea

Su

Eu

Lb

Lo

SW5

ADR3

ADR2

ADR1

ADR0

Start

Clear/Start

4

6

?

?

?

?

?

?

?

?

?

?

?

?

D7

D6

D5

D4

D3

D2

D1

D0

U24:B

Clear

CLR

VCC

OP0

OP1

OP2

OP3

OP4

OP5

OP6

OP7

W0

W1

W2

W3

W4

W5

W6

W7

PC0

PC1

PC2

PC3

D0

D1

D2

D3

D4

D5

D6

D7

ADR0

ADR1

ADR2

U24:C

9

VCC

8

10

D7

D6

D5

D4

D3

D2

D1

D0

ADR3

ADR2

ADR1

ADR0

ADR3

7400

SW6

5

6

7

8

9

10

11

12

13

14

15

16

VCC

SW1

Low

Single Step

VCC

SW3

OPCode / Data

Switches

12

11

SW4

WEram

ENmar

Write

Memory

13

VCC

Program/Run

SW2: Open=Run Closed=Program

1

2

13

12

U26:A

1

VCC

U26:D

3

2

To program:

1) Switch SW2 marked Run/Program should be DOWN in the program position.

2) Switch SW7 marked Manual/Auto should be UP in the manual position.

3) Use the 4 address and 8 data input switches to enter each line of the program.

Observe the Address and Data Input 7-segment displays to see what is being entered.

4) Press the Write Memory button once to write data to RAM.

SW7

U27:A

U27:B

13

11

Manual

U27:C

U26:B

Auto

U25:B

4

6

10

14

18

20

CLK

Note: The 555 timer circuit has been substituted with

a virtual clock source to speed up the simulation.

U25:B(C)

INIT=LOW

START=0

COUNT=-1

CLOCK=2

PC3

PC2

PC1

PC0

3

4

5

HLT

VCC

Here is a sample test program:

Address Data

0

09

1

1A

2

1b

3

2C

4

E0

5

F0

CLK

12

Manual/Auto

Once data is written, the run the program:

1) Switch the SW2 Run/Program switch UP to the run position.

2) Switch the SW7 Manual/Auto switch DOWN to start the clock.

W7 W6 W5 W4 W3 W2 W1 W0

Cp

74LS107

12

Q

74LS107

CLK

6

12

CLK

2

11

CLK

6

13

CLK

2

13

The program is 10h + 14h + 18h - 20h = 1Ch so the output display should show 1C

and the HLT signal should be active when the program is finished running.

Hopefully it works for you too.

74LS107

J

10

U2:B

CLK

11

10

74LS107

3

U2:A

U1:B

U1:A

9

A

b

C

U25:A

HLT

7400

8

7

6

5

4

3

2

1

OFF

4

3

2

1

ON

ON

OFF

Address

Switches

U24:D

High

SW2

U3:D

U10

CLK

OE1

OE2

E1

E2

MR

D0

D1

D2

D3

CLK

OE1

OE2

E1

E2

MR

D0

D1

D2

D3

U11

74LS173

Accumulator

3

4

5

6

3

4

5

6

Q0

Q1

Q2

Q3

74LS173

Accumulator

Q0

Q1

Q2

Q3

Ep

14

13

12

11

7

1

2

9

10

15

14

13

12

11

11

74LS126

CLK

La

7

1

2

9

10

15

CLK

La

13

10

U3:C

12

U3:B

CLR

U3:A

CLK

Ea

11

12

13

14

D3

D2

D1

D0

U4

Q3

Q2

Q1

Q0

74LS173

Memory Address Register

15

10

9

2

1

7

MR

E2

E1

OE2

OE1

CLK

Ea

Lm

10

10

6

5

4

3

ADR0

ADR1

ADR2

ADR3

13

13

ENmar

11

12

12

13

14

10

11

6

5

3

2

15

1

11

4B

4A

3B

3A

2B

2A

1B

1A

E

A/B

2Y

1Y

4

3Y

9

4Y

74LS126

Accumulator

Output

74LS126

Accumulator

Output

74LS157

2-1 Multiplexer

12

U12:D

U13:D

U5

U49

VCC

6

4

5

E1

E2

E3

13

12

10

Su

13

12

10

Su

5

I0

I1

I2

I3

I4

I5

I6

I7

15

14

13

12

11

10

9

7

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

A

B

C

1

2

3

U15:D

U14:D

74LS86

74LS86

A

B

C

6

4

5

E1

E2

E3

11

11

6

2

15

11

C0

A0

A1

A2

A3

B0

B1

B2

B3

5

3

14

12

C4

9

S0

S1

S2

S3

4

1

13

10

12

13

11

11

74LS126

10

8

4

6

1

3

13

12

10

8

U18:D

74LS126

Eu

15

14

13

12

11

10

9

7

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

C0

4

U52

CE

5

1

74LS138

1

2

3

74LS283

Full Adder

(MSB)

U19:D

E1

E2

E3

U16

Carry

O0

O1

O2

O3

O4

O5

O6

O7

6

4

5

VCC

15

14

13

12

11

10

9

7

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

U17

C4

S0

S1

S2

S3

4

1

13

10

U51

A

B

C

Carry

74LS283

Full Adder

(LSB)

74HCT238

16-byte RAM

Latch Enable Decoder

1

2

3

6

2

15

11

5

3

14

12

Su

E1

E2

E3

I8

I9

I10

I11

I12

I13

I14

I15

B0

B1

B2

B3

15

14

13

12

11

10

9

7

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

A0

A1

A2

A3

A

B

C

6

4

5

WEram

U50

1

2

3

74HCT238

O8

O9

O10

O11

O12

O13

O14

O15

74LS138

16-byte RAM

Output Enable Decoder

CLK

Lb

CLK

Lb

O11

I11

1

11

3

4

7

8

13

14

17

18

O12

I12

1

11

3

4

7

8

13

14

17

18

O13

I13

1

11

3

4

7

8

13

14

17

18

O14

I14

1

11

3

4

7

8

13

14

17

18

O15

I15

1

11

7

1

2

9

10

15

CLK

OE1

OE2

E1

E2

MR

D0

D1

D2

D3

Q0

Q1

Q2

Q3

OP4

OP5

OP6

OP7

OP0

OP1

OP2

OP3

Q

CLK

6

U38:B

74LS107

1

9

Q

CLK

6

12

CLK

2

11

11

12

CLK

11

CLK

6

10

13

10

13

5

10

U31:C

CLR

U31:D

12

13

T6

OE

LE

T4

2

5

6

9

12

15

16

19

T3

T2

T1

U35:E

1

2

U32:A

1

4

5

LDA

ADD

SUB

U35:B

U33:A

OE

LE

D0

D1

D2

D3

D4

D5

D6

D7

2

5

6

9

12

15

16

19

OE

LE

D0

D1

D2

D3

D4

D5

D6

D7

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

2

5

6

9

12

15

16

19

OE

LE

D0

D1

D2

D3

D4

D5

D6

D7

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

2

5

6

9

12

15

16

19

OE

LE

D0

D1

D2

D3

D4

D5

D6

D7

OE

LE

74LS373

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

2

5

6

9

12

15

16

19

10

13

12

10

13

12

10

13

12

11

11

11

U45:B

3

4

5

1

2

13

U45:A

U46:A

U46:B

U47:B

U47:C

U47:F

Li

Ei

La

Ea

U48:A

2

12

CE

U48:B

U47:D

Lm

3

1

U47:E

Su

U47:A

13

12

HLT

U34:A

Cp Ep

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

U44:B

11

2

5

6

9

12

15

16

19

U44:A

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

U43:C

U35:F

10

D0

D1

D2

D3

D4

D5

D6

D7

U33:B

12

13

4

5

U42:D

6

3

4

5

1

2

U41:D

U35:C

6

OE

LE

U40:D

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

10

U39:D

1

2

OE

LE

D0

D1

D2

D3

D4

D5

D6

D7

9

10

4

5

2

5

6

9

12

15

16

19

12

13

2

5

6

9

12

15

16

19

OUT

U32:B

8

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Control Matrix

U35:A

6

9

10

OE

LE

D0

D1

D2

D3

D4

D5

D6

D7

Instruction Decoder

12

13

2

5

6

9

12

15

16

19

9

10

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

12

D0

D1

D2

D3

D4

D5

D6

D7

U35:D

12

OE

LE

13

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

13

D0

D1

D2

D3

D4

D5

D6

D7

T5

3

4

7

8

13

14

17

18

2

5

6

9

12

15

16

19

12

CLK

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

1

11

O10

I10

3

4

7

8

13

14

17

18

74LS107

1

11

U38:A

74LS107

11

O9

I9

D0

D1

D2

D3

D4

D5

D6

D7

U37:B

74LS107

10

3

4

7

8

13

14

17

18

U37:A

74LS107

1

11

U36:B

74LS107

O8

I8

4

OE

LE

U36:A

3

4

7

8

13

14

17

18

U31:B

1

11

CLK

O7

I7

4

5

3

4

7

8

13

14

17

18

Ring Counter

U31:A

2

1

11

2

5

6

9

12

15

16

19

O6

I6

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

3

4

7

8

13

14

17

18

D0

D1

D2

D3

D4

D5

D6

D7

1

11

74LS173

Output Register

OE

LE

1

2

O5

I5

2

5

6

9

12

15

16

19

3

4

7

8

13

14

17

18

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

1

11

D0

D1

D2

D3

D4

D5

D6

D7

O4

I4

U22

3

4

5

6

Q0

Q1

Q2

Q3

74LS173

Output Register

OE

LE

13

3

4

7

8

13

14

17

18

CLK

OE1

OE2

E1

E2

MR

D0

D1

D2

D3

Q0

Q1

Q2

Q3

3

4

5

6

14

13

12

11

7

1

2

9

10

15

U23

CLK

OE1

OE2

E1

E2

MR

74LS173

Instruction

Register

(Address)

11

1

11

7

1

2

9

10

15

14

13

12

11

7

1

2

9

10

15

CLK

OE1

OE2

E1

E2

MR

D0

D1

D2

D3

Q0

Q1

Q2

Q3

3

4

5

6

11

12

13

14

U9

14

13

12

11

2

5

6

9

12

15

16

19

74LS173

Instruction

Register

(OPCode)

CLK

Lo

CLR

3

4

5

6

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

U8

CLK

Lo

CLR

10

O3

I3

74LS173

B Register

(MSB)

CLK

Ei

Li

D0

D1

D2

D3

OE

LE

D0

D1

D2

D3

D4

D5

D6

D7

CLK

Li

CLR

D3

D2

D1

D0

2

5

6

9

12

15

16

19

15

10

9

2

1

7

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

Q3

Q2

Q1

Q0

3

4

7

8

13

14

17

18

D0

D1

D2

D3

D4

D5

D6

D7

6

5

4

3

1

11

U20

OE

LE

MR

E2

E1

OE2

OE1

CLK

O2

I2

74LS173

B Register

(LSB)

2

5

6

9

12

15

16

19

11

12

13

14

3

4

7

8

13

14

17

18

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

D3

D2

D1

D0

1

11

D0

D1

D2

D3

D4

D5

D6

D7

Q3

Q2

Q1

Q0

O1

I1

U21

OE

LE

6

5

4

3

3

4

7

8

13

14

17

18

2

5

6

9

12

15

16

19

15

10

9

2

1

7

1

11

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

MR

E2

E1

OE2

OE1

CLK

O0

I0

D0

D1

D2

D3

D4

D5

D6

D7

14

13

12

11

U53

3

4

7

8

13

14

17

18

D0

D1

D2

D3

D4

D5

D6

D7

Eu

Lb

Lo

You might also like

- SAP-1 Simple As Possible Computer Schematic Diagram - Updated DesignDocument1 pageSAP-1 Simple As Possible Computer Schematic Diagram - Updated Designpong74lsNo ratings yet

- ASAP-2 Almost Simple As Possible Computer SchematicDocument1 pageASAP-2 Almost Simple As Possible Computer Schematicpong74lsNo ratings yet

- Design and Implementation of Simple As Possible Computer (SAP-1)Document51 pagesDesign and Implementation of Simple As Possible Computer (SAP-1)Miguel San AntonioNo ratings yet

- Datapaths: Understanding CPU ComponentsDocument30 pagesDatapaths: Understanding CPU ComponentsIqxca AzmYani100% (1)

- Digital Logic Design Lab Manual: Department of Electrical Engineering, Fast-Nu, LahoreDocument115 pagesDigital Logic Design Lab Manual: Department of Electrical Engineering, Fast-Nu, LahoreQasim LodhiNo ratings yet

- SAP 1 Simple As Possible ComputerDocument51 pagesSAP 1 Simple As Possible ComputerShawon Nazrul Islam80% (5)

- Binary MultiplierDocument14 pagesBinary MultiplierTaruna AggarwalNo ratings yet

- Sap 1 2Document21 pagesSap 1 2Brandon Maciel50% (2)

- The Single Cycle CPU ProjectDocument16 pagesThe Single Cycle CPU ProjectErik MachorroNo ratings yet

- Sap 2Document35 pagesSap 2Michael Vincent B. Nierva88% (8)

- Types of Micro OperationsDocument17 pagesTypes of Micro OperationsP Suresh Babu91% (11)

- MicrosequencerDocument38 pagesMicrosequencerJonathan MejiaNo ratings yet

- Computer OrganizationDocument396 pagesComputer Organizationkanaka raghu sreeramaNo ratings yet

- Floating Point ALU Using VHDL BlueDocument25 pagesFloating Point ALU Using VHDL BluepaulcbijuNo ratings yet

- Lab 5 Binary ArithmeticDocument5 pagesLab 5 Binary ArithmeticRifah Shanjida Momo100% (1)

- MicroprocessorDocument2 pagesMicroprocessorKiran TimsinaNo ratings yet

- VHDL ProgramsDocument10 pagesVHDL ProgramsgyanranjandashNo ratings yet

- Instructional Tools For Designing and Analysing A Very Simple CPUDocument10 pagesInstructional Tools For Designing and Analysing A Very Simple CPUFrancisco Javier Cesni MaldonadoNo ratings yet

- Control Unit:: Hardwired vs. Microprogrammed ApproachDocument49 pagesControl Unit:: Hardwired vs. Microprogrammed ApproachskskaundilyaNo ratings yet

- 4 Bit BCD AdderDocument5 pages4 Bit BCD Adderjitendra jhaNo ratings yet

- Unit 5a - CPU DesignDocument64 pagesUnit 5a - CPU DesignMʌŋı ßʌķŞhı100% (1)

- Solution Manual For Assembly Language Programming and Organization of IBM PC PDFDocument129 pagesSolution Manual For Assembly Language Programming and Organization of IBM PC PDFabdul haseebNo ratings yet

- 16 Micro-Programmed ControlDocument36 pages16 Micro-Programmed ControlJohn Paul Cordova100% (1)

- IC Lab Manual by Suresh BabuDocument83 pagesIC Lab Manual by Suresh Babunandakishore.nalla92% (13)

- LD ManualDocument89 pagesLD ManualchaitanyaNo ratings yet

- Programmable Logic Devices 2, TutorialDocument10 pagesProgrammable Logic Devices 2, Tutorialindresh.verma100% (1)

- Cisco Storage Design Fundamentals: Lab GuideDocument96 pagesCisco Storage Design Fundamentals: Lab Guidecdrbc100% (1)

- PLMU Computer Studies Dept SAP-1 modificationDocument17 pagesPLMU Computer Studies Dept SAP-1 modificationJaysen GeronimoNo ratings yet

- Sap-1 Computer Part1Document56 pagesSap-1 Computer Part1Tawki BakiNo ratings yet

- 6802 User ManualDocument76 pages6802 User Manualmaldelrey100% (1)

- Sap 1 Manual NewDocument41 pagesSap 1 Manual NewAlexis John Rubio0% (1)

- SAP (Simple-As-Possible) Computers: 10-1 ArchitectureDocument24 pagesSAP (Simple-As-Possible) Computers: 10-1 ArchitectureAfrahly Afable100% (1)

- CISE 204 Digital System Design Lab Manual PDFDocument44 pagesCISE 204 Digital System Design Lab Manual PDFEng-Mohammed KayedNo ratings yet

- Lab ManualDocument19 pagesLab ManualSanthi SriNo ratings yet

- Digital Electronics Lab EE-224-FDocument48 pagesDigital Electronics Lab EE-224-FIshwar Singh ChandraNo ratings yet

- EXP 6 Serial AdderDocument2 pagesEXP 6 Serial Adderubuntu 13.0450% (2)

- Computer ArithmeticDocument26 pagesComputer Arithmeticspweda100% (1)

- Sap 1Document54 pagesSap 1ICANSAP0% (3)

- Junior Training SheetDocument70 pagesJunior Training SheetJuan Sebastian Hoyos100% (1)

- Mirror AdderDocument51 pagesMirror AdderjeevanprsdNo ratings yet

- The D Flip FlopDocument7 pagesThe D Flip FlopAlinChanNo ratings yet

- Pedroni MITPress 2ndedition Solution Samples v3Document25 pagesPedroni MITPress 2ndedition Solution Samples v3Squall_DA0% (1)

- 8051 ProgramsDocument2 pages8051 ProgramsvipulkondekarNo ratings yet

- Serial AdderDocument6 pagesSerial AdderPrathap Vuyyuru100% (1)

- Introduction To Cmos Vlsi Design: MIPS Processor ExampleDocument43 pagesIntroduction To Cmos Vlsi Design: MIPS Processor ExampleSurbhi PrasadNo ratings yet

- Digital Lab Manual V2.1Document120 pagesDigital Lab Manual V2.1Marwan AffandiNo ratings yet

- A Unified Algorithm For Elementary FunctionsDocument8 pagesA Unified Algorithm For Elementary FunctionsCristo_Alanis_8381No ratings yet

- Chapter 11 Laboratory ExperimentDocument102 pagesChapter 11 Laboratory ExperimentMrinal TakNo ratings yet

- Curso Pic24j60Document173 pagesCurso Pic24j60Diojan Torres100% (1)

- Miroprogram Control UnitDocument21 pagesMiroprogram Control UnitSameer SalamNo ratings yet

- Study Gates, Flip-Flops LabDocument51 pagesStudy Gates, Flip-Flops Labsudipta2580No ratings yet

- Micro ControllersDocument141 pagesMicro ControllersBiswajit SarkarNo ratings yet

- Vedic MultiplierDocument14 pagesVedic MultiplierSunay RajNo ratings yet

- Ti I2cDocument13 pagesTi I2crajkumar_jain4855100% (1)

- SAP-1 Simple As Possible Computer With Microcoded ROMDocument1 pageSAP-1 Simple As Possible Computer With Microcoded ROMpong74lsNo ratings yet

- SAP-1 Simple As Possible Computer Schematic DiagramDocument1 pageSAP-1 Simple As Possible Computer Schematic Diagrampong74ls100% (5)

- Camera module with OV7670 and AL422B FIFODocument1 pageCamera module with OV7670 and AL422B FIFOMuhammad Alfiansyah100% (3)

- Interrupt Control: Serial I/O ControlDocument15 pagesInterrupt Control: Serial I/O ControlnagpalanishNo ratings yet

- SAP-1 Simple As Possible Microprocessor - Original DesignDocument1 pageSAP-1 Simple As Possible Microprocessor - Original DesignFarhan S. Adul100% (1)

- Discharge LampsDocument35 pagesDischarge LampsAnjali ShahNo ratings yet

- Vacuum Cleaner 2023Document2 pagesVacuum Cleaner 2023Faisal RamdaniNo ratings yet

- Instrumentation SubmittalDocument290 pagesInstrumentation SubmittalMohamed EisaNo ratings yet

- The Bright Future of LED Technology: Saving Energy "Green" LightDocument51 pagesThe Bright Future of LED Technology: Saving Energy "Green" LightPredrag RoganovicNo ratings yet

- Ed sq2 3ph 200 60 s2 15 enDocument2 pagesEd sq2 3ph 200 60 s2 15 ensáng nguyễnNo ratings yet

- Compact Technical ManualDocument18 pagesCompact Technical ManualSergei KurpishNo ratings yet

- 491-Md-310 Inspection Report: 1. Head SprocketDocument4 pages491-Md-310 Inspection Report: 1. Head SprocketsantoshNo ratings yet

- Service Manual: Home Sewing MachineDocument186 pagesService Manual: Home Sewing Machineboroda2410100% (2)

- C0319 Frame 3 Rolling Element Bearing Replacement-MARUMADocument8 pagesC0319 Frame 3 Rolling Element Bearing Replacement-MARUMAANGEL MURILLONo ratings yet

- Ahe00043en - FBLG (Radiadores Finned Coil FBLG)Document2 pagesAhe00043en - FBLG (Radiadores Finned Coil FBLG)Marco FreireNo ratings yet

- Doosan Dbc130 Mechanical Repair Manual CompressDocument157 pagesDoosan Dbc130 Mechanical Repair Manual CompressDiwa ThiveNo ratings yet

- Michelson Interferometer Viva QuestionsDocument2 pagesMichelson Interferometer Viva QuestionsDhruv NagarNo ratings yet

- Fdocuments - in - Deutz Fahr Agroplus 80 Tractor Service Repair Manual 1587139753Document22 pagesFdocuments - in - Deutz Fahr Agroplus 80 Tractor Service Repair Manual 1587139753Mateusz WolakNo ratings yet

- Surge Protector Secrets You Aren't Supposed To KnowDocument12 pagesSurge Protector Secrets You Aren't Supposed To KnowPaul QuillenNo ratings yet

- SY95CDocument304 pagesSY95CPhil LastNo ratings yet

- Camden CM-7536-1-BRZ Data SheetDocument2 pagesCamden CM-7536-1-BRZ Data SheetJMAC SupplyNo ratings yet

- Gurps Fallout RiflesDocument1 pageGurps Fallout RiflesAndrew Scott100% (1)

- Part 23.03 Analogue Addressable Fire Alarm SystemDocument20 pagesPart 23.03 Analogue Addressable Fire Alarm SystemRotsapNayrb100% (1)

- BS 6724 Copper Conductor Multi Core SWA LSZH BASEC 0.6/1kV CableDocument5 pagesBS 6724 Copper Conductor Multi Core SWA LSZH BASEC 0.6/1kV CableRehan AfzalNo ratings yet

- L7 - Material Removal Process (Single and Multi Point Cutting Tools)Document14 pagesL7 - Material Removal Process (Single and Multi Point Cutting Tools)Aditya AdityaNo ratings yet

- PC20R-8 PC27R-8 Hydraulic System Structure and FunctionDocument79 pagesPC20R-8 PC27R-8 Hydraulic System Structure and FunctionДаниил Поговоров100% (1)

- 4 - JS ExcavatorDocument12 pages4 - JS Excavatorhamza rezguiNo ratings yet

- Motors | Automation | Energy | Transmission & Distribution | CoatingsDocument40 pagesMotors | Automation | Energy | Transmission & Distribution | Coatingsfabrice mellantNo ratings yet

- Enerpac WMC Series CatalogDocument1 pageEnerpac WMC Series CatalogTitanplyNo ratings yet

- Fuse Catalog Nte-ElectronicsDocument32 pagesFuse Catalog Nte-ElectronicsSamir AbauNo ratings yet

- DBC1 AVR SINCRO MANUAL - Rev02Document12 pagesDBC1 AVR SINCRO MANUAL - Rev02jean sanchezNo ratings yet

- 25KV Current TransformerDocument4 pages25KV Current TransformerKamlesh MhatreNo ratings yet

- Doosan TT Series CNCDocument7 pagesDoosan TT Series CNCRevolusiSoekarnoNo ratings yet

- Mosaic Modular Switch System GuideDocument83 pagesMosaic Modular Switch System Guidesurajmishra1985No ratings yet

- Panel Resun PF200PDocument2 pagesPanel Resun PF200PCamilo SepulvedaNo ratings yet