Professional Documents

Culture Documents

Critical Conduction Mode PFC Controller: Features Description

Uploaded by

Manuel NolascoOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Critical Conduction Mode PFC Controller: Features Description

Uploaded by

Manuel NolascoCopyright:

Available Formats

FAN7530 Critical Conduction Mode PFC Controller

January 2007

FAN7530

Critical Conduction Mode PFC Controller

Features

Low Total Harmonic Distortion (THD) Precise Adjustable Output Over-Voltage Protection Open-Feedback Protection and Disable Function Zero Current Detector 150s Internal Start-up Timer MOSFET Over-Current Protection Under-Voltage Lockout with 3.5V Hysteresis Low Start-up (40A) and Operating Current (1.5mA) Totem Pole Output with High State Clamp +500/-800mA Peak Gate Drive Current 8-Pin DIP or 8-Pin SOP

Description

The FAN7530 is an active power factor correction (PFC) controller for boost PFC applications that operates in critical conduction mode (CRM). It uses the voltage mode PWM that compares an internal ramp signal with the error amplifier output to generate MOSFET turn-off signal. Since the voltage mode CRM PFC controller does not need rectified AC line voltage information, it saves the power loss of the input voltage sensing network necessary for the current mode CRM PFC controller. FAN7530 provides many protection functions, such as over voltage protection, open-feedback protection, overcurrent protection, and under-voltage lockout protection. The FAN7530 can be disabled if the INV pin voltage is lower than 0.45V and the operating current decreases to 65A. Using a new variable on-time control method, THD is lower than the conventional CRM boost PFC ICs.

Applications

Adapter Ballast LCD TV, CRT TV SMPS

Related Application Notes

AN-6027 - Design of Power Factor Correction Circuit

Using FAN7530

Ordering Information

Part Number

FAN7530N FAN7530M FAN7530MX

Operating Temp. Range

-40C to +125C -40C to +125C -40C to +125C

Pb-Free

Yes Yes Yes

Package

8-DIP 8-SOP 8-SOP

Packing Method

Rail Rail Tape & Reel

Marking Code

FAN7530 FAN7530 FAN7530

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1

www.fairchildsemi.com

FAN7530 Critical Conduction Mode PFC Controller

Typical Application Diagrams

L AC IN VAUX NAUX RZCD R2 ZCD CO VCC MOT I1 COMP R1 CS FAN7530 INV D VO

I2

GND

FAN7530 Rev. 00

Figure 1. Typical Boost PFC Application

Internal Block Diagram

VCC 8 UVLO 2.5V Ref Internal Bias Vref VCC

12V

8.5V

Disable

150ms Timer S

Drive Output

7 OUT 13V

ZCD 5 6.5V 1.4V 1.5V Zero Current Detector

Q R OVP 2.675V 2.5V

CS

4 40k 8pF 0.8V Ramp Signal Sawtooth Generator Current Protection Comparator

Disable

0.45V 0.35V

1V Offset

MOT 2

Error Amplifier 1V~5V Range

Gm

Vref

1 INV

6 GND

3 COMP

FAN7530 Rev. 00

Figure 2. Functional Block Diagram of FAN7530

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 2

www.fairchildsemi.com

FAN7530 Critical Conduction Mode PFC Controller

Pin Assignments

VCC 8 OUT 7 GND 6 ZCD 5

YWW

FAN7530

1 INV 2 MOT 3 COMP 4 CS

FAN7530 Rev. 00

Figure 3. Pin Configuration (Top View)

Pin Definitions

Pin #

1 2 3 4 5 6 7 8

Name

INV MOT COMP CS ZCD GND OUT Vcc

Description

This pin is the inverting input of the error amplifier. The output voltage of the boost PFC converter should resistively divided to 2.5V. This pin is used to set the slope of the internal ramp. The voltage of this pin is maintained at 2.9V. If a resistor is connected between this pin and GND, current flows out of the pin and the slope of the internal ramp is proportional to this current. This pin is the output of the transconductance error amplifier. Components for the output voltage compensation should be connected between this pin and GND. This pin is the input of the over-current protection comparator. The MOSFET current is sensed using a sensing resistor and the resulting voltage is applied to this pin. An internal RC filter is included to filter switching noise. This pin is the input of the zero current detection block. If the voltage of this pin goes higher than 1.5V, then goes lower than 1.4V, the MOSFET is turned on. This pin is used for the ground potential of all the pins. For proper operation, the signal ground and the power ground should be separated. This pin is the gate drive output. The peak sourcing and sinking current levels are +500mA and -800mA respectively. For proper operation, the stray inductance in the gate driving path must be minimized. This pin is the IC supply pin. IC current and MOSFET drive current are supplied using this pin.

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 3

www.fairchildsemi.com

FAN7530 Critical Conduction Mode PFC Controller

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only. TA = 25C unless otherwise specified.

Symbol

VCC IOH, IOL Iclamp Idet VIN TJ TA TSTG VESD_HBM VESD_MM VESD_CDM Supply Voltage

Parameter

Peak Drive Output Current Driver Output Clamping Diodes VO>VCC or VO<-0.3V Detector Clamping Diodes Error Amplifier, MOT, CS Input Voltages Operating Junction Temperature Operating Temperature Range Storage Temperature Range ESD Capability, Human Body Model ESD Capability, Machine Model ESD Capability, Charged Device Model

Value

VZ +500/-800 10 10 -0.3 to 6 150 -40 to 125 -65 to 150 2.0 300 500

Unit

V mA mA mA V C C C kV V V

Thermal Impedance(1)

Symbol

JA Note: 1. Regarding the test environment and PCB type, please refer to JESD51-2 and JESD51-10.

Parameter

Thermal Resistance, Junction-to-Ambient 8-DIP 8-SOP

Value

110 150

Unit

C/W C/W

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 4

www.fairchildsemi.com

FAN7530 Critical Conduction Mode PFC Controller

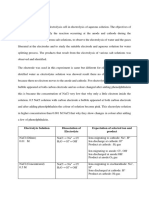

Electrical Characteristics

VCC = 14V and TA = -40C~125C unless otherwise specified.

Symbol

Vth(start) Vth(stop) HY(uvlo) VZ Ist ICC Idcc ICC(dis) Vref1 Vref1 Vref2 Ib(ea) Isource Isink Veao(H) Veao(Z) gm Vmot ton(max)

Parameter

Start Threshold Voltage Stop Threshold Voltage UVLO Hysteresis Zener Voltage Start-up Supply Current Operating Supply Current Dynamic Operating Supply Current Operating Current at Disable Voltage Feedback Input Threshold1 Line Regulation Temperature Stability of Input Bias Current Output Source Current Output Sink Current Output Upper Clamp Voltage Zero Duty Cycle Output Voltage Transconductance(2) Maximum On-Time Voltage Maximum On-Time Programming Current Sense Input Threshold Voltage Limit Input Bias Current Current Sense Delay to Output(2) Vref1(2)

Condition

VCC increasing VCC decreasing ICC = 20mA VCC = Vth(start) - 0.2V Output no switching 50kHz, CL=1nF Vinv = 0V TA = 25C VCC = 14V ~ 20V Vinv = 1V ~ 4V Vinv = Vref1 - 0.1V Vinv = Vref1 + 0.1V Vinv = Vref1 - 0.1V

Min.

11 7.5 3.0

Typ.

12 8.5 3.5 22 40 1.5 2.5

Max.

13 9.5 4.0

Unit

V V V V

UNDER-VOLTAGE LOCKOUT SECTION

SUPPLY CURRENT SECTION 70 3.0 4.0 95 2.535 10.0 0.5 -12 12 5.4 0.9 90 Rmot = 40.5k Rmot = 40.5k, TA = 25C 2.784 19 6.0 1.0 115 2.900 24 6.6 1.1 140 3.016 29 A mA mA A V mV mV A A A V V mho V sec

20 2.465

65 2.500 0.1 20

ERROR AMPLIFIER SECTION

-0.5

MAXIMUM ON-TIME SECTION

CURRENT SENSE SECTION VCS(limit) Ib(cs) td(cs) Note: 2. These parameters, although guaranteed by design, are not tested in production. 0.7 VCS = 0V ~ 1V dV/dt = 1V/100ns, from 0V to 5V -1.0 0.8 -0.1 350 0.9 1.0 500 V A nsec

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 5

www.fairchildsemi.com

FAN7530 Critical Conduction Mode PFC Controller

Electrical Characteristics (Continued)

VCC = 14V and TA = -40C~125C unless otherwise specified.

Symbol

Vth(ZCD) HY(ZCD) Vclamp(H) Vclamp(L) Ib(ZCD) Isource(zcd) Isink(zcd) tdead

Parameter

Input Voltage Threshold(3) Detect Hysteresis

(3)

Condition

Min.

1.35 0.05

Typ.

1.50 0.10 6.7 0.65 -0.1

Max.

1.65 0.15 7.4 1.00 1.0 -10 10

Unit

V V V V A mA mA nsec

ZERO CURRENT DETECT SECTION

Input High Clamp Voltage Input Low Clamp Voltage Input Bias Current Source Current Capability Sink Current Capability(3)

(3)

Idet = 3mA Idet = -3mA VZCD = 1V ~ 5V TA = 25C TA = 25C

6.0 0 -1.0

Maximum Delay from ZCD to Output dV/dt = -1V/100ns, Turn-on(3) from 5V to 0V Output Voltage High Output Voltage Low Rising Falling Time(3) Time(3) IO = -100mA, TA = 25C IO = 200mA, TA = 25C Cl = 1nF Cl = 1nF VCC = 20V, IO = 100A VCC = 5V, IO = 100A

100

200

OUTPUT SECTION VOH VOL tr tf VO(max) VO(UVLO) td(rst) Vovp HY(ovp) Vth(en) HY(en) Note: 3. These parameters, although guaranteed by design, are not tested in production. 9.2 11.0 1.0 50 50 11.5 13.0 12.8 2.5 100 100 14.5 1 50 TA = 25C TA = 25C 2.620 0.120 0.40 0.05 150 2.675 0.175 0.45 0.10 300 2.730 0.230 0.50 0.15 V V nsec nsec V V sec V V V V

Maximum Output Voltage Output Voltage with UVLO Activated Restart Timer Delay OVP Threshold Voltage OVP Hysteresis Enable Threshold Voltage Enable Hysteresis

RESTART TIMER SECTION OVER-VOLTAGE PROTECTION SECTION

ENABLE SECTION

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 6

www.fairchildsemi.com

FAN7530 Critical Conduction Mode PFC Controller

Typical Characteristics

13.0

9.5

12.5

9.0

Vth(start) [V]

Vth(stop) [V]

12.0

8.5

11.5

8.0

11.0 -60 -40 -20 0 20 40 60 80 100 120 140

7.5 -60 -40 -20 0 20 40 60 80 100 120 140

Temperature [C]

Temperature [C]

Figure 4. Start Threshold Voltage vs. Temp.

Figure 5. Stop Threshold Voltage vs. Temp.

4.00

23.0

3.75

22.5

HY(UVLO) [V]

VZ [V]

3.50

22.0

3.25

21.5

3.00 -60 -40 -20 0 20 40 60 80 100 120 140

21.0 -60 -40 -20 0 20 40 60 80 100 120 140

Temperature [C]

Temperature [C]

Figure 6. UVLO Hysteresis vs. Temp.

Figure 7. Zener Voltage vs. Temp.

60

2.4

30

ICC [mA]

45

Ist [A]

1.6

0.8

15 0.0 -60 -40 -20 0 20 40 60 80 100 120 140 -60 -40 -20 0 20 40 60 80 100 120 140 Temperature [C]

Temperature [C]

Figure 8. Start-up Supply Current vs. Temp.

Figure 9. Operating Supply Current vs. Temp.

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 7

www.fairchildsemi.com

FAN7530 Critical Conduction Mode PFC Controller

Typical Characteristics (Continued)

90

72

ICC(dis) [A]

-60 -40 -20 0 20 40 60 80 100 120 140

Idcc [mA]

54

36

0 -60 -40 -20 0 20 40 60 80 100 120 140

Temperature [C]

Temperature [C]

Figure 10. Dynamic Operating Supply Current vs. Temp.

Figure 11. Operating Current at Disable vs. Temp.

10.0 2.52

7.5

Vref1 [mV]

Vref1 [V]

2.50

5.0

2.48

2.5

0.0 -60 -40 -20 0 20 40 60 80 100 120 140 -60 -40 -20 0 20 40 60 80 100 120 140

Temperature [C]

Temperature [C]

Figure 12. Vref1 vs. Temp.

Figure 13. Vref1 vs. Temp.

0.50 -9

0.25

Ib(ea) [A]

Isource [A]

-60 -40 -20 0 20 40 60 80 100 120 140

0.00

-12

-0.25

-15

-0.50

-18 -60 -40 -20 0 20 40 60 80 100 120 140

Temperature [C]

Temperature [C]

Figure 14. Input Bias Current vs. Temp.

Figure 15. Output Source Current vs. Temp.

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 8

www.fairchildsemi.com

FAN7530 Critical Conduction Mode PFC Controller

Typical Characteristics (Continued)

18

6.6

15

6.3

12

Veao(H) [V]

-60 -40 -20 0 20 40 60 80 100 120 140

Isink [A]

6.0

5.7

5.4 -60 -40 -20 0 20 40 60 80 100 120 140

Temperature [C]

Temperature [C]

Figure 16. Output Sink Current vs. Temp.

Figure 17. Output Upper Clamp Voltage vs. Temp.

1.10

3.00

1.05

2.95

Veao(Z) [V]

1.00

Vmot [V]

-60 -40 -20 0 20 40 60 80 100 120 140

2.90 2.85 2.80 -60 -40 -20 0 20 40 60 80 100 120 140

0.95

0.90

Temperature [C]

Temperature [C]

Figure 18. Zero Duty Cycle Output Voltage vs. Temp.

Figure 19. Maximum On-Time Voltage vs. Temp.

0.90 27

0.85

Ton(max) [s]

24

Vcs(limit) [V]

-60 -40 -20 0 20 40 60 80 100 120 140

0.80

21

0.75

0.70 -60 -40 -20 0 20 40 60 80 100 120 140

Temperature [C]

Temperature [C]

Figure 20. Maximum On-Time vs. Temp.

Figure 21. Current Sense Input Threshold Voltage vs. Temp.

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 9

www.fairchildsemi.com

FAN7530 Critical Conduction Mode PFC Controller

Typical Characteristics (Continued)

1.0

7.2

0.5

6.8

0.0

Vclamp(H) [V]

-60 -40 -20 0 20 40 60 80 100 120 140

Ib(cs) [A]

6.4

-0.5 6.0 -1.0 -60 -40 -20 0 20 40 60 80 100 120 140

Temperature [C]

Temperature [C]

Figure 22. Input Bias Current vs. Temp.

Figure 23. Input High Clamp Voltage vs. Temp.

1.00

1.0

0.75

0.5

Vclamp(L) [V]

0.50

Ib(zcd) [A]

-60 -40 -20 0 20 40 60 80 100 120 140

0.0

0.25

-0.5

0.00

-1.0 -60 -40 -20 0 20 40 60 80 100 120 140

Temperature [C]

Temperature [C]

Figure 24. Input Low Clamp Voltage vs. Temp.

Figure 25. Input Bias Current vs. Temp.

0.9 14 0.6

VO(max) [V]

VO(uvlo) [V]

-60 -40 -20 0 20 40 60 80 100 120 140

13

0.3 0.0 -0.3 -60 -40 -20 0 20 40 60 80 100 120 140

12

Temperature [C]

Temperature [C]

Figure 26. Maximum Output Voltage vs. Temp.

Figure 27. Output Voltage with UVLO Activated vs. Temp.

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 10

www.fairchildsemi.com

FAN7530 Critical Conduction Mode PFC Controller

Typical Characteristics (Continued)

300 250 200

2.73

2.70

td(rst) [s]

Vovp [V]

150 100 50 -60 -40 -20 0 20 40 60 80 100 120 140

2.67

2.64

-60 -40 -20

20

40

60

80

100 120 140

Temperature [C]

Temperature [C]

Figure 28. Restart Delay Time vs. Temp.

Figure 29. OVP Threshold Voltage vs. Temp.

0.500 0.21

0.475

HY(OVP) [V]

0.15

0.12 -60 -40 -20 0 20 40 60 80 100 120 140

Vth(en) [V]

0.18

0.450

0.425

0.400 -60 -40 -20 0 20 40 60 80 100 120 140

Temperature [C]

Temperature [C]

Figure 30. OVP Hysteresis vs. Temp.

Figure 31. Enable Threshold Voltage vs. Temp.

0.150

0.125

HY(en) [V]

0.100

0.075

0.050 -60 -40 -20 0 20 40 60 80 100 120 140

Temperature [C]

Figure 32. Enable Hysteresis vs. Temp.

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 11

www.fairchildsemi.com

FAN7530 Critical Conduction Mode PFC Controller

Applications Information

1. Error Amplifier Block

The error amplifier block consists of a transconductance amplifier, output OVP comparator, and disable comparator. For the output voltage control, a transconductance amplifier is used instead of the conventional voltage amplifier. The transconductance amplifier (voltage controlled current source) aids the implementation of OVP and disable function. The output current of the amplifier changes according to the voltage difference of the inverting and non-inverting input of the amplifier. The output voltage of the amplifier is compared with the internal ramp signal to generate the switch turn-off signal. The OVP comparator shuts down the output drive block when the voltage of the INV pin is higher than 2.675V and there is 0.175V hysteresis. The disable comparator disables the operation of the FAN7530 when the voltage of the inverting input is lower than 0.45V and there is 100mV hysteresis. An external small signal MOSFET can be used to disable the IC, as shown in Figure 33. The IC operating current decreases below 65A to reduce power consumption if the IC is disabled. rent detector turns on the MOSFET. The ZCD pin is protected internally by two clamps, 6.7V-high clamp and 0.65V-low clamp. The 150s timer generates a MOSFET turn-on signal if the drive output has been low for more than 150s from the falling edge of the drive output.

Vin ZCD RZCD 5 6.7V 1.4V 1.5V Zero Current Detector

150s Timer S Q R

Turn-on Signal

FAN7530 Rev. 00

Figure 34. Zero Current Detector Block

3. Sawtooth Generator Block

The output of the error amplifier and the output of the sawtooth generator are compared to determine the MOSFET turn-off instance. The slope of the sawtooth is determined by an external resistor connected to the MOT pin. The voltage of the MOT pin is 2.9V and the slope is proportional to the current flowing out of the MOT pin. The internal ramp signal has a 1V offset; therefore, the drive output is shut down if the voltage of the COMP pin is lower than 1V. The MOSFET on-time is maximum when the COMP pin voltage is 5V. According to the slope of the internal ramp, the maximum on-time can be programmed. The necessary maximum on-time depends on the boost inductor, lowest AC line voltage, and maximum output power. The resistor value should be designed properly.

OVP

2.675V

2.5V

Disable

0.45V

0.35V Vout

Vref1 (2.5V) Error Amp Gm

INV 1 Disable Signal

COMP

FAN7530 Rev. 00

Off Signal MOT 1V Offset 3 2.9V Sawtooth Generator

Figure 33. Error Amplifier Block

2. Zero Current Detection Block

The zero current detector (ZCD) generates the turn-on signal of the MOSFET when the boost inductor current reaches zero using an auxiliary winding coupled with the inductor. If the voltage of the ZCD pin goes higher than 1.5V, the ZCD comparator waits until the voltage goes below 1.4V. If the voltage goes below 1.4V, the zero cur-

Error Amp Output

FAN7530 Rev. 00

Figure 35. Sawtooth Generator Block

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 12

www.fairchildsemi.com

FAN7530 Critical Conduction Mode PFC Controller

4. Over-Current Protection Block

The MOSFET current is sensed using an external sensing resistor for the over-current protection. If the CS pin voltage is higher than 0.8V, the over-current protection comparator generates a protection signal. An internal RC filter is included to filter switching noise.

5. Switch Drive Block

The FAN7530 contains a single totem-pole output stage designed for direct drive of the power MOSFET. The drive output is capable of up to +500/-800mA peak current with a typical rise and fall time of 50ns with 1nF load. The output voltage is clamped to 13V to protect the MOSFET gate if the VCC voltage is higher than 13V.

40k CS 4 8pF 0.8V

OCP Signal

6. Under-Voltage Lockout Block

If the VCC voltage reaches 12V, the ICs internal blocks are enabled and start operation. If the VCC voltage drops below 8.5V, most of the internal blocks are disabled to reduce the operating current. VCC voltage should be higher than 8.5V under normal conditions.

Over-Current Protection Comparator

FAN7530 Rev. 00

Figure 36. Over-Current Protection Block

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 13

www.fairchildsemi.com

FAN7530 Critical Conduction Mode PFC Controller

Typical Application Circuit

Application

Ballast

Output Power

100W

Input Voltage

Universal input (85~265VAC)

Output Voltage

400V

Features

High efficiency (>90% at 85VAC input) Low total harmonic distortion (THD) (<10% at 265VAC input, 25W load)

Key Design Notes

R1, R2, R5, C11 should be optimized for best THD characteristic.

1. Schematic

T1 VAUX BD C5 R3 R4 C10 NTC ZD1 D1 C3 C2 LF1 C1 R2

INV 1

PFC OUTPUT D2

R5 D3 Q1 C11

6 5 ZCD

R10

R6 C9

C4

8 VCC

OUT GND

R9 FAN7530

MOT COMP CS 2 3 4

R11

V1 F1 C6

R1

R8 C7 C8

R7

AC INPUT

FAN7530 Rev. 00

Figure 37. Schematic

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 14

www.fairchildsemi.com

FAN7530 Critical Conduction Mode PFC Controller

2. Inductor Schematic Diagram

1 NVcc 2 3 Np 5

FAN7530 Rev. 00

Figure 38. Inductor Schematic Diagram

3. Winding Specification No

Np NVcc

Pin (sf)

53 24

Wire

0.1 30

Turns

58 8

Winding Method

Solenoid Winding Solenoid Winding

Insulation: Polyester Tape t = 0.050mm, 4 Layers 0.2 10 Outer Insulation: Polyester Tape t = 0.050mm, 4 Layers Air Gap: 0.6mm for each leg

4. Electrical Characteristics Pin

Inductance 3-5

Specification

600H 10%

Remarks

100kHz, 1V

5. Core & Bobbin

Core: EI3026 Bobbin: EI3026 Ae(mm2): 111

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 15

www.fairchildsemi.com

FAN7530 Critical Conduction Mode PFC Controller

6. Demo Circuit Part List Part

F1 NTC R1 R2 R3 R4 R5 R6 R7 R8 R9 R10 R11

Value

Fuse 3A/250V NTC 10D-9 Resistor 56k 820k 330k 150 20k 10 0.2 10k 10k 2M 12.9k Capacitor

Note

Part

T1

Value

Inductor 600H MOSFET

Note

EI3026

Q1 1/4W 1/4W 1/2W 1/2W 1/4W 1/4W 1/2W 1/4W 1/4W 1/4W 1/4W BD D1 D2 D3 ZD1

FQPF13N50C Diode 1N4148 BYV26C SB140 1N4746

Fairchild

Fairchild 600V, 1A Fairchild 18V

Bridge Diode KBL06 Line Filter LF1 40mH IC IC1 FAN7530 TNR Fairchild Wire 0.4mm 600V/4A

C1 C2 C3 C4 C5 C6 C7 C8 C9 C10 C11

150nF/275VAC 470nF/275VAC 2.2nF/3kV 2.2nF/3kV 47F/25V 47nF/50V 220nF/50V 100F/450V 12nF/100V 56pF/50V

Box Capacitor Box Capacitor Ceramic Capacitor Ceramic Capacitor Electrolytic Capacitor Ceramic Capacitor Multilayer Ceramic Capacitor Electrolytic Capacitor Film Capacitor Ceramic Capacitor V1 471 470V

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 16

www.fairchildsemi.com

FAN7530 Critical Conduction Mode PFC Controller

7. Layout

Power Ground

Separate the power ground and the signal ground

Signal Ground

Place the output voltage sensing resistors close to IC

Figure 39. PCB Layout Considerations for FAN7530

8. Performance Data POUT

PF 100W THD Efficiency PF 75W THD Efficiency PF 50W THD Efficiency PF 25W THD Efficiency

85VAC

0.998 5.1% 90.9% 0.999 4.1% 91.6% 0.998 4.4% 91.3% 0.995 7.9% 86.4%

115VAC

0.998 3.6% 93.7% 0.998 3.6% 93.3% 0.997 5.0% 91.9% 0.991 8.6% 87.1%

230VAC

0.991 5.2% 95.6% 0.986 5.0% 94.6% 0.974 5.7% 92.7% 0.923 8.3% 87.3%

265VAC

0.984 6.2% 96% 0.975 5.7% 95.3% 0.956 6.2% 93.4% 0.876 8.7% 88.1%

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 17

www.fairchildsemi.com

FAN7530 Critical Conduction Mode PFC Controller

Mechanical Dimensions

8-DIP

Dimensions are in millimeters (inches) unless otherwise noted. .

1.524 0.10

#1

#8

9.20 0.20 0.362 0.008 9.60 MAX 0.378

#4

#5

2.54 0.100

5.08 MAX 0.200 7.62 0.300 3.40 0.20 0.134 0.008

3.30 0.30 0.130 0.012 0.33 0.013 MIN

0.25 0.05

0~15

+0.10

0.010 0.002

September 1999, Rev B 8dip_dim.pdf

+0.004

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 18

0.018 0.004

www.fairchildsemi.com

0.060 0.004

0.46 0.10

6.40 0.20 0.252 0.008

0.79 ) 0.031

FAN7530 Critical Conduction Mode PFC Controller

Mechanical Dimensions (Continued)

8-SOP

Dimensions are in millimeters (inches) unless otherwise noted.

MIN 1.55 0.20 0.061 0.008

0.1~0.25 0.004~0.001

#1

#8

4.92 0.20 0.194 0.008

5.13 MAX 0.202

(

#4 #5 6.00 0.30 0.236 0.012 1.80 MAX 0.071 3.95 0.20 0.156 0.008 5.72 0.225 0.50 0.20 0.020 0.008

September 2001, Rev B1 sop8_dim.pdf

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 19

0.56 ) 0.022

0~ 8

MAX0.10 MAX0.004

1.27 0.050

www.fairchildsemi.com

0.41 0.10 0.016 0.004

+0.10 0.15 -0.05 +0.004 0.006 -0.002

FAN7530 Critical Conduction Mode PFC Controller

2006 Fairchild Semiconductor Corporation FAN7530 Rev. 1.0.1 20

www.fairchildsemi.com

You might also like

- 1N4001 DDocument4 pages1N4001 DJohn SharpNo ratings yet

- High Speed Switching Diode Spec SheetDocument1 pageHigh Speed Switching Diode Spec SheetManuel NolascoNo ratings yet

- 2SB1370Document3 pages2SB1370Manuel NolascoNo ratings yet

- Dual Digital Potentiometer Chip with Ultra-Low Power and Temperature CompensationDocument12 pagesDual Digital Potentiometer Chip with Ultra-Low Power and Temperature CompensationManuel NolascoNo ratings yet

- Hip 4080Document17 pagesHip 4080Juninbox1No ratings yet

- OP AMP Ne5532Document15 pagesOP AMP Ne5532José Mario DonaireNo ratings yet

- 2sa1015 TosDocument3 pages2sa1015 Tosmei jonieNo ratings yet

- MS 2135FDocument34 pagesMS 2135FManuel NolascoNo ratings yet

- Service Manual: Fm/Am Compact Disc PlayerDocument54 pagesService Manual: Fm/Am Compact Disc PlayerManuel NolascoNo ratings yet

- Plasma TV: Service ManualDocument37 pagesPlasma TV: Service ManualTobias LehenbergerNo ratings yet

- CXA2074Q/S: US Audio Multiplexing DecoderDocument39 pagesCXA2074Q/S: US Audio Multiplexing DecoderManuel NolascoNo ratings yet

- SCH Ampli 8-c4Document1 pageSCH Ampli 8-c4Manuel NolascoNo ratings yet

- Drill Vise MillDocument2 pagesDrill Vise MillFrenchwolf420No ratings yet

- AN78M20FDocument10 pagesAN78M20FFrantsiskoNo ratings yet

- KIA7805Document17 pagesKIA7805Thomas1JessieNo ratings yet

- Hip 4080Document17 pagesHip 4080Juninbox1No ratings yet

- Specifications: Varistor GNR14DDocument6 pagesSpecifications: Varistor GNR14Ddotb_09_09No ratings yet

- AN78M20FDocument10 pagesAN78M20FFrantsiskoNo ratings yet

- Termistori NTCDocument29 pagesTermistori NTCConstantin Vilnoiu100% (1)

- Sunn Concert BassDocument1 pageSunn Concert BassManuel NolascoNo ratings yet

- High Speed Switching Diode Spec SheetDocument1 pageHigh Speed Switching Diode Spec SheetManuel NolascoNo ratings yet

- Datasheet - HK In5408 4525768Document2 pagesDatasheet - HK In5408 4525768Ndambuki DicksonNo ratings yet

- Datasheet - HK In5408 4525768Document2 pagesDatasheet - HK In5408 4525768Ndambuki DicksonNo ratings yet

- AT2011 VW - ZF - BackDocument94 pagesAT2011 VW - ZF - BackRodrigo PalaciosNo ratings yet

- LB1845 PWM Current ControlDocument7 pagesLB1845 PWM Current ControlNacer MezghicheNo ratings yet

- BZXXV XDocument7 pagesBZXXV XManuel NolascoNo ratings yet

- K 9259 DDocument57 pagesK 9259 DManuel NolascoNo ratings yet

- 037 RSM CapacitorsDocument15 pages037 RSM CapacitorsManuel NolascoNo ratings yet

- Hip 4080Document17 pagesHip 4080Juninbox1No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5784)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Quizlet-Philippine Electrical CodeDocument2 pagesQuizlet-Philippine Electrical Codena zafira0% (1)

- Fundamental of Database: Madda Walabu University College of Computing Department of Information TechnologyDocument46 pagesFundamental of Database: Madda Walabu University College of Computing Department of Information TechnologychalaNo ratings yet

- F 0177 914 Continuous Emission MonitorDocument2 pagesF 0177 914 Continuous Emission MonitorKUNALNo ratings yet

- Complex Numbers: Problem-SolvingDocument2 pagesComplex Numbers: Problem-SolvingK TariNo ratings yet

- Top 10 Windows Firewall Netsh CommandsDocument4 pagesTop 10 Windows Firewall Netsh CommandsedsoncalleNo ratings yet

- Basic Research Approaches and Designs - An Overview - Amoud - 2020Document18 pagesBasic Research Approaches and Designs - An Overview - Amoud - 2020Haaji CommandoNo ratings yet

- Formation and Evolution of Planetary SystemsDocument25 pagesFormation and Evolution of Planetary SystemsLovelyn Baltonado100% (2)

- Mapping Abap XML PDFDocument88 pagesMapping Abap XML PDFassane2mcsNo ratings yet

- Cube Nets Non-Verbal Reasoning IntroductionDocument6 pagesCube Nets Non-Verbal Reasoning Introductionmirali74No ratings yet

- 2 Fourier and Wavelet Transforms: 2.1. Time and Frequency Representation of SignalsDocument25 pages2 Fourier and Wavelet Transforms: 2.1. Time and Frequency Representation of SignalszvjpNo ratings yet

- 2024 Quiz Bee Math 7Document1 page2024 Quiz Bee Math 7Jabez Magda GenorgaNo ratings yet

- Instantaneous Waterhammer EquationDocument10 pagesInstantaneous Waterhammer EquationkiranNo ratings yet

- Reed - Camion - XT39R4 - 1003 - Technical Manual - Panel de Control PDFDocument293 pagesReed - Camion - XT39R4 - 1003 - Technical Manual - Panel de Control PDFLuisEduardoHerreraCamargo100% (1)

- Synopsis On Mobile TrackingDocument11 pagesSynopsis On Mobile Trackingcooolhoney885No ratings yet

- Topic 4 - Chemical Kinetics 4b - Half LifeDocument20 pagesTopic 4 - Chemical Kinetics 4b - Half LifeJoshua LaBordeNo ratings yet

- Discussion Exp 2 Chm674Document4 pagesDiscussion Exp 2 Chm674Eva Lizwina MatinNo ratings yet

- Hikmayanto Hartawan PurchDocument12 pagesHikmayanto Hartawan PurchelinNo ratings yet

- Administering Agilent 3070 Systems (MS Windows NT and 2000) Chapter 8Document60 pagesAdministering Agilent 3070 Systems (MS Windows NT and 2000) Chapter 8Adam KaNo ratings yet

- Puppo, F. (2012) - Dalla Vaghezza Del Linguaggio Alla Retorica Forense. Saggio Di Logica GiuridicaDocument3 pagesPuppo, F. (2012) - Dalla Vaghezza Del Linguaggio Alla Retorica Forense. Saggio Di Logica GiuridicaAldunIdhunNo ratings yet

- VHDL ExperimentsDocument55 pagesVHDL Experimentssandeepsingh93No ratings yet

- Hadoop HiveDocument61 pagesHadoop HivemustaqNo ratings yet

- Atmospheric, Gage, and Absolute PressureDocument13 pagesAtmospheric, Gage, and Absolute PressureJefrie Marc LaquioNo ratings yet

- Java Array, Inheritance, Exception Handling Interview QuestionsDocument14 pagesJava Array, Inheritance, Exception Handling Interview QuestionsMuthumanikandan Hariraman0% (1)

- Binder 1Document36 pagesBinder 1BobbyNo ratings yet

- Uefi Firmware Enabling Guide For The Intel Atom Processor E3900 Series 820238Document42 pagesUefi Firmware Enabling Guide For The Intel Atom Processor E3900 Series 820238賴翊翊No ratings yet

- Quickin: 3D/2D Modelling Suite For Integral Water SolutionsDocument110 pagesQuickin: 3D/2D Modelling Suite For Integral Water SolutionscocoNo ratings yet

- D200801 Slope and Offset Adjustment For A Pressure SensorDocument4 pagesD200801 Slope and Offset Adjustment For A Pressure SensorBrian McMorrisNo ratings yet

- Modeling Confined Masonry Walls with OpeningsDocument11 pagesModeling Confined Masonry Walls with OpeningsMangisi Haryanto ParapatNo ratings yet

- Assignment No.3 Bolted JointsDocument6 pagesAssignment No.3 Bolted JointsYash SahuNo ratings yet

- Propeller Model Tests GuideDocument12 pagesPropeller Model Tests GuideOdpewğw RlelelwNo ratings yet