Professional Documents

Culture Documents

QPSK Ist

Uploaded by

johnmechanjiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

QPSK Ist

Uploaded by

johnmechanjiCopyright:

Available Formats

Implementation of a QPSK System on FPGA

S.O. Popescu

*

, A.S.Gontean

*

and D.Ianchis

*

*

Applied Electronics Departament, Faculty of Electronics and Telecommunications,

Politehnica University of Timisoara, Romania;

silvana.popescu@etc.upt.ro, aurel.gontean@etc.upt.ro, daniel.ianchis@etc.upt.ro

Abstract The paper presents the design of a QPSK digital

communication system and its implementation on FPGAs.

The simulations of the system were made in Matlab/

Simulink environment and System Generator, a tool used

for FPGA designs. The system is made up of two Spartan 3E

Starter Kit boards. The first is implemented to comport as a

modulator and the second as a demodulator. The VHDL

hardware description language was used to design each

model. The local clock oscillator on the board operates at

50Mhz and used at 31,250 kHz for the carrier. The

operating results were compared with the theorethical ones

and were also evaluated by measurements.

I. INTRODUCTION

A significant transition from analog to digital has

occurred in the last years and communications is a field

which has gain a lot because of this development. The

advanced algorithms used in a digital communication

system made it more reliable than an analog one.

Studies about the implementation of digital

communication systems were made in [1]-[7].

The hardware and software resources used in generating

the QPSK (Quadrature Phase Shift Keying) modulation

and demodulation were a computer with the Xilinx

WebPack ISE on it, two Spartan 3E Starter Kit boards and

a LeCroy WaveSurfer Xs Series Oscilloscope, a high

performance digital oscilloscope.

The purpose of this paper is to create a QPSK (Binary

Phase Shift Keying) system made of a modulator, a

channel and a demodulator from two Spartan 3E boards.

The modulated signal was obtained in the first Spartan 3E

board, passed through a channel and transmitted to the

second board, the demodulator. At the output of the

demodulator, the modulating signal was found again.

The paper is organized into 6 sections. The paper begins

with an introduction in section 1. Section 2 presents the

theoretical backgrounds about the digital communication

system and about the QPSK modulation and

demodulation. The implementation of the QPSK system in

Matlab/ Simulink and System Generator are presented in

section 3. Section 4 is dedicated to the implementation of

the system: modulator and demodulator on the Spartan 3E

Starter Kit boards. The results are discussed in section 5.

The final section, 6, presents the conclusions.

II. THEORETICAL BACKGROUNDS

A. Digital Communication System

A typically digital communication system is presented

in Fig.1. The role of a digital communication system is to

transport digital data between two nodes: the transmitter

and the receiver. A digital communication system is made

up of both digital and analog parts. The digital part

Figure 1. A Digital Communication System [8].

consists of digital source/user, source encoder/decoder,

channel encoder/decoder and the digital modulator/

demodulator. The transmitter, receiver, the channel

models and noise models forms the analog part [1].

The message to be sent is from a digital source. The

binary information obtained at the output of the channel

encoder is than passed to a digital modulator with the

main purpose to translate the discrete symbols into an

analog waveform that can be transmitted over the channel

[9], [10]. In the receiver, the reverse signal processing

happens. The channel represents the physical medium that

carries a signal between the transmitter and the receiver.

Any signal which passes through the channel is corrupted

with noise whatever the medium used for transmission [8].

The digital data is transmitted between the transmitter

and the receiver by varying a physical characteristic of a

sinusoidal carrier, either the frequency or the phase or the

amplitude. This operation is performed with a modulator

at the transmitting end to impose the physical change to

the carrier and a demodulator at the receiving end to detect

the resultant modulation on reception [2], [8].

B. QPSK Modulation and Demodulation

The signals of the QPSK modulation are defined in (1),

where

c

f

is the frequency of the carrier and u t I

[8], [9]:

s

(t) = Acos|2n

c

t + 0

] , i = 1, 2, S, 4

and 0

=

(2-1)n

4

(1)

The initial phases of the signals are

n

4

,

3n

4

,

5n

4

,

7n

4

.

Equation (1) can also be written as [8], [9]:

s

(t) = s

1

(t)

1

(t) + s

2

(t)

2

(t) (2)

where:

1

(t) = _

2

I

cos 2n

c

t , u t T

(3)

2

(t) = -_

2

I

sin2n

c

t , u t T

(4)

SISY 2011 2011 IEEE 9th International Symposium on Intelligent Systems and Informatics September 8-10, 2011, Subotica, Serbia

365 978-1-4577-1974-5/11/$26.00 2011 IEEE

s

1

= E cos 0

(5)

s

2

= E sin 0

(6)

where E =

A

2

1

2

is the symbol energy.

In QPSK, two bits are grouped together to form

signals, and one of the four possible cases of dibits: 00,

01, 10 and 11 is transmitted. Also, the odd bits were

mapped to s

1

and the even bits into s

2

[2].

Equation (2) of the entire QPSK signal can be written

as:

s(t) =

A

2

I(t) cos 2n

c

t -

A

2

(t) sin 2n

c

t

(7)

where I(t) and (t)are pulse trains determined by the

odd and even bits [9].

Since each bit occupies I

b

seconds, the signals

corresponding to the dibits last for I

s

= 2I

b

[9].

The QPSK modulator illustrated in fig.2 is based on (7).

The binary sequence is separated by the serial-to-parallel

converter into odd-bit-sequence for I channel and even-

bit- sequence for Q channel. The corresponding

waveforms are illustrated in fig.3.

Figure 2. The QPSK Modulator [9].

Figure 3. QPSK Waveforms [9].

Figure 4. QPSK Demodulator.

In the demodulator, the reverse operation happens. The

I-channel and the Q-channel are demodulated separately

as two different BPSK signals. The I-channel is

demodulated with a cosine waveform and the Q-channel,

with a sine waveform. A parallel-to-serial-converter is

used to combine the two sequences into a single one

which represents the modulating signal.

III. QPSK SYSTEM

A. QPSK System in Simulink

Fig. 5 represents a communication system implemented

in the Matlab/ Simulink environment that uses the BPSK

modulation technique. The system is composed of the

binary data source, a modulator, a channel and a

demodulator.

In [10], a QPSK modulator is implemented in the

Simulink environment and in System Generator. We used

the implementation of the modulator [10] in order to

create the system.

The modulator [10]: The binary data source is made of

a random data source and a rounding function and

generates the modulating signal. The binary sequence is

separated into an odd-bit-sequence I and an even-bit-

sequence with the help of the sample-and-hold block. The

I-channel is modulated with a cosine waveform generated

by a cosine block and the Q-channel is modulated with a

sine waveform. The switch blocks will choose between

the first or third output depending on the value of the

second input. In the case of the I-channel, if the second

input is 1, the output value will be cosine, but if the

second input is 0, the output will be cosine and for the

Q-channel, if the second input is 1, the output value

will be sine, but if the second input is 0, the output will

be sine. The sum block combines the two modulated

signals into the QPSK signal.

Figure 5. QPSK System.

The corresponding signal in the modulator can be seen

in fig.6.

The modulated signal is then pass through a channel

where noise is added (fig.7). The waveform of the

modulated signal with noise is shown in fig.8.

S. O. Popescu et al. Implementation of a QPSK System on FPGA

366

Figure 6. The waveforms in the modulator [10]

(a) The modulating signal (b) I(t) (c) I(t) cos 2n

c

t

(d) (t) (e) (t) sin2n

c

t (f) The modulated signal

Figure 7. Band Limited Noisy Channel.

Figure 8. The waveforms shown on the scope

(a) the modulated signal (b) the noise

(c) the modulated signal with noise.

The modulated signal added with noise arrives at the

demodulator (fig. 9) and is divided into two channels.

The first channel is modulated with a cosine waveform

and the second with a sine as well as in theory. At the

outputs, the I and Q channels are found and put together

to obtain the initial binary sequence (fig. 10).

Figure 9. QPSK demodulator.

Figure 10. The waveforms in the demodulator

(a) The modulated signal with noise (b) The I-channel

(c) The Q-channel (d) The demodulated signal.

B. QPSK System in System Generator

Designs made in System Generator include all

implementation steps: synthesis, place and route in order

to generate an FPGA programming file [11]. The main

advantage of System Generator is making possible the

administration of the Xilinx components.

Our QPSK system implemented in System Generator

uses the same modulator implemented in [10], the data

source, a channel and a demodulator.

The modulating signal is generated internal by a LFSR

(Linear Feedback Shift Register). The Time Division

Demultiplexer block divides the modulating signal into

the odd-sequence I and even-sequence Q, action which

takes place inside the FPGA (fig.11). Then, the I-channel

is modulated with cosine and the Q-channel with sine

(fig.12). The mux block implements a multiplexer. It has

3 inputs: the d0 and d1 inputs of the mux represent cosine

and cosine for the I sequence and sine and sine for the

Q sequence. The sel input selects between d0 and d1

depending on the odd-sequence for mux1 and the even-

sequence for mux. The modulated signal is obtained by

adding the two outputs. The modulated signal is then pass

through the same channel used in Simulink where noise is

added and arrives at the input of the demodulator

(fig.13a).

In the demodulator, the modulated signal with noise is

multiplied once with sine, and the second time with

cosine. The sine and cosine waveforms are recovered in

Simulink with the sine and cosine blocks.

SISY 2011 2011 IEEE 9th International Symposium on Intelligent Systems and Informatics September 8-10, 2011, Subotica, Serbia

367

Figure 11. The waveforms in the modulator:

(a) The modulating signal (b) The I-channel

(c) The Q-channel

Figure 12. The Waveforms:

(a) I-channel (b) Q-channel (c) the modulated signal.

Figure 13. QPSK Demodulator in System Generator.

Figure 14. The Waveforms:

(a) the modulated signal with noise (b) the demodulated I-channel

(c) the demodulated Q-channel.

Figure 15. The Waveforms:

(a) the modulating signal (b) the demodulated signal.

The two signals obtained are kept in two accumulators

and then compared with a threshold. If the compared

signal is positive, the demodulator takes the decision that

1 was transmitted, otherwise, 0, obtaining the

demodulated I and Q channels (fig.14b and fig.14c). The

multiplexer is the one who puts the I and Q channels

together obtaining the demodulated signal which is the

initial modulating signal (fig.15).

IV. BPSK SYSTEM ON THE SPARTAN 3E BOARD

The BPSK System (fig.16) that we implemented on the

Spartan 3E Starter Kit board [12] has as a model the

implementation in System Generator with the only

difference that the sine and cosine signals are generated

internal, in a ROM.

The BPSK system (fig.16) consists of two Spartan 3E

boards, the first board behaves as a modulator and the

second one, as a demodulator. The connections between

the two boards are made of three wires: the green wire

comports as a communication channel, the red wire

represents the synchronization between the two boards

and the black one comports as an asynchronous reset

signal.

S. O. Popescu et al. Implementation of a QPSK System on FPGA

368

Figure 16. QPSK System experimental setup.

The modulating signal is generated internal, in the

modulator, by a LFSR and is divided into two sequences:

the-odd-sequence or the I-channel and the-even-sequence

or the Q-channel. The I-channel is modulated with cosine

and the Q-channel with sine. The sine and cosine are also

generated internal, and are made of 16 different values

kept in a ROM memory [13]. The cosine is obtained from

sine by reading the values later with 4 samples. By adding

the two modulated signals, the QPSK modulated signal is

obtained. The modulated signal is then sent to the DAC

(Digital-to-Analog Converter) on the board in order to be

sent through the channel. The principle of the QPSK

modulator implemented on the FPGA is shown in fig.17.

Figure 17. The principle of the QPSK modulator on the FPGA [10].

The modulated signal affected with noise arrives at the

second board which behaves as a demodulator. The signal

is converted into a digital form with the help of a pmod

AD1. This digital signal is then multiply with both

signals, the sine and cosine generated internal in a ROM

memory. The results are kept in an accumulator and

compared with a decision threshold and so, the

demodulated I-channel and Q-channel are obtained and in

the end the demodulated signal. The principle of the

QPSK demodulator implemented on the FPGA is

illustrated in fig.18.

Figure 18. The principle of the QPSK demodulator on the FPGA

V. RESULTS

After implementing the QPSK System made of a

modulator and demodulator on the two Spartan 3E Starter

Kit boards, the signals were routed to the LeCroy

WaveSurfer Xs Series Oscilloscope [14], a high

performance digital oscilloscope.

Fig.19 illustrates two signals in the modulator: the

LFSR and the QPSK modulated signal. In fig.20, the

modulating and the demodulated signals are shown.

Figure 19. The Waveforms:

(a) the modulating signal (LFSR) ; (b) the modulated signal.

Figure 20. The waveforms:

(a) The modulating signal (b) The demodulated signal.

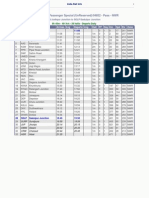

Fig. 21 and 22 illustrate the design summary of the

modulator and demodulator boards.

Figure 21. Design Summary of the QPSK Modulator.

Figure 22. Design Summary of the QPSK Demodulator.

SISY 2011 2011 IEEE 9th International Symposium on Intelligent Systems and Informatics September 8-10, 2011, Subotica, Serbia

369

Fig.23 and fig.24 show the post and route

implementation of the QPSK modulator and demodulator

on the two Spartan 3E boards.

Figure 23. The route paths of the QPSK modulator.

Figure 24. The route paths of the QPSK demodulator.

VI. CONCLUSION

The paper presents an implementation of a QPSK

System (Modulator and Demodulator) in the

Matlab/Simulink environment as well as a proposal of a

QPSK System in System Generator.

The binary sequence is generated internal by a LFSR

and is divided into two sequences: the odd-sequence (I-

channel) and the even-sequence (Q-channel). The odd-

sequence is modulated with the cosine waveform and the

even-sequence with the sine waveform, waveforms

obtained outside the board. The QPSK modulated signal is

obtained by adding the two modulated signals. The QPSK

modulated signal is then passed through the same channel

used in Simulink where noise is added. In the

demodulator, the modulated signal with noise is

multiplied twice, once with sine, and the second time with

cosine. The two signals are kept in two accumulators and

then compared with a threshold. If the compared signal is

greater than the threshold, the demodulator takes the

decision that 1 was transmitted, otherwise, 0, obtaining

the demodulated I and Q channels. The multiplexer is the

one who puts the I and Q channels together obtaining the

demodulated signal which is the initial modulating signal.

The same principle is applied in implementing the

modulator and the demodulator on the two boards, with

the difference that the sine and cosine signals were

generated inside the board. The sine signal was made of

16 different values kept in a ROM memory and the cosine

was obtained reading the ROM memory later with 4

samples. The odd-sequence was modulated with the

cosine waveform and the even-sequence with the sine

waveform. Adding the two modulated signals, the QPSK

signal was obtained. The modulated signal is then sent to

the DAC on the board in order to be sent through the

channel. The modulated signal affected with noise arrives

at the demodulator. The signal is converted into a digital

form with the help of an AD board. This digital signal is

then multiply with both signals, the sine and cosine

generated internal in the ROM memory from the second

board. The results are kept in an accumulator and

compared with a decision threshold and so, the

demodulated I-channel and Q-channel are obtained and in

the end the demodulated signal.

ACKNOWLEDGMENT

This work was partially supported by the strategic grant

POSDRU 6/1.5/S/13, (2008) of the Ministry of Labour,

Family and Social Protection, Romania, co-financed by

the European Social Fund Investing in People.

REFERENCES

[1] A.Grgr, F.Arikan, O.Arikan, Simulation of a digital

communication system, in Proceedings of the 13

th

European

Signal Processing Conference EUSIPCO, 2005, Turkey,

http://www.eurasip.org/Proceedings/Eusipco/Eusipco2005/defeve

nt/papers/cr1142.pdf

[2] Y.Tachwali, H.Refai, Implementation of a BPSK Transceiver on

Hybrid Software Defined Radio Platforms, 3

rd

International

Conference on Information and Communication Technologies:

From Theory to Applications, Syria, 2008, pp. 1-5.

[3] P.Dondon, J.M.Micouleau, J.Legall, .K.Kadionik, Design of a

low cost BPSK modulator/demodulator for a practical teaching of

digital modulation techniques, in the 4

th

WSEAS/IASME

International Conference on Engineering Education, Greece, 2007,

pp.61-66.

[4] W.Song, J.Zhang, Q.Yao, Design and Implementation of BPSK

Modulator and Demodulator on Modern DSP Technology, 3rd

IEEE International Symposium on Microwave, Antenna,

Propagation and EMC Technologies for Wireless

Communications, China, 2009, pp.1135-1137.

[5] G.Elamary, G.Chester, J.Neasham, A Simple Digital VHDL

QPSK Modulator Designed Using CPLD/ FPGAs for Biomedical

Devices Applications, in Proceedings of the World Congress on

Engineering 2009 Vol.I, 2009, United Kingdom, pp.

[6] P.Dondon, J.M.Micouleau, P.Kadionik, Improving learning

efficiency for digital modulation courses, WSEAS Engineering

education, 2005, Greece, pp.

[7] W.Song, Q.Yao, Design and Implementation of QPSK Modem

Based on FPGA, 2010,

[8] S.Popescu, A.Gontean, M.Babaita, BPSK System on Spartan 3E

FPGA, unpublished.

[9] F.Xiong, Digital Modulation Techniques, Artech House, UK,

2000.

[10] S.Popescu, A.Gontean, D.Ianchis, QPSK Modulator on FPGA,

unpublished.

[11] System Generator for DSP. Getting Started Guide. Xilinx. 2008

[12] Spartan 3E FPGA Starter Kit board. User guide. Xilinx. 2011.

[13] F.Ahamed, A.Scorpino, An educational digital communications

project using FPGAs to implement a BPSK Detector, IEEE

Transactions on Education, Vol.48, No.1, 2005, pp.191-197.

[14] LeCroy WaveSurfer, Xs Series Oscilloscope Operators Manual,

2008

S. O. Popescu et al. Implementation of a QPSK System on FPGA

370

You might also like

- Waspmote Lora 868mhz 915mhz Sx1272 Networking GuideDocument47 pagesWaspmote Lora 868mhz 915mhz Sx1272 Networking GuidejohnmechanjiNo ratings yet

- Advanced MIMO Waveform Deployment Using GNU RadioDocument9 pagesAdvanced MIMO Waveform Deployment Using GNU RadiojohnmechanjiNo ratings yet

- Bitszg 553Document3 pagesBitszg 553johnmechanjiNo ratings yet

- Pawan Tomar Was Born in Moradabad, Uttar Pradesh, India in 1989. HeDocument1 pagePawan Tomar Was Born in Moradabad, Uttar Pradesh, India in 1989. HejohnmechanjiNo ratings yet

- Synopsys Design Compiler Download and Installation MethodsDocument3 pagesSynopsys Design Compiler Download and Installation MethodsjohnmechanjiNo ratings yet

- Ieee FormatDocument4 pagesIeee FormatjohnmechanjiNo ratings yet

- Walsh Functions Wien9 04Document13 pagesWalsh Functions Wien9 04johnmechanjiNo ratings yet

- New Form No 15GDocument4 pagesNew Form No 15GDevang PatelNo ratings yet

- 2013 08 07 PdfbotDocument2 pages2013 08 07 PdfbotjohnmechanjiNo ratings yet

- 04908331Document4 pages04908331johnmechanjiNo ratings yet

- Ox48v Qtriu 0LW9T K30JTDocument1 pageOx48v Qtriu 0LW9T K30JTbeststar1No ratings yet

- Lab 5Document4 pagesLab 5johnmechanjiNo ratings yet

- 04542291Document6 pages04542291johnmechanjiNo ratings yet

- 06031440Document6 pages06031440johnmechanjiNo ratings yet

- 04457920Document9 pages04457920johnmechanjiNo ratings yet

- HornDocument11 pagesHornjohnmechanjiNo ratings yet

- 04340413Document5 pages04340413johnmechanjiNo ratings yet

- IRI-22481-Jodhpur - Delhi Sarai Rohilla (Via Ratangarh) ExpDocument1 pageIRI-22481-Jodhpur - Delhi Sarai Rohilla (Via Ratangarh) ExpjohnmechanjiNo ratings yet

- Laboratory ExerciseDocument15 pagesLaboratory ExercisejohnmechanjiNo ratings yet

- IRI-04852-Jodhpur Hisar Passenger Special (UnReserved)Document1 pageIRI-04852-Jodhpur Hisar Passenger Special (UnReserved)johnmechanjiNo ratings yet

- IRI-22481-Jodhpur - Delhi Sarai Rohilla (Via Ratangarh) ExpDocument1 pageIRI-22481-Jodhpur - Delhi Sarai Rohilla (Via Ratangarh) ExpjohnmechanjiNo ratings yet

- TEST6Document2 pagesTEST6johnmechanjiNo ratings yet

- 05560584Document1 page05560584johnmechanjiNo ratings yet

- IRI-54823-Jodhpur Hissar Passenger (UnReserved)Document1 pageIRI-54823-Jodhpur Hissar Passenger (UnReserved)johnmechanjiNo ratings yet

- Error Detection and CorrectionDocument73 pagesError Detection and CorrectionJagannath AcharyaNo ratings yet

- Ch10 ForouzanDocument44 pagesCh10 Forouzanjohnmechanji0% (1)

- Synopsys SPW DsDocument4 pagesSynopsys SPW Dsgame___overNo ratings yet

- TEST6Document2 pagesTEST6johnmechanjiNo ratings yet

- IRI-04852-Jodhpur Hisar Passenger Special (UnReserved)Document1 pageIRI-04852-Jodhpur Hisar Passenger Special (UnReserved)johnmechanjiNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Cummins Power Generation Proposed Aba MV S/S Associated WorksDocument2 pagesCummins Power Generation Proposed Aba MV S/S Associated WorksbenNo ratings yet

- Hoja Tecnica PLC'S VTP 402Document7 pagesHoja Tecnica PLC'S VTP 402Angel Flores RojasNo ratings yet

- Ug948 Vivado Sysgen TutorialDocument137 pagesUg948 Vivado Sysgen TutorialQuỳnh Lê CôngNo ratings yet

- Home stereo single-chip tuner IC with electronic tuningDocument15 pagesHome stereo single-chip tuner IC with electronic tuningevel1414No ratings yet

- CMOS Working Principle and ApplicationsDocument23 pagesCMOS Working Principle and Applicationssachinkumar anjutagiNo ratings yet

- OSciloDocument8 pagesOSciloChristiam HugoNo ratings yet

- NX-series PROFINET® Coupler Unit NX-PNCDocument15 pagesNX-series PROFINET® Coupler Unit NX-PNCNH KimNo ratings yet

- 42tl016 Audio Transformer DiagramDocument2 pages42tl016 Audio Transformer DiagramMiguelangel Lopez MadridNo ratings yet

- 6BK16200AA000AA0 Datasheet enDocument3 pages6BK16200AA000AA0 Datasheet enMedAchrefZoghlamiNo ratings yet

- Lenovo G400s Disassembly ManualDocument104 pagesLenovo G400s Disassembly ManualAlexandre Telles100% (1)

- Vanguard Electric 2022Document24 pagesVanguard Electric 2022Frederick GuerreroNo ratings yet

- Indus Lecture 2 PartialDocument69 pagesIndus Lecture 2 PartialIris Jean Mosquera100% (1)

- Info Iec60255-151 (Ed1.0) BDocument11 pagesInfo Iec60255-151 (Ed1.0) BMuthu KumarNo ratings yet

- Industrial Training at Hobbyzone KepongDocument21 pagesIndustrial Training at Hobbyzone KepongEhh MuslihahNo ratings yet

- Um2861 Stm32u5 Nucleo144 Board mb1549 StmicroelectronicsDocument49 pagesUm2861 Stm32u5 Nucleo144 Board mb1549 StmicroelectronicsunwantedadvertisementNo ratings yet

- Ii B.Tech I Semester (R09) Regular Examination Results Hall Ticket NoDocument2 pagesIi B.Tech I Semester (R09) Regular Examination Results Hall Ticket NoMuramshetty SantoshNo ratings yet

- Safety-Certified Hardware and FirmwareDocument10 pagesSafety-Certified Hardware and FirmwarenuriaNo ratings yet

- IJIREEICE5 s2 Divakar Finding Optimal Feed Location of A Microstrip Patch Antenna Using HFSS PDFDocument3 pagesIJIREEICE5 s2 Divakar Finding Optimal Feed Location of A Microstrip Patch Antenna Using HFSS PDFSandeepSranNo ratings yet

- Freescale MC9S08SH8 Hoja de DatosDocument341 pagesFreescale MC9S08SH8 Hoja de DatosfcoparraortizNo ratings yet

- Half-Wave Rectifier: 15 . DetermineDocument3 pagesHalf-Wave Rectifier: 15 . DetermineS&E Cambodia Show0% (1)

- Two-way car alarm manualDocument11 pagesTwo-way car alarm manualRichard Bernal50% (2)

- 2 4tec3Document20 pages2 4tec3betor_28No ratings yet

- Concept Strengthening Sheet CSS 03 Based On AIATS 03 CF+OYM PhysicsDocument7 pagesConcept Strengthening Sheet CSS 03 Based On AIATS 03 CF+OYM PhysicsJIDNESH BHERENo ratings yet

- L-TRI - Assembly-Operation-Maintenance Guide - AGS531883-01 - 2014-02Document52 pagesL-TRI - Assembly-Operation-Maintenance Guide - AGS531883-01 - 2014-02Hani SamirNo ratings yet

- ISD4004 Based Voice RecorderDocument2 pagesISD4004 Based Voice RecorderIndra SetiawanNo ratings yet

- 14 FlipflopsDocument20 pages14 FlipflopsMichael David CaparazNo ratings yet

- Rangkaian Pembagi Tegangan Dan Arus: Voltage and Current Divider CircuitDocument17 pagesRangkaian Pembagi Tegangan Dan Arus: Voltage and Current Divider Circuitali muhammad hanafiyahNo ratings yet

- Small-Signalmodeling of SEPIC ConverterDocument4 pagesSmall-Signalmodeling of SEPIC ConverterraviNo ratings yet

- ETI 1978-09 SeptemberDocument139 pagesETI 1978-09 SeptemberCarlos SoaresNo ratings yet

- Lab Report Cell Phone EnergyDocument7 pagesLab Report Cell Phone EnergysmurfyblueberryNo ratings yet