Professional Documents

Culture Documents

Ds 1867-100 315612 - 1 PDF

Uploaded by

Osman KoçakOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ds 1867-100 315612 - 1 PDF

Uploaded by

Osman KoçakCopyright:

Available Formats

DS1867 Dual Digital Potentiometer with EEPROM

www.dalsemi.com

FEATURES

Nonvolatile version of the popular DS1267 Low power consumption, quiet, pumpless design Operates from single 5V or 5V supplies Two digitally controlled, 256-position potentiometers Wiper position is maintained in the absence of power Serial port provides means for setting and reading both potentiometers Resistors can be connected in series to provide increased total resistance 16-pin SOIC and 20-pin TSSOP for surface mount applications Standard resistance values: - DS1867-10 ~ 10 k - DS1867-50 ~ 50 k - DS1867-100 ~ 100 k Operating Temperature Range: - Industrial: -40 C to +85 C

PIN ASSIGNMENT

VB H1 L1 W1 RST CLK GND 1 2 3 4 5 6 7 14 13 12 11 10 9 8 VCC SOUT WO HO LO COUT DQ

14-Pin DIP (300-mil) See Mech. Drawings Section

VB NC H1 L1 W1 RST CLK GND

1 2 3 4 5 6 7 8

16 15 14 13 12 11 10 9

VCC NC SOUT WO HO LO COUT DQ

PIN DESCRIPTION

L0, L1 H0, H1 W1, W2 VB SOUT

RST

16-Pin SOIC (300-mil)

DQ CLK COUT VCC GND NC DNC

Low End of Resistor High End of Resistor Wiper End of Resistor Substrate Bias Wiper for Stacked Configuration Serial Port Reset Input Serial Port Data Input Serial Port Clock Input Cascade Serial Port Output +5-Volt Supply Input Ground No Internal Connection Do Not Connect

See Mech. Drawings Section VB

NC H1 L1 W1 RST CLK DNC DNC GND

1

2 3 4 5 6 7 8 9 10

20 19 18 17 16 15 14 13 12 11

VCC DNC DNC SOUT WO HO LO COUT DNC DQ

20-Pin TSSOP (173-mil)

See Mech. Drawings Section

1 of 14

102199

DS1867

DESCRIPTION

The DS1867 Dual Digital Potentiometer with EEPROM is the nonvolatile version of the popular DS1267 Dual Digital Potentiometer. The DS1867 consists of two digitally controlled potentiometers having 256position wiper settings. Wiper position is maintained in the absence of power through the use of EEPROM memory cell arrays. Communication and control of the device are accomplished over a 3-wire serial port which allows reads and writes of the wiper position. Both potentiometers can be stacked for increased total resistance with the same resolution. For multiple-device, single-processor environments, the DS1867 can be cascaded for control over a single 3-wire bus. The DS1867 is offered in three standard resistance values.

OPERATION

The DS1867 contains two 256-position potentiometers whose wiper positions are set by an 8-bit value. These two 8-bit values are written to a 17-bit I/O shift register which is used to store wiper position and the stack select bit when the device is powered. An additional memory area, the shadow memory, stores the 17-bit I/O shift register during a power-down sequence which provides for wiper nonvolatility. A block diagram of the DS1867 is presented in Figure 1. Communication and control of the DS1867 is accomplished through a 3-wire serial port interface that drives an internal control logic unit. The 3-wire serial interface consists of the three input signals: RST , CLK, and DQ. The RST control signal is used to enable 3-wire serial port operation of the device. The RST signal is an active high input and is required to begin any communication to the DS1867. The CLK signal input is used to provide timing synchronization for data input and output. The DQ signal line is used to transmit potentiometer wiper settings and the stack select bit configuration to the 17-bit I/O shift register of the DS1867. Figure 2(a) presents the 3-wire serial port protocol. As shown, the 3-wire port is inactive when the RST signal input is low. Communication with the DS1867 requires the transition of the RST input from a low state to a high state. Once the 3-wire port has been activated, data is latched into the part on the low to high transition of the CLK signal input. Three-wire serial timing requirements are provided in the timing diagrams of Figure 2(b) and (c). Data written to the DS1867 over the 3-wire serial interface is stored in the 17-bit I/O shift register (see Figure 3). The 17-bit I/O shift register contains both 8-bit potentiometer wiper position values and the stack select bit. The composition of the I/O shift register is presented in Figure 3. Bit 0 of the I/O shift register contains the stack select bit. This bit will be discussed in the section entitled Stacked Configuration. Bits 1 through 8 of the I/O shift register contain the potentiometer-1 wiper position value. Bit 1 will contain the MSB of the wiper setting for potentiometer-1 and bit 8 the LSB for the wiper setting. Bits 9 through 16 of the I/O shift register contain the value of the potentiometer-0 wiper position with the MSB for the wiper position occupying bit 9 and the LSB bit 16.

2 of 14

102199

DS1867

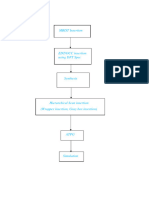

DS1867 BLOCK DIAGRAM Figure 1

3 of 14

102199

DS1867

TIMING DIAGFRAMS Figure 2

(a) 3-Wire Serial Interface General Overview

4 of 14

102199

DS1867

I/O SHIFT REGISTER Figure 3

17-BIT I/O SHIFT REGISTER

Transmission of data always begins with the stack select bit followed by the potentiometer-1 wiper position value and lastly the potentiometer-0 wiper position value (see Figure 2(a)). When wiper position data is to be written to the DS1867, 17-bits (or some integer multiple) of data should always be transmitted. Transactions which do not send a complete 17-bits (or multiple) will leave the register incomplete and possibly an error in desired wiper position. After a communication transaction has been completed the RST signal input should be taken to a low state to prevent any inadvertent changes to the device shift register. Once RST has reached a low state, the contents of the I/O shift register are loaded into the respective multiplexers for setting wiper position. A new wiper position will only engage pending a RST transition to the low state. The wiper position for the high-end terminals H0 and H1 will have data values FF (hex), while the low-end terminals will have data values 00 (hex).

STACKED CONFIGURATION

The potentiometers of the DS1867 can be connected in series as shown in Figure 4. This is referred to as the stacked configuration and allows the user to double the total end-to-end resistance of the part. The resolution of the combined potentiometers will remain the same as a single potentiometer but with a total of 512 wiper positions available. Device resolution is defined as RTOT/256 (per potentiometer); where RTOT is equal to the device resistance value. The wiper output for the combined stacked potentiometer will be taken at the Sout pin, which is the multiplexed output of the wiper of potentiometer-0 (W0) or potentiometer-1 (W1). The potentiometer wiper selected at the Sout output is governed by the setting of the stack select bit (bit-0) of the 17-bit I/O shift register. If the stack select bit has value 0, the multiplexed output, Sout, will be that of the potentiometer-0 wiper. If the stack select bit has value 1, the multiplexed output, Sout, will be that of the potentiometer-1 wiper.

STACKED CONFIGURATION Figure 4

CASCADE OPERATION

A feature of the DS1867 is the ability to control multiple devices from a single processor. Multiple DS1867s can be linked or daisy-chained as shown in Figure 5. As a data bit is entered into the I/O shift register of the DS1867 it will appear at the Cout output after a maximum delay of 70 nanoseconds.

5 of 14

102199

DS1867

The Cout output of the DS1867 can be used to drive the DQ input of another DS1867. When connecting multiple devices, the total number of bits sent is always 17 times the number of DS1867s in the daisy chain. An optional feedback resistor can be placed between the Cout terminal of the last device and the DQ input of the first DS1867, thus allowing the controlling processor to read, as well as, write data or circularly clock data through the daisy chain. The value of the feedback or isolation resistor should be in the range from 2 to 10 kohms. When reading data via the COUT pin and isolation resistor, the DQ line is left floating by the reading device. When RST is driven high, bit 17 is present on the COUT pin, which is fed back to the input DQ pin through the isolation resistor. When the CLK input transitions low to high, bit 17 is loaded into the first position of the I/O shift register and bit 16 becomes present on COUT and DQ of the next device. After 17 bits (or 17 times the number of DS1867s in the daisy chain), the data has shifted completely around and back to its original position. When RST transitions to the low state to end data transfer, the value (the same as before the read occurred) is loaded into the wiper-0, wiper-1, and stack select bit I/O register.

CASCADING MULTIPLE DEVICES Figure 5

NONVOLATILE WIPER SETTINGS

The DS1867 maintains the position of the wiper in the absence of power. This feature is provided through the use of EEPROM type memory cell arrays. During normal operation, the position of the wiper is determined by the device multiplexers and stored in the shadow memory (EEPROM). The manner in which an update occurs has been optimized for reliability, durability, and performance. Additionally, the update operation is totally transparent to the user. When power is applied to the DS1867, wiper settings will be the last recorded in the EEPROM memory cells or shadow memory before the last power-down. Changes to the EEPROM memory cells occur during a predefined power-down sequence. If the DS1867 detects a voltage transition to 4.5 volts or less, on the power supply input, the part initiates an automatic wiper storage sequence. This storage sequence will save in EEPROM memory the contents of the I/O shift register before a total power-shutdown; provided specific power-down timing requirements are met. The minimum total power-down time is specified at 4 milliseconds. Power-down timing requirements on VCC are shown in Figure 6. The EEPROM memory cells are specified to accept greater than 25,000 writes before a wear-out condition. If the EEPROM memory cells do reach a wear-out condition, the DS1867 will still function properly while power is applied. A minimum time of 4 ms between 4.5V and 3V is required to perform the proper position storage of the wiper.

6 of 14

102199

DS1867

POWER-DOWN EEPROM TIMING REQUIREMENTS Figure 6

TYPICAL APPLICATION CONFIGURATIONS

Figures 7 and 8 show two typical application configurations for the DS1867. By connecting the wiper terminal of the part to a high impedance load, the effects of the wiper resistance is minimized, since the wiper resistance can vary from 400 to 1000 ohms depending on wiper voltage. Figure 7 presents the device connected in an inverting variable gain amplifier. The gain of the circuit on Figure 7 is given by the following equation: Av = -n/(255-n); where n = 0 to 255 Figure 8 shows the device operating in a fixed gain attenuator where the potentiometer is used to attenuate an incoming signal. Note the resistance R1 is chosen to be much greater than the wiper resistance to minimize its effect on circuit gain.

INVERTING VARIABLE GAIN AMPLIFIER Figure 7

DS1867

7 of 14

102199

DS1867

FIXED GAIN ATTENUATOR Figure 8

ABSOLUTE AND RELATIVE LINEARITY

Absolute linearity is defined as the difference between the actual measured output voltage and the expected output voltage. Figure 9 presents the test circuit used to measure absolute linearity. Absolute linearity is given in terms of a minimum increment or expected output when the wiper position is moved one position. In the case of the test circuit, a minimum increment (MI) would equal 10/512volts. The equation for absolute linearity is given in equation (1). Eq: (1) Absolute Linearity AL = {Vo(actual)- Vo(expected)}/MI Relative linearity is a measure of error between two adjacent wiper position points and is given in terms of MI by equation (2). Eq: (2) Relative Linearity RL = {Vo(n+1) - Vo(n)}/MI Figure 10 is a plot of absolute linearity and relative linearity versus wiper position for the DS1867 at 25 C. The specification for absolute linearity of the DS1867 is 0.75 MI typical. The specification for relative linearity of the DS1867 is 0.30 MI typical.

LINEARITY MEASUREMENT CONFIGURATION Figure 9

8 of 14

102199

DS1867

9 of 14

102199

DS1867

ABSOLUTE MAXIMUM RATINGS*

Voltage on Any Pin Relative to Ground (VB=GND) Voltage on Resistor Pins when VB=-5.5V Operating Temperature Storage Temperature Soldering Temperature -1.0V to +5.5V -5.5V to +5.5V -40 to +85C -55C to +125C 260C for 10 seconds

* This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

RECOMMENDED DC OPERATING CONDITIONS

PARAMETER Supply Voltage Input Logic 1 Input Logic 0 Substrate Bias Resistor Inputs SYMBOL VCC VIH VIL VB L,H,W MIN 4.5 2.0 -0.5 -5.5 VB TYP MAX 5.5 VCC+0.5 +0.8 GND VCC+0.5

(-40 C to +85 C)

UNITS V V V V V 2 1 1 NOTES

DC ELECTRICAL CHARACTERISTICS

PARAMETER Supply Current Input Leakage Wiper Resistance Wiper Current Logic 1 Output @2.4Volts Logic 0 Output @0.4Volts Standby Current Power-Down Time Power Trip Point Recovery Time tREC SYMBOL ICC ILI RW IW IOH IOL ISTBY tPU tPU1 4 2.5 3.9 2 -1.0 4 -1 MIN

(-40 C to +85 C; VCC=5V 10%)

TYP 250 MAX 900 +1 400 1000 1 UNITS A A mA mA mA 250 A ms ms 4.2 5 4.5 10 V ms 11,14 9 10 8 8 NOTES

10 of 14

102199

DS1867

ANALOG RESISTOR CHARACTERISTICS

PARAMETER End-to-End Resistor Tolerance Absolute Linearity Relative Linearity -3 dB Cutoff Frequency Noise Figure Temperature Coefficient fCUTOFF SYMBOL MIN -20

(-40 C to +85 C;VCC= 5V 10%)

TYP MAX +20 0.75 0.30 UNITS % LSB LSB Hz 120 750 dB/(Hz)1/2 ppm/ C NOTES 17 4 5 7

CAPACITANCE

PARAMETER Input Capacitance Output Capacitance SYMBOL CIN COUT MIN TYP MAX 5 7 pF pF

(TA = 25 C)

UNITS NOTES 3 3

AC ELECTRICAL CHARACTERISTICS

PARAMETER CLK Frequency Width of CLK Pulse Data Setup Time Data Hold Time Propagation Delay Time Low to High Level Clock to Output Propagation Delay Time High to Low Level Clock to Output

RST High to Clock Input High RST Low to Clock Input High

(-40 C to +85 C; VCC= 5V 10%)

TYP MAX 10 UNITS MHz ns ns ns 70 ns NOTES 15 15 15 15 13,15

SYMBOL fCLK tCH tDC tCDH tPLH

MIN DC 50 30 10

tPHL

70

ns

13,15

tCC tHLT tCR tRLT

50 50 50 200

ns ns ns ns

15 15 15 15

CLK Rise Time

RST Inactive

NONVOLATILE MEMORY CHARACTERISTICS (-40 C to +85 C; VCC= 5V 10%)

PARAMETER Writes SYMBOL MIN 25000 11 of 14 TYP MAX UNITS NOTES 16 102199

DS1867

NOTES:

1. All voltages are referenced to ground. 2. Resistor inputs cannot exceed the substrate bias voltage, VB, in the negative direction. 3. Capacitance values apply at 25 C. 4. Absolute linearity is used to determine wiper voltage versus expected voltage as determined by wiper position. Test limits for absolute linearity are 1.6 LSB. 5. Relative linearity is used to determine the change in voltage between successive tap positions. Test limits for relative linearity are 0.5 LSB. 6. Typical values are for tA =25 C and nominal supply voltage. 7. -3 dB cutoff frequency characteristics for the DS1867 depend on potentiometer total resistance: DS1867-010; 1 MHz, DS1867-050; 200 kHz, DS1867-100; 100 kHz. 8. COUT is active regardless of the state of RST . 9. Power-down time is specified at a minimum of 4 ms. It is the time required for the DS1867 to guarantee wiper position storage as VCC moves from 4.5V to 3.0V. 10. This is the time from power trip-point min (3.9V) to 3.0V to guarantee wiper storage. 11. tREC is the time required before the DS1867 stored wiper position becomes valid on power-up. 12. Power trip points reference required voltage necessary for DS1867 to restore the stored wiper position setting. 13. See Figure 11. 14. During power-up the wiper position will be set at 80H. 15. See Figure 2. 16. A device write is specified as being a controlled power-down providing enough time to complete an EEPROM write. It is also defined as a complete bit change from one value to another, i.e., 0 to 1. Power-downs which do not change the wiper value can be expected have 200,000-write durability. 17. Valid at 25 C only.

12 of 14

102199

DS1867

ABSOLUTE AND RELATIVE LINEARITY Figure 10

Absolute and Relative Linearity (Normalized to 1 LSB)

DIGITAL OUTPUT LOAD SCHEMATIC Figure 11

13 of 14

102199

DS1867

TYPICAL SUPPLY CURRENT VS. SERIAL CLOCK RATE Figure 12

Serial Clock Rate (bits/second)

14 of 14

102199

This datasheet has been downloaded from: www.DatasheetCatalog.com Datasheets for electronic components.

You might also like

- Arduino Section ProgrammingDocument54 pagesArduino Section ProgrammingJohn LeungNo ratings yet

- Arduino Booklet PDFDocument45 pagesArduino Booklet PDFgpt1708No ratings yet

- Arduino ProjectsDocument373 pagesArduino ProjectsErshad Shafi Ahmed94% (33)

- Arduino Start Kit User ManualDocument32 pagesArduino Start Kit User Manualdantesosa100% (4)

- Control A 5V Motor With The ArduinoDocument3 pagesControl A 5V Motor With The Arduinosher123No ratings yet

- Learn Arduino Manual 3Document31 pagesLearn Arduino Manual 3cris_itdNo ratings yet

- Drive A 7 Segment LED With An ArduinoDocument5 pagesDrive A 7 Segment LED With An Arduinosher123No ratings yet

- XBee 2.5 DatasheetDocument2 pagesXBee 2.5 DatasheetYerson CrespoNo ratings yet

- Arduino in A Nutshell 1.8Document20 pagesArduino in A Nutshell 1.8hemu07121990No ratings yet

- Motor Driver Shield ManualDocument7 pagesMotor Driver Shield ManualShiela Monique Fajardo100% (2)

- Ravor ManualDocument8 pagesRavor ManualZabri ZakariaNo ratings yet

- Arduino Basics PIR SensorDocument7 pagesArduino Basics PIR SensorswoneraNo ratings yet

- Arduino Audio InputDocument16 pagesArduino Audio InputswoneraNo ratings yet

- ArduinoDocument156 pagesArduinoMike Gomez91% (23)

- Arduino Ethernet Shield TutorialDocument8 pagesArduino Ethernet Shield TutorialJose Jose Andres100% (5)

- Bionic Arduino Class4Document50 pagesBionic Arduino Class4ybouriniNo ratings yet

- Arduino Controlled Hexbug SpiderDocument4 pagesArduino Controlled Hexbug SpiderswoneraNo ratings yet

- Arduino BasicsDocument50 pagesArduino BasicsSsj Kakarott86% (7)

- Hacking Internet With ArduinoDocument15 pagesHacking Internet With ArduinoYo Gain DrawNo ratings yet

- Arduino ProjectsDocument46 pagesArduino Projectstecnojorge100% (7)

- Arduino Fungsi SyntaxDocument36 pagesArduino Fungsi Syntaxmul21No ratings yet

- Arduino TutorialDocument131 pagesArduino TutorialgoblinmarineNo ratings yet

- Simulator For ArduinoDocument26 pagesSimulator For ArduinoNinok Rizky AmaliaNo ratings yet

- ArduinoDocument156 pagesArduinoMike Gomez91% (23)

- Arduino ProjectsDocument46 pagesArduino Projectstecnojorge100% (7)

- GRARA Meets ArduinoDocument49 pagesGRARA Meets ArduinoSujeet Kumar Mishra100% (1)

- ArduinoDocument40 pagesArduinovicalog100% (6)

- 20 Unbelievable Arduino ProjectsDocument430 pages20 Unbelievable Arduino ProjectsCao Anh100% (10)

- Arduino Experimenters GuideDocument32 pagesArduino Experimenters Guiderudyzarzoff100% (1)

- ArduinoDocument7 pagesArduinoManik JainNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Module 5-Ktunotes - In-MinDocument55 pagesModule 5-Ktunotes - In-MinVishnu CKNo ratings yet

- Experiment 6 FinalDocument6 pagesExperiment 6 Finalliddleme33No ratings yet

- Cao-Notess by Girdhar Gopal Gautam 3gDocument130 pagesCao-Notess by Girdhar Gopal Gautam 3gGirdhar Gopal GautamNo ratings yet

- DM74LS164 8-Bit Serial In/Parallel Out Shift Register: General Description FeaturesDocument5 pagesDM74LS164 8-Bit Serial In/Parallel Out Shift Register: General Description FeaturesRoby Adi WibowoNo ratings yet

- Examen Module Complémentaire Labview: Exercise 1 (7 PTS)Document13 pagesExamen Module Complémentaire Labview: Exercise 1 (7 PTS)Màriem Làkhal Ep KàboubiNo ratings yet

- PC ElementsDocument450 pagesPC ElementssamiNo ratings yet

- FIFO Depth Calculation ?Document1 pageFIFO Depth Calculation ?AbhNo ratings yet

- Counters and RegistersDocument15 pagesCounters and RegistersReal ManNo ratings yet

- Linear and Digital Integrated Circuits-Lab ManualDocument96 pagesLinear and Digital Integrated Circuits-Lab ManualPrabu KumarNo ratings yet

- MBI5024 Datasheet VA 02-EnDocument18 pagesMBI5024 Datasheet VA 02-Enf1lealNo ratings yet

- Kreatryx Digital Circuits PDFDocument48 pagesKreatryx Digital Circuits PDFshubhamNo ratings yet

- Design Verification and Test of Digital VLSI Circuits NPTEL Video CourseDocument63 pagesDesign Verification and Test of Digital VLSI Circuits NPTEL Video CourseKhushboo Shrish DixitNo ratings yet

- CD4015BM/CD4015BC Dual 4-Bit Static Shift Register DatasheetDocument7 pagesCD4015BM/CD4015BC Dual 4-Bit Static Shift Register DatasheetLucilia Dos SantosNo ratings yet

- 171 CatalogDocument156 pages171 Catalogchente_b100% (1)

- EE6311-Linear and Digital Integrated Circuits LaboratoryDocument97 pagesEE6311-Linear and Digital Integrated Circuits LaboratoryGNo ratings yet

- Debouncing MC14490Document13 pagesDebouncing MC14490Chany ChapnikNo ratings yet

- CPSC 121: Models of Computation Lab #5: Flip-Flops and Frequency DivisionDocument8 pagesCPSC 121: Models of Computation Lab #5: Flip-Flops and Frequency DivisionJason RichardsNo ratings yet

- Improvement of The Orthogonal Code Convolution Capabilities Using Fpga ImplementationDocument50 pagesImprovement of The Orthogonal Code Convolution Capabilities Using Fpga Implementationscribdashokram100% (2)

- Data Sheets TTL Logic Family ComponentsDocument44 pagesData Sheets TTL Logic Family ComponentsTales VitorNo ratings yet

- DFT DocumentationDocument20 pagesDFT Documentationyamini100% (1)

- MAX7219/MAX7221 Serially Interfaced, 8-Digit LED Display DriversDocument15 pagesMAX7219/MAX7221 Serially Interfaced, 8-Digit LED Display DriversAlfredo Meurer JuniorNo ratings yet

- Lab Manual EC0323 Communication Lab-II LabDocument105 pagesLab Manual EC0323 Communication Lab-II LabSivasakthiNo ratings yet

- Digital System Design Based On Data Path and Control UnitDocument52 pagesDigital System Design Based On Data Path and Control UnitHemant Tulsani33% (3)

- ST7529 v1.8Document86 pagesST7529 v1.8matti4No ratings yet

- Digital LabDocument51 pagesDigital LabBala SubramanianNo ratings yet

- MC14014B, MC14021B 8 Bit Static Shift Register: Marking DiagramsDocument8 pagesMC14014B, MC14021B 8 Bit Static Shift Register: Marking Diagramsdaniel ortegaNo ratings yet

- VHDL Code For Serial in Serial Out Shift Register Using Behavioral ModellingDocument3 pagesVHDL Code For Serial in Serial Out Shift Register Using Behavioral Modellingmeaow8886% (7)

- Final Design Report - Steven MotesDocument6 pagesFinal Design Report - Steven Motessteven_motesNo ratings yet

- Uart Using Fpga P1 (1) (2) - 1Document22 pagesUart Using Fpga P1 (1) (2) - 1Naveen KothaNo ratings yet

- OVM Verification of Quad SPIDocument91 pagesOVM Verification of Quad SPIkienukiruNo ratings yet