Professional Documents

Culture Documents

Technologie Des Circuits Integres

Uploaded by

mcraam1985Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Technologie Des Circuits Integres

Uploaded by

mcraam1985Copyright:

Available Formats

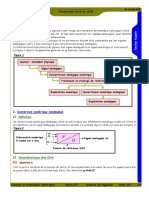

TECHNOLOGIE DES CIRCUITS INTEGRES TTL - CMOS

1.1

Dfinition de circuit intgr :

Un circuit intgr dsigne un bloc constitu par un monocristal de silicium ( Puce ) de quelques millimtres carrs lintrieur duquel se trouve inscrit en nombre variable des composants lectroniques lmentaires ( Transistors, diodes, rsistances, condensateurs, ... ).

1.2 Dfinition de classes dintgration :

Dans lordre chronologique, on distingue 4 classe dintgration : *0 Les microcircuits SSI ( Single Size Intgration ) : 100 transistors par cm2. *1 Les circuits intgrs MSI ( Mdium Size Intgration ) : 1000 transistors par cm2. *2 Les circuits LSI ( Large Size Intgration ) : 10000 100000 transistors par cm2. *3 Les circuits VLSI ( Very Large Size Intgration ) : 0.1 1 million transistors par cm2.

M HISETTE

1.3

Notion de niveaux logiques :

Pour une famille donne, les niveaux logiques 0 et 1 ne correspondent pas une tension prcise, mais une certaine plage de tension. On appellera pour les valeurs de tension en entre ( Input ): *4 VIHmin : Tension minimale en entre qui assure le niveau logique haut. *5 VILmax : Tension maximale en entre qui assure le niveau logique bas.

Vcc VIHmin

Caractristique dentre

( Etat indfini )

VILmax

On appellera pour les valeurs de tension en sortie ( Output ): *6 VOHmin : Tension minimale de sortie ltat logique haut. *7 V0Lmax : Tension maximale de sortie ltat logique bas.

Vcc

Caractristique de sortie

VOHmin

( Etat indfini )

VOLmax 0

1.4 Compatibilit des niveaux logiques . Vcc VOHmin

VOHmin - VIHmin

Vcc VIHmin

( Etat indfini )

VILmax - VOLmax

( Etat indfini )

VOLmax 0

*8 *9

0

Niveaux de sortie circuit 1

VILmax 0

Niveaux dentre circuit 2

Compatibilit au niveau haut : Il faut que VOHmin > VIHmin Compatibilit au niveau bas : Il faut que VILmax > VOlmax

M HISETTE

1.5 Temps moyen de propagation.

Lorsquon applique lentre dun circuit un niveau logique, il y a un certain retard pour que la sortie ragisse. Cette dure est le temps moyen de propagation t PD.

S

50%

tPHL Entre

tPLH Sortie

*10 tPHL: Temps de propagation du niveau haut au niveau bas. *11 tPLH: Temps de propagation du niveau bas au niveau haut. tPD = (tPHL + tPLH ) / 2

Remarque : Ce temps dtermine la frquence maximale FMAX laquelle les circuits intgrs sont capables de ragir.

1.6 Facteur de charge : Sortance N.

Ce paramtre caractrise le nombre N maximal dentres de portes logiques pouvant tre commandes par la sortie dun autre oprateur logique de la mme famille.

IO

II II II

X X X

IOH : Courant de sortie maximal ltat haut IOL : Courant de sortie maximal ltat bas IIH : Courant dentre maximal ltat haut IIL : Courant dentre maximal ltat bas

*12 Sortance N ( A ltat haut ) = IOH / IIH *13 Sortance N ( A ltat bas ) = IOL / IIL

Remarque : La documentation constructeur fournie les donnes suivantes : IOH, IIH, IOL, IIL.

1.7 Notion de familles de circuits logiques :

Il existe plusieurs familles de circuits technologiques. Les 2 plus utilises sont : *14 TTL ( Transistors Transistors Logic )

*15

CMOS (transistors effet de champ MOS - Complmentaire - Mtal - Oxyde - Semiconducteur - )

M HISETTE

PORTES LOGIQUES TTL

Plusieurs technologies : TTL standard (n est plus utilise) TTL Low Power TTL Schottky (Rapide) TTL Low Power Schottky TTL Advanced Schottky TTL Advanced Low Power Schottky Caractristiques de fonctionnement :

Gamme dalimentation : 5 V +/- 5%.

Transistor Transistor Logique

Fiche de rfrence N7

Niveaux Logiques d une porte logique TTL (LS) SORTIE 74 00 74 L 00 74 S 00 74 LS 00 74 AS 00 74 ALS00 VO

VCC Niveau 1 VOH mini Niveau indtermin VOL maxi VIL maxi Niveau 0 0V 0,5 V Niveau 0 0V 2,7 V VIH mini Niveau indtermin 0,7 V 5V VCC Niveau 1 2V

ENTREE VI

5V

Gamme de temprature : de 0 C + 70 C. Puissance dissipe : environ 2 mW par porte (srie LS). Frquence de fonctionnement : jusqu 3 MHz. Sortance : jusqu 20 (srie LS).

(Nombre dentres que lon peut relier une sortie de porte)

Sortie collecteur ouvert (Open collector output)

On sort directement sur le collecteur du transistor de sortie. Obligation de connecter une rsistance R de tirage au +5 V. Pour un calcul rigoureux de R, se reporter la page 43 du Memotech

Symbole

VO

To

La sortie est quivalente un interrupteur.

VO

Faible immunit aux bruits. Caractristique d Entre/Sortie dun inverseur VO

VCC VOH

Sortie 3 tats (3-state output)

+5V

Symbole

74 LS 00 VI

&

VO

T1

VO

Dans une porte classique, l un des 2 transistors T1 ou T2 du totem ple est conducteur. Dans une porte 3 tats, il est possible de bloquer simultanment les 2 transistors T1 et T2 par l entre de validation EN (EN = 0). On dispose alors de 3 tats en sortie:

EN 1 1 0 T1 Passant Bloqu Bloqu T2 Bloqu Passant Bloqu Etat Haut Bas Haute impdance (Sortie en l air ).

VOL

T2

VIL VIH

VCC

VI

M HISETTE

PORTES LOGIQUES CMOS

Plusieurs technologies : Srie 4000 : 40 00 B (sorties buffrises : amplifies) 40 00 UB (sorties non-buffrises) Srie 74 : 74 C 00 (identique la srie 4000) 74 HC 00 (High-speed CMOS : CMOS rapides) Caractristiques de fonctionnement :

Gamme dalimentation : de 3 V 15 V. Gamme de temprature : de 40 C + 85 C. Puissance dissipe : environ 10 nW par porte. Frquence de fonctionnement : jusqu 12 MHz.

RS IOL IIN

Fiche de rfrence

Modlisation de lentre et de la sortie dune porte logique CMOS

SORTIE

Rs IOH

ENTREE

IIN CG

VDD

VOH

VIH

RG

Etat logique 1

Etat logique 1

CG VOL VIL RG

Sortance :

jusqu 50 (srie 4000B).

(Nombre dentres que lon peut relier une sortie de porte)

Excellente immunit aux bruits.

Caractristique d Entre/Sortie dun inverseur VO

VDD

Etat logique 0 GRANDEURS CARACTERISTIQUES : RS = environ 300 RG = plusieurs M CG = environ 50 pF VOH : VOL : VIH : VIL : IOH : IOL : IIN :

Etat logique 0 Tension de sortie l tat haut. Tension de sortie l tat bas. Tension d entre l tat haut. Tension d entre l tat bas. Courant de sortie l tat haut. Courant de sortie l tat bas. Courant d entre. 5

VI

1

VI

VO

VDD / 2

VDD

M HISETTE

You might also like

- Chapitre 07 - Les Semiconducteurs de Puissance, Le MOSFETDocument42 pagesChapitre 07 - Les Semiconducteurs de Puissance, Le MOSFETSteve Alain Onana DangNo ratings yet

- Bode PDFDocument10 pagesBode PDFYoussefSaroukhNo ratings yet

- Poly Aop123Document48 pagesPoly Aop123ELmokhtar HamrouniNo ratings yet

- Annexe4 MultiplieurDocument8 pagesAnnexe4 MultiplieurAla Eddine LarGatNo ratings yet

- Exercices DDocument2 pagesExercices DsekNo ratings yet

- ConversionDocument8 pagesConversionsaidNo ratings yet

- Traitement Du Signal Examen SC 12 PDFDocument2 pagesTraitement Du Signal Examen SC 12 PDFMohamed Aly SowNo ratings yet

- BasculeDocument8 pagesBasculeElecfort AlgerNo ratings yet

- DéfinitionDocument5 pagesDéfinitionAicha B'mh100% (1)

- Modéle de RedactionDocument31 pagesModéle de RedactionBöuäbdälläh AïmenNo ratings yet

- Chapitre 4 - 2008 1 PDFDocument38 pagesChapitre 4 - 2008 1 PDFoussema zmerliNo ratings yet

- ds1 2122 CorrectionDocument9 pagesds1 2122 CorrectionSana AkherrazNo ratings yet

- Amplificateur de Puissance Classe B, ABDocument7 pagesAmplificateur de Puissance Classe B, ABKhaira ToulaNo ratings yet

- Serie3 2020 Enoncé-1Document4 pagesSerie3 2020 Enoncé-1Ayoub EddamenNo ratings yet

- BTS SE EQ Corrigé Principal 2017Document8 pagesBTS SE EQ Corrigé Principal 2017Ayman LamzouriNo ratings yet

- TD4 LMDDocument2 pagesTD4 LMDbigNo ratings yet

- TD 1GEL Transistor LineaireDocument1 pageTD 1GEL Transistor LineaireAllegro Presto ModeratoNo ratings yet

- TP 5 Realisation Modulation FM À VaricapDocument3 pagesTP 5 Realisation Modulation FM À VaricapYves AbrahamNo ratings yet

- Ampli ACCORDEDocument10 pagesAmpli ACCORDEMaria MEKLI100% (1)

- Cours VHDL 2Document45 pagesCours VHDL 2Zine Elabidine MoslihNo ratings yet

- Chapitre 8 Convertisseur Adc DacDocument9 pagesChapitre 8 Convertisseur Adc DacMedNo ratings yet

- Le Microprocesseur 8086Document22 pagesLe Microprocesseur 8086Merbai YassineNo ratings yet

- Compte Rendu TP Numéro 2 Communication NumériqueDocument29 pagesCompte Rendu TP Numéro 2 Communication NumériqueTakfarinas MezioudNo ratings yet

- Demi PontDocument9 pagesDemi PontOlivier OuinaNo ratings yet

- Série Dexercices 1 Matrice de RépartitionDocument1 pageSérie Dexercices 1 Matrice de RépartitionLou Loulou0% (1)

- Cours CIs - 2012Document174 pagesCours CIs - 2012Ayman OubghachiNo ratings yet

- EC GIM324 - Electronique Analogique Et NumériqueDocument57 pagesEC GIM324 - Electronique Analogique Et NumériqueArmand EssNo ratings yet

- Cours Antennes Outils Modeles Transmission Oct14 v3Document156 pagesCours Antennes Outils Modeles Transmission Oct14 v3Oumar KOITANo ratings yet

- Intro Codage Source Et Codage de Canal PDFDocument145 pagesIntro Codage Source Et Codage de Canal PDFAli KHALFA100% (1)

- Serie TD6Document7 pagesSerie TD6Sarah NourNo ratings yet

- Rapport Brohage Des AOPDocument5 pagesRapport Brohage Des AOPAli Moustapha NourNo ratings yet

- Poste S 63 Version 1Document15 pagesPoste S 63 Version 1tonye joelNo ratings yet

- GEL-3006 2016 09 Numerique PDFDocument92 pagesGEL-3006 2016 09 Numerique PDFYolandeMengueNo ratings yet

- TEC 588 - TP4 - Etude D'un Générateur de SignauxDocument5 pagesTEC 588 - TP4 - Etude D'un Générateur de SignauxJugurthaHadjar100% (1)

- Cours DSP 2020-Programmation - 43Document44 pagesCours DSP 2020-Programmation - 43Youssef Mahdi0% (1)

- Cours 1 CmosDocument38 pagesCours 1 CmosMed LabbiNo ratings yet

- Se1 TD PDFDocument24 pagesSe1 TD PDFAnonymous DDmaOcxKb100% (1)

- TEL602Document1 pageTEL602badreddineNo ratings yet

- Support de Cours FH EtudiantDocument136 pagesSupport de Cours FH EtudiantbilllNo ratings yet

- Exercices - Chapitre 4Document19 pagesExercices - Chapitre 4Yessine BouhamedNo ratings yet

- Transistor A Effet de ChampsDocument2 pagesTransistor A Effet de ChampsYassine El BouazzaouiNo ratings yet

- Chapitre 6 - Modulation NumériqueDocument12 pagesChapitre 6 - Modulation NumériqueEmmanuel AlbertNo ratings yet

- Exposé PFE NaderDocument11 pagesExposé PFE NaderChaima BelhediNo ratings yet

- HfsyscdkvhdvdDocument5 pagesHfsyscdkvhdvdHã PpÿNo ratings yet

- TP Can CnaDocument8 pagesTP Can CnaEdward Adounvo100% (1)

- Chapitre 1 Electronique de CommandeDocument6 pagesChapitre 1 Electronique de CommandeFth WalterNo ratings yet

- KévinDocument49 pagesKévinJosué NdamNo ratings yet

- 1 TP Numerisation Signal Analogique-2 PDFDocument4 pages1 TP Numerisation Signal Analogique-2 PDFAnonymous jbjqt9LhtINo ratings yet

- Chapitre 1 DispositifsDocument54 pagesChapitre 1 DispositifsAbdou SuperNo ratings yet

- 2cellules MOSDocument31 pages2cellules MOSaammiinneeNo ratings yet

- Cours Signaux Chapitre 4 ETUDIANTSDocument30 pagesCours Signaux Chapitre 4 ETUDIANTScharle2251100% (1)

- Theme: Rapport de TP 2 ElectroniqueDocument11 pagesTheme: Rapport de TP 2 ElectroniqueDarckson KoulibalyNo ratings yet

- 3 Cours Microprocesseur 16 BitsDocument15 pages3 Cours Microprocesseur 16 BitsSeghiour AbdellatifNo ratings yet

- Guide de Démarrage - Stm32Cubeide Carte Extension 746Ng Ens: Anthony Juton, Pascal Varoqui - Février 2023Document21 pagesGuide de Démarrage - Stm32Cubeide Carte Extension 746Ng Ens: Anthony Juton, Pascal Varoqui - Février 2023Anthony Juton100% (1)

- Fonctionnement de La PLLDocument9 pagesFonctionnement de La PLLLahouari FatahNo ratings yet

- 1 Code AMI (Alternate Mark Inversion) Ou NRZ BipolaireDocument1 page1 Code AMI (Alternate Mark Inversion) Ou NRZ BipolaireFarah AlameddineNo ratings yet

- Twistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesFrom EverandTwistronics: Le saint graal de la physique, des matériaux quantiques et des nanotechnologiesNo ratings yet

- Chapitre 5 Technologie Des Circuits Logiques IntegresDocument46 pagesChapitre 5 Technologie Des Circuits Logiques IntegresPUBG Mido DZ100% (1)

- Chap. 1 TTL CMOSDocument15 pagesChap. 1 TTL CMOSGhazi DayehNo ratings yet

- Chapitre4 - La Famille TTLDocument47 pagesChapitre4 - La Famille TTLKillua ZoldekNo ratings yet

- Correction 02Document2 pagesCorrection 02mcraam1985No ratings yet

- Numérique Partie1 CombiDocument176 pagesNumérique Partie1 Combimcraam1985100% (1)

- Correction 02Document2 pagesCorrection 02mcraam1985No ratings yet

- TD Exo Algebre BooleDocument23 pagesTD Exo Algebre Booledxsszsz100% (2)

- CO Operations BinairesDocument5 pagesCO Operations Binairesmcraam1985No ratings yet

- Unghi Dilatanta Din Forfecare in Aparat TriaxialDocument4 pagesUnghi Dilatanta Din Forfecare in Aparat TriaxialAndor-Csongor NagyNo ratings yet

- Ag LagrangeDocument1 pageAg LagrangeSoufiane BouchlaghemNo ratings yet

- D.S 1 3M 14 15Document2 pagesD.S 1 3M 14 15Hayk ElNo ratings yet

- Examen Sujet7 PDFDocument4 pagesExamen Sujet7 PDFHeraiz RachidNo ratings yet

- Probabilité Exercices-CorrigesDocument33 pagesProbabilité Exercices-CorrigesosefresistanceNo ratings yet

- Modèle RicardoDocument11 pagesModèle RicardozinebencgistNo ratings yet

- Dc1 4tech2Document2 pagesDc1 4tech2Omar MakhNo ratings yet

- Commande Non-Linéaire de La MADADocument192 pagesCommande Non-Linéaire de La MADAMoulay1No ratings yet

- Corrige TD 5Document6 pagesCorrige TD 5mourad100% (1)

- Note de Calcul RadierDocument15 pagesNote de Calcul RadierNZOMO91% (23)

- Ad2 CONFORTpentexemplesDocument22 pagesAd2 CONFORTpentexemplesYounes BingaNo ratings yet

- Guide Chargement CamionsDocument20 pagesGuide Chargement CamionsAnas El AkramiNo ratings yet

- RPA Methode StatiqueDocument21 pagesRPA Methode StatiqueAbdelhakim BelaidNo ratings yet

- 03.conception Structure PorteuseDocument54 pages03.conception Structure PorteuseFares Chammam0% (1)

- Règles CM66 Et Additif 80Document392 pagesRègles CM66 Et Additif 80AyoubThunder100% (7)

- Equation D - Une DroiteDocument4 pagesEquation D - Une DroiteRachid BerjaguaNo ratings yet

- Technologie Et Principes de La Régulation BTSDocument8 pagesTechnologie Et Principes de La Régulation BTSkamradscorpionNo ratings yet

- 1811-Leçons Élémenaitres de Mathématiques-l'Abbé de La CailleDocument546 pages1811-Leçons Élémenaitres de Mathématiques-l'Abbé de La Caillemartin160464No ratings yet

- Entraînements Réglés HEIG - Ex - Et - Corr - CompletDocument75 pagesEntraînements Réglés HEIG - Ex - Et - Corr - ComplettoulouiNo ratings yet

- Équations (4ème)Document3 pagesÉquations (4ème)MATHS - VIDEOS100% (1)

- La Difference de Potentiel TD CompletDocument4 pagesLa Difference de Potentiel TD CompletKhaoula SamaaliNo ratings yet

- Exercice 01:: P Q PQ P P PDocument4 pagesExercice 01:: P Q PQ P P PAbderrazzak ElhaimerNo ratings yet

- Facades Verrieres Avis Technique Structura Duo 2-07-1231Document22 pagesFacades Verrieres Avis Technique Structura Duo 2-07-1231akreitNo ratings yet

- 2008 National Exo1 Correction BBT 6 5ptsDocument2 pages2008 National Exo1 Correction BBT 6 5ptsla physique selon le programme FrançaisNo ratings yet

- Abdelmeziane NabilDocument176 pagesAbdelmeziane NabildanemsalNo ratings yet

- 2018 Grok Lighting EN ES FR PDFDocument337 pages2018 Grok Lighting EN ES FR PDFNakhayo JumaNo ratings yet

- TP Diffraction Des Rayons XDocument16 pagesTP Diffraction Des Rayons XNoura Zhd100% (1)

- Dynamique Des Rotors en Torsion-IntroductionDocument2 pagesDynamique Des Rotors en Torsion-IntroductionMed RjebNo ratings yet

- 06 Noces (Camus)Document14 pages06 Noces (Camus)RafaelSilvaNo ratings yet