Professional Documents

Culture Documents

Oscillators PDF

Uploaded by

Biswajit BeheraOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Oscillators PDF

Uploaded by

Biswajit BeheraCopyright:

Available Formats

Oscillators

1. Introduction

What makes an oscillator?

2. Types of oscillators

Fixed frequency or voltage controlled oscillator

LC resonator

Ring Oscillator

Crystal resonator

Relaxation/Multivibrator/RC oscillators

3. Design of oscillators

Frequency control, stability

Amplitude limits

Buffered output isolation

Bias circuits

Voltage control

Phase noise

PDFaid.Com

#1 Pdf Solutions

Oscillator Basics

A feedback amplifier: with positive feedback. Gain with feedback is

1

o

F

S

X a

a

af X

= =

What conditions are needed for oscillation?

| | 1 0 af af = =

This is called theBarkhausen criterion.

Of: If the oscillation is to be sustained with Xs =0, no input, then

o F o

F o

X aX afX

X fX

= =

=

Amplitude is controlled by the magnitude |af|

Frequency is controlled by the phase of af.

f

X

S

X

O

X

F

a

f

X

S

X

O

X

F

a

Typically, the feedback block is frequency dependent a resonator or filter or phase shift

network.

Considering a resonant circuit like a parallel RLC, the phase slope

d

d

will set the frequency.

You can see that a change in phase d will result in a change in frequency d.

A large phase slope produces less frequency variation for a given d.

What would cause a d?

A second way to study the operation of oscillators is to evaluate the characteristic

equation: the roots of which are the circuit poles.

1 ( ) ( ) 0 a s f s =

For sustained oscillations at

o

, we need roots on the j axis at s =+/- j

o

. This would

be the case with a factor (s

2

+

o

2

).

The inverse Laplace transform gives the solution: sin( ) cos( )

o o

t or t

An undamped sinusoid.

j

j

o

x

x -j

o

j

j

o

x

x -j

o

LC Oscillators

Utilize an LC tank circuit as a resonator to control frequency.

High Q resonator provides good stability, low phase noise

The frequency can be adjusted by voltage if desired, by using varactor diodes in

the resonator.

For oscillation to begin, open loop gain A 1 and A =0.

Circuit #1:

Consider this tuned amplifier:

Load: The impedance of the resonator peaks (=Rp)and the phase is 0

o

at

0

. The

susceptances of the L and C cancel at resonance.

Bias Circuit

Buffer

amp

resonator

gain

Z

load

Bias Circuit

Buffer

amp

resonator

Bias Circuit

Buffer

amp

resonator

gain

Z

load

L

R

P C

V

DD

V

IN

V

OUT

|Z|

0

Z

-90

o

+90

o

L

R

P C

V

DD

V

IN

V

OUT

L

R

P C

V

DD

V

IN

V

OUT

|Z|

0

Z

-90

o

+90

o

We represent the MOSFET with its simplest small signal model.

The small signal gain is given by:

Vout =- g

m

R

P

v

gs

Notice the inversion between input and output. This produces a 180 degree phase shift

for the stage, an inverter.

g

m

v

gs

R

P

g

m

v

gs

R

P

The large signal output will be a sine wave with a DC component equal to V

DD

. Since

there is very little DC voltage drop across the inductor, the average value of the output

over one period must be equal to V

DD

. The signal is out of phase with the input.

The maximum AC output voltage amplitude will be limited by either clipping (voltage

limiting)

Vout =V

DD

- V

Dsat

or by current limiting

Vout =I

Dmax

R

P

The two mechanisms have very different behavior. With voltage limiting, the output

voltage begins to resemble a square wave. The odd-order harmonic distortion will

increase. If the circuit is intended to provide good linear amplification or good spectral

purity, this scenario is to be avoided.

With current limiting, the signal amplitude can be adjusted so that it never reaches

clipping. It swings above and below V

DD

without distorting. Always build the oscillator

so that it current limits.

Circuit #2:

The tuned amplifier can form the core of an oscillator. We need to add feedback and one

more inversion.

If (g

m

R

P

)

2

1, this circuit will oscillate. It can only oscillate at

0

, because only at that

frequency will we have a total phase shift of 0

o

.

The oscillations will begin when the noise inherent in the transistors is amplified around

the loop. The strength of the oscillations will build exponentially with time. The small

signal analysis doesnt provide a limit to this growth. Obviously, this is wrong. The

amplitude will reach a limit either by voltage or current. The example below is current

limiting.

L

R

P C

V

DD

V

OUT

L

R

P C

180

o

@

0

180

o

@

0

L

R

P C

V

DD

V

OUT

L

R

P C

180

o

@

0

180

o

@

0

This circuit is also known as the Cross-coupled Oscillator. We can redraw it to look

like this:

This representation emphasizes the differential topology. The two outputs are 180

degrees out of phase. This can be very useful for many applications driving a Gilbert

cell mixer, for example. It has one major shortcoming, however.

Problem: amplitude control Vout = I

D

R

P

Vout can be controlled by adjusting the widths of the active devices. This sets the

maximum current that the device is capable of providing at a given V

GS

since

I

D

(V

GS

V

T

) for a deep submicron MOSFET.

BUT,

Vout also will depend on V

DD

, because the average V

GS

=V

DD

in this circuit.

That means that it may not always be possible to avoid voltage limiting. If the device

width is reduced too far, there may not be sufficient gain for a reliable startup.

L

R

P C

V

DD

V

OUT

L

R

P C

180

o

@

0

180

o

@

0

V

OUT

L

R

P C

V

DD

V

OUT

L

R

P C

180

o

@

0

180

o

@

0

V

OUT

Circuit #3:

One popular solution to achieve better amplitude control is to break the ground

connection, connect the sources, and bias the cross-coupled pair with a current source.

Now, the amplitude is controlled by I

0

. All of this current is steered between either the

left or right side of the diff pair. Thus, the amplitude of the output will be I

0

R

P

. This is

not perfect, because no transistor current source is ideal. The current will vary slightly

with changes in V

DD

, but it is much more stable than circuit #2. Also, the drain-substrate

capacitances of the MOSFET vary with V

DD

causing some frequency shift. Yet, it is

much better for most applications than Circuit #2.

The only drawback for this design comes from the current source noise. The channel

noise of the device adds to the total noise of the amplifier, so the phase noise of this

current-biased design is somewhat worse than that of circuit #2.

L

R

P C

V

DD

V

OUT

L

R

P C

V

OUT

I

0

L

R

P C

V

DD

V

OUT

L

R

P C

V

OUT

I

0

Circuit #4: Colpitts Oscillator

In this configuration the active device is in a common base configuration. The open loop

gain will be set by the gm of the device, by Rp and the capacitive divider. The frequency

of oscillation is determined by the resonator as in the previous examples.

To analyze the open loop gain, lets open the loop

L

R

P

C

2

C

1

C

3

L

R

P

C

2

C

1

C

3

Gain

Feedback

L

R

P

C

2

C

1

C

3

V1

V2

V1

I

E

L

R

P

C

2

C

1

C

3

V1

V2

V1

I

E

An oscillator example: Common Base Colpitts.

This oscillator uses an LC resonator to set the oscillation frequency and a capacitive

divider to establish the loop gain. The collector voltage is in phase with the input for a

common base configuration. The goal is to determine the conditions where the open

loop gain =1 considering the voltage gain of the amplifier AL, and the feedback factor

1/N The loading effects of the device and the unloaded Q of the resonator must be

considered in the analysis.

Here is a partial schematic without biasing details. The C1 C2 divider sets the feedback

ratio. The loop is broken between V1 and V1p.

Assume 1/gm <<RL. Then, the loading effect of the device input impedance, 1/gm, is

transformed up by the tapped C network to N

2

/gm. This is combined with GP due to the

unloaded Q of the resonator.

2

1

1 2

/

1

m

P m

g

A

G g N

C

C C N

=

+

= =

+

Then the open loop gain is given by:

'

1

2

1

1

/

m

OL

P m

g V

A

V N

G g N

= =

+

Setting A

OL

=1 and solving for N, we get:

2

4 1

2 2

m m m

P OL P OL P

g g g

N

G A G A G

=

This is bias dependent because gm =I

C

/V

T

.

We also need to consider the effects of the device capacitors on the frequency.

Note that Cp is in parallel with C2.

Also, Ccb is in parallel with C3 and C

T

where

1 2

1 2

T

C C

C

C C

=

+

and capacitor C3 might represent the varactor diode or tuning capacitance.

How do you find the device capacitances? The data sheet will give you Ccb and the f

T

.

From f

T

, you will find C.

2 ( )

m

T

cb

g

f

C C

=

+

Thus, subtract C from C2 and Ccb from C

T

.

For startup, we should choose an open loop gain greater than 1. Choose 3 for example.

Select Ibias and determine gm. Evaluating the equation for N at an open loop voltage

gain of 3, we obtain two answers. The larger N value limits loop gain by the tapped C

ratio. The smaller N limits by the loading of the tank with N

2

/gm.

C

2

C

1

V1

L

R

P

C

3

V2

C

B

C

E

r

e

V1

C

2

C

1

V1

L

R

P

C

3

V2

C

B

C

E

r

e

V1 Ccb

g

m

V1

One further consideration is the phase shift caused by the parallel combination of C2 and

re ( =1/gm). There will be a slight phase shift that will move the total phase around the

loop off the peak of the resonator.

Not desirable: resonator has maximum phase slope at

o

.

The effect is minimized by making C2 large and re large:

2

1

e

o

r

C

<<

Or, you can add resistance in series.

RE can help reduce the phase shift by making re +RE >>C

2

This will also reduce the loop gain.

V1

L

R

P

C

2

C

1

C

3

V2

RE

I

E

V1

L

R

P

C

2

C

1

C

3

V2

L

R

P

C

2

C

1

C

3

V2

RE

I

E

Oscillator simulation methods:

Biasing and Bypassing

In order to simulate the open loop gain and the oscillator closed loop response, we first

need to bias the transistor. The choice of collector current is arbitrary but the amplitude

will grow in proportion to I

C

. So, you need to choose V

CC

and the base bias voltage to

avoid voltage limiting due to forward biasing of the base-collector junction. In the

example shown here, I

C

=0.5 mA. The base voltage source =V

CC

/2. Since the base

current in the device is quite low, about 10 uA, there is no need to dump a lot of current

into the base bias resistive divider. Also, RF bypass capacitors should be appropriately

chosen for the frequency in use. In this case, 165 MHz. A 1nF capacitor has roughly 1

ohm capacitive reactance at this frequency. Choosing much larger capacitors runs the

risk of encouraging low frequency parasitic oscillations. Where V

CC

enters the board,

however, a larger capacitor, typically tantalum or electrolytic, is appropriate to provide a

charge reservoir on the PC board and to provide low frequency isolation from the power

source.

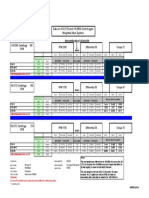

AC simulation of open loop. AC is a linearized simulation, so the result is

independent of the choice of Vac. If you look at the ratio of V1p to V1, you find a gain

of approximately 1.6 at the gain peak 161 MHz. Perhaps the frequency is off slightly due

to Ccb being larger than expected.

Note that the peak OL gain simulated is less than the analysis predicted; 1.6 vs. 3.

Replacing the device with a Voltage controlled Current source (VCCS), the simulations

and analysis agreed exactly. Evidently, our simplified small signal model of the BJ T,

which does not include Rbb, is not good enough to get exact agreement.

Transient analysis of oscillator.

This is used for a closed loop analysis of the oscillator. Starting the simulation requires

that an impulse be delivered to the resonator. Otherwise, the oscillator will not start in

simulation. A pulsed current source is ideal in that it defaults to an open circuit when

inactive. Make sure the period of the pulse is longer than the simulation time. Otherwise

you will get multiple impulses making for a confusing output signal!

We see that the oscillator has reached a limiting amplitude of 1.147V. Note that the

oscillator is current limiting, not voltage limiting because V

CB

=Vres Ve never drops

below 2V. The resonator amplitude seems to be predicted by Vres =I

C

*(RP||N

2

/gm), off

V1

L

R

P

C

2

C

1

C

3

V2

RE

I

E

V1

L

R

P

C

2

C

1

C

3

V2

RE

I

E

by a factor of 2 from Lees predictions

1

. This may be explained by the rather low bias

current which is not driving the device strongly into cutoff.

The frequency spectrum was made using the fs function in ADS. The syntax is:

I used fs(Vout,0,500MHz,,,,,6us,10us)

This windows the fft to the end of the transient simulation data, thus avoiding the crazy

startup stuff which would give misleading spectral information

Harmonic balance simulation can also be used for closed-loop oscillator analysis.

HB has be advantage that it calculates the steady-state solution directly and is relatively

fast compared with transient analysis (when it converges). To simulate an oscillator, the

ADS OscPort must be inserted into the signal path. The arrow must point in the right

direction.

It is important to give HB a starting frequency that is close to what you expect to be the

frequency of oscillation. Specify sufficient harmonics so that harmonic distortion can be

calculated at the desired integer multiples of the fundamental frequency.

1

T. Lee, The Design of CMOS Radio-Frequency Integrated Circuits, Second ed., Cambridge, 2004.

The harmonic balance controller must be activated for oscillator analysis in order to

recognize the OscPort.

The spectral output from HB for the example oscillator is shown above. Harmindex

represents the harmonic frequency.

The output from a HB oscillator simulation can be either a frequency spectrum or a time

domain representation of any voltage or current in the circuit. You can see that the

spectral representation is much cleaner than the FFT generated one from Transient

simulation. This is because HB calculates only the harmonic frequencies.

The time domain is generated using the ts function. This is an inverse Fourier Transform

or something similar that is used to convert the harmonic frequency amplitudes and

phases into a time domain sequence.

Rev. 4/9/2008 Prof. S. Long/ECE/UCSB

OscPort ( Grounded Oscillator Port)

Symbol

Available in ADS and RFDE

Parameters

V = initial guess at fundamental voltage

Z = initial value for Z

0

, in ohms (default: 1.1 ohms)

NumOctaves = number of octaves to search (default: 2)

Steps = number of steps per search octave (default: 10)

FundIndex = fundamental number for oscillator (default: 1)

Harm = harmonic or fundamental for oscillator (default: 1)

MaxLoopGainStep = maximum arc length continuation step size during loop-gain

search

Notes/Equations

1. This is a special device used for an oscillator analysis. Do not use more than

one oscillator port in a circuit.

2. NumOctaves specifies the total number of octaves over which the oscillator

search is done. Half of the octaves are below the initial frequency and half are

above. For example, if NumOctaves is 2, then the frequency search goes from

Freq/2 to Freq 2. Steps sets the number of frequency points per octave that

are used in the search. For a high-Q oscillator, a large number of steps might

be required.

3. If fundamental voltage V is not specified, the simulator first performs a small-

signal AC analysis to determine the actual frequency and oscillation voltage.

If V is specified, it represents an initial guess at the fundamental oscillator

voltage at the point where the OscPort is inserted. The initial guess for V

should be as close to the actual value as possible. An inaccurate value

increases the simulation time and might prevent convergence. If it is not

known, don't specify it.

Rev. 4/9/2008 Prof. S. Long/ECE/UCSB

4. Provided the circuit produces at least one complex conjugate pole pair in the

right-half-plane over the frequency range tested, the analysis will determine

the oscillation waveform and amplitude. Proper probe placement and

impedance can reduce the analysis time significantly and help ensure

accurate oscillator analysis results. To reduce the probability of a failed

analysis, place the probe and set the initial impedance in a manner consistent

with the following guidelines:

Feedback Oscillators (such as Colpitts)

o Insert probe at a point in the feedback loop where the signal is

contained to a single path.

o Point the arrow of the probe in the direction of positive gain

around the loop.

o Insert probe at a point in the feedback loop where source

impedance is much smaller than load impedance (at least a

factor of 10; a factor of 100 or more is preferable).

o Point the arrow of the probe at the high impedance (load) node.

o Set the initial probe impedance (Z

0

) to a value approximately

half-way between the source and load impedances presented

by the circuit at the point of insertion.

To minimize the analysis time, set the probe impedance to a factor of 10

below the load impedance, and a factor of 10 above the source impedance

(provided the source and load impedances are sufficiently far apart). Doing

this effectively reduces to zero the dependence of the small signal loop gain

on Z

0

.

Negative Resistance Oscillators

o Insert probe between a negative and positive impedance in the

circuit. There should be no other signal paths between these

two parts of the circuit. Typically, the probe is inserted between

the resonator and the effective negative resistance.

o You can point the arrow of the probe at either the negative

impedance node or the positive impedance node.

o Set the initial probe impedance to any reasonable value. To

minimize the analysis time, it should be at least a factor of two

higher or lower than the magnitude of the passive load

impedance.

The frequency is specified on the harmonic balance analysis component. The

value for Z is chosen based on impedance levels in the circuit and the degree

of non-linearity in the circuit. Do not use either 1 or 0 for Z as this will cause

convergence problems.

If the oscillator analysis fails, and this test indicates that the circuit should

oscillate, the failure may be due to the fact that the circuit is too nonlinear.

This problem can sometimes be solved by trying different impedance values

of OscPort (determined by the Z attribute). Lower impedance values usually

seem to work better. Also try reversing the OscPort direction.

Another approach is to try to get the oscillator to oscillate at some nicer

parameter value and then to sweep the parameter value to the desired value.

The parameter may be bias, self-bias impedance, some gain controlling value,

Rev. 4/9/2008 Prof. S. Long/ECE/UCSB

or another factor. In short, anything that will make the oscillator more linear,

yet still let it oscillate.

FundIndex is used for selecting which fundamental tone is considered the

unknown frequency during oscillator analysis.

The FundIndex default is 1, which means that Freq[1] on the Harmonic

Balance controller is the unknown frequency. This should be changed only if a

larger multi-tone system is simulated, such as an oscillator and mixer. In this

case, the user may want Freq[1] to be a known driven source and Freq[2] to

be the unknown frequency used by the oscillator; for this, set FundIndex=2.

For the best harmonic balance solution, the frequency that causes the most

nonlinearity should be Freq[1].

Harm is used to make a circuit oscillator on a harmonic of the fundamental

frequency rather than directly on the fundamental. For example, the circuit

may consist of a 2GHz oscillator followed by a divide-by-two circuit. In this

case, the harmonic balance analysis would be set up with Freq[1]=1 GHz, and

OscPort2 would have Harm=2. (Note that successful simulation of an

oscillator and divider will most likely require that transient-assisted harmonic

balance be used.)

Phase noise: Read T.Lee 18-1 to 18-3

Clapp Oscillator

This is a modification of the Colpitts.

The resonator is modified by adding a capacitor C3 in series with the inductor L. Since

this branch of the circuit should remain inductive, L must be increased from its Colpitts

value.

This provides several benefits:

1. R

P

of the inductor will be higher. Consider the series equivalent circuit of the inductor

below.

The inductor unloaded Q is Qu =L/Rs

The parallel equivalent resistance R

P

=Rs Qu

2

= (L)

2

/Rs

As the inductance value is increased, L and Rs both increase at the same rate. But, RP

increases with the square of L. This means that the voltage swing 2I

C

R

P

(for the same

current) can be increased with larger L. This is desirable for increasing the stored energy

in the tank and reducing phase noise.

2. There are now 3 capacitors in series. The voltage at node V3 is stepped up from V2,

also storing more energy in the resonator.

3. If C3 is smaller than the series combination of C1 and C2, it can be used to tune the

frequency of the oscillator over a relatively wide range.

V1

L

R

P

C

2

C

1

C

3

V2

RE

I

E

V3

V1

L

R

P

C

2

C

1

C

3

V2

RE

I

E

V3

Rs L Rs L

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Jyotish - 1996 - Vedic Nadi Astrology and Career PDFDocument145 pagesJyotish - 1996 - Vedic Nadi Astrology and Career PDFashu99967% (3)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- English Grammar Made Easy by Dreambig InstitutionDocument56 pagesEnglish Grammar Made Easy by Dreambig InstitutionBiswajit BeheraNo ratings yet

- Jyotish - 2017 - Dr. Revathi Vee Kumar - Pairing of Opposite Houses in PredictionDocument111 pagesJyotish - 2017 - Dr. Revathi Vee Kumar - Pairing of Opposite Houses in PredictionKiran Rajanna100% (3)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Your Star Saraswathy K.N. - TextDocument31 pagesYour Star Saraswathy K.N. - Textsaumya168096100% (1)

- Understanding the TrikonasDocument182 pagesUnderstanding the Trikonasflyinggor100% (2)

- Splendour of Vargas - SN Kapoor (ICAS) PDFDocument567 pagesSplendour of Vargas - SN Kapoor (ICAS) PDFGNo ratings yet

- Hora Shatak 100 Astro RulesDocument172 pagesHora Shatak 100 Astro RulesAstrologerAnjaan89% (9)

- Jyotish - 2009 - N.N. Sharma - Interpreting Divisional ChartsDocument195 pagesJyotish - 2009 - N.N. Sharma - Interpreting Divisional ChartsAnojj S Bhalla100% (10)

- Vedic Astrology Secret Revealed Kaal Purusha DL - PDFDocument141 pagesVedic Astrology Secret Revealed Kaal Purusha DL - PDFsaumya168096No ratings yet

- Biology BIOL 1003 CH 1-3 QuizDocument14 pagesBiology BIOL 1003 CH 1-3 QuizYummyWords100% (1)

- ADDC Construction QuestionairesDocument19 pagesADDC Construction QuestionairesUsman Arif100% (1)

- New Rules Combinations in Hindu Astrology by S K MehtaDocument100 pagesNew Rules Combinations in Hindu Astrology by S K MehtaBiswajit BeheraNo ratings yet

- Planets and Education by Naval SinghDocument204 pagesPlanets and Education by Naval SinghBiswajit BeheraNo ratings yet

- Astro Sutras of J N BhasinDocument278 pagesAstro Sutras of J N Bhasindevdattahuddar_82089No ratings yet

- The Drekkana enDocument228 pagesThe Drekkana enm_nijole86% (7)

- Jyotish Sidantha SaralDocument96 pagesJyotish Sidantha SaralBiswajit BeheraNo ratings yet

- House BhavasDocument3 pagesHouse BhavasBiswajit BeheraNo ratings yet

- Predicting Your Future Through AstrologyDocument202 pagesPredicting Your Future Through AstrologyKALSHUBH85% (13)

- 4b.jyotish - 1880 - R.M. Chatterjee - Extracts From Works On Astrology - Vol.2 PDFDocument593 pages4b.jyotish - 1880 - R.M. Chatterjee - Extracts From Works On Astrology - Vol.2 PDFsaumya168096100% (1)

- jk-1602251Document7 pagesjk-1602251Biswajit BeheraNo ratings yet

- Adda StoreDocument41 pagesAdda StoreBiswajit BeheraNo ratings yet

- Jammu and Kashmir Reservation Act InsightsDocument10 pagesJammu and Kashmir Reservation Act InsightsKiran BettadapurNo ratings yet

- union-of-india-v-gadadhar-paridawatermark-1604343Document37 pagesunion-of-india-v-gadadhar-paridawatermark-1604343Biswajit BeheraNo ratings yet

- SO176(2024)Document7 pagesSO176(2024)Biswajit BeheraNo ratings yet

- 5 6070911263301435597Document92 pages5 6070911263301435597Biswajit Behera0% (1)

- The Prisons Act_ 1894Document56 pagesThe Prisons Act_ 1894Biswajit BeheraNo ratings yet

- Handling-of-Disciplinary-Proceedings-DoPT-26-03-2024Document74 pagesHandling-of-Disciplinary-Proceedings-DoPT-26-03-2024Biswajit BeheraNo ratings yet

- 50 Important DIDocument18 pages50 Important DIBiswajit BeheraNo ratings yet

- Reportable: Signature Not VerifiedDocument52 pagesReportable: Signature Not VerifiedBiswajit BeheraNo ratings yet

- MCQDocument14 pagesMCQBiswajit BeheraNo ratings yet

- 120+ Reasoning Inequality Questions With AnswersDocument23 pages120+ Reasoning Inequality Questions With AnswersAbhishek VermaNo ratings yet

- 0905193436grade B 2019 AdvtDocument25 pages0905193436grade B 2019 AdvtAbhishek rajNo ratings yet

- Abundance BlocksDocument1 pageAbundance BlockssunnyNo ratings yet

- المحاضرة الرابعة المقرر انظمة اتصالات 2Document31 pagesالمحاضرة الرابعة المقرر انظمة اتصالات 2ibrahimNo ratings yet

- Combustion Cat 2008Document32 pagesCombustion Cat 2008Miguel LinaresNo ratings yet

- Diagram "From-To" Pada Optimasi Tata Letak Berorientasi Proses (Process Layout)Document17 pagesDiagram "From-To" Pada Optimasi Tata Letak Berorientasi Proses (Process Layout)Febrian Satrio WicaksonoNo ratings yet

- GPS and The Quest For Pizza: National Aeronautics and Space AdministrationDocument1 pageGPS and The Quest For Pizza: National Aeronautics and Space Administrationvijay maddiNo ratings yet

- D6528-07 ASTM Standard Consolidated Undrained Direct Simple Shear Testing of Cohesive SoilsDocument9 pagesD6528-07 ASTM Standard Consolidated Undrained Direct Simple Shear Testing of Cohesive SoilsDayana HernandezNo ratings yet

- Welcome To International Journal of Engineering Research and Development (IJERD)Document9 pagesWelcome To International Journal of Engineering Research and Development (IJERD)IJERDNo ratings yet

- Chemistry 12: Provincial ExaminationDocument25 pagesChemistry 12: Provincial ExaminationCát TriệuNo ratings yet

- Time and Work Assignments PDFDocument8 pagesTime and Work Assignments PDFpavan0% (1)

- The Quill Vol. LVIII Issue 1 1-12Document12 pagesThe Quill Vol. LVIII Issue 1 1-12Yves Lawrence Ivan OardeNo ratings yet

- 1999 - Seismic Soil Structure Interaction in Buildings - I Analytical Aspects PDFDocument13 pages1999 - Seismic Soil Structure Interaction in Buildings - I Analytical Aspects PDFCesar PugsioNo ratings yet

- Arta Fridei Kahlo A Fost Intotdeauna o ReactieDocument13 pagesArta Fridei Kahlo A Fost Intotdeauna o ReactieAlta DaianNo ratings yet

- Hairpin tube arrangements and multiple-bend designs for superheatersDocument2 pagesHairpin tube arrangements and multiple-bend designs for superheatersMArifHidayahNo ratings yet

- Takara 2012Document57 pagesTakara 2012Deepak Ranjan SahooNo ratings yet

- Masturbation It Might Feel Good But ItsDocument7 pagesMasturbation It Might Feel Good But ItsKshivam KhandelwalNo ratings yet

- Ub40 LyricsDocument76 pagesUb40 LyricsJose Lucio Flores SantosNo ratings yet

- Lesson 1 - Simple StressDocument5 pagesLesson 1 - Simple StressJohn Philip NadalNo ratings yet

- Product CataloguepityDocument270 pagesProduct CataloguepityRaghuRags100% (1)

- CBSE Worksheet-01 Class - VI Science (The Living Organisms and Their Surroundings)Document3 pagesCBSE Worksheet-01 Class - VI Science (The Living Organisms and Their Surroundings)Ushma PunatarNo ratings yet

- Enviroclean 25 LTRDocument1 pageEnviroclean 25 LTRMaziyarNo ratings yet

- Applying Value Engineering to Improve Quality and Reduce Costs of Ready-Mixed ConcreteDocument15 pagesApplying Value Engineering to Improve Quality and Reduce Costs of Ready-Mixed ConcreteayyishNo ratings yet

- LogiquidsDocument2 pagesLogiquidsAloma FonsecaNo ratings yet

- HS-2172 Vs HS-5500 Test ComparisonDocument1 pageHS-2172 Vs HS-5500 Test ComparisonRicardo VillarNo ratings yet

- Advanced Radiographic Techniques PDFDocument21 pagesAdvanced Radiographic Techniques PDFelokfaiqNo ratings yet

- Instruction Manual: E2M40 and E2M80 Rotary Vacuum PumpsDocument46 pagesInstruction Manual: E2M40 and E2M80 Rotary Vacuum PumpsVicki NugrohoNo ratings yet

- PC Poles: DescriptionDocument2 pagesPC Poles: DescriptionSantoso SantNo ratings yet

- Cricothyroidotomy and Needle CricothyrotomyDocument10 pagesCricothyroidotomy and Needle CricothyrotomykityamuwesiNo ratings yet

- Advanced Composite Materials Design EngineeringDocument19 pagesAdvanced Composite Materials Design EngineeringpanyamnrNo ratings yet