Professional Documents

Culture Documents

M62301SP, FP: Description Pin Configuration (Top View)

Uploaded by

roozbehxoxOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

M62301SP, FP: Description Pin Configuration (Top View)

Uploaded by

roozbehxoxCopyright:

Available Formats

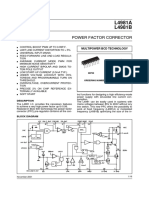

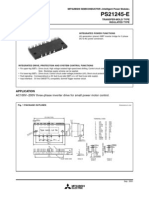

MITSUBISHI<Dig.Ana.

INTERFACE>

M62301SP,FP

10~12-BIT 4CH INTEGRATING A-D CONVERTER

DESCRIPTION

M62301 semiconductor integrated circuit forms an integrating A-D converter,being connected to a microcomputer unit.By using selection signals and counter clock signals from the unit,a 10~12-bit A-D converter can be created at a low cost. The integration time and resolution can be set at the users option by changing external parameters.In addition,the built-in circuit offset,delay time and temperature fluctuation are adjustable,enabling a wide range of applications. M62301 has a 3 input decoder circuit,high-precision reference voltage(1.22V)generator,current supply and comparator for integration,and voltage-monitoring reset circuit for a 5V power supply.It is also equipped with girdling to prevent current leak from integration capacitor.

PIN CONFIGURATION (TOP VIEW)

Vcc FOR RESET C0 C1 C2 INT RESET GIRDLING 1 GIRDLING 2 ANALOG GND

1 2 3 4 5 6 7 20 19 18 17 16

DIGITAL GND A1 A2 A3 A4 DIGITAL VDD

15 REFERENCE INPUT 14 13

FEATURES

Separate power supplies for analog section and digital section. Low power dissipation.....................................2mA(typ) (1mA for A-D conversion and the other 1mA for reset) Linear error......................................................0.02%(typ) Conversion time...............................................526s/ch(typ) Built-in system reset.........................................4.45V(typ)

INTEGRATING 8 CAPACITOR 9 10

REFERENCE VOLTAGE 12 CONSTANT CURRENT CONTROL 11 ANALOG Vcc

Outline 20P4B(SP) 20P2N-A(FP)

APPLICATION

High-precision control systems such as temperature control and speed control

BLOCK DIAGRAM

DIGITAL CONSTANT ANALOG CURRENT Vcc ANALOG GND DIGITAL CONTROL GND VDD

12

A1 A2 A3 A4

11

10

20

14

19 18 17 16

A1 A2 A3 A4 VREF GND

DISCHARGE +

0.49V

INT

0.36V

REFERENCE 15 INPUT

1

150s DELAY CIRCUIT

Vcc FOR RESET RESET

REFERENCE 13 VOLTAGE VREF

1.22V

DECODER

7

GIRDLING 1

INTEGRATING CAPACITOR

C0 C1 C2

GIRDLING 2

MITSUBISHI ELECTRIC

( 1 / 9 )

MITSUBISHI<Dig.Ana.INTERFACE>

M62301SP,FP

10~12-BIT 4CH INTEGRATING A-D CONVERTER

ABSOLUTE MAXIMUM RATINGS(Ta=25C, unless otherwise noted)

Symbol Vcc VDD VID VIA IoINT IoRE VINT VRESET VRE Pd K Topr Tstg Parameter Analog section supply voltage Digital section supply voltage Digital input voltage Analog input voltage INT output current Reset output current INT output withstand voltage Reset output withstand voltage Reset supply voltage Power dissipation Thermal derating Operating temperature Storage temperature Conditions Ratings 15 8 -0.3~VDD+0.3 -0.3~VDD+0.3 6 6 15 15 6 990(DIP)/660(FP) 9.9(DIP)/6.6(FP) -20 ~ +75 -55 ~ +125 Unit V V V V mA mA V V V mW mW/C

C C

RECOMMENDED OPERATING CONDITIONS(Ta=25C, unless otherwise noted)

Symbol Vcc VDD VIA VIR CI RI Io Parameter Analog section supply voltage Digital section supply voltage Analog input voltage range (II=50A) Reference input voltage(II=50A) Integration capacity

Resistance to determine charge current

Limits

Min Typ Max

Unit V V V V pF k mA

4.5 4.5 0 1 300 6

8.0 5.0

12.0 5.5 No more than(Vcc-2.5V) and VDD(Note 1) No more than(Vcc-2.5V) and VDD(Note 1) 22000 60 4

Output current

Note 1.Maximum analog input voltage is less than the difference between Vcc-2.5V as well as VDD. *Charging current II= VREF R1

MITSUBISHI ELECTRIC

( 2 / 9 )

MITSUBISHI<Dig.Ana.INTERFACE>

M62301SP,FP

10~12-BIT 4CH INTEGRATING A-D CONVERTER

ELECTRICAL CHARACTERISTICS(Vcc=5.0V,VDD=5.0V,Ta=25C, unless otherwise noted)

Symbol Icc VIA Parameter Supply current Analog input voltage range Reference input voltage

+ -

Test conditions

Min.

Limits Typ. 1.0

Max. 2.0 2.5 2.2

Unit mA V

II=100A II=200A IREF=5A CREF=4700pF

VREF IREF IREF Ec EL TT Tdi IB VIH VIL VLINT IOHINT VDET VDET TDE VLRE IOHRE IRE VOPL

1.17

1.22

1.27 50 -10 0.1 0.09

V A %/FSR %/FSR s

Permissible current inflow at reference voltage Conversion error Linear error Conversion time Discharge time Analog input current Digital input H level Digital input L level INT output L level INT output leak current Detection voltage Hysteresis voltage Delay time Reset output L level Reset output leak current Supply current Limit operating voltage (Note 1)RI=24k (Note 2)RI=24k VIA=2.5V,CI=0.01F RI=24k V 8=3V 0.3V CI=4700pF 3.5 IOL=1mA V 5=15V 4.30 30 75 IOL=1mA V 5=15V VRE=5V RL=2.2k,VLRE0.4V RL=100k,VLRE0.4V 0.1 4.45 50 150 0.1 1.0 0.75 0.6 0.05 0.02 526 3 -0.35

17 -3.5 0.8 0.4 1 4.60 80 300 0.4 1 2.0 1.0 0.8

s A V V V A V mV s V A mA V

Note 1.Conversion error;Deviation from the line that links the 0 scale point (mode 0) and reference scale point (mode 3. VFSR=2.5V).Associated with all channels. Note 2.Linear error;Deviation from the line that links the 0-V input point and 2.5V input point on a given channel.

MITSUBISHI ELECTRIC

( 3 / 9 )

MITSUBISHI<Dig.Ana.INTERFACE>

M62301SP,FP

10~12-BIT 4CH INTEGRATING A-D CONVERTER

OPERATING DESCRIPTION (1)Decoder Based on digital inputs to C0,C1,C2,the analog switch is set to on,and the input of "0" scale (GND input),input of reference scale (reference voltage input),input to A1~A4,or discharge Mode C0 C1 C2 1 0 0 0 Discharge 2 1 0 0 GND 3 0 1 0 VREF

from integration capacitor (CI) is performed.None of these operations is performed when the "mode 8" input is given:

4 1 1 0 A1

5 0 0 1 A2

6 1 0 1 A3

7 0 1 1 A4

8 1 1 1

(2)A-D conversion

DECODER SELECTION MODE 1 2 1 3 1 4~7 1

VIN+0.49V V 8 VREF+0.49V 0.49V 0.36V

TGND

TREF

TIN

Multiplexer first selects VGND,obtaining minimum pulse TGND.It then selects VREF,obtaining reference pulse TREF.Input is selected next,obtaining input pulse TIN.VIN is obtained by deducting TGND,as the offset,from TREF and TIN. VIN=VREF TIN-TG TREF-TG

Note. To ensure discharge from capacitor CI,the decoder input as in the above diagram should stay in mode 1 at least for the period calculated above:Tdi=(CI X VIAmax+0.49 ) 1mA

It is not necessary to measure TGND,and TREF for each channel.

By measuring voltage at the maximum input for approximately 500s under the counter clock of 8MHz,resolution of approximately 12bits can be obtained; 500s . 12 =2 125ns .

MITSUBISHI ELECTRIC

( 4 / 9 )

MITSUBISHI<Dig.Ana.INTERFACE>

M62301SP,FP

10~12-BIT 4CH INTEGRATING A-D CONVERTER

(3)Constant current control Integrating current II can be obtained based on the reference voltage(1.22V)by the built-in high-precision generator and resistance RI. II= 1.22 (A)........................(1) RI Integration time TI can be calculated as follows; TI=(VIN+0.49) CI II .............(2) II VREF

13 12 8

1.22V

RI

CI

(However,parameters such as built-in comparator offset voltage,analog switch offset,voltage leak current and delay time are not counted.)

4.45V

50mA

RESET SUPPLY VOLTAGE

VRE

0.8V

RESET OUTPUT

OUTPUT UNSETTLED

TDE

TDE

When voltage applied to pin VRE becomes less than 4.45V,the RESET output status becomes "L".If voltage increases over 4.50V,the RESET status becomes "H" within 150sec.

MITSUBISHI ELECTRIC

( 5 / 9 )

MITSUBISHI<Dig.Ana.INTERFACE>

M62301SP,FP

10~12-BIT 4CH INTEGRATING A-D CONVERTER

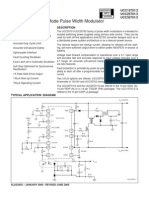

APPLICATION SUGGESTION 1.4-channel 11-bit A-D converter system

TO MICROCOMPUTER 5V POWER SUPPLY

5V

10k 10k

1 2 20 19 18 17 16 15 14 13 12 11

CREF:To stabilize reference voltage, be sure to connect capacitance of approximately 4700pF. CINT:We suggest that this capacitance be connected to prevent malfunction due to noise.

TO MICROCOMPUTER CONTROL PIN TO COUNTER TO RESET CINT 680PF

3 4 5 6 7 8 9

INPUT ANALOG VOLTAGE

CREF

4700pF

50A

10

Use CI that leaks as slight current as possible.To prevent leak to the circuit board,we recommend providing girdling 7 , 9

II=50A RI 24k

CI 4700pF

. Charge current II = 1.22V = . 50A 24k

Resolution depends on the number of microcomputer counter clock pulses that are generated while the INT output status is "high" at the maximum input voltage 2.5V (vcc-2.5V). When the microcomputer counter clock frequency is 8MHz,the resolution can be calculated by using the constant calculated above,as follows; 4700pFX (2.5+0.13) 50A 1 8M . 11 = .2

Therefore,the resolution of this system is approximately 11 bits.

MITSUBISHI ELECTRIC

( 6 / 9 )

MITSUBISHI<Dig.Ana.INTERFACE>

M62301SP,FP

10~12-BIT 4CH INTEGRATING A-D CONVERTER

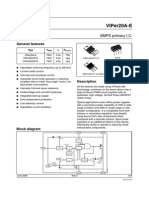

2.4-channel 12-bit A-D converter system Separate power supplies to analog section and digital section, analog input voltage range mode wider up to VDD,external reference voltage for integration.

TO MICROCOMPUTER 5V POWER SUPPLY 8V CREF:To stabilize reference voltage, be sure to connect capacitance of approximately 4700pF. CINT:We suggest that this capacitance be connected to prevent malfunction due to noise.

10k 10k

1 2 20

A1 19 A2 18 A3 17 A4 16

2.5V 15

TO MICROCOMPUTER CONTROL PIN TO COUNTER TO RESET CINT 680pF

3 4 5 6 7 8 9

INPUT ANALOG VOLTAGE

VDD 14

13 12 11

50A

10

TO MICROCOMPUTER 5V POWER SUPPLY 4700pF CREF Use CI that leaks as slight current as possible.To prevent leak to the circuit board,we recommend providing II=50A girdling 7 , 9 RI 24k

CI 6800pF

When the counter clock frequency is 8MHz,resolution is: Because separate power supplies are provided for the analog are digital sections,the M62301 has two supply voltage Vcc and VDD,enabling a wide analog input voltage range VIA.The upper limit of the range is required to be no more than the difference between Vcc-2.5V as well as VDD,therefore,the analog input voltage range in this application is 0V to 5V. 6800pF X 1 8M (5 + 0.13) 50A . 12 = .2

An A-D converter system with resolution of approximately 12 bits can be formed.

Recommended operational settings according to clock frequency,resolution,and time required for discharge(decoder mode 1) Counter clock Resolution 10-bit 8MHz 11-bit 12-bit 10-bit Change current II(A) 50 100 50 100 50 100 Resistance to determine constant current RI(k) 24 12 24 12 24 12 24 12 24 12 24 12 Integration capacitance CI 1400pF 2800pF 2800pF 5600pF 5600pF 12000pF 700pF 1400pF 1400pF 2800pF 2800pF 5600pF Discharge time Tdi(s) 7.7 15.4 15.4 30.7 30.7 65.9 3.9 7.7 7.7 15.4 15.4 30.7

50 100 50 16MHz 11-bit 100 50 12-bit 100 Note 1.Discharge time Tdi=(CI X VIAmax+0.49 ) 1mA The values in this table apply when VIAmax is 5V.

MITSUBISHI ELECTRIC

( 7 / 9 )

MITSUBISHI<Dig.Ana.INTERFACE>

M62301SP,FP

10~12-BIT 4CH INTEGRATING A-D CONVERTER TYPICAL CHARACTERISTICS

THERMAL DERATING ANALOG PART SUPPLY CURRENT VS.SUPPLY VOLTAGE

1000 800 600

2.0

1.0 400 200 0 0

25

50

75

100

125

5

ANALOG Vcc (V) LINEAR ERROR

10

AMBIENT TEMPERATURE Ta(C) STANDARD VOLTAGE VS. AMBIENT TEMPERATURE

1.24 1.23 1.22 1.21 1.20 1.19 -20

0.05 0.04 0.03 0.02 0.01 0 0 (OSR) 1.0

RI=24k RI=12k

20

40

60

80

2.0

AMBIENT TEMPERATURE Ta (V) INT OUTPUT L LEVEL VS.OUTPUT CURRENT

2.5 (FSR)

ANALOG INPUT RANGE VIA(V)

INT OUTPUT VS.AMBIENT TEMPERATURE

1.0 0.9 0.8 0.7 0.6 0.5 0.4 0.3 0.2 0.1 0 0 0.1 1 10

INT OUTPUT CURRENT IO INT (mA)

200

100

0 -20

20

40

60

80

AMBIENT TEMPERATURE Ta (C)

MITSUBISHI ELECTRIC

8 / 9 )

MITSUBISHI<Dig.Ana.INTERFACE>

M62301SP,FP

10~12-BIT 4CH INTEGRATING A-D CONVERTER

RESET SUPPLY CURRENT VS. SUPPLY VOLTAGE

DETECTION VOLTAGE vs. AMBIENT TEMPERATURE

2.0 1.8 1.6 1.4 1.2 1.0 0.8 0.6 0.4 0.2 0 0 1 2

4.7 4.6 4.5 4.4 4.3 4.2 3 4 5 6 7 8 9 10 -20 0 20 40 60 80

RESET VOLTAGE Vcc VRE (V) RESET OUTPUT L LEVEL VS.OUTPUT CURRENT AMBIENT TEMPERATURE Ta(C) DELAY TIME VS.AMBIENT TEMPERATURE

1.0 0.9 0.8 0.7 0.6 0.5 0.4 0.3 0.2 0.1 0 0 0.1 1 10

RESET OUTPUT CURRENT IORE (mA)

250 200 150 100 50 0 -20

20

40

60

80

AMBIENT TEMPERATURE Ta(C)

LIMIT RESET VOLTAGE

2.0 1.8 1.6 1.4 1.2 1.0 0.8 0.6 0.4 0.2 0 0 0.6 1.0 2.0

RL=2.2k RL=100k

RESET VOLTAGE Vcc VRE (V)

MITSUBISHI ELECTRIC

( 9 / 9 )

You might also like

- 1011-2011 TRAINING MANUAL Deutz Engine 999 0512Document141 pages1011-2011 TRAINING MANUAL Deutz Engine 999 0512Anangtri Wahyudi97% (29)

- L7250 (Smooth) - HA13627 - Hitachi Motor DriverDocument46 pagesL7250 (Smooth) - HA13627 - Hitachi Motor Drivertrandito100% (5)

- Analog Circuit Design Volume Three: Design Note CollectionFrom EverandAnalog Circuit Design Volume Three: Design Note CollectionRating: 3 out of 5 stars3/5 (2)

- Alternators and Starter Motors 2003 PDFDocument106 pagesAlternators and Starter Motors 2003 PDFjovopavlovic100% (4)

- FDS 4000 PDFDocument74 pagesFDS 4000 PDFMr.K ch100% (1)

- Volvo Penta TAD734GEDocument19 pagesVolvo Penta TAD734GERomulo Oliveira Araujo100% (2)

- P1001-B02 GA100-883 PCIe Gen4 HBM2 TESLA PASSIVE Table of ContentsDocument55 pagesP1001-B02 GA100-883 PCIe Gen4 HBM2 TESLA PASSIVE Table of Contentslol100% (2)

- sc7001q Ay 961Document18 pagessc7001q Ay 961r2c1No ratings yet

- L6565Document18 pagesL6565Sergio Daniel BarretoNo ratings yet

- Transition-Mode PFC Controller: 1 FeaturesDocument17 pagesTransition-Mode PFC Controller: 1 Featuresadriancho66No ratings yet

- 10-Bit and 12-Bit Binary Multiplying DACs from National SemiconductorDocument14 pages10-Bit and 12-Bit Binary Multiplying DACs from National SemiconductormicochangoNo ratings yet

- Ivc102 DatasheetDocument15 pagesIvc102 DatasheetChristian CândidoNo ratings yet

- MC1648 DataSheetDocument11 pagesMC1648 DataSheetKWojtekNo ratings yet

- 1267379259Document7 pages1267379259sinasayedanaNo ratings yet

- Two-Phase Stepper Motor Driver: DescriptionDocument19 pagesTwo-Phase Stepper Motor Driver: DescriptionDan EsentherNo ratings yet

- Quad Low Side Driver: DescriptionDocument17 pagesQuad Low Side Driver: DescriptionDan EsentherNo ratings yet

- ADC0844/ADC0848 8-Bit P Compatible A/D Converters With Multiplexer OptionsDocument20 pagesADC0844/ADC0848 8-Bit P Compatible A/D Converters With Multiplexer Optionsrazali1982No ratings yet

- Dual Full-Bridge Driver: DescriptionDocument13 pagesDual Full-Bridge Driver: DescriptionBaher Bassem MorkosNo ratings yet

- Adc 0808Document14 pagesAdc 0808Vikas PatelNo ratings yet

- Isolated Flyback Switching Regulator W - 9V OutputDocument16 pagesIsolated Flyback Switching Regulator W - 9V OutputCasey DialNo ratings yet

- LB1845 DDocument9 pagesLB1845 DFernando LizarragaNo ratings yet

- General Description Features: Bipolar/CMOS/DMOSDocument13 pagesGeneral Description Features: Bipolar/CMOS/DMOSjavierrincon800No ratings yet

- IRAMX16UP60ADocument18 pagesIRAMX16UP60Atheylor1990No ratings yet

- Am 422Document10 pagesAm 422Nicola CardinNo ratings yet

- Datasheet DC MotorDocument9 pagesDatasheet DC MotorKosala KapukotuwaNo ratings yet

- ADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesDocument17 pagesADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesJorge Luis Castillo GuarachiNo ratings yet

- ADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesDocument18 pagesADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesMarco MenezesNo ratings yet

- ICL7106-7107 (Harris)Document16 pagesICL7106-7107 (Harris)cgmannerheimNo ratings yet

- En CD00000085Document16 pagesEn CD00000085amijoski6051No ratings yet

- ICL7106, ICL7107, ICL7106S, ICL7107S: 3 / Digit, LCD/LED Display, A/D ConvertersDocument17 pagesICL7106, ICL7107, ICL7106S, ICL7107S: 3 / Digit, LCD/LED Display, A/D ConvertersDave MartzNo ratings yet

- Driver Bobina de Encendido VB326SPDocument9 pagesDriver Bobina de Encendido VB326SPteroplasNo ratings yet

- Integrated Circuit Systems, IncDocument11 pagesIntegrated Circuit Systems, Incroger marqNo ratings yet

- LM358 Low Power Dual Op AmpDocument8 pagesLM358 Low Power Dual Op AmpAmrutha AmmuNo ratings yet

- ADC0831/ADC0832/ADC0834 and ADC0838 8-Bit Serial I/O A/D Converters With Multiplexer OptionsDocument33 pagesADC0831/ADC0832/ADC0834 and ADC0838 8-Bit Serial I/O A/D Converters With Multiplexer OptionsRoy Muy GolfoNo ratings yet

- Ltc1871ems (LTSX, Frntoluz Welch Allyn)Document36 pagesLtc1871ems (LTSX, Frntoluz Welch Allyn)RICHIHOTS2No ratings yet

- PS21245 eDocument9 pagesPS21245 eTol SirtNo ratings yet

- MC 1496Document12 pagesMC 1496Alejandro GarciaNo ratings yet

- UCC35702Document24 pagesUCC35702Malay K GhoshNo ratings yet

- Driver Mosfet TC428Document16 pagesDriver Mosfet TC428jaimeNo ratings yet

- Distributed byDocument42 pagesDistributed bydennyjoelNo ratings yet

- Max 31865 DatasheetDocument25 pagesMax 31865 Datasheetalexender2kNo ratings yet

- 12V DC To 40V DC Converter Circuit DiagramDocument10 pages12V DC To 40V DC Converter Circuit DiagramAhdiat Darmawan LubisNo ratings yet

- MITSUBISHI PS21245-E 4th Gen IGBT Inverter ModuleDocument9 pagesMITSUBISHI PS21245-E 4th Gen IGBT Inverter ModulepukymottoNo ratings yet

- ADC0809CCNDocument16 pagesADC0809CCNFrancesca Castelar BenalcazarNo ratings yet

- 8051 SchematicDocument37 pages8051 SchematicShabeeb Ali OruvangaraNo ratings yet

- BLDC MainDocument24 pagesBLDC MainGeralt VesemirNo ratings yet

- Imprimir Datasheet 1Document14 pagesImprimir Datasheet 1Randy Siancas VelezNo ratings yet

- ADC0820 8-Bit High Speed P Compatible A/D Converter With Track/Hold FunctionDocument23 pagesADC0820 8-Bit High Speed P Compatible A/D Converter With Track/Hold Functionjohndone2009No ratings yet

- LM3914 Dot Bar Display Driver GuideDocument16 pagesLM3914 Dot Bar Display Driver GuideHelton AmorimNo ratings yet

- Fan 7314Document14 pagesFan 7314Kamal NonekNo ratings yet

- DAC0808 8-Bit D/A Converter: Literature Number: SNAS539ADocument15 pagesDAC0808 8-Bit D/A Converter: Literature Number: SNAS539AYasser Mauricio Flores RamonNo ratings yet

- Uc 3872 DWDocument8 pagesUc 3872 DWCarlos CuebasNo ratings yet

- Adc 0809Document12 pagesAdc 0809Carbon Nano TubeNo ratings yet

- TDA8703 8-bit High-Speed Analog-to-Digital Converter Data SheetDocument18 pagesTDA8703 8-bit High-Speed Analog-to-Digital Converter Data Sheetductoan_hvqsNo ratings yet

- Ad 421Document14 pagesAd 421Vishal Devrao JadhavNo ratings yet

- Air Acond Ps21246 OnduladorDocument10 pagesAir Acond Ps21246 OnduladorJ CorreoNo ratings yet

- Interfacing High-Voltage Applications To Low-Power ControllersDocument8 pagesInterfacing High-Voltage Applications To Low-Power ControllersIr Mathan RajNo ratings yet

- Unisonic Technologies Co., LTD: 8-Channel Analog Multiplexers/DemultiplexersDocument7 pagesUnisonic Technologies Co., LTD: 8-Channel Analog Multiplexers/DemultiplexersNaresh KsNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsFrom EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsNo ratings yet

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- 056-054 DSE8x10 in Fixed Export (Base Load)Document4 pages056-054 DSE8x10 in Fixed Export (Base Load)hariana100% (1)

- Application Manual: Keb Combivert F5-Basic / General 2.3Document334 pagesApplication Manual: Keb Combivert F5-Basic / General 2.3Anoop KumarNo ratings yet

- Genset - Parallel Scheme - enDocument36 pagesGenset - Parallel Scheme - enNguyễn Bá DũngNo ratings yet

- 056-155 Redundant MSCDocument2 pages056-155 Redundant MSCroozbehxoxNo ratings yet

- Capacitor AluminumDocument433 pagesCapacitor AluminumroozbehxoxNo ratings yet

- Datasheet - HK Bo8032a 1219966Document1 pageDatasheet - HK Bo8032a 1219966roozbehxoxNo ratings yet

- Esr PDFDocument6 pagesEsr PDFsatyaNo ratings yet

- Eam-110 Gac To Cummins Qsx15 Interface ... - Huegli TechDocument3 pagesEam-110 Gac To Cummins Qsx15 Interface ... - Huegli TechroozbehxoxNo ratings yet

- EAM110 GAC To Cummins QST Interface Module: PowerDocument3 pagesEAM110 GAC To Cummins QST Interface Module: PowerroozbehxoxNo ratings yet

- SMT Devices Series Overview QFP (Quad Flat Packages, Gullwing Leads)Document6 pagesSMT Devices Series Overview QFP (Quad Flat Packages, Gullwing Leads)Marius GandraburNo ratings yet

- Ee 791 Drives Lab MaualDocument39 pagesEe 791 Drives Lab MaualSiddhartha Ghosh100% (1)

- Generator Sizing Guide: Technical Data TD00405018EDocument16 pagesGenerator Sizing Guide: Technical Data TD00405018EComsip400No ratings yet

- FBs PLC Catalog enDocument28 pagesFBs PLC Catalog enroozbehxoxNo ratings yet

- Dse7110 Mkii Dse7120 Mkii Data SheetDocument2 pagesDse7110 Mkii Dse7120 Mkii Data Sheetmnvijaybabu100% (1)

- H8S 2240Document818 pagesH8S 2240roozbehxoxNo ratings yet

- DMO465R DatasheetDocument34 pagesDMO465R DatasheetMoisés Maidana100% (1)

- Flyer Xchange 16s e 100412.3Document9 pagesFlyer Xchange 16s e 100412.3Ranjit Marimuthu100% (2)

- LS Inverter iG5A ManualDocument181 pagesLS Inverter iG5A ManualSusovit Dwa100% (10)

- IL NT AMF 2 2 Reference Guide r5 PDFDocument146 pagesIL NT AMF 2 2 Reference Guide r5 PDFvasilimertzaniNo ratings yet

- ECU List 7 0 0 Global Guide r3Document419 pagesECU List 7 0 0 Global Guide r3Satrio Ongis Nade75% (4)

- Leroy Somer ALTERNATORDocument18 pagesLeroy Somer ALTERNATORroozbehxoxNo ratings yet

- BP12864CDocument1 pageBP12864CroozbehxoxNo ratings yet

- Ug40d L PDFDocument63 pagesUg40d L PDFSaasiNo ratings yet

- Generator Sets Installation GuideDocument216 pagesGenerator Sets Installation Guidezinmerford92% (26)

- XGT Panel HW Manual XP10 Eng V1.2Document221 pagesXGT Panel HW Manual XP10 Eng V1.2roozbehxoxNo ratings yet

- 21823.0 Appendix RBC1100 - LX449 V1 - 0Document8 pages21823.0 Appendix RBC1100 - LX449 V1 - 0roozbehxoxNo ratings yet

- Chapter02 OSedition7FinalDocument81 pagesChapter02 OSedition7FinalYounas BangashNo ratings yet

- U50SI1 Schematics OverviewDocument32 pagesU50SI1 Schematics OverviewHamter YoNo ratings yet

- RD-8132 Cdma Repeater: User ManualDocument27 pagesRD-8132 Cdma Repeater: User ManualelxsoonNo ratings yet

- SBC AlternatorDocument4 pagesSBC Alternatormalik budi sNo ratings yet

- WCF Advanced Activity DevelopmentDocument30 pagesWCF Advanced Activity Developmentrajanikant_singhNo ratings yet

- 7733v3.0 (G52 77331X2) (B75IA E33) 100x150Document204 pages7733v3.0 (G52 77331X2) (B75IA E33) 100x150Antreas DionysiouNo ratings yet

- 060-4199-180 LMMDocument58 pages060-4199-180 LMMPeter LapthorneNo ratings yet

- Mobile XE8Document364 pagesMobile XE8Yasser N.No ratings yet

- 7.2.2.4 Comparing RIP and EIGRP Path Selection FORMDocument2 pages7.2.2.4 Comparing RIP and EIGRP Path Selection FORMnick brandwineNo ratings yet

- KX-TDA15 V1.1 Installation ManualDocument156 pagesKX-TDA15 V1.1 Installation Manualmasterpro666No ratings yet

- 3500Document54 pages3500Steve da Rivia67% (3)

- DECA User Manual: July 20, 2017Document134 pagesDECA User Manual: July 20, 2017ADHITYANo ratings yet

- Transmission Software Service Tool ConnectionDocument3 pagesTransmission Software Service Tool ConnectionpitbullNo ratings yet

- C 6587 PW User GuideDocument28 pagesC 6587 PW User GuideMitica ScurtuNo ratings yet

- SIMATIC - S7-200 To S7-1200 Migration Overview V3Document6 pagesSIMATIC - S7-200 To S7-1200 Migration Overview V3Jorge_Andril_5370No ratings yet

- HAWK Sultan Acoustic Wave Series PDFDocument103 pagesHAWK Sultan Acoustic Wave Series PDFJuan Carlos DavidNo ratings yet

- Emc Ecc IntroDocument581 pagesEmc Ecc Introc193402No ratings yet

- Flir Dm92 Dm93 DatasheetDocument2 pagesFlir Dm92 Dm93 DatasheetFelixAvilaNo ratings yet

- Spartan 14 License AgreementDocument2 pagesSpartan 14 License AgreementOrlando David Medinueta De AvilaNo ratings yet

- r13 NoteDocument16 pagesr13 NoteTaingren HutNo ratings yet

- Bocad BasicDocument197 pagesBocad BasicTiến Lượng Nguyễn71% (7)

- 9400series CatalogueDocument71 pages9400series CatalogueAlfredo Enrique SosaNo ratings yet

- CCS - View Topic - SOLVED - Problem With INT - RDA Not Beeing FDocument5 pagesCCS - View Topic - SOLVED - Problem With INT - RDA Not Beeing Fapi-3755810100% (3)

- Hotel Management SystemDocument20 pagesHotel Management SystemRohit100% (1)

- Mainboard ESC Model P965T ADocument43 pagesMainboard ESC Model P965T AejmelchiorsNo ratings yet

- LILIN 2014 IP Product SelectorDocument20 pagesLILIN 2014 IP Product SelectorAnte NekicNo ratings yet

- ATV58 To ATV71 Transition ManualeDocument83 pagesATV58 To ATV71 Transition ManualeBudy AndikaNo ratings yet

- FH Zamboanga - Marketing Office-Fdas & CCTV Specs 03.30.21Document2 pagesFH Zamboanga - Marketing Office-Fdas & CCTV Specs 03.30.21Designers Eng'gConsultancyNo ratings yet

- RTCA DO-254 Design Assurance GuidanceDocument2 pagesRTCA DO-254 Design Assurance Guidancemichelson00No ratings yet