Professional Documents

Culture Documents

UC3842A/UC3843A: SMPS Controller

Uploaded by

josephsnadaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

UC3842A/UC3843A: SMPS Controller

Uploaded by

josephsnadaCopyright:

Available Formats

www.fairchildsemi.

com

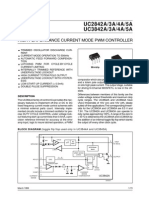

UC3842A/UC3843A

SMPS Controller

Features

Low Start Current 0.2mA (typ) Operating Range Up To 500KHz Cycle by Cycle Current Limiting Under Voltage Lock Out With Hysteresis Short Shutdown Delay Time: typ.100ns High Current Totem-pole Output Output Swing Limiting: 22V

Description

The UC3842A/UC3843A are fixed PWM controller for OffLine and DC to DC converter applications. The internal circuits include UVLO, low start up current circuit, temperature compensated reference, high gain error amplifier, current sensing comparator, and high current totem-pole output for driving a POWER MOSFET. Also UC3842A/ UC3843A provide low start up current below 0.3mA and short shutdown delay time typ. 100ns. The UC3842A has UVLO threshold of 16V(on) and 10V(off). The UC3843A is 8.4V(on) and 7.6V(off). The UC3842A and UC3843A can operate within 100% duty cycle.

8-DIP

8-SOP

Internal Block Diagram

7 VCC 29V

VREF 8

Internal Bias 1/2VREF

5V VREF

SET/ RESET UVLO

5 GND

Good LOGIC 7 PWR

VC

VFB 2

Error Amp + -

C.S PWM Comp. LATCH 1/3 1V S R 22V 6 OUTPUT

COMP 1

5 PWR

C.S 3 RT/CT 4

GND

OSCILLATOR

Rev. 5.0

2000 Fairchild Semiconductor International

UC3842A/UC3843A

Absolute Maximum Ratings

Parameter Supply Voltage Output Current Analog Inputs (pin 2, 3) Error Amp. Output Sink Current Power Dissipation Symbol VCC IO VI(ANA) ISINK(EA) PD Value 30 1 - 0.3 to 6.3 10 1 Unit V A V mA W

Electrical Characteristics

(VCC = 15V, RT = 10K, CT = 3.3nF, TA = 0C to + 70C ,Unless otherwise specified) Parameter REFERENCE SECTION Output Voltage Line Regulation Load Regulation Output Short Circuit OSILLATOR SECTION Initial Accuracy Voltage Stability Amplitude Discharge Current CURRENT SENSE SECTION Gain Maximum Input Signal PSRR Input Bias Current Delay to Output GV VI(MAX) PSRR IBIAS TD (NOTE 2, 3) VPIN1 = 5V(NOTE 2) VCC = 12V to 25V (NOTE 1, 2) VPIN3 = 0 V to 2V (NOTE1) 2.85 0.9 3 1.0 70 -2 100 3.15 1.1 -10 200 V/V V dB uA ns FOSC STV VOSC IDISCHG TJ = 25C VCC = 12V to 25V VPIN4, Peak to Peak TJ = 25C, Pin4 = 2V 47 7.8 52 0.2 1.7 8.3 57 1 8.8 KHz % V mA VREF VREF VREF ISC TJ = 25C, IO = 1mA VCC = 12V to 25V IO = 1mA to 20mA Ta = 25C 4.9 5.0 6 5.1 20 V mV mV mA Symbol Conditions Min. Typ. Max. Unit

6 25 - 100 - 180

UC3842A/UC3843A

Electrical Characteristics (Continued)

(VCC = 15V, RT = 10K, CT = 3.3nF, TA = 0C to + 70C, Unless otherwise specified) Parameter ERROR AMPLIFIER SECTION Input Voltage Input Bias Current Open Loop Gain Unity Gain Bandwidth PSRR Output Sink Current Output Source Current Output High Voltage Output Low Voltage OUTPUT SECTION Output Low Level Output High Level Rise Time Fall Time Output Voltage Swing Limit VOL VOH tR tF VOLIM ISINK = 20mA ISINK = 200mA ISOURCE = 20mA ISOURCE = 200mA TJ = 25C, C1 = 1nF (NOTE 1) TJ = 25C, C1 = 1nF (NOTE 1) VCC = 27V, C1 = 1nF UC3842A UC3843A UC3842A UC3843A UC3842A/UC3843A VPIN2 = VPIN3 = 0V ICC = 25mA 13 12 15 7.8 9 7.0 94 0.1 1.5 13.5 13.5 40 40 22 16 8.4 10 7.6 96 0.2 11 29 0.4 2.2 100 100 17 9.0 11 8.2 100 0 0.4 17 V V V V ns ns V V V V V % % mA mA V VI IBIAS GVO GBW PSRR ISINK ISOURCE VOH VOL TPIN1 = 2.5V VO = 2V to 4V (NOTE 1) TJ= 25C (NOTE 1) VCC = 12V to 25V (NOTE 1) VPIN2 = 2.7V VPIN1 = 1.1V VPIN2 = 2.3V VPIN1 = 5.0V VPIN2 = 2.3V R1 = 15K to GND VPIN2 = 2.7V R1 = 15K to Pin8 2.42 65 0.7 60 2 -0.5 5 2.50 -0.3 90 1 70 6 -0.8 6 0.8 2.58 -2 1.1 V uA dB MHz dB mA mA V V Symbol Conditions Min. Typ. Max. Unit

UNDER VOLTAGE LOCKOUT SECTION Start Threshold Min. Operating Voltage ( After turn on ) PWM SECTION Maximum Duty Cycle Minimum Duty Cycle TOTAL STANDBY CURRENT Start-Up Current Operating Supply Current VCC Zener Voltage IST ICC VZ DMAX DMIN VTH VTL

* Adjust VCC above the start threshold before setting at 15V Notes : 1. These parameters, although guaranteed, are not 100% tested in production. 2. Parameter measured at trip point of latch with V2 = 0V. 3. Gain defined as: GV = VPIN1VPIN3(VPIN3 = 0 to 0.8V)

UC3842A/UC3843A

Mechanical Dimensions

Package

8-DIP

1.524 0.10 0.018 0.004 0.060 0.004 0.46 0.10 6.40 0.20 0.252 0.008 0.79 ) 0.031 #8 9.20 0.20 0.362 0.008 9.60 MAX 0.378 #5 2.54 0.100 5.08 MAX 0.200 7.62 0.300 3.40 0.20 0.134 0.008 3.30 0.30 0.130 0.012 0.33 0.013 MIN

#1

#4

0.25 0.05

0~15

+0.10

0.010 0.002

+0.004

UC3842A/UC3843A

Mechanical Dimensions (Continued)

Package

8-SOP

MIN 1.55 0.20 0.061 0.008 0.1~0.25 0.004~0.001

#1

#8 4.92 0.20 0.194 0.008 5.13 MAX 0.202

( #4 #5 6.00 0.30 0.236 0.012

+0.10 0.15 -0.05 +0.004 0.006 -0.002

0.56 ) 0.022 1.80 MAX 0.071 MAX0.10 MAX0.004 3.95 0.20 0.156 0.008 5.72 0.225 0.50 0.20 0.020 0.008

0~

1.27 0.050

0.41 0.10 0.016 0.004

UC3842A/UC3843A

Ordering Information

Product Number UC3842AN UC3842AD UC3843AN UC3843AD Package 8 DIP 8 SOP 8 DIP 8 SOP 0 ~ + 70C Operating Temperature

UC3842A/UC3843A

UC3842A/UC3843A

LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR INTERNATIONAL. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

www.fairchildsemi.com 7/12/00 0.0m 001 Stock#DSxxxxxxxx 2000 Fairchild Semiconductor International

2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

You might also like

- Uc3843a PDFDocument8 pagesUc3843a PDFKang JadiJaya OtodidakNo ratings yet

- UC3525Document9 pagesUC3525Roger FollanoNo ratings yet

- KA3525ADocument6 pagesKA3525AJoão Pedro AlmeidaNo ratings yet

- UC3845Document13 pagesUC3845roozbehxoxNo ratings yet

- UC3843 DatasheetDocument13 pagesUC3843 DatasheetBigbrain99No ratings yet

- 7824 Data SheetDocument34 pages7824 Data Sheethjkhj4219No ratings yet

- MC34063ADocument15 pagesMC34063AAlfredo Valencia RodriguezNo ratings yet

- LM 339Document11 pagesLM 339Adi PamungkasNo ratings yet

- 8205Document16 pages8205sonytinNo ratings yet

- DatasheetDocument8 pagesDatasheetSyed AliNo ratings yet

- Utc Lm78Xx Linear Integrated Circuit: 3-Terminal 1A Positive Voltage RegulatorDocument7 pagesUtc Lm78Xx Linear Integrated Circuit: 3-Terminal 1A Positive Voltage RegulatorAbdulNo ratings yet

- MC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorsDocument14 pagesMC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorsVũ TưởngNo ratings yet

- LM324Document8 pagesLM324fitomenaNo ratings yet

- LM555/NE555: Single TimerDocument8 pagesLM555/NE555: Single TimerlancasaNo ratings yet

- CS2841BD14Document10 pagesCS2841BD14giapy0000No ratings yet

- Uc3842b 3843BDocument10 pagesUc3842b 3843Bbob75No ratings yet

- MC34063AMDocument16 pagesMC34063AMSajjad4434No ratings yet

- Jameco Part Number 1390194: Distributed byDocument31 pagesJameco Part Number 1390194: Distributed byfox7878No ratings yet

- Regulating Pulse Width Modulators with Improved PerformanceDocument7 pagesRegulating Pulse Width Modulators with Improved PerformancekkaytugNo ratings yet

- Fixed Frequency Current Mode PWM Controller: Description Pin ConfigurationDocument11 pagesFixed Frequency Current Mode PWM Controller: Description Pin ConfigurationDong Ho JinNo ratings yet

- 04 Spec Sheet PWM Controller ChipDocument16 pages04 Spec Sheet PWM Controller Chipxuanhiendk2No ratings yet

- MC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorsDocument13 pagesMC34063A, MC33063A, NCV33063A 1.5 A, Step Up/Down/ Inverting Switching RegulatorszocanNo ratings yet

- SG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorDocument10 pagesSG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorJayesh SuryavanshiNo ratings yet

- LT 3693Document24 pagesLT 3693Zoltán BaranyaiNo ratings yet

- LTC 1625Document24 pagesLTC 1625Sakura KunNo ratings yet

- Datasheet lm337Document8 pagesDatasheet lm337eduardo1011No ratings yet

- Datasheet Fairchild UC3843Document7 pagesDatasheet Fairchild UC3843Tina JohnsonNo ratings yet

- MC1723 PDFDocument9 pagesMC1723 PDFOsman KoçakNo ratings yet

- UC3845ANDocument15 pagesUC3845ANMiloud ChouguiNo ratings yet

- UC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerDocument16 pagesUC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerCortés BernaNo ratings yet

- Regulador Dual Cs8371-dDocument11 pagesRegulador Dual Cs8371-dAdrian Biasussi BiasuzziNo ratings yet

- FDocument20 pagesFfaithfully_fatihNo ratings yet

- L 6565Document17 pagesL 6565tatatabuchoNo ratings yet

- MAX038Document16 pagesMAX038fabirznNo ratings yet

- KA3842BDocument12 pagesKA3842BLucio Sortija LuqueNo ratings yet

- MC34262-D-Power Factor Controller-ON-SEMI PDFDocument19 pagesMC34262-D-Power Factor Controller-ON-SEMI PDFnightreader99No ratings yet

- LM350 DatasheetDocument12 pagesLM350 DatasheetOmarVelasquezC.No ratings yet

- Silicon Transistor: Data Sheet Preliminary Data SheetDocument12 pagesSilicon Transistor: Data Sheet Preliminary Data SheetroozbehxoxNo ratings yet

- 7 M 0880Document18 pages7 M 0880Mahmoued YasinNo ratings yet

- MC34060ADocument16 pagesMC34060AJoão GranemanNo ratings yet

- ST3232 Data SheetDocument12 pagesST3232 Data SheetcredioNo ratings yet

- LM293Document10 pagesLM293Bruno NascimentoNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- Analog Circuit Design Volume Three: Design Note CollectionFrom EverandAnalog Circuit Design Volume Three: Design Note CollectionRating: 3 out of 5 stars3/5 (2)

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetFrom EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetNo ratings yet

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetFrom EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetRating: 2 out of 5 stars2/5 (1)

- Digital Power Electronics and ApplicationsFrom EverandDigital Power Electronics and ApplicationsRating: 3.5 out of 5 stars3.5/5 (3)

- Brother DCP7065DN Toner ResetDocument3 pagesBrother DCP7065DN Toner ResetjosephsnadaNo ratings yet

- SC 995Document1 pageSC 995jo snadaNo ratings yet

- Hantek2000 QuickGuide enDocument3 pagesHantek2000 QuickGuide enmorusNo ratings yet

- Genuine Epson InkDocument2 pagesGenuine Epson InkjosephsnadaNo ratings yet

- Skilled Migrant Subclass 189 PointDocument5 pagesSkilled Migrant Subclass 189 Pointfamousp16No ratings yet

- IELTS Speaking Home Town GuideDocument3 pagesIELTS Speaking Home Town GuidejosephsnadaNo ratings yet

- IELTS Speaking: Describing Places: Model AnswerDocument2 pagesIELTS Speaking: Describing Places: Model AnswerjosephsnadaNo ratings yet

- Brother FaxDocument1 pageBrother FaxIntegrated IoesplNo ratings yet

- GRFI Writing All DocumentsDocument9 pagesGRFI Writing All DocumentsnarendraNo ratings yet

- IELTS Reading Answer SheetDocument1 pageIELTS Reading Answer Sheetskuppal50% (2)

- IELTS TOEFL Vocabulary AdjectivesDocument2 pagesIELTS TOEFL Vocabulary AdjectivesPedro Jose Méndez MarquezNo ratings yet

- Blank Answer Sheet ListeningDocument1 pageBlank Answer Sheet ListeningmustafaafghanNo ratings yet

- ResistorsDocument3 pagesResistorssajay2010No ratings yet

- CompTia's A+ Study Guide - 1 of 2Document17 pagesCompTia's A+ Study Guide - 1 of 2Anthony DixonNo ratings yet

- dc15f - EG31M S2 R102Document33 pagesdc15f - EG31M S2 R102josephsnadaNo ratings yet

- AO4407Document5 pagesAO4407Gerald Tello MadridNo ratings yet

- Gigabyte Ga-g31m-Es2c Rev 1.12 SCHDocument33 pagesGigabyte Ga-g31m-Es2c Rev 1.12 SCHtaz1mxNo ratings yet

- Infocus x2 ManualDocument49 pagesInfocus x2 ManualLarsa AntonssonNo ratings yet

- Hard DiskDocument17 pagesHard DiskarmanmohammedNo ratings yet

- AR-5731 AR-5726: Essential Copy/Print Performance Plus A Compact, Productive Inner Finisher OptionDocument4 pagesAR-5731 AR-5726: Essential Copy/Print Performance Plus A Compact, Productive Inner Finisher OptionjosephsnadaNo ratings yet

- Speaking Sample Interview Hometown JobsDocument1 pageSpeaking Sample Interview Hometown Jobswaheed_iiuiNo ratings yet

- Fdd6688/Fdu6688: 30V N-Channel Powertrench MosfetDocument6 pagesFdd6688/Fdu6688: 30V N-Channel Powertrench MosfetjosephsnadaNo ratings yet

- New Product Rench EN ET: P-Channel Enhancement-Mode MOSFETDocument4 pagesNew Product Rench EN ET: P-Channel Enhancement-Mode MOSFETjosephsnadaNo ratings yet

- Can An Ohmmeter Test Thyristor and TriacDocument2 pagesCan An Ohmmeter Test Thyristor and Triacmr.sanyNo ratings yet

- ICC - ECBC ProjectDocument21 pagesICC - ECBC ProjectfenixNo ratings yet

- Under Speed 2Document4 pagesUnder Speed 2claudio santosNo ratings yet

- Ianus M22: Dual Evacuation & Refrigerant Charging Equipment For Flammable & Non Flammable GasesDocument5 pagesIanus M22: Dual Evacuation & Refrigerant Charging Equipment For Flammable & Non Flammable GasesSylvain AguedaNo ratings yet

- Cooling Solutions Refrigerants Compressors GuideDocument21 pagesCooling Solutions Refrigerants Compressors GuideSukhee TserNo ratings yet

- Transformadores PDFDocument1 pageTransformadores PDFAlex RamirezNo ratings yet

- Solar Powered Automatic Irrigation SystemDocument31 pagesSolar Powered Automatic Irrigation SystemKhan Arshid Iqbal100% (8)

- RT809F TutorialLlogic Board Gamma Chip BUF16821Document7 pagesRT809F TutorialLlogic Board Gamma Chip BUF16821Sk WongNo ratings yet

- Package Computer Room Unit: Saudi Arabian Oil CompanyDocument1 pagePackage Computer Room Unit: Saudi Arabian Oil CompanyWaqarNo ratings yet

- Tiva C Series LaunchPadDocument13 pagesTiva C Series LaunchPadVivek ShrigiriNo ratings yet

- B-Class Sedan Service Manual EC Engine Control System: Installation Position of Engine ECU: Position DescriptionDocument3 pagesB-Class Sedan Service Manual EC Engine Control System: Installation Position of Engine ECU: Position Descriptiondrivers automotrizNo ratings yet

- Wepik The Efficiency and Advancements of Solenoid Engines A Comprehensive Overview 20230626123324WEMMDocument8 pagesWepik The Efficiency and Advancements of Solenoid Engines A Comprehensive Overview 20230626123324WEMMLakshayaasri SingaravelNo ratings yet

- D0000083Document16 pagesD0000083tinduongNo ratings yet

- DOPP232Document5 pagesDOPP232Dennis Garces ZaldivarNo ratings yet

- DHB2PT-33B Dedicated Holding BinDocument2 pagesDHB2PT-33B Dedicated Holding BinJorgeNo ratings yet

- TLV431x Low-Voltage Adjustable Precision Shunt Regulator: 1 Features 2 ApplicationsDocument52 pagesTLV431x Low-Voltage Adjustable Precision Shunt Regulator: 1 Features 2 Applicationsscribd_alphaNo ratings yet

- IECEx BAS 13.0008X 000Document4 pagesIECEx BAS 13.0008X 000Marcos SiqueiraNo ratings yet

- YK Style G Optiview Centrifugal Liquid Chiller Operation Manual (Form 160.54-O1)Document206 pagesYK Style G Optiview Centrifugal Liquid Chiller Operation Manual (Form 160.54-O1)ANGEL MURILLONo ratings yet

- Instruction Manual - Series 200 Remote Meter Panels 500 PPD (10 KG/H) Maximum CapacityDocument14 pagesInstruction Manual - Series 200 Remote Meter Panels 500 PPD (10 KG/H) Maximum CapacityJorge RiverosNo ratings yet

- Yokohama Databook 2011Document46 pagesYokohama Databook 2011Edson MirandaNo ratings yet

- Accessories WrenchesDocument1 pageAccessories WrenchesabbycanNo ratings yet

- Honeywell On SystemDocument2 pagesHoneywell On SystemVishnu Vardhan . CNo ratings yet

- Load Haul Dump General Specification: Capacities PowertrainDocument2 pagesLoad Haul Dump General Specification: Capacities PowertrainEsty100% (2)

- Piaggio X9250Document75 pagesPiaggio X9250Toni MarasovicNo ratings yet

- Bw1800 Manual Alarma EcosportDocument16 pagesBw1800 Manual Alarma Ecosportandrss100% (1)

- Rebel 2020 SeriesDocument149 pagesRebel 2020 SeriesCornel Nicolae BratuNo ratings yet

- Cyl, Sleeve, Ship Assy: Bucyrus International, IncDocument6 pagesCyl, Sleeve, Ship Assy: Bucyrus International, Incmilenko Cortes100% (2)

- GA-H61M-S2PV Motherboard DiagramDocument33 pagesGA-H61M-S2PV Motherboard DiagramDouble HelixNo ratings yet

- Add To Ca RT Ref.N O Part No Part Name Q/V OR D NDP MOQ Stoc K P/ Q Remar KS Ntor Q 125Document4 pagesAdd To Ca RT Ref.N O Part No Part Name Q/V OR D NDP MOQ Stoc K P/ Q Remar KS Ntor Q 125Soroj BiswasNo ratings yet

- R8100C Mvaw02Document20 pagesR8100C Mvaw02Rinda_RaynaNo ratings yet

- Plano Hidraulico D11 TDocument2 pagesPlano Hidraulico D11 TJose DelfinNo ratings yet