Professional Documents

Culture Documents

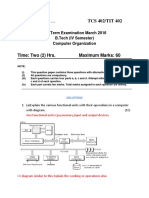

Computer Organization - List of Assignments.

Uploaded by

arnab_bhattacharj_26Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Computer Organization - List of Assignments.

Uploaded by

arnab_bhattacharj_26Copyright:

Available Formats

Techno India EM-4/1, Sector-V, Salt Lake City, Kolkata- 700091

CSE 3rd Semester (2012-2016) Assignment list 1 Subject Name: Computer Organization Subject Code: CS 303 Submission date: 23.10.2013 1. The IBM short oating point representation uses base 16, one sign bit, a seven-bit excess 64 exponent and a normalized 24-bit fraction. a) What number is represented by the bit pattern shown below? 1 0111111 01110000 00000000 00000000 Show your answer in decimal. Note: the spaces are included in the number for readability only. b) Represent (14.3)6 in this notation. 2. For parts (a) through (e), use a floating point representation with a sign bit in the leftmost position, followed by a two-bit twos complement exponent, followed by a normalized three-bit fraction in base 2. Zero is represented by the bit pattern: 0 0 0 0 0 0. There is no hidden 1. a) What decimal number is represented by the bit pattern: 1 0 0 1 0 0? b) Keeping everything else the same but changing the base to 4 will: increase / decrease / not change the smallest representable positive number. c) What is the smallest gap between successive numbers? d) What is the largest gap between successive numbers? e) There are a total of six bits in this floating point representation, and there are 26 = 64 unique bit patterns. How many of these bit patterns are valid? 3. Represent (107.15)10 in a floating point representation with a sign bit, a seven-bit excess 64 exponent, and a normalized 24-bit fraction in base 2. There is no hidden 1. Truncate the fraction by chopping bits as necessary. 4. i)Show the IEEE 754 bit patterns for the following numbers: a) +1.1011 25 (single precision) b) +0 (single precision) c) 1.00111 21 (double precision) d) NaN (single precision)

4. ii) Represent (107.875)10 in the IEEE-754 single precision floating point representation which has a sign bit, an eight-bit excess 127 exponent, and a normalized 23-bit significand in base 2 with a hidden 1 to the left of the radix point. Truncate the fraction if necessary by chopping bits as necessary. Show your work.

5. Using the IEEE 754 single precision format, show the value (not the bit pattern) of:

Department of CSE

Page 1 of 7

Techno India EM-4/1, Sector-V, Salt Lake City, Kolkata- 700091

a) The largest positive representable number (note: is not a number). b) The smallest positive nonzero number that is normalized. c) The smallest positive nonzero number in denormalized format. d) The smallest normalized gap. e) The largest normalized gap. f ) The number of normalized representable numbers (including 0; note that and NaN are not numbers). 6. The 16-bit adder shown below uses a ripple carry among four-bit carry look ahead adders.

(a) What is the longest gate delay through this adder? (b) What is the shortest gate delay through this adder, from any input to any output? (c) What is the gate delay for s12? 7. Given multiplication units that each produce a 16-bit unsigned product on two unsigned 8-bit inputs, and 16-bit adders that produce a 16-bit sum and a carry-out on two 16-bit inputs and a carry-in, connect these units so that the overall unit multiplies 16-bit unsigned numbers, producing a 32-bit result. 8. Add (641)10 to (259)10 in unsigned BCD, using as few digits in the result as necessary. 9. A pocket pager contains a small processor with 27 8-bit words of memory. The ISA has four registers: R0, R1, R2, and R3. The instruction set is shown in figure as well as the bit patterns that correspond to each register, the

Department of CSE

Page 2 of 7

Techno India EM-4/1, Sector-V, Salt Lake City, Kolkata- 700091

Instruction format, and the modes, which determine if the operand is a register (mode bit = 0) or the operand is a memory location (mode bit = 1). Either or both of the operands can be registers, but both operands cannot be memory locations. If the source or destination is a memory location, then the corresponding source or destination field in the instruction is not used since the address field is used instead. (a) Write a program using object code (not assembly code) that swaps the contents of registers R0 and R1. You are free to use the other registers as necessary, but do not use memory. Use no more than four lines of code (fewer lines are possible). Place 0s in any positions where the value does not matter. (b) Write a program using object code that swaps the contents of memory locations 12 and 13. As in part (a), you are free to use the other registers as necessary, but do not use other memory locations. Place 0s in any positions where the value does not matter. 10. (a) Write three-address, two-address, and one-address programs to compute the function A = (B-C)*(D-E). Assume 8-bit opcodes, 16-bit operands and addresses, and that data is moved to and from memory in 16-bit chunks. (Also assume that the opcode must be transferred from memory by itself.) Your code should not overwrite any of the operands. Use any temporary registers needed. (b) Compute the size of your program in bytes. (c) Compute the memory traffic your program will generate at execution time, including instruction fetches. 11. A control unit for a machine tool is shown in figure. You are to create the microcode for this machine. The behavior of the machine is as follows: If the Halt input A is ever set to 1, then the output of the machine stays halted forever and outputs a perpetual 1 on the X line, and 0 on the V and W lines. A waiting light (output V) is enabled (set to 1) when no inputs are enabled. That is, V is lit when the A, B, and C inputs are 0, and the machine is not halted. A bell is sounded (W=1) on every input event (B=1 and/or C=1) except when the machine is halted. Input D and output S can be used for state information for your microcode. Use 0s for any fields that do not matter. Hint: Fill in the lower half of the table first.

Department of CSE

Page 3 of 7

Techno India EM-4/1, Sector-V, Salt Lake City, Kolkata- 700091

12. Design a 16-word, four-bit RAM using 44 RAMs and a single external decoder. 13. Design an eight-word, 32-bit RAM using 8x8 RAMs. 14 Draw the circuit for a 4-to-16 tree decoder, using a maximum fan-in and fan-out of two. 15. A direct mapped cache consists of 128 slots. Main memory contains 16K blocks of 16 words each. Access time of the cache is 10 ns, and the time required to fill a cache slot is 200 ns. Load-through is not used; that is, when an accessed word is not found in the cache, the entire block is brought into the cache, and the word is then accessed through the cache. Initially, the cache is empty. Note: When referring to memory, 1K = 1024. (a) Show the format of the memory address. (b) Compute the hit ratio for a program that loops 10 times from locations 15 200. Note that although the memory is accessed twice during a miss (once for the miss, and once again to satisfy the reference), a hit does not occur for this case. To a running program, only a single memory reference is observed. (c) Compute the effective access time for this program. 16. A fully associative mapped cache has 16 blocks, with eight words per block. The size of main memory is 216 words, and the cache is initially empty. Access time of the cache is 40 ns, and the time required to transfer eight words between main memory and the cache is 1 s. (a) Compute the sizes of the tag and word fields. (b) Compute the hit ratio for a program that executes from 2045, then loops four times from 2845 before halting. Assume that when there is a miss, that the entire cache slot is filled in 1 s, and that the first word is not seen by the CPU until the entire slot is filled. That is, assume load-through is not used. Initially, the cache is empty. (c) Compute the effective access time for the program described in part (b) above. 17. A computer has 16 pages of virtual address space but only four physical page frames. Initially the physical memory is empty. A program references the virtual pages in the order: 0 2 4 5 2 4 3 11 2 10. (a) Which references cause a page fault with the LRU page replacement policy? (b) Which references cause a page fault with the FIFO page replacement policy?

Department of CSE

Page 4 of 7

Techno India EM-4/1, Sector-V, Salt Lake City, Kolkata- 700091

18. A virtual memory system has a page size of 1024 words, eight virtual pages, four physical page frames, and uses the LRU page replacement policy. The page table is as follows:

(a) What is the main memory address for virtual address 4096? (b) What is the main memory address for virtual address 1024? (c) A fault occurs on page 0. Which page frame will be used for virtual page 0? 19. When running a particular program with N memory accesses, a computer with a cache and paged virtual memory generates a total of M cache misses and F page faults. T1 is the time for a cache hit; T2 is the time for a main memory hit; and T3 is the time to load a page into main memory from the disk. (a) What is the cache hit ratio? (b) What is the main memory hit ratio? That is, what percentage of main memory accesses do not generate a page fault? (c) What is the overall effective access time for the system? 20. How much storage is needed for the page table for a virtual memory that has 232 bytes, with 212 bytes per page, and 8 bytes per page table entry? 21. A certain memory system has a 32 MB main memory, and a 64 KB cache. Blocks are 16 bytes in size. Show the fields in a memory address if the cache is a. associative b. direct-mapped c. 8-way set-associative 22. Design a circuitry for 5-bit comparator 23. A disk has an average seek time of 20 ms and an average rotational latency of 16.7 ms. its transfer rate is 2.0 MB/s. What size block is necessary so that delay in locating the data is only 50% of the total time to read or write a block. Discuss whether all of a virtual memory page of this size would be likely to be accessed in main memory before it is replaced.

Department of CSE

Page 5 of 7

Techno India EM-4/1, Sector-V, Salt Lake City, Kolkata- 700091

24. Design a 3-bit carry lookahead adder and determine the maximum number of gates between any input and each of the four outputs (3 sum bits and a carry). 25. How many gate delays are there in the longest path from some input to some output of a 64-bit adder using 4-bit carry lookahead groups and a multiple level structure? Compare with the longest path for a 64-bit ripple carry adder. 26. Convert the following decimal numbers to IEEE single-precision floating-point numbers. Report the results as hexadecimal values. You need not extend the calculation of the significand value beyond its most significant 8 bits. a. -65 b. 7.3125 c. 0.8 d. 0.000083 e. 72,000,831 f. -42.16 g. 6.02 x 1023 27. Write an ANSI C program to convert a decimal number to a 32-bit IEEE real. Report the result as a hexadecimal number, and also in scientific notation: n.nnn x 1Onn. 28. In a computer instruction format, the instruction length is 11 bits and the size of an address field is 4 bits. Is it possible to have: 5 2-address instructions 45 1-address instructions 32 0-address instructions using the format? Justify your answer. b. Assume that a computer architect has already designed 6 two-address and 24 zeroaddress instructions using the instruction format above. What is the maximum number of one-address instructions that can be added to the instruction set? 29. A set associative cache consists of 64 slots divided into 4-slot sets. Main memory contains 4K blocks of 128 words each. Show the format of the main memory address. 30. Using the page table shown below, translate virtual address 2050 into a physical address, and translate physical address 25 into a virtual address. Address length is 16 bits, page size is 2048 words. Physical memory has 4 page frames. Page Present (1-in/0-out) Page Frame 0 1 3 1 1 2 2 1 0 3 0 --

Department of CSE

Page 6 of 7

Techno India EM-4/1, Sector-V, Salt Lake City, Kolkata- 700091

31. An operating system uses a Least Recently Used (LRU) page replacement algorithm. Consider the following page reference ordering (pages are referenced from left to right): 1, 8, 1, 7, 8, 2, 7, 2, 1, 8, 3 What will be the number of page faults that are generated for this particular LRU case assuming that the process has been allocated four page frames, and that initially, none of the pages are in the main memory? 32. If a virtual memory system has 4 pages in real memory and the rest must be swapped to disk, determine the hit ratio for the following page address system. Assume memory starts empty. Use the First In First Out (FIFO) page replacement policy. Choose the closest answer. PAGE REQUESTS: 2 5 3 4 1 4 7 2 1 3 1 7 4 5 4 6

Department of CSE

Page 7 of 7

You might also like

- Shivalik College of Engineering Question Bank Computer Organization B.Tech II Year (IV Semester)Document5 pagesShivalik College of Engineering Question Bank Computer Organization B.Tech II Year (IV Semester)Paras TilaraNo ratings yet

- MCS-012 - Computer Organisation and AssemblyDocument4 pagesMCS-012 - Computer Organisation and AssemblyLataPuthranNo ratings yet

- MCS 012Document4 pagesMCS 012rajatkumar.codingNo ratings yet

- BCA 2nd Sem Ass.2018-19Document15 pagesBCA 2nd Sem Ass.2018-19Kumar InfoNo ratings yet

- CAO Set 8Document8 pagesCAO Set 8Vilayat AliNo ratings yet

- CRC of BCA (2) Assignment (Revised Syllabus)Document17 pagesCRC of BCA (2) Assignment (Revised Syllabus)BshrinivasNo ratings yet

- Model Co Paper MaeDocument4 pagesModel Co Paper MaeShashank RaoNo ratings yet

- Maximum capacity, combinational circuit, bus bandwidth calculatorDocument3 pagesMaximum capacity, combinational circuit, bus bandwidth calculatorAnanthi RajkumarNo ratings yet

- Assignment 1 CSADocument4 pagesAssignment 1 CSAPrashant RawatNo ratings yet

- BSC (H) CSHT II 204 Mid2012 Ddu Assignment IDocument2 pagesBSC (H) CSHT II 204 Mid2012 Ddu Assignment IRavi RanjanNo ratings yet

- MAC Instruction Sequence Steps Exam QuestionsDocument7 pagesMAC Instruction Sequence Steps Exam QuestionsnizobellNo ratings yet

- COA Assignment: This Assignment Consists of 10 Questions. Each Question Is of 5 MarksDocument3 pagesCOA Assignment: This Assignment Consists of 10 Questions. Each Question Is of 5 Marksprakhar agrawalNo ratings yet

- Question Bank For DecoDocument2 pagesQuestion Bank For Decotheamg7272No ratings yet

- Do Practice CODocument2 pagesDo Practice COSudeep SharmaNo ratings yet

- FALLSEM2019-20 CSE2001 TH VL2019201007433 Reference Material I 18-Sep-2019 DA-2Document2 pagesFALLSEM2019-20 CSE2001 TH VL2019201007433 Reference Material I 18-Sep-2019 DA-2Sachin KharelNo ratings yet

- Computer Organization and Architecture (01CE0402) Lab ManualDocument4 pagesComputer Organization and Architecture (01CE0402) Lab ManualrockyNo ratings yet

- FALLSEM2019-20 CSE2001 TH VL2019201007433 Reference Material I 18-Sep-2019 DA-2 PDFDocument2 pagesFALLSEM2019-20 CSE2001 TH VL2019201007433 Reference Material I 18-Sep-2019 DA-2 PDFSubarna Lamsal0% (1)

- Name:: CMSC 313 Fall 2001 Computer Organization & Assembly Language Programming Exam 1Document11 pagesName:: CMSC 313 Fall 2001 Computer Organization & Assembly Language Programming Exam 1Mahadeva HerbalsNo ratings yet

- Practice Questions To Set 8Document8 pagesPractice Questions To Set 8NiravNo ratings yet

- CS 2006 (Coa) - CS - End - May - 2023Document14 pagesCS 2006 (Coa) - CS - End - May - 2023223UTKARSH TRIVEDINo ratings yet

- Computer Architecture Final Exam ReviewDocument10 pagesComputer Architecture Final Exam Reviewkhayat_samirNo ratings yet

- Code No.:: (This Paper Contains 3 Pages)Document3 pagesCode No.:: (This Paper Contains 3 Pages)Sreepada RavikumarNo ratings yet

- Computer Organization Jan 2010Document2 pagesComputer Organization Jan 2010Prasad C MNo ratings yet

- Quiz QuestionsDocument2 pagesQuiz QuestionsAditya DusiNo ratings yet

- 2629acomputer ArchitectureDocument15 pages2629acomputer ArchitectureSiddhant Jain SethNo ratings yet

- R07 Set No. 2Document7 pagesR07 Set No. 2Mothilal KaramtothuNo ratings yet

- End Semester Examination: January, 2022 Digital Electronics and Computer OrganizationDocument3 pagesEnd Semester Examination: January, 2022 Digital Electronics and Computer OrganizationFFFNo ratings yet

- Computer Architecture and Organization Assignment IIDocument2 pagesComputer Architecture and Organization Assignment IIDEMEKE BEYENENo ratings yet

- CS211 Exam PDFDocument8 pagesCS211 Exam PDFUnknown UserNo ratings yet

- Assignment COA ETCS-204Document3 pagesAssignment COA ETCS-204YuvrajNo ratings yet

- Question Bank - M5 To M7Document2 pagesQuestion Bank - M5 To M7Pieter MarkerNo ratings yet

- CAO 2021 Assignment QuestionDocument9 pagesCAO 2021 Assignment Questiondawit tadewoseNo ratings yet

- Ceng252 Quiz3answersDocument3 pagesCeng252 Quiz3answersVenkata Krishnamraju Kalidindi100% (2)

- Microprocessor Microcontroller EXAM 2021 MGDocument11 pagesMicroprocessor Microcontroller EXAM 2021 MGRene EBUNLE AKUPANNo ratings yet

- Term End Examination November 2012Document4 pagesTerm End Examination November 2012Akash SharmaNo ratings yet

- Computer Organization Jun 2010Document2 pagesComputer Organization Jun 2010Prasad C MNo ratings yet

- Computer Applications and ManagementDocument11 pagesComputer Applications and ManagementParag PaliwalNo ratings yet

- E6995ca TutDocument14 pagesE6995ca Tutrabinoss0% (1)

- B.E./B.Tech. DEGREE EXAMINATION Computer Architecture QuestionsDocument3 pagesB.E./B.Tech. DEGREE EXAMINATION Computer Architecture QuestionssamueljamespeterNo ratings yet

- GATE QnADocument5 pagesGATE QnAGaurav MoreNo ratings yet

- Co QSTN BankDocument4 pagesCo QSTN Bankjoydeep12No ratings yet

- Assignment-2-Holi Vacations PDFDocument4 pagesAssignment-2-Holi Vacations PDFanon_875278414No ratings yet

- Computer Organization 21CS34 Question BankDocument117 pagesComputer Organization 21CS34 Question BankGaurav NNo ratings yet

- MCS 012Document5 pagesMCS 012S.M. FarhanNo ratings yet

- CSC 204 - Final Study GuideDocument12 pagesCSC 204 - Final Study GuideFVCproductionsNo ratings yet

- Fallsem2019-20 Cse2001 TH VL2019201000616 Da-2 Quiz-1 QP Key Da2 PDFDocument3 pagesFallsem2019-20 Cse2001 TH VL2019201000616 Da-2 Quiz-1 QP Key Da2 PDFBadhan PaulNo ratings yet

- Pdfjoiner PDFDocument26 pagesPdfjoiner PDFbakosey323No ratings yet

- Bput CoaDocument2 pagesBput CoaANIKET SAHOONo ratings yet

- CEG 2131 - Fall 2002 - FinalDocument11 pagesCEG 2131 - Fall 2002 - FinalAmin DhouibNo ratings yet

- Sheet ThreeDocument4 pagesSheet ThreeRana BadranNo ratings yet

- Sheet (5) - Computer Organization (Timing and Control)Document4 pagesSheet (5) - Computer Organization (Timing and Control)memoustafaNo ratings yet

- Solutions To Set 8Document18 pagesSolutions To Set 8kitana_sectNo ratings yet

- Tutorial 8Document6 pagesTutorial 8Nixon GamingNo ratings yet

- Exam2 s09 v2Document10 pagesExam2 s09 v2serhatandic42No ratings yet

- Mid Term Exam Solutions TCS 402Document18 pagesMid Term Exam Solutions TCS 402Obsii ChalaNo ratings yet

- Chapter 4.: Ex. 1. Caches and Address Translation. Consider A 64 Byte Cache With 8 Byte Blocks, An Associativity ofDocument8 pagesChapter 4.: Ex. 1. Caches and Address Translation. Consider A 64 Byte Cache With 8 Byte Blocks, An Associativity ofthanhspy007No ratings yet

- R5210505 Computer OrganizationDocument1 pageR5210505 Computer OrganizationsivabharathamurthyNo ratings yet

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemFrom EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNo ratings yet

- Homework 1Document11 pagesHomework 1kashi13No ratings yet

- Software Engg.Document83 pagesSoftware Engg.Gurpreet SinghNo ratings yet

- Algebraic StructuresDocument124 pagesAlgebraic StructuresFrederico Sande VianaNo ratings yet

- An Anthropologist Among The Marxis by RamchandraGuha PDFDocument139 pagesAn Anthropologist Among The Marxis by RamchandraGuha PDFarnab_bhattacharj_26No ratings yet

- Define classes BOOK, BATSMAN, STUDENT and STACKDocument1 pageDefine classes BOOK, BATSMAN, STUDENT and STACKarnab_bhattacharj_26No ratings yet

- Indian CitizenshipDocument5 pagesIndian Citizenshiparnab_bhattacharj_26No ratings yet

- ICCDocument4 pagesICCarnab_bhattacharj_26No ratings yet

- Computer Architecture Sample PaperDocument3 pagesComputer Architecture Sample Paperarnab_bhattacharj_26No ratings yet

- Indo Bangladesh ProblemsDocument5 pagesIndo Bangladesh Problemsarnab_bhattacharj_26No ratings yet

- Algebra PDFDocument950 pagesAlgebra PDFrt2222No ratings yet

- Indian CinemaDocument2 pagesIndian Cinemaarnab_bhattacharj_26No ratings yet

- IMF Vs World BankDocument2 pagesIMF Vs World Bankarnab_bhattacharj_26No ratings yet

- Journey of HockeyDocument3 pagesJourney of Hockeyarnab_bhattacharj_26No ratings yet

- Hockey legend Dhyan Chand's inspiring careerDocument3 pagesHockey legend Dhyan Chand's inspiring careerarnab_bhattacharj_26No ratings yet

- Types of TerrorismDocument2 pagesTypes of Terrorismarnab_bhattacharj_26No ratings yet

- Comptroller and Auditor GeneralDocument3 pagesComptroller and Auditor Generalarnab_bhattacharj_26No ratings yet

- Kite Runner.Document10 pagesKite Runner.arnab_bhattacharj_26No ratings yet

- Maharatna CompanyDocument3 pagesMaharatna Companyarnab_bhattacharj_26No ratings yet

- Sequential Circuit Synthesis - II: Virendra Singh Indian Institute of Science BangaloreDocument23 pagesSequential Circuit Synthesis - II: Virendra Singh Indian Institute of Science Bangalorearnab_bhattacharj_26No ratings yet

- Theory of Orthographic ProjectionDocument95 pagesTheory of Orthographic ProjectionNauman Khan0% (1)

- Agni MissileDocument4 pagesAgni Missilearnab_bhattacharj_26No ratings yet

- Memory Organization and AddressingDocument52 pagesMemory Organization and Addressingarnab_bhattacharj_26No ratings yet

- And The Mountains EchoedDocument5 pagesAnd The Mountains Echoedarnab_bhattacharj_26No ratings yet

- Floating Point AddersDocument126 pagesFloating Point Addersarnab_bhattacharj_26No ratings yet

- Indian Culture Globalised WorldDocument5 pagesIndian Culture Globalised Worldarnab_bhattacharj_26No ratings yet

- Floating Point AdderDocument14 pagesFloating Point Adderarnab_bhattacharj_26No ratings yet

- Assignment Mathematics AlgebraDocument4 pagesAssignment Mathematics Algebraarnab_bhattacharj_26No ratings yet

- Floating Point AdderDocument14 pagesFloating Point Adderarnab_bhattacharj_26No ratings yet

- Datatypes in CDocument12 pagesDatatypes in Carnab_bhattacharj_26No ratings yet

- Indian Culture Globalised WorldDocument5 pagesIndian Culture Globalised Worldarnab_bhattacharj_26No ratings yet

- Lay Out New PL Press QltyDocument68 pagesLay Out New PL Press QltyDadan Hendra KurniawanNo ratings yet

- Ericsson 3G Chapter 5 (Service Integrity) - WCDMA RAN OptDocument61 pagesEricsson 3G Chapter 5 (Service Integrity) - WCDMA RAN OptMehmet Can KahramanNo ratings yet

- Badminton Lesson 1 4 - 5 Grade: TH THDocument31 pagesBadminton Lesson 1 4 - 5 Grade: TH THLoxcey LopezNo ratings yet

- Biotechnology Eligibility Test (BET) For DBT-JRF Award (2010-11)Document20 pagesBiotechnology Eligibility Test (BET) For DBT-JRF Award (2010-11)Nandakumar HaorongbamNo ratings yet

- Case Study, g6Document62 pagesCase Study, g6julie pearl peliyoNo ratings yet

- Solution of Introduction To Many-Body Quantum Theory in Condensed Matter Physics (H.Bruus & K. Flensberg)Document54 pagesSolution of Introduction To Many-Body Quantum Theory in Condensed Matter Physics (H.Bruus & K. Flensberg)Calamanciuc Mihai MadalinNo ratings yet

- AP World History: Islamic Empires and Scientific AdvancementDocument55 pagesAP World History: Islamic Empires and Scientific AdvancementJa'TasiaNo ratings yet

- Irc SP 65-2005 PDFDocument32 pagesIrc SP 65-2005 PDFAjay Kumar JainNo ratings yet

- Classification of Methods of MeasurementsDocument60 pagesClassification of Methods of MeasurementsVenkat Krishna100% (2)

- Gas Chromatography - COLIN F. POOLE 2012 PDFDocument743 pagesGas Chromatography - COLIN F. POOLE 2012 PDFVo Manh Tien100% (1)

- 3240-B0 Programmable Logic Controller (SIEMENS ET200S IM151-8)Document7 pages3240-B0 Programmable Logic Controller (SIEMENS ET200S IM151-8)alexandre jose dos santosNo ratings yet

- Maturity Mode Agile BookDocument110 pagesMaturity Mode Agile BookSai VenkatNo ratings yet

- EasyLogic PM2000 Series - METSEPM2130Document4 pagesEasyLogic PM2000 Series - METSEPM2130ٍJordan SportNo ratings yet

- Capex Vs RescoDocument1 pageCapex Vs Rescosingla.nishant1245No ratings yet

- Alpha Phi Omega National Service Fraternity Strategic PlanDocument1 pageAlpha Phi Omega National Service Fraternity Strategic Planlafay3tteNo ratings yet

- Sheet (1) : An Iron Ring Has A Cross-Sectional Area of 3 CMDocument2 pagesSheet (1) : An Iron Ring Has A Cross-Sectional Area of 3 CMKhalifa MohamedNo ratings yet

- Experimental Investigation On The Properties of Compressed Earth Blocks Stabilised With A Liquid ChemicalDocument7 pagesExperimental Investigation On The Properties of Compressed Earth Blocks Stabilised With A Liquid ChemicalDeb Dulal TripuraNo ratings yet

- Mono - Probiotics - English MONOGRAFIA HEALTH CANADA - 0Document25 pagesMono - Probiotics - English MONOGRAFIA HEALTH CANADA - 0Farhan aliNo ratings yet

- SRS documentation of Virtual Classroom System , SRS documentation of Personal Identity Management ,SRS documentation of EMentoring for women system , SRS Documentation of Employee Performance Management SRS Documentation of Online TicketingDocument79 pagesSRS documentation of Virtual Classroom System , SRS documentation of Personal Identity Management ,SRS documentation of EMentoring for women system , SRS Documentation of Employee Performance Management SRS Documentation of Online Ticketingsaravanakumar1896% (26)

- ĐỀ CƯƠNG ANH 9 - CK2 (23-24)Document7 pagesĐỀ CƯƠNG ANH 9 - CK2 (23-24)thuyhagl2710No ratings yet

- Assessment of Benefits and Risk of Genetically ModDocument29 pagesAssessment of Benefits and Risk of Genetically ModSkittlessmannNo ratings yet

- Löwenstein Medical: Intensive Care VentilationDocument16 pagesLöwenstein Medical: Intensive Care VentilationAlina Pedraza100% (1)

- SMChap 018Document32 pagesSMChap 018testbank100% (8)

- Dwarf Boas of The Caribbean PDFDocument5 pagesDwarf Boas of The Caribbean PDFJohn GamesbyNo ratings yet

- Evolution BrochureDocument4 pagesEvolution Brochurelucas28031978No ratings yet

- Bonding in coordination compoundsDocument65 pagesBonding in coordination compoundsHitesh vadherNo ratings yet

- Unitary Small Air-Conditioners and Air-Source Heat Pumps (Includes Mixed-Match Coils) (RATED BELOW 65,000 BTU/H) Certification ProgramDocument65 pagesUnitary Small Air-Conditioners and Air-Source Heat Pumps (Includes Mixed-Match Coils) (RATED BELOW 65,000 BTU/H) Certification ProgramAmer GaladNo ratings yet

- Table of Contents and Executive SummaryDocument38 pagesTable of Contents and Executive SummarySourav Ojha0% (1)

- Network Theory - BASICS - : By: Mr. Vinod SalunkheDocument17 pagesNetwork Theory - BASICS - : By: Mr. Vinod Salunkhevinod SALUNKHENo ratings yet

- Working With Session ParametersDocument10 pagesWorking With Session ParametersyprajuNo ratings yet