Professional Documents

Culture Documents

Apl 5913

Uploaded by

Aldemir Fernando BattagliaOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Apl 5913

Uploaded by

Aldemir Fernando BattagliaCopyright:

Available Formats

0.8V Reference Ultra Low Dropout (0.

25V@3A) Linear Regulator

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 1

Ultra Low Dropout

- 0.25V(typical) at 3A Output Current

Low ESR Output Capacitor (Multi-layer Chip

Capacitors (MLCC)) Applicable

0.8V Reference Voltage

High Output Accuracy

- 1.5% over Line, Load and Temperature

Fast Transient Response

Adjustable Output Voltage by External

Resistors

Power-On-Reset Monitoring on Both VCNTL and

VIN Pins

Internal Soft-Start

Current-Limit Protection

Under-Voltage Protection

Thermal Shutdown with Hysteresis

Power-OK Output with a Delay Time

Shutdown for Standby or Suspend Mode

Simple SOP-8P Package with Exposed Pad

Lead Free and Green Devices Available

(RoHS Compliant)

Features

The APL5913 is a 3A ultra low dropout linear regulator.

This product is specifically designed to provide well sup-

pl y vol at age f or f ront -si de-bus t er mi nat i on on

motherboards and NB applications. The IC needs two

supply voltages, a control voltage for the circuitry and a

main supply voltage for power conversion, to reduce

power dissipation and provide extremely low dropout.

The APL5913 integrates many functions. A Power-On-Re-

set (POR) circuit monitors both supply voltages to pre-

vent wrong operations. A thermal shutdown and current

limit functions protect the device against thermal and cur-

rent over-loads. A POK indicates the output status with

time delay which is set internally. It can control other con-

verter for power sequence. The APL5913 is enabled by

other power system. Pulling and holding the EN pin be-

low 0.3V shuts off the output.

The APL5913 is available in SOP-8P package which fea-

tures small size as SOP-8 and an Exposed Pad to reduce

the junction-to-case resistance, being applicable in

2~2.4W applications.

Applications

Pin Configuration

SOP-8P (Top View)

General Description

(connected to VIN plane for better heat

dissipation)

= Exposed Pad

Front Side Bus VTT (1.2V/3A)

Note Book PC Applications

Motherboard Applications

1

2

3

4

8

7

6

5

EN

POK

VCNTL

VIN

GND

FB

VOUT

VOUT

VIN

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 2

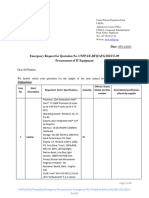

Ordering and Marking Information

Block Diagram

Package Code

KA : SOP-8P

Operating Ambient Temperature Range

C : 0 to 70 C

Handing Code

TR : Tape & Reel

Assembly Material

L : Lead Free Device

G : Halogen and Lead Free Device

APL5913

Handling Code

Temperature Range

Package Code

APL5913

XXXXX

APL5913 KA : XXXXX - Date Code

Assembly Material

o

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which

are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020C for

MSL classification at lead-free peak reflow temperature. ANPEC defines Green to mean lead-free (RoHS compliant) and halogen

free (Br or Cl does not exceed 900ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500ppm by

weight).

GND

VOUT

VIN VCNTL

Current

Limit

Thermal

Limit

EN

VREF

0.8V

FB

90%

VREF

Delay

POK

Power-

On-Reset

Soft-Start

and

Control Logic

0.4V

UV

EAMP

POK

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 3

Typical Application Circuits

1. Using an Output Capacitor with ESR18m

2. Using an MLCC as the Output Capacitor

V

OUT

(V) R1 (k) R2 (k) C1 (pF)

1.05 43 137.6 47

1.5 27 30.86 82

1.8 15 12 150

V

CNTL

+5V

V

OUT

+1.2V / 3A

C

CNTL

1F

V

IN

+1.5V

GND

VOUT

VCNTL

POk

VIN

C

IN

100F

C

OUT

220F

EN

Enable

EN

POk

R3

1k

5

3

6

1

8

7

APL5913

R1

1k

C1

33nF (in the range of 12 ~ 48nF)

VOUT

4

FB

2

R2

2k

V

CNTL

+5V

V

OUT

+1.2V / 3A

C

CNTL

1F

V

IN

+1.5V

GND

VOUT

VCNTL

POk

VIN

C

IN

22F

C

OUT

22F

EN

Enable

EN

POk

R3

1k

5

3

6

1

8

7

APL5913

R1

39k

C1

56pF

VOUT

4

FB

2

R2

78k

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 4

Symbol Parameter Rating Unit

V

CNTL

VCNTL Supply Voltage (VCNTL to GND) -0.3 ~ 7 V

V

IN

VIN Supply Voltage (VIN to GND) -0.3 ~ 3.3 V

V

I/O

EN and FB to GND -0.3 ~ V

CNTL

+0.3 V

V

POK

POK to GND -0.3 ~ 7 V

P

D

Power Dissipation 3 W

T

J

Junction Temperature 150

o

C

T

STG

Storage Temperature -65 ~ 150

o

C

T

SDR

Maximum Lead Soldering Temperature, 10 Seconds 260

o

C

Absolute Maximum Ratings

Thermal Characteristics

Recommended Operating Conditions

Symbol Parameter Value Unit

JA Junction-to-Ambient Thermal Resistance in Free Air

(Note1)

42

o

C/W

JC Junction-to-Case Thermal Resistance in Free Air

(Note 2)

18

o

C/W

Note 1 :

JA

is measured with the component mounted on a high effective thermal conductivity test board in free air. The exposed pad

of SOP-8P is soldered directly on the PCB.

Note 2 : The Thermal Pad Temperature is measured on the PCB copper area connected to the thermal pad of package.

Symbol Parameter Range Unit

V

CNTL

VCNTL Supply Voltage 3.1 ~ 6 V

V

IN

VIN Supply Voltage 1.1 ~ 3.3 V

V

OUT

Output Voltage

V

CNTL

=3.3t5%

V

CNTL

=5.0t5%

0.8 ~ 1.2

0.8 ~ V

IN

-0.2

V

I

OUT

VOUT Output Current 0 ~ 4 A

T

J

Junction Temperature -25 ~ 125

o

C

1

2

3

4

8

7

6

5

VIN

Measured Point

PCB Copper

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 5

Electrical Characteristics

APL5913

Symbol Parameter Test Conditions

Min Typ Max

Unit

SUPPLY CURRENT

I

CNTL

VCNTL Supply Current EN = VCNTL, V

FB

is well regulated 0.4 1 2 mA

I

SD

VCNTL Shutdown Current EN = GND 180 380 A

POWER-ON-RESET

VCNTL POR Threshold V

CNTL

Rising 2.7 2.9 3.1 V

VCNTL POR Hysteresis 0.4 V

VIN POR Threshold V

IN

Rising 0.8 0.9 1.0

VIN POR Hysteresis 0.5 V

OUTPUT VOLTAGE

V

REF

Reference Voltage FB =VOUT 0.8 V

Output Voltage Accuracy I

OUT

=0A ~ 3A, T

J

= -25 ~125

o

C -1.5 +1.5 %

Line Regulation V

CNTL

=3.3 ~ 5.5V -0.13 0 0.13 %/V

Load Regulation I

OUT

=0A ~ 3A 0.06 0.15 %

DROPOUT VOLTAGE

I

OUT

= 3A, V

CNTL

=5V, T

J

= 25

o

C 0.17 0.25 V

Dropout Voltage

I

OUT

= 3A, V

CNTL

=5V, T

J

= -50~125

o

C 0.3 V

PROTECTION

V

CNTL

=5V, T

J

= 25

o

C 4.8 5.7 6.6 A

V

CNTL

=5V, T

J

= -25 ~ 125

o

C 4 A

V

CNTL

=3.3V, T

J

= 25

o

C 4.6 5.5 6.4 A

I

LIM

Current Limit

V

CNTL

=3.3V, T

J

= -25 ~ 125

o

C 3.8 A

T

SD

Thermal Shutdown Temperature T

J

Rising 150

o

C

Thermal Shutdown Hysteresis 50

o

C

Under-Voltage Threshold V

FB

Falling 0.4 V

ENABLE AND SOFT-START

EN Logic High Threshold Voltage V

EN

Rising 0.3 0.4 0.5 V

EN Hysteresis 30 mV

EN Pin Pull-Up Current EN=GND 10 A

T

SS

Soft-Start Interval 2 ms

POWER OK AND DELAY

V

POK

POK Threshold Voltage for Power

OK

V

FB

Rising 90% 92% 94% V

REF

V

PNOK

POK Threshold Voltage for Power

Not OK

V

FB

Falling 79% 81% 83% V

REF

POK Low Voltage POK sinks 5mA 0.25 0.4 V

T

DELAY

POK Delay Time 1 3 10 ms

Refer to the typical application circuit. These specifications apply over, V

CNTL

= 5V, V

IN

= 1.5V, V

OUT

= 1.2V and T

A

= 0

to 70C, unless otherwise specified. Typical values refer to T

A

= 25C.

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 6

4.5

4.6

4.7

4.8

4.9

5

5.1

5.2

5.3

5.4

5.5

-50 -25 0 25 50 75 100 125

0

50

100

150

200

250

0.0 0.5 1.0 1.5 2.0 2.5 3.0

0

50

100

150

200

250

300

350

400

450

0.0 0.5 1.0 1.5 2.0 2.5 3.0

0.0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1.0

-50 -25 0 25 50 75 100 125

Typical Operating Characteristics

VCNTL Supply Current vs.

Junction Temperature

V

C

N

T

L

S

u

p

p

l

y

C

u

r

r

e

n

t

,

I

C

N

T

L

(

m

A

)

Junction Temperature (C)

V

CNTL

=3.3V

V

CNTL

=5V

Current-limit vs.

Junction Temperature

C

u

r

r

e

n

t

-

l

i

m

i

t

,

I

L

I

M

(

A

)

Junction Temperature (C)

V

CNTL

=3.3V

V

CNTL

=5V

Dropout Voltage vs. Output Current

Dropout Voltage vs. Output Current

D

r

o

p

o

u

t

V

o

l

t

a

g

e

(

m

V

)

D

r

o

p

o

u

t

V

o

l

t

a

g

e

(

m

V

)

Output Current, lOUT(A) Output Current, lOUT(A)

V

CNTL

=3.3V

V

OUT

=1.2V

V

CNTL

=5V

V

OUT

=1.2V T

J

=125C

T

J

=75C

T

J

=25C

T

J

=0C

T

J

=-25C

T

J

=125C

T

J

=75C

T

J

=25C

T

J

=0C

T

J

=-25C

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 7

-70

-60

-50

-40

-30

-20

-10

0

100 1000 10000 100000 1000000

2.5

2.7

2.9

3.1

3.3

3.5

3.7

3.9

4.1

4.3

4.5

-50 -25 0 25 50 75 100 125

0.792

0.794

0.796

0.798

0.800

0.802

0.804

0.806

0.808

-50 -25 0 25 50 75 100 125

Typical Operating Characteristics

Junction Temperature (C) Junction Temperature (C)

Reference Voltage vs.

Junction Temperature

R

e

f

e

r

e

n

c

e

V

o

l

t

a

g

e

,

V

R

E

F

(

m

V

)

POK Delay Time vs.

Junction Temperature

P

O

K

D

e

l

a

y

T

i

m

e

(

m

s

)

V

CNTL

=3.3V

V

CNTL

=5V

-60.00

-50.00

-40.00

-30.00

-20.00

-10.00

0.00

100 1000 10000 100000 1000000

Frequency (Hz)

R

i

p

p

l

e

R

e

j

e

c

t

i

o

n

(

d

B

)

VCNTL PSRR

V

CNTL

= 4.5V~5.5V

V

IN

= 1.5V

V

OUT

= 1.2V

I

OUT

= 3A

C

IN

= 100F

C

OUT

= 330F(ESR=30m)

A

m

p

l

i

t

u

d

e

(

d

B

)

VIN PSRR

Frequency (Hz)

V

CNTL

= 5V

V

IN

= 1.5V(lower bound)

V

INPK

-PK = 100mV

C

IN

= 47F

C

OUT

= 330F(30m)

I

OUT

= 3A

V

OUT

= 1.2V

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 8

Operating Waveforms

1. Load Transient Response :

1.1 Using an Output Capacitor with ESR18m

- C

OUT

= 220F/6.3V (ESR = 30m), CIN = 100F/6.3V

- I

OUT

= 10mA to 3A to 10mA, Rise time = Fall time = 1s

I

OUT

= 10mA ->3A I

OUT

= 10mA -> 3A ->10mA I

OUT

= 3A ->10mA

V

OUT

I

OUT

V

OUT

I

OUT

V

OUT

I

OUT

Ch1 : V

OUT

, 50mV/Div

Ch2 : I

OUT

, 1A/Div

Time : 2s/Div

Ch1 : V

OUT

, 50mV/Div

Ch2 : I

OUT

, 1A/Div

Time : 20s/Div

Ch1 : V

OUT

, 50mV/Div

Ch2 : I

OUT

, 1A/Div

Time : 2s/Div

R1=1k, R2=2k, C1=33nF R1=1k, R2=2k, C1=33nF

11

22

+5V

C3

1F

C4

470F x2

C5

1000F x2

L2

3.3H

Q1

APM2014N

UGATE

LGATE

4

VCC

5

GND

3

OCSET

7

PHASE

8

Q2

APM2014N

C2

1F

2

U2

APW7057

FB

6

BOOT

1

D1

1N4148

R7

2k

C7

0.1F

R5

1.75k

R8

8.2k

C6

0.1F

Q3

Shutdown

R6

0

R4

2.2

C8

470pF

L1

1H

C9

47F

VCNTL

+5V

VOUT

+1.2V/3A

CVCNTL

1F

VIN

+1.5

V

GND

VOUT

VCNTL

POK

VIN

C

IN

100F

COUT

220F

EN

Enable

EN

POK

R3

1k 7

3

6

1

8

5

U1

APL5913

R1

1k

C1

33nF

VOUT

4

FB

2

R2

2k

Test Circuit

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 9

Ch1

Ch2

Ch3

Ch4

Power OFF

VIN

VOUT

VPOK

VCNTL

Ch1

Ch2

Ch3

Ch4

Power OFF

VIN VIN

VOUT VOUT

VPOK VPOK

VCNTL VCNTL

Operating Waveforms (Cont.)

2. Power ON and Power OFF :

- V

IN

= 1.5V, V

CNTL

= 5V,V

OUT

= 1.2V

- C

OUT

= 220F/6.3V (ESR = 30m), C

IN

= 100F/6.3V, R

L

=1

Power ON

V

IN

V

OUT

V

CNTL

V

POK

Ch1

Ch2

Ch3

Ch4

Ch1 : V

IN

, 1V/div

Ch2 : V

OUT

, 1V/div

Ch3 : V

POK

, 1V/div

Ch4 : V

CNTL

, 2V/div

Time : 10ms/div

1.2 Using a MLCC as the Output Capacitor

- C

OUT

= 22F/6.3V (ESR = 3m), C

IN

= 22F/6.3V

- I

OUT

= 10mA to 3A to 10mA, Rise time = Fall time = 1s

I

OUT

= 10mA ->3A I

OUT

= 10mA -> 3A ->10mA I

OUT

= 3A ->10mA

V

OUT

I

OUT

V

OUT

I

OUT

V

OUT

I

OUT

Ch1 : V

OUT

, 100mV/Div

Ch2 : I

OUT

, 1A/Div

Time : 2s/Div

Ch1 : V

OUT

, 100mV/Div

Ch2 : I

OUT

, 1A/Div

Time : 20s/Div

Ch1 : V

OUT

, 100mV/Div

Ch2 : I

OUT

, 1A/Div

Time : 2s/Div

11

22

11

22

11

22

R1=39k, R2=78k

C1=56pF

R1=39k, R2=78k

C1=56pF

Ch1 : V

IN

, 1V/div

Ch2 : V

OUT

, 1V/div

Ch3 : V

POK

, 1V/div

Ch4 : V

CNTL

, 2V/div

Time : 10ms/div

V

IN

V

OUT

V

CNTL

V

POK

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 10

Operating Waveforms (Cont.)

POK Delay

Ch1

Ch2

Ch3

VIN

VOUT

VPOK

POK Delay

Ch1

Ch2

Ch3

VIN VIN

VOUT VOUT

VPOK VPOK

4. POK Delay :

- V

IN

= 1.5V, V

CNTL

= 5V,V

OUT

= 1.2V

- C

OUT

= 220F/6.3V (ESR = 30m), C

IN

= 100F/6.3V, R

L

=1

Ch1

Ch2

Ch3

Ch4

Shutdown

VEN

VOUT

IOUT

VPOK

Ch1

Ch2

Ch3

Ch4

Shutdown

VEN VEN

VOUT VOUT

IOUT IOUT

VPOK VPOK

3. Shutdown and Enable :

- VIN = 1.5V, VCNTL = 5V,VOUT = 1.2V

- C

OUT

= 220F/6.3V (ESR = 30m), C

IN

= 100F/6.3V, R

L

=1

Ch1

Ch2

Ch3

Ch4

Enable

VEN

VOUT

IOUT

VPOK

Ch1

Ch2

Ch3

Ch4

Enable

VEN VEN

VOUT VOUT

IOUT IOUT

VPOK VPOK

Ch1 : V

EN

, 5V/div

Ch2 : V

OUT

, 1V/div

Ch3 : I

OUT

, 1A/div

Ch4 : V

POK

, 1V/div

Time : 1ms/div

Ch1 : V

EN

, 5V/div

Ch2 : V

OUT

, 1V/div

Ch3 : I

OUT

, 1A/div

Ch4 : V

POK

, 1V/div

Time : 1ms/div

Ch1 : V

IN

, 1V/div

Ch2 : V

OUT

, 1V/div

Ch3 : V

POK

, 1V/div

Time : 1ms/div

V

POK

V

POK

V

EN

V

EN

V

OUT

V

OUT

I

OUT

I

OUT

V

POK

V

OUT

V

IN

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 11

Functional Pin Description

GND (Pin 1)

Ground pin of the circuitry. All voltage levels are mea-

sured with respect to this pin.

FB (Pin 2)

Connecting this pin to an external resistor divider receives

the feedback voltage of the regulator. The output voltage

set by the resistor divider is determined by:

where R1 is connected from VOUT to FB with Kelvin sens-

ing and R2 is connected from FB to GND. A bypass ca-

pacitor may be connected with R1 in parallel to improve

load transient response.

VOUT (Pin 3,4)

Output of the regulator. Please connect Pin 3 and 4 to-

gether using wide tracks. It is necessary to connect a

output capacitor with this pin for closed-loop compen-

sation and improve transient responses.

VIN (Pin 5) and Exposed Pad

Main supply input pins for power conversions. The Ex-

posed Pad provides a very low impedance input path for

the main supply voltage. Please tie the Exposed Pad and

VIN Pin (Pin 8) together to reduce the dropout voltage. The

voltage at this pins is monitored for Power-On-Reset

purpose.

Function Description

Power-On-Reset

A Power-On-Reset (POR) circuit monitors both input volt-

ages at VCNTL and VIN pins to prevent wrong logic

controls. The POR function initiates a soft-start process

after the two supply voltages exceed their rising POR

threshold voltages during powering on. The POR func-

tion also pulls low the POK pin regardless the output

voltage when the VCNTL voltage falls below its falling

POR threshold.

(V)

VCNTL (Pin 6)

Power input pin of the control circuitry. Connecting this

pin to a +5V (recommended) supply voltage provides

the bias for the control circuitry. The voltage at this pin is

monitored for Power-On-Reset purpose.

POK (Pin 7)

Power-OK signal output pin. This pin is an open-drain

output used to indicate status of output voltage by sens-

ing FB voltage. This pin is pulled low when the rising FB

voltage is not above the V

POK

threshold or the falling FB

voltage is below the V

PNOK

threshold, indicating the output

is not OK.

EN (Pin 8)

Enable control pin. Pulling and holding this pin below 0.

3V shuts down the output. When re-enabled, the IC un-

dergoes a new soft-start cycle. When leave this pin open,

an internal current source 10A pulls this pin up to VCNTL

voltage, enabling the regulator.

Internal Soft-Start

An internal soft-start function controls rising rate of the

output voltage to limit the current surge at start-up. The

typical soft-start interval is about 2ms.

Output Voltage Regulation

An error amplifier works with a temperature- compen-

sated 0.8V reference and an output NMOS regulates out-

put to the preset voltage. The error amplifier is designed

with high bandwidth and DC gain provides very fast tran-

sient response and less load regulation. It compares the

,

_

+

R2

R1

1 0.8 VOUT

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 12

Function Description (Cont.)

Application Information

Power Sequencing

The power sequencing of VIN and VCNTL is not necessary to

be concerned. However, do not apply a voltage to VOUT

for a long time when the main voltage applied at VIN is not

present. The reason is the internal parasitic diode from

VOUT to VIN conducts and dissipates power without pro-

tections due to the forward-voltage.

Output Capacitor

The APL5913 requires a proper output capacitor to

maintain stability and improve transient response over

temperature and current. The output capacitor selection

is to select proper ESR (equivalent series resistance)

and capacitance of the output capacitor for good stability

and load transient response.

reference with the feedback voltage and amplifies the dif-

ference to drive the output NMOS which provides load

current from VIN to VOUT.

Current-Limit

The APL5913 monitors the current via the output NMOS

and limits the maximum current to prevent load and

APL5913 from damages during overload or short-circuit

conditions.

Under-Voltage Protection (UVP)

The APL5913 monitors the voltage on FB pin after soft-

start process is finished. Therefore, the UVP is disable

during soft-start. When the voltage on FB pin falls below

the under-voltage threshold, the UVP circuit shuts off the

output immediately. After a while, the APL5913 starts a

new soft-start to regulate output.

Thermal Shutdown

Output Voltage Regulation (Cont.) For normal operation, device power dissipation should

be externally limited so that junction temperatures will

not exceed +125C.

Enable Control

The APL5913 has a dedicated enable pin (EN). A logic

low signal (V

EN

< 0.3V) applied to this pin shuts down the

output. Following a shutdown, a logic high signal re-en-

ables the output through initiation of a new softstart cycle.

when leave it opens, this pin is pulled up by an internal

current source (10A, typical) to enable operation. Its not

necessary to use an external transistor to save cost.

Power-OK and Delay

The APL5913 indicates the status of the output voltage by

monitoring the feedback voltage (V

FB

) on FB pin. As the

VFB rises and reaches the rising Power-OK threshold

(V

POK

), an internal delay function starts to perform a delay

time. At the end of the delay time, the IC turns off the

internal NMOS of the POK to indicate the output is OK. As

the VFB falls and reaches the falling Power-OK threshold

(V

PNOK

), the IC immediately turns on the NMOS of the POK

to indicate the output is not OK without a delay time.

A thermal shutdown circuit limits the junction temperature of

APL5913. When the junction temperature exceeds +150C,

a thermal sensor turns off the output NMOS, allowing the

device to cool down. The regulator regulates the output again

through initiation of a new soft-start cycle after the junc-

tion temperature cools by 50C, resulting in a pulsed

output during continuous thermal overload conditions.

The thermal shutdown is designed with a 50

o

C hyster-

esis to lower the average junction temperature during

continuous thermal overload conditions, extending life-

time of the device.

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 13

Output Capacitor (Cont.)

The APL5913 is designed with a programmable feedback

compensation adjusted by an external feedback network

for the use of wide ranges of ESR and capacitance in all

applications. Ultra-low-ESR capacitors (such as ceramic

chip capacitors) and low-ESR bulk capacitors (such as

solid Tantalum, POSCap, and Aluminum electrolytic

capacitors) can all be used as an output capacitor. The

value of the output capacitors can be increased without

limit.

During load transients, the output capacitors, depending

on the stepping amplitude and slew rate of load current,

are used to reduce the slew rate of the current seen by

the APL5913 and help the device to minimize the variations

of output voltage for good transient response. For the

applications with large stepping load current, the low-

ESR bulk capacitors are normally recommended.

Decoupling ceramic capacitors must be placed at the load

and ground pins as close as possible and the impedance

of the layout must be minimized.

Input Capacitor

The APL5913 requires proper input capacitors to supply

current surge during stepping load transients to prevent

the input rail from dropping. Because the parasitic in-

ductor from the voltage sources or other bulk capacitors

to the VIN pin limit the slew rate of the surge currents,

more parasitic inductance needs more input capacitance.

Ul tra-l ow-ESR capaci tors (such as cerami c chi p

capacitors) and low-ESR bulk capacitors (such as solid

tantalum, POSCap, and Aluminum electrolytic capacitors)

can all be used as an input capacitor of VIN. For most of

applications, the recommended input capacitance of VIN

is 10F at least. If the drop of the input voltage is not

cared, the input capacitance can be less than 10F. More

capacitance reduces the variations of the input voltage of

VIN pin.

Feedback Network

Figure 1 shows the feedback network among VOUT, GND,

VERR

VFB

R1

R2

C1

VOUT

FB

VOUT

VREF

EAMP

APL5913

COUT

ESR

Figure 1

Condition 1 : Large ESR ( 18m )

- Select the R1 in the range of 400 ~ 2.4k

- Calculate the R2 as the following :

- Calculate the C1 as the following :

Condition 2 : Middle ESR

- Calculate the R1 as the following:

and FB pins. It works with the internal error amplifier to

provide proper frequency response for the linear regulator.

The ESR is the equivalent series resistance of the output

capacitor. The C

OUT

is ideal capacitance in the output

capacitor. The V

OUT

is the setting of the output voltage.

The feedback network selection depends on the values

of the ESR and C

OUT

which has been classified into three

conditions:

Application Information (Cont.)

Select a proper R1(selected) to be a little larger than

the calculated R1.

- Calculate the C1 as the following :

Where R1=R1(selected)

Select a proper C1(selected) to be a little smaller

than the calculated C1.

- The C1 calculated from equation (4) must meet

the following equation:

(1) ..........

0.8(V) - (V) V

0.8(V)

) R1(k ) R2(k

OUT

(2) ......

) R1(k

(V) V

40 C1(nF)

) R1(k

(V) V

10

OUT OUT

(3) ......... 15 (V) V 37.5

) ESR(m

2157

) R1(k OUT +

[ ] (4) ........

) R1(k

F) ( C

101 ) ESR(m 0.71 C1(pF)

OUT

+

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 14

Feedback Network (Cont.) PCB Layout Consideration (See Figure 2)

1. Please solder the Exposed Pad and VIN together on

the PCB. The main current flow is through the ex

posed pad.

2. Please place the input capacitors for VIN and VCNTL

pins near pins as close as possible.

3. Ceramic decoupling capacitors for load must be

placed near the load as close as possible.

4. To place APL5913 and output capacitors near the load

is good for performance.

5. The negative pins of the input and output capaci-tors

and the GND pin of the APL5913 are connected to the

ground plane of the load.

6. Please connect PIN 3 and 4 together by a wide track.

7. Large current paths must have wide tracks.

8. See the Typical Application

(See Figure 2)

- Connect the one pin of the R2 to the GND of APL5913

- Connect the one pin of R1 to the Pin 3 of APL5913

- Connect the one pin of C1 to the Pin 3 of APL5913

Application Information (Cont.)

.(8) F) ( C ) ESR(m

) R1(k

(V) V 1.25

0.033 C1(pF) OUT

OUT

1

]

1

+

(7) ..

) R1(k

(V) V 37.5

1 F) ( C 34.2) ) ESR(m (0.24 C1(pF)

OUT

OUT

1

]

1

+ +

(6) .. (V) V 37.5 F) ( C 300) ) ESR(m (2.1 ) R1(k OUT OUT +

Where R1=R1(calculated) from equation (3)

If the C1(calculated) can not meet the equation (5),

please use the Condition 3.

- Use equation (2) to calculate the R2.

Condition 3 : Low ESR (eg. Ceramic Capacitors)

- Calculate the R1 as the following:

Select a proper R1(selected) to be a little larger than

the calculated R1. The minimum selected R1 is

equal to 1k when the calculated R1 is smaller

than 1k or negative.

- Calculate the C1 as the following :

Where R1=R1(selected)

Select a proper C1(selected) to be a little smaller

than the calculated C1.

- The C1 calculated from equation (7) must meet

the following equation :

Where R1=R1(calculated) from equation (6)

If the C1(calculated) can not meet the equation (8),

please use the Condition 2.

- Use equation (2) to calculate the R2.

The reason to have three conditions described above is

to optimize the load transient responses for all kinds of

the output capacitor. For stability only, the Condition 2,

regardless of equation (5), is enough for all kinds of output

capacitor.

Figure 2

V

CNTL

V

OUT

C

CNTL

V

IN

GND

VOUT

VCNTL

VIN

C

IN

C

OUT

APL5913

R1

C1

VOUT

FB

R2

Load

(5) ..

) R1(k

(V) V 37.5

1

) ESR(m

143

1 7.2 C1(pF)

OUT

1

]

1

+

1

]

1

+

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 15

Application Information (Cont.)

Thermal Consideration

Figure 3

Exposed

Pad Die Top

VIN

plane

PCB

Ambient

Air

118 mil

102 mil

SOP-8-P

5

6

7

8 1

2

3

4

Top

VOUT

plane

Exposed

Pad Die Top

VIN

plane

PCB

Ambient

Air

118 mil

102 mil

SOP-8P

5

6

7

8 1

2

3

4

Top

VOUT

plane

Recommended Minimum Footprint

0

.

2

1

2

0

.

0

7

2

0.050

0.024

1 2 3 4

8 7 6 5

0

.

1

1

8

0.138

Unit : Inch

See Figure 3. The SOP-8P is a cost-effective package fea-

turing a small size like a standard SOP-8 and a bottom

exposed pad to minimize the thermal resistance of the

package, being applicable to high current applications.

The exposed pad must be soldered to the top V

IN

plane.

The copper of the V

IN

plane on the Top layer conducts heat

into the PCB and air. Please enlarge the area to reduce the

case-to-ambient resistance (

CA

).

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 16

Package Information

SOP-8P

0.020

0.010

0.020

0.050

0.006

0.063

MAX.

0.40 L

0

E

e

h

E1

0.25

D

c

b

0.17

0.31

0.016 1.27

0.50

1.27 BSC

0.51

0.25

0.050 BSC

0.010

0.012

0.007

MILLIMETERS

MIN.

S

Y

M

B

O

L

A1

A2

A

0.00

1.25

SOP-8P

MAX.

0.15

1.60

MIN.

0.000

0.049

INCHES

D1 2.25 0.098

2.00 0.079 E2

3.50

3.00

0.138

0.118

8

o

0

o

8

o

0

o

h

X

4

5

D

e

E E

1

SEE VIEW

A

c b

D1

E

2

THERMAL

PAD

A

0

L

VIEW A

0

.

2

5

SEATING PLANE

GAUGE PLANE

A

1

A

2

Inter-lead flash and protrusions shall not exceed 10 mil per side.

Note : 1. Follow JEDEC MS-012 BA.

2. Dimension "D" does not include mold flash, protrusions

or gate burrs. Mold flash, protrusion or gate burrs shall not

exceed 6 mil per side .

3. Dimension "E" does not include inter-lead flash or protrusions.

4.80 5.00

5.80 6.20

3.80 4.00

0.244 0.228

0.157 0.150

0.197 0.189

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 17

Carrier Tape & Reel Dimensions

Package Type Unit Quantity

SOP- 8P Tape & Reel 2500

Devices Per Unit

(mm)

A

E

1

A

B

W

F

T

P0

OD0

B

A0

P2

K0

B

0

SECTION B-B

SECTION A-A

OD1

P1

H

T1

A

d

Application A H T1 C d D W E1 F

330.0

2.00

50 MIN.

12.4+2.00

-0.00

13.0+0.50

-0.20

1.5 MIN. 20.2 MIN. 12.00.30 1.750.10 5.50.05

P0 P1 P2 D0 D1 T A0 B0 K0

SOP-8(P)

4.00.10 8.00.10 2.00.05

1.5+0.10

-0.00

1.5 MIN.

0.6+0.00

-0.40

6.400.20 5.200.20 2.100.20

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 18

Test item Method Description

SOLDERABILITY MIL-STD-883D-2003 245C, 5 sec

HOLT MIL-STD-883D-1005.7 1000 Hrs Bias @125C

PCT JESD-22-B, A102 168 Hrs, 100%RH, 121C

TST MIL-STD-883D-1011.9 -65C~150C, 200 Cycles

ESD MIL-STD-883D-3015.7 VHBM > 2KV, VMM > 200V

Latch-Up JESD 78 10ms, 1

tr

> 100mA

Reflow Condition (IR/Convection or VPR Reflow)

Classification Reflow Profiles

Profile Feature Sn-Pb Eutectic Assembly Pb-Free Assembly

Average ramp-up rate

(T

L

to T

P

)

3C/second max. 3C/second max.

Preheat

- Temperature Min (Tsmin)

- Temperature Max (Tsmax)

- Time (min to max) (ts)

100C

150C

60-120 seconds

150C

200C

60-180 seconds

Time maintained above:

- Temperature (T

L

)

- Time (t

L

)

183C

60-150 seconds

217C

60-150 seconds

Peak/Classification Temperature (Tp) See table 1 See table 2

Time within 5C of actual

Peak Temperature (tp)

10-30 seconds 20-40 seconds

Ramp-down Rate 6C/second max. 6C/second max.

Time 25C to Peak Temperature 6 minutes max. 8 minutes max.

Note: All temperatures refer to topside of the package. Measured on the body surface.

Reliability Test Program

t 25 C to Peak

tp

Ramp-up

t

L

Ramp-down

ts

Preheat

Tsmax

Tsmin

T

L

T

P

25

T

e

m

p

e

r

a

t

u

r

e

Time

Critical Zone

T

L

to T

P

Copyright ANPEC Electronics Corp.

Rev. A.7 - Apr., 2008

APL5913

www.anpec.com.tw 19

Table 2. Pb-free Process Package Classification Reflow Temperatures

Package Thickness Volume mm

3

<350

Volume mm

3

350-2000

Volume mm

3

>2000

<1.6 mm 260 +0C* 260 +0C* 260 +0C*

1.6 mm 2.5 mm 260 +0C* 250 +0C* 245 +0C*

2.5 mm 250 +0C* 245 +0C* 245 +0C*

*Tolerance: The device manufacturer/supplier shall assure process compatibility up to and including the

stated classification temperature (this means Peak reflow temperature +0C. For example 260C+0C)

at the rated MSL level.

Table 1. SnPb Eutectic Process Package Peak Reflow Temperatures

Package Thickness Volume mm

3

<350

Volume mm

3

350

<2.5 mm 240 +0/-5C 225 +0/-5C

2.5 mm 225 +0/-5C 225 +0/-5C

Classification Reflow Profiles (Cont.)

Customer Service

Anpec Electronics Corp.

Head Office :

No.6, Dusing 1st Road, SBIP,

Hsin-Chu, Taiwan

Tel : 886-3-5642000

Fax : 886-3-5642050

Taipei Branch :

2F, No. 11, Lane 218, Sec 2 Jhongsing Rd.,

Sindian City, Taipei County 23146, Taiwan

Tel : 886-2-2910-3838

Fax : 886-2-2917-3838

You might also like

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Inverter E171781Document6 pagesInverter E171781Aldemir Fernando BattagliaNo ratings yet

- Report On CpuDocument41 pagesReport On Cpubabu75% (4)

- Microsoft Interview QuestionsDocument17 pagesMicrosoft Interview Questionspavankumar112No ratings yet

- Python Interview QuestionsDocument77 pagesPython Interview Questionsnawrajlekhak84% (19)

- VWorkspace 8.6.3 ReleaseNotesDocument10 pagesVWorkspace 8.6.3 ReleaseNotesRubén J. AguileraNo ratings yet

- Apl 5930Document17 pagesApl 5930zanaturNo ratings yet

- Features General Description: 5A Low Dropout Fast Response Positive Adjustable Regulator and Fixed 3.3VDocument13 pagesFeatures General Description: 5A Low Dropout Fast Response Positive Adjustable Regulator and Fixed 3.3VchoppersureNo ratings yet

- Apl 5336Document20 pagesApl 5336FlavianoSilvaNo ratings yet

- Apl 1084Document12 pagesApl 1084EstebanRuizDiazNo ratings yet

- AZ3842 PWM Controller Data Sheet SummaryDocument13 pagesAZ3842 PWM Controller Data Sheet SummaryEngr Khalid IqbalNo ratings yet

- APW7165Document20 pagesAPW7165Jorge BulacioNo ratings yet

- Single Bilateral Switch: Order CodesDocument11 pagesSingle Bilateral Switch: Order CodesGaryTechNo ratings yet

- Low Dropout Positive Regulator DatasheetDocument9 pagesLow Dropout Positive Regulator DatasheetiammiaNo ratings yet

- Features: 1.5A Low Dropout Fast Response Positive Adjustable Regulator and Fixed 1.8V, 2.5V, 2.85V, and 3.3VDocument15 pagesFeatures: 1.5A Low Dropout Fast Response Positive Adjustable Regulator and Fixed 1.8V, 2.5V, 2.85V, and 3.3VNgười Lương ThiệnNo ratings yet

- Apl 5902Document21 pagesApl 5902kamran latifNo ratings yet

- APL431Document17 pagesAPL431Pravin MevadaNo ratings yet

- Fan 7316Document21 pagesFan 7316sontuyet82No ratings yet

- Universal DC/DC Converter: (Top View)Document11 pagesUniversal DC/DC Converter: (Top View)Engine Tuning UpNo ratings yet

- APW7159ADocument23 pagesAPW7159AVoicu AdrianNo ratings yet

- Features General Description: USB Power-Distribution SwitchesDocument21 pagesFeatures General Description: USB Power-Distribution SwitchesgraynotNo ratings yet

- HCPL 314JDocument14 pagesHCPL 314JonafetsNo ratings yet

- 1.5-A Peak Boost/Buck/Inverting Switching Regulators: FeaturesDocument23 pages1.5-A Peak Boost/Buck/Inverting Switching Regulators: FeaturesReinaldo VergaraNo ratings yet

- La 42102Document8 pagesLa 42102buyadiNo ratings yet

- TOSHIBA Bipolar Linear Integrated Circuit Silicon Monolithic TA48S015,018,025,033,05,09AFDocument12 pagesTOSHIBA Bipolar Linear Integrated Circuit Silicon Monolithic TA48S015,018,025,033,05,09AFTran Minh VuNo ratings yet

- Transition-Mode PFC Controller: 1 FeaturesDocument17 pagesTransition-Mode PFC Controller: 1 Featuresadriancho66No ratings yet

- Uc284xa Uc384xaDocument16 pagesUc284xa Uc384xayusufwpNo ratings yet

- UC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllerDocument15 pagesUC2842B/3B/4B/5B UC3842B/3B/4B/5B: High Performance Current Mode PWM ControllertoajuiceNo ratings yet

- NCP 3063Document20 pagesNCP 3063Roozbeh BahmanyarNo ratings yet

- L 6565Document17 pagesL 6565tatatabuchoNo ratings yet

- Aic 1084-33PMDocument6 pagesAic 1084-33PMluismilenio3111No ratings yet

- WT7514 PDFDocument9 pagesWT7514 PDFle5100kwNo ratings yet

- Ame 1085Document17 pagesAme 1085Eduardo GarcíaNo ratings yet

- MC100EL1648 5 V ECL Voltage Controlled Oscillator Amplifier: DescriptionDocument16 pagesMC100EL1648 5 V ECL Voltage Controlled Oscillator Amplifier: DescriptionHudionoHoodNo ratings yet

- APW7313Document20 pagesAPW7313Gabriel BeguiriztainNo ratings yet

- 6N137 / VO2601 / 11 / VO2630 / 31 / VO4661: High Speed Optocoupler, 10 MBDDocument12 pages6N137 / VO2601 / 11 / VO2630 / 31 / VO4661: High Speed Optocoupler, 10 MBDAndré LuisNo ratings yet

- 8205Document16 pages8205sonytinNo ratings yet

- La 42031Document7 pagesLa 42031Deyby GarciaNo ratings yet

- Uc 3872 DWDocument8 pagesUc 3872 DWCarlos CuebasNo ratings yet

- STRW6252Document15 pagesSTRW6252miltoncgNo ratings yet

- Ap 34063Document10 pagesAp 34063Hoang LeNo ratings yet

- High Speed Optocouplers Single Dual 10 MBdDocument10 pagesHigh Speed Optocouplers Single Dual 10 MBdJan NowakNo ratings yet

- Features General Description: 3A, 12V, Synchronous-Rectified Buck ConverterDocument20 pagesFeatures General Description: 3A, 12V, Synchronous-Rectified Buck ConverterDarien SanchezNo ratings yet

- Datasheet PDFDocument15 pagesDatasheet PDFperro sNo ratings yet

- ACS712 DatasheetDocument15 pagesACS712 DatasheetHernan PorriniNo ratings yet

- Tda 4601Document8 pagesTda 4601Mirko AleksicNo ratings yet

- SSC2001S Application NoteDocument18 pagesSSC2001S Application NoteGerardo Mendez CamarilloNo ratings yet

- ACS714Document15 pagesACS714connect2nsNo ratings yet

- 2.5V and 4.096V Voltage References: Features DescriptionDocument20 pages2.5V and 4.096V Voltage References: Features Descriptionikaro181083No ratings yet

- Datasheet ET1100Document10 pagesDatasheet ET1100Manal FeghaliNo ratings yet

- Load Switch XC8102Document20 pagesLoad Switch XC8102giusqNo ratings yet

- ST3232 Data SheetDocument12 pagesST3232 Data SheetcredioNo ratings yet

- Elevador VoltajeDocument10 pagesElevador VoltajeFernando AugustoNo ratings yet

- Nc7Sbu3157 - Fsau3157 Tinylogic Low Voltage Uhs SPDT Analog Switch With 2V Undershoot ProtectionDocument11 pagesNc7Sbu3157 - Fsau3157 Tinylogic Low Voltage Uhs SPDT Analog Switch With 2V Undershoot ProtectionAgus TabraniNo ratings yet

- Green Mode PWM Controller Ap384XgDocument13 pagesGreen Mode PWM Controller Ap384XgbaphometabaddonNo ratings yet

- AP1117 Datasheet - Regulador 3.3VDocument11 pagesAP1117 Datasheet - Regulador 3.3VDavid Pinto ForeroNo ratings yet

- La 42052Document6 pagesLa 42052Alejandro Borrego DominguezNo ratings yet

- Vishay Semiconductors Optocoupler with Phototransistor Output and Base ConnectionDocument8 pagesVishay Semiconductors Optocoupler with Phototransistor Output and Base ConnectionBrzata PticaNo ratings yet

- Driver Bobina de Encendido VB326SPDocument9 pagesDriver Bobina de Encendido VB326SPteroplasNo ratings yet

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsFrom EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsRating: 3 out of 5 stars3/5 (2)

- MPM3510A r1.0 PDFDocument22 pagesMPM3510A r1.0 PDFAldemir Fernando BattagliaNo ratings yet

- w25q64fw Revd 032513Document96 pagesw25q64fw Revd 032513Aldemir Fernando BattagliaNo ratings yet

- Philips 1969-01 CM3 Radio-Audio-Television 939916106901Document406 pagesPhilips 1969-01 CM3 Radio-Audio-Television 939916106901Aldemir Fernando BattagliaNo ratings yet

- MPM3510A r1.0 PDFDocument22 pagesMPM3510A r1.0 PDFAldemir Fernando BattagliaNo ratings yet

- Turn Off The Inverter Protection - 1453108338292Document14 pagesTurn Off The Inverter Protection - 1453108338292Aldemir Fernando Battaglia86% (7)

- NECMicrocontroller GuideDocument8 pagesNECMicrocontroller GuideAldemir Fernando BattagliaNo ratings yet

- MX25L12873F, 3V, 128Mb, v1.2 PDFDocument98 pagesMX25L12873F, 3V, 128Mb, v1.2 PDFAldemir Fernando BattagliaNo ratings yet

- Audio 1997 02 PDFDocument100 pagesAudio 1997 02 PDFAldemir Fernando BattagliaNo ratings yet

- Cat Luk Repset 2015-16 UsDocument404 pagesCat Luk Repset 2015-16 Usjackvicosa5781No ratings yet

- Bt134 Series e NXPDocument8 pagesBt134 Series e NXPJorge Junior Briceño UrónNo ratings yet

- Dual Synchronous, Step-Down Controller With 5-V and 3.3-V LdosDocument31 pagesDual Synchronous, Step-Down Controller With 5-V and 3.3-V LdosAldemir Fernando BattagliaNo ratings yet

- TCS20DPR Datasheet en 20110207Document7 pagesTCS20DPR Datasheet en 20110207Aldemir Fernando BattagliaNo ratings yet

- Software Updates (New and Changed Functions) Software Updates (New and Changed Functions)Document13 pagesSoftware Updates (New and Changed Functions) Software Updates (New and Changed Functions)Aldemir Fernando BattagliaNo ratings yet

- Positive Voltage Regulator Ics: FeaturesDocument56 pagesPositive Voltage Regulator Ics: FeaturesJabang Aru SaputroNo ratings yet

- Software Updates (New and Changed Functions) Software Updates (New and Changed Functions)Document13 pagesSoftware Updates (New and Changed Functions) Software Updates (New and Changed Functions)Aldemir Fernando BattagliaNo ratings yet

- n25q 64mb 1 8v 65nmDocument81 pagesn25q 64mb 1 8v 65nmAldemir Fernando BattagliaNo ratings yet

- HD Tune Help33Document7 pagesHD Tune Help33Aldemir Fernando BattagliaNo ratings yet

- Panel LG Display Lp156wh4-Tln1 2Document32 pagesPanel LG Display Lp156wh4-Tln1 2Aldemir Fernando BattagliaNo ratings yet

- DMN66D0LDW 7Document5 pagesDMN66D0LDW 7Aldemir Fernando BattagliaNo ratings yet

- 2000 Service Manual PDFDocument1,970 pages2000 Service Manual PDFAldemir Fernando BattagliaNo ratings yet

- High-Speed Complementary MOSFET Power InverterDocument9 pagesHigh-Speed Complementary MOSFET Power InverteropenscribdformeNo ratings yet

- Black and White TV Video Output Applications High-Voltage Switching Applications Driver Stage Audio Amplifier ApplicationsDocument5 pagesBlack and White TV Video Output Applications High-Voltage Switching Applications Driver Stage Audio Amplifier ApplicationsAldemir Fernando BattagliaNo ratings yet

- Color TV Vertical Deflection Output Applications Color TV Class-B Sound Output ApplicationsDocument5 pagesColor TV Vertical Deflection Output Applications Color TV Class-B Sound Output ApplicationsCornelNo ratings yet

- Transistor Specifications and CharacteristicsDocument5 pagesTransistor Specifications and CharacteristicsAldemir Fernando BattagliaNo ratings yet

- 7N60Document8 pages7N60Aldemir Fernando BattagliaNo ratings yet

- AF4502CDocument8 pagesAF4502CbehzadNo ratings yet

- PD1503YVS: Dual N-Channel Enhancement Mode MOSFETDocument7 pagesPD1503YVS: Dual N-Channel Enhancement Mode MOSFETAldemir Fernando BattagliaNo ratings yet

- Data Sheet P2003EVGDocument5 pagesData Sheet P2003EVGEdgar SilveiraNo ratings yet

- Os Lab Manual AimlDocument107 pagesOs Lab Manual Aimlpooja ppNo ratings yet

- Telecommunication Networks 15B11EC611: Dr. Bhagirath Sahu Assistant Professor, JIIT, NoidaDocument26 pagesTelecommunication Networks 15B11EC611: Dr. Bhagirath Sahu Assistant Professor, JIIT, NoidaMOHAMMED FAYEZ KHANNo ratings yet

- 3.4 User InterfaceDocument3 pages3.4 User InterfaceMuhammad BilalNo ratings yet

- SQA Lec 12Document27 pagesSQA Lec 12Laiba FarooqiNo ratings yet

- Fujitsu Lifebook N Series: Bios GuideDocument22 pagesFujitsu Lifebook N Series: Bios GuideRicardo DiazNo ratings yet

- Code Samples Exploring Data Types, Arrays, and Loops in SystemVerilogDocument2 pagesCode Samples Exploring Data Types, Arrays, and Loops in SystemVerilogMohammed Nawaz ShaikNo ratings yet

- LogDocument12 pagesLogJonalyn C.SallesNo ratings yet

- Collection Hashmap PDFDocument3 pagesCollection Hashmap PDFANIL KUMARNo ratings yet

- Practical UML™: A Hands-On Introduction For Developers: Use Case DiagramsDocument17 pagesPractical UML™: A Hands-On Introduction For Developers: Use Case Diagramsapi-3819971100% (1)

- Object-Oriented Programming C++ Exam QuestionsDocument3 pagesObject-Oriented Programming C++ Exam QuestionsRabison ChitrakarNo ratings yet

- 4.7 Integrated Circuitry Transistors and Diodes: B. G. LiptákDocument3 pages4.7 Integrated Circuitry Transistors and Diodes: B. G. LiptákascvNo ratings yet

- EBEC3103 (Topic 9) Circuit TheoryDocument15 pagesEBEC3103 (Topic 9) Circuit TheoryTimon TimNo ratings yet

- Red Hat Enterprise Linux-6-Performance Tuning Guide-En-USDocument91 pagesRed Hat Enterprise Linux-6-Performance Tuning Guide-En-USprashrockNo ratings yet

- Ete All MCQS' in 1 PDF - 1Document204 pagesEte All MCQS' in 1 PDF - 1Kanhaiya SharmaNo ratings yet

- PV 2017 FinalDocument3 pagesPV 2017 FinalUmarShahrozNo ratings yet

- Heavy-duty wheel weighers for trucks up to 220,000 lbsDocument4 pagesHeavy-duty wheel weighers for trucks up to 220,000 lbsNasser Youssouf MahamoudNo ratings yet

- Kompas-3D: More Than 100 NoveltiesDocument61 pagesKompas-3D: More Than 100 Noveltiesmichel frNo ratings yet

- Object Oriented Programming: File I/ODocument20 pagesObject Oriented Programming: File I/OKashif MujeebNo ratings yet

- DNS SECURES THE ABC'SDocument31 pagesDNS SECURES THE ABC'SMgciniNcubeNo ratings yet

- ACS310 Manual PDFDocument346 pagesACS310 Manual PDFJNo ratings yet

- PL/SQL Bulk CollectDocument5 pagesPL/SQL Bulk CollectShaik AmanullahNo ratings yet

- The Fpga As A Flexible and Low-Cost Digital Solution For Wireless Base StationsDocument16 pagesThe Fpga As A Flexible and Low-Cost Digital Solution For Wireless Base StationsozgurNo ratings yet

- Date: 05/11/2023: Dear Sir/MadamDocument8 pagesDate: 05/11/2023: Dear Sir/MadamMohammad Ali ArianNo ratings yet

- VTP Process Photodiodes Spec SheetDocument1 pageVTP Process Photodiodes Spec SheetAlexNo ratings yet

- Hybrid Security Control Panel OperationDocument77 pagesHybrid Security Control Panel OperationErik Alejandro Morales RomeroNo ratings yet

- Com - Jdexpert.virtual64bit LogcatDocument5 pagesCom - Jdexpert.virtual64bit LogcatArjhon Jake CeladesNo ratings yet