Professional Documents

Culture Documents

Arquitectura Basica

Uploaded by

AmeliaTouchCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Arquitectura Basica

Uploaded by

AmeliaTouchCopyright:

Available Formats

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 2 12/03/2011

Arquitectura Bsica de un Computador

Hay dos trminos empleados al referirse al diseo de un computador: arquitectura

(architecture), y organizacin (organization). En la prctica, en el lenguaje espaol se ha

hecho comn su uso como sinnimos.

El trmino organizacin se refiere a la forma como estn conectados los diferentes

elementos fsicos que conforman el computador y por tanto afectan la manera como sta

funciona. Podran tenerse cientos de computadores diferentes, todos ellos utilizando el mismo

procesador. El trmino arquitectura se refiere a la manera como se comporta el

computador desde el punto de vista de un programador. Pueden haber computadoras con

organizacin diferente (una computadora con procesador Intel core 2 duo es diferente a las

antiguas computadoras compatibles Pentium), y sin embargo tener la misma arquitectura, o

por lo menos compatibilidad hacia atrs. Eso trae como ventaja que los programas

desarrollados para la computadora ms antigua, puedan ejecutarse en la computadora ms

moderna.

En ese sentido, un programador slo requiere conocer la arquitectura del computador para

escribir aplicaciones para dicho computador.

Partes de un computador

De la definicin vista antes para el computador, podemos deducir lo siguiente :

Ya que el computador puede ejecutar un programa, debe ser capaz de recordar las

instrucciones de dicho programa, por lo tanto debe contar con memoria.

Debe reconocer instrucciones y ejecutarlas. Al elemento que lee y procesa las

instrucciones se le llama unidad de procesamiento central o CPU (central processing

unit).

Tiene que haber alguna manera de enviarle el programa que deseamos que ejecute, y

debe haber alguna manera de que veamos el resultado. Para ello se deben contar con

dispositivos perifricos de entrada/salida, como por ejemplo el teclado (dispositivo de

entrada de datos), monitor (dispositivo de salida de datos), unidad de disco (dispositivo de

entrada/salida).

Debe existir alguna manera de que el CPU se comunique con los dispositivos perifricos.

El nexo entre stos y el CPU son las interfases de entrada/salida (input/output interfaces).

Todo computador es un circuito secuencial sincrnico, y como tal, debe contar con una

seal de reloj, que acta como el corazn del sistema, haciendo una analoga con el

cuerpo humano.

Como se ver ms adelante, existen memorias que slo almacenan y retienen la informacin

cuando estn energizadas (memorias voltiles), y otras que mantienen la informacin grabada

incluso cuando no estn conectadas a la fuente de alimentacin (memorias no voltiles). Un

computador para funcionar debe contar como mnimo con memoria no voltil (donde estar el

programa inicial que ejecuta el computador al encenderse), y si se van a manipular datos (que

es lo usual) tambin requerir memoria RAM (ms adelante se describe este tipo de

memoria).

En resumen, un computador consta de : memoria no voltil, memoria RAM, CPU, interfases

de entrada/salida, perifricos, y circuito de reloj.

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 3 12/03/2011

Microcontrolador, microprocesador, procesador.

Antes de 1970, el CPU de un computador era un circuito electrnico conformado por varios

circuitos integrados. En la dcada del 70 se fabrica el primer CPU que ocupaba un solo

circuito integrado, y se le denomin microprocesador (microprocessor), y con ese trmino

se conoce hasta el da de hoy a un circuito integrado que contiene nicamente el CPU de un

computador (ejemplos de microprocesadores son: Z80, 8088, 80486).

Al mejorar la tecnologa de fabricacin de circuitos integrados, se crea el microcontrolador

(microcontroller): un circuito integrado (C.I.) que, adems de un CPU, cuenta con memoria

no voltil para almacenar programas, memoria RAM, interfases de entrada/salida y algunos

perifricos. Por ejemplo, el chip 68HC11 de Motorola es un microcontrolador, y el chip

ATmega8 tambin.

Posteriormente, a llegarse a ms de un milln de transistores por circuito integrado, los

fabricantes comienzan a emplear un nuevo trmino: procesador (processor) para definir a un

circuito integrado que adems del CPU incluye otros elementos del computador, pero no

todos. Ejemplo de ello es el procesador Intel Atom N2800 o el Intel core i7-2760QM.

La unidad de procesamiento central (CPU) :

Es la unidad que reconoce un nmero finito de instrucciones, las que lee (de una unidad de

memoria), procesa y ejecuta, y gracias a ello es capaz de ejecutar cualquier algoritmo descrito

en base a estas instrucciones.

Consta de dos elementos fundamentales : la unidad de procesos y la unidad de control.

Unidad de Procesos (Processing Unit):

Es la encargada de efectuar las operaciones aritmticas y lgicas con los operandos de las

instrucciones que as lo requieran. Consta para ello de:

Una o ms unidades aritmtico-lgicas (ALU)

Registros, que proveen almacenamiento interno al CPU

Caminos de comunicacin entre los registros y ALU. Tambin se le suele conocer

como "camino de datos" (datapath).

INTERFASES

E/S

RELOJ

UNIDAD DE

MEMORIA

CPU PERIFERICOS

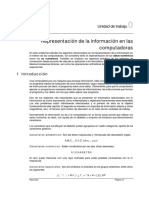

Fig. 1 Estructura bsica de un computador

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 4 12/03/2011

Unidad Aritmtico-lgica ALU (Arithmetic-Logic Unit):

Es un circuito, que puede ser combinacional o secuencial, que efecta operaciones

aritmticas y lgicas. Para ello cuenta con lneas de entrada para los operandos, y de

seleccin para elegir la operacin a realizar. Forma parte de la unidad de procesos.

Unidad de Control (Control Unit):

Es un circuito secuencial encargado de generar las seales de control requeridas para

accesar a la memoria, interfases de E/S, la unidad de procesos (indicndole lo que tiene

que hacer, en cada ciclo de reloj, durante la ejecucin de las instrucciones) y otras partes

del sistema. Este circuito es el que lee las instrucciones y las interpreta.

Tipos de Arquitecturas:

Hay muchas maneras de clasificar las arquitecturas de un computador. Dependiendo de la

manera como el CPU accede a los datos y las instrucciones, se pueden clasificar en dos tipos.

Arquitectura Von Neuman

El CPU no distingue entre memoria de datos y memoria de programa (o tambin denominado

"memoria de instrucciones"). Para el CPU existe una nica memoria en la cual estn tanto las

instrucciones como los datos.

En la figura se muestra un diagrama de bloques de un computador con dicha arquitectura.

Control

ARQUITECTURA VON NEUMAN

Entrada

Salida

Memoria

Unidad de

Procesos

Unidad de

Control

Interface

Entrada/Salida

Reloj

Datos

Control

Instruccin y datos

CPU

datos

instruccin

Fig. 2 Arquitectura Von Neuman

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 5 12/03/2011

Arquitectura Harvard:

En esta arquitectura, el CPU distingue dos tipos de memoria. Una de las cuales lee las

instrucciones, denominada memoria de instrucciones memoria de programa (program

memory), y otra que contiene los datos a utilizar por las instrucciones. En la figura se puede

apreciar el diagrama de bloques de un computador con esta arquitectura. Observar la

presencia de dos caminos independientes para los datos y las instrucciones, que van a

diferentes memorias.

Memoria de

Datos

Memoria de

Instrucciones

Unidad de

Procesos

Unidad de

Control

Entrada/Salida

Reloj

Datos

Control

Control

Datos

Instruccin

ARQUITECTURA HARVARD

salida

entrada

Memoria

Es un dispositivo que almacena informacin de manera binaria. La unidad de almacenamiento

ms pequea se denomina celda de memoria (memory cell) capaz de almacenar un bit de

informacin. Un conjunto de celdas de memoria a las que se puede tener acceso

simultneamente (para leer o escribir) se denomina registro (register).

Cada registro tiene asignado un nico nmero de acceso, denominado direccin (address).

Para que el CPU pueda tener acceso a la informacin almacenada en la memoria, sta debe

contar con lneas por las cuales se pueda leer la informacin almacenada en un registro, o

escribir en ella. A este conjunto de lneas se les denomina lneas de datos (data lines).

Adems, debe contar con lneas de seleccin, para elegir el registro que se desea leer o

escribir.

Estas lneas se denominan lneas de direcciones (address lines).

Adems tambin debe contar con lneas que permitan controlar cuando se desea escribir o leer

la memoria. Estas lneas se denominan lneas de control (control lines).

En la figura 4 se muestra el bosquejo de una memoria de 4 registros, de 4 bits cada uno.

Fig. 3 Arquitectura Harvard

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 6 12/03/2011

Como se indica, cada cuadro representa una celda, en este caso un flip-flop. Tiene cuatro

multiplexores de 4x1 y observar que cada celda va a una nica entrada de un nico

multiplexor, y adems que las lneas de seleccin de los cuatro multiplexores son comunes.

Si por ejemplo, se tuviese en las entradas de las lneas de seleccin 0 y 1 el valor 11, en la

salida D0 se tendr el contenido de la celda superior del registro 3 (bit 0 del registro 3), en la

salida D1 el contenido de la siguiente celda del registro 3 (bit 1 del registro 3), y en la salida

D3 el contenido de la celda inferior del registro 3 (bit 3 del registro 3). Esto se muestra en la

figura 5, donde estn sombreadas las celdas cuya informacin aparece en las salidas.

Para este ejemplo, las lneas de direccin son las lneas de seleccin de los multiplexores (2

lneas), las lneas de datos son las salidas de los multiplexores (D0, D1, D2 y D3) y los

registros son los conjuntos de 4 celdas verticales, como se indica en la figura.

Fig. 4 Memoria de 4x4 bits

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 7 12/03/2011

Fig. 5 Seleccin del contenido del registro 3

A continuacin se definen una serie de trminos utilizados en relacin con las memorias y en

general con las computadoras.

Palabra (word): Es un conjunto de bits de informacin accesados simultneamente.

Byte: Conjunto de 8 bits de informacin.

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 8 12/03/2011

Longitud de palabra (word length): Es el nmero de bits de informacin que almacena un

registro de la memoria. En el caso de memorias de acceso paralelo, stas tendrn un nmero

de lneas de datos igual a la longitud de palabra.

Capacidad de la memoria: Es la cantidad de bits de informacin que es capaz de almacenar

una memoria. O lo que es lo mismo, el nmero total de celdas de memoria con las que cuenta.

Se especifica indicando el nmero de registros con los que cuenta, seguido de la longitud de

palabra (nmero de bits de cada registro), como por ejemplo 32Kx8, que significa que la

memoria tiene una capacidad de 256Kb o lo que es lo mismo 32K registros de 8 bits cada

uno.

Kilobyte (KB): 1024 bytes.

Kilobit (Kb): 1024 bits

Megabyte: 1024 KB (2

10

bytes)

Megabit: 1024 Kb (2

10

bits)

Seal: Es una cantidad elctrica que lleva informacin.

Seal binaria: Aquellas que pueden representar slo dos valores lgicos.

Buses: Grupo de seales binarias que colectivamente transportan un valor numrico, o que

tienen algo en comn.

Modelo de Memoria

Es una representacin grfica de la memoria, en la cual se muestran las direcciones de los

registros de manera consecutiva y el contenido de dichos registros. Cada registro viene

representado por un pequeo rectngulo, cuyo nmero interior representa el valor almacenado

en el registro (su contenido), y el nmero al lado izquierdo fuera del rectngulo la direccin

de dicho registro, o direccin de memoria, como se muestra en el ejemplo de la figura.

Las lneas punteadas indican que hay un grupo de registros con direcciones consecutivas que

no se muestran.

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 9 12/03/2011

$14

$15

$8C

$20

$17

$01

$02

$03

$0021

$1000

$1001

$2016

$2017

$2018

$0020

$0000

$FFFF

MODELO DE MEMORIA

Direcciones

Valores contenidos

en las direcciones de

memoria

Fig. 6 Modelo de memoria

Por ejemplo, el registro con direccin $0020 tiene almacenado el valor $14, y el registro con

direccin $2017 tiene almacenado el valor $02.

El signo $ indica que el nmero est expresado en base 16, por lo que $14 equivale a 20 en

base 10.

Este tipo de representacin es muy til para poder visualizar el contenido de las reas de

inters de la memoria que son accedidas por un programa o instruccin que se quiera analizar.

Tipos de memorias

Existen muchos tipos de memorias, las cuales se pueden clasificar dependiendo de la

tecnologa en base a la cual estn hechas, la manera como se logra el acceso a sus registros,

o la duracin de la informacin almacenada en ellas.

Dependiendo de la duracin de la informacin almacenada en ellas se pueden clasificar en:

Memorias no voltiles (non-volatile memories): Aquellas cuya informacin, una vez

grabada, no se pierde incluso cuando la memoria no est energizada (osea, no est

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 10 12/03/2011

conectada a una fuente de alimentacin). En este grupo estn las memorias ROM, PROM,

EPROM, EEPROM, FLASH EPROM.

Memorias voltiles(volatile memories): Tambin conocidas como memorias RAM

(memorias de acceso aleatorio, del ingls: Random Access Memory). Son memorias en las

que la informacin se pierde cuando se les desconecta la fuente de alimentacin. Estas a

su vez se clasifican en:

memorias estticas (static memories): La informacin almacenada se mantiene

mientras est conectada la fuente de alimentacin. En este grupo estn las

memorias RAM estticas.

memorias dinmicas (dynamic memories): En estas memorias, no basta con

mantener conectada la fuente de alimentacin al chip, sino que se requiere un

proceso denominado de "refresco de memoria" (refresh memory), pues de no

hacerse, se pierde la informacin. Este ciclo de refresco debe realizarse cada 2 a 4

ms como mximo, en cada celda de memoria. Para el refresco se requiere el diseo

de un circuito especial, ya que las memorias no lo hacen automticamente.

Dependiendo de la forma de acceso a la informacin se pueden clasificar en:

Memorias seriales: El acceso a los registros se hace por medio de una lnea de datos

nicamente, de modo que si un registro tiene por ejemplo 8 bits, tienen que hacerse 8

lecturas por esa lnea.

Memorias de acceso paralelo: tal vez deberan de llamarse de acceso aleatorio, pero ese

trmino ya es utilizado para referirse a las memorias voltiles. En el lenguaje comn, a las

memorias de acceso paralelo se les llama simplemente memorias. De hecho, el trmino

"acceso paralelo" no es muy usado, y tampoco del todo adecuado. En estas memorias se

accede simultneamente a todos los bits de un registro. Para ello la memoria cuenta con

lneas de datos (tantos como bits tengan sus registros) y lneas de direcciones.

Dependiendo de si se pueden leer y escribir:

Memorias de slo lectura: Son memorias que una vez instalados en un circuito, slo

pueden leerse, o, de poder escribirse, el tiempo para la escritura es considerable comparado

con el tiempo de lectura. Por dar un ejemplo: para leer el registro de una EEPROM, se

requieren unos 150ns, pero para escribir en un registro se requieren unos 2ms, es decir ms

de diez mil veces el tiempo requerido para la lectura.

Memorias de lectura/escritura: Pueden leerse y escribirse, y el tiempo de acceso para la

lectura y la escritura es del mismo orden de magnitud. Un ejemplo son las memorias RAM

tanto estticas como dinmicas.

MEMORIAS ROM (Read Only Memory)

Son memorias de slo lectura, cuya grabacin se realiza durante el proceso de fabricacin del

circuito integrado, es decir, es el fabricante del chip quien lo programa. El diseador que

requiere la memoria debe indicar al fabricante qu informacin desea grabar. Y deben de

comprarse en el orden de 1000 unidades a ms, todas con la misma informacin grabada.

Adems, el tiempo desde el momento que se solicita la grabacin, hasta que finalmente se

tienen los dispositivos, es de varias semanas (antiguamente varios meses). Por esta razn, se

emplean slo en productos masivos, como los juegos de video. Son los de ms bajo costo, en

relacin con los dems tipos de memorias, cuando se compran en grandes volmenes.

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 11 12/03/2011

Existen memorias de hasta 512Kx8

Existen microcontroladores cuya memoria no voltil es memoria ROM. Estos

microcontroladores son ms baratos que sus equivalentes con otro tipo de memoria no voltil,

pero se venden en grandes volmenes. Los compradores, al momento de hacer el pedido al

fabricante, entregan el programa que deber ser grabado en la memoria ROM, y el fabricante

del microcontrolador los graba durante el proceso de fabricacin. Un ejemplo de este tipo de

microcontrolador es el que tiene la computadora de aplicacin especfica NMY-0020 de la

Ca. New Micros, en el cual se emplea el microcontrolador 68HC11A8, y que en su memoria

ROM tiene grabado un programa monitor.

MEMORIAS PROM (Programmable ROM)

A diferencia de las memorias ROM, stas pueden ser programadas elctricamente (osea,

grabadas), con ayuda de un programador de memorias. Estas memorias se venden sin nada

grabado (memorias en blanco), y es el diseador el que las programa con la informacin que

desea, con ayuda del programador de memorias.

El inconveniente que tienen es que pueden programarse slo una vez, y una vez grabadas no

se pueden borrar.

La razn de ello es que la programacin de sus celdas de memoria con un 1 o un 0 se basa en

quemar o no unos fusibles, y como tales, una vez quemados, no se pueden volver a

reconectar.

Son de baja capacidad (unos 4Kb u 8Kb), pero mucho ms veloces que los dems tipos de

memorias de slo lectura.

Actualmente no se utilizan mucho.

MEMORIAS EPROM (Erasable PROM)

Son memorias que al igual que las PROM, se programan elctricamente, pero adems pueden

borrarse con luz ultravioleta y reprogramarse. Para ello, los encapsulados de estas memorias

cuentan con una pequea ventana transparente poer donde se debe hacer incidir la luz

ultravioleta cuando se desea borrarlas.

Para grabarlas se requiere, al igual que las PROM, de un programador de memorias.

Los fabricantes de estos chips, dan la informacin de cmo programarlas en sus hojas

tcnicas. Y es posible que uno pueda disear su propio circuito grabador de memorias

EPROM.

Ejemplos de este tipo de memorias son el chip de 4Mb AMDF27C040 en un arreglo de

512Kx8 de la Ca. Advance Microdevices, el chip M27C322 de 32Mb con un arreglo de

4Mx8 de la Ca. STMicroelectronics y precio de $12.85 en lotes de 100 unidades ($18.31 c/u

en Marzo del 2007. Fuente http://www.mouser.com Marzo del 2007 y Marzo del 2009), y el

chip M27C512-90F6 de 512Kb con un arreglo de 64Kx8, de la Ca. STMicroelectronics, y

precio de $2.82 c/u ( $1.91 c/u en Marzo del 2009 en lotes de 1000 unidades. Fuente

http://www.em.avnet.com Marzo del 2007 y Marzo del 2009).

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 12 12/03/2011

Debido a que son reprogramables, y de capacidades similares a las memorias ROM, son ms

utilizadas que stas, pues es posible comprarlas por unidad, y a precios econmicos en

grandes volmenes.

Son ms caras que las memorias ROM.

Existe un tipo particular de memoria EPROM que se define a continuacin.

Memorias OTP EPROM (One Time Programmable EPROM):

Son memorias EPROM con un encapsulado que no cuenta con ventana para la

incidencia de luz ultravioleta. Debido a ello, no se pueden borrar, y de all que se

denominen "programables una sola vez". El costo de un encapsulado sin ventana es

menor que el de uno con ventana (en la dcada de los 90, del orden de $1.00) , y ello

influye en el costo final del circuito integrado. Por ello las memorias OTP EPROM

son de menor precio que las EPROM convencionales. Ejemplos de memorias OTP

EPROM son: el chip MR27V6402D de 64Mb en arreglo de 8MBx8 de la Ca. OKI

Semiconductors, el chip M27C512-90B6 de 512Kb con un arreglo de 64Kx8, de la

Ca. STMicroelectronics, y precio de $1.23 c/u en Marzo del 2009 ($0.90 c/u en lotes

de 1000 unidades en Marzo del 2007. Fuente http://www.em.avnet.com Marzo del

2007, Marzo del 2009).

En los microcontroladores que cuentan con memoria EPROM, a la memoria se le

denomina OTP EPROM si el circuito integrado no cuenta con ventana para el borrado

de la misma. La diferencia en precio de un microcontrolador de encapsulado con

ventana y otro sin ventana es significativa. Por ejemplo, el microcontrolador

PIC12C508A/J W-ND de la Ca. Microchip, que cuenta con una memoria EPROM de

512x12, cuesta por unidad $16.00, y por ciento $8.02 c/u. Sin embargo, el

PIC12C508A-04/P-ND, cuya nica diferencia con el anterior es contar con memoria

OTP-EPROM, cuesta por unidad $1.73, y por ciento $0.96 c/u. Es decir, una relacin

de 9 a 1 en el precio. (precios tomados de Ca. Digi-key, Marzo del 2007,

http://www.digi-key.com ).

1

Por ejemplo, el microcontrolador PIC12C508J W-ND de la Ca. Microchip, que cuenta

con una memoria EPROM de 512x12, cuesta por unidad $16.65, y por ciento $8.44

c/u. Sin embargo, el PIC12C508-04/P-ND, cuya nica diferencia con el anterior es

contar con memoria OTP-EPROM, cuesta por unidad $2.05, y por ciento $1.40 c/u. Es

decir, una relacin de 6 a 1 en el precio. (precios tomados de Ca. Digi-key. Pgina

web: www.digi-key.com)

1

La diferencia tan grande en precios de los microcontroladores no es tanto por la existencia o no de la ventana,

sino en los volmenes de produccin y ventas. Como los encapsulados con ventana se usan para la construccin

de prototipos, no se venden tantos y por ello no se fabrican tantos: eso eleva su precio de venta. Para que se

tenga una idea de los volmenes de ventas y su impacto en los precios, en el ao 2004 el microcontrolador

PIC12C508-04/P-ND costaba $2.05 por unidad, ($1.40 c/u por ciento) y en Marzo del 2007 $2.25 por unidad

($1.44 c/u por ciento), es decir, aument en 10% su precio. Pero el microcontrolador PIC12508A-04/P-ND, que

segn el fabricante Microchip es una mejora y reemplaza al anterior , cuesta $1.73 por unidad ($0.93 por

ciento), es decir, cuesta 20% menos. De hecho, disminuy el volumen de ventas del PIC12C508-04/P-ND y la

fabricacin se centra en el nuevo microcontrolador.

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 13 12/03/2011

MEMORIAS EEPROM (Electrically Erasable PROM)

Son memorias que pueden grabarse y borrarse elctricamente. Ms caras que las memorias

EPROM. Estas memorias han sido diseadas para programarse en el circuito en el que van a

ir instaladas, a diferencia de las anteriores, que requieren de un programador de memorias.

Estas memorias pueden borrarse de dos maneras.

En una, mediante un pulso elctrico se borran todas los registros de la memoria. A este

mtodo se le llama "Bulk erase", o borrado en bloque.

En la otra, se selecciona un registro que se desea borrar, y con un pulso elctrico se borra slo

dicho registro, mantenindose la informacion de los dems. Este tipo de borrado se denomina

"Byte erase", debido al hecho que estas memorias normalmente cuentan con registros de 8

bits.

Un ejemplo de memoria de acceso serial es el chip AT24C1024B-PU25 de la compaa

Atmel

2

, que es una memoria EEPROM de acceso serial en un arreglo interno de 128Kx8, y

tiene un precio de $3.91 por unidad y de $2.60 c/u por ciento (fuente:

http://www.digikey.com, Marzo 2009).

Otro ejemplo, de acceso paralelo es el chip AT28C256 de 256Kb, fabricado por la compaa

Atmel, con un arreglo de 32Kx8 y un precio de $5.90 por unidad ($8.99 por unidad el ao

2004. Fuentes: www.jameco.com, Agosto 2004, www.digikey.com Marzo 2009).

Actualmente predominan las memorias EEPROM seriales sobre las EEPROM de acceso

paralelo, pues las de acceso paralelo fueron desplazadas por las memorias Flash. Por ejemplo,

a Marzo del 2007, la memoria paralela 28LV010E-12PI de 1Mb (128Kx8) de la Ca. Atmel,

tiene un precio de $31.93 por unidad, y de $19.30 c/u por ciento (fuente:

http://www.digikey.com Marzo 2007). Una memoria Flash de la misma capacidad, la

AT29B010A-12J U del mismo fabricante, tiene un precio de $2.63 por unidad y $1.638 por

ciento. Ms de 1000% de diferencia. Y para terminar la comparacin, una memoria serial, la

AT24C1024W-10SU-2.7 de 1Mb (128Kx8) tiene un precio de $5.76 por unidad y $3.28 c/u

por ciento (fuente: http://www.digikey.com Marzo 2007).

MEMORIAS FLASH-EPROM (FLASH Memory)

Estas memorias tambin se denominan simplemente memorias Flash.

Al igual que las memorias EEPROM, se programan y borran elctricamente, pero difieren en

los tipos de borrado. Al igual que en las EEPROM, se puede realizar el borrado de todas las

celdas del chip a la vez, es decir, el modo "Bulk erase". Sin embargo, no cuentan con el

borrado registro por registro. Hasta hace unos aos, ese era el nico tipo de borrado con el

que contaban, sin embargo, en la actualidad, las memorias Flash cuentan con un tipo de

borrado por bloques "Block erase" tambin denominado borrado por sectores ("sector erase").

En las memorias con este tipo de borrado, la memoria est dividida en varias partes

denominadas bloques sectores, cada uno con un nmero de registros consecutivos, y se

puede borrar un bloque sin afectar el contenido de los dems bloques. vale la pena resaltar

que al borrar un bloque sector, se borra un grupo de registros y no un nico registro como es

en el caso de las memorias EEPROM.

2

En Agosto del 2004, el circuito integrado que exista era el AT24C1024-10PI-2.7 de la compaa Atmel, que

es una memoria EEPROM de acceso serial en un arreglo interno de 128Kx8, y tena un precio de $8.04 por

unidad y de $6.17 c/u por ciento (fuente: http://www.digikey.com, Agosto 2004).

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 14 12/03/2011

Al igual que las EEPROM, han sido diseadas para no requerir de un programador de

memorias, sino que pueden reprogramarse en el circuito en el que van a ser instalados.

La mayora de fabricantes de estos tipos de memorias, producen chips que requieren de un

circuito especial en la tarjeta en la que van a ir instalados. Pero desde hace unos aos,

aparecieron fabricantes que han desarrollado memorias FLASH que no requieren de circuitos

especiales, y que se conectan como si fuesen memorias EEPROM.

La razn por la cual estas memorias son muy utilizadas, es que al mejorar la tecnologa de

produccin de memorias, las nuevas que aparecen de mayor capacidad, lo son unas 4 veces

ms que las EEPROM de mayor capacidad que se introducen en el mercado.

Ejemplos de uso son las unidades de disco semiconductoras utilizadas en las computadoras

personales porttiles (Notebooks), denominadas FLASH-Disks. Tambin se utilizan en las

tarjetas de memoria de las cmaras digitales como las Sony "Memory Stick's

", y en las

tarjetas de memoria usadas en las agendas electrnicas (las denominadas PDA's), como las

"SD-Memory cards". stas son tarjetas que contienen uno o ms chips de memoria Flash.

Son en la actualidad el tipo de memoria no voltil ms vendido a nivel mundial.

Hay varios tipos de memorias Flash, unas, denominadas NAND Flash, cuyas capacidades

llegan a 1Gb en la actualidad (128MB) como el chip HY27US001G1M-T de la compaa

Hynix Semiconductor, y la otra, de acceso paralelo, cuyas capacidades llegan a 128Mb

(8Mx16). Ejemplos de memorias de acceso paralelo son el chip de memoria Flash EPROM

LH28F320 de 32Mb en arreglo de 4Mx8, de la Ca. Sharp. el AM29LV065 de 64Mb de la

Ca. Advance Micro Devices (AMD), o el M29F010B70K6E de 1Mb (128Kx8) a $1.49 la

unidad (fuente: http://www.em.avnet.com Marzo 2007).

Hasta hace pocos aos, la relacin de precios de menor a mayor, para la misma capacidad de

memoria era: ROM, OTP-EPROM, EPROM, Flash, EEPROM (no se incluyen las memorias

PROM pues prcticamente son una reliquia, y existieron mientras fueron las memorias ms

rpidas). Sin embargo, esto ya cambi (por lo menos para un rango de capacidades) y el orden

de precios, de menor a mayor es: ROM, Flash, OTP-EPROM, EPROM, EEPROM.

Es decir, en ciertos casos es ms barata una memoria Flash que una memoria OTP-EPROM o

EEPROM.

Un ejemplo de microcontrolador con memoria flash es el ATmega8L-8PC de la familia AVR

de Atmel. Este chip puede programarse en el circuito, como se ver en el primer laboratorio

del curso, y tiene un precio de $3.66 por unidad y $2.2464 c/u por ciento (www.digikey.com

Marzo 2010). En Agosto del 2004 el mismo circuito integrado costaba $3.66 por unidad y

$2.13 c/u por ciento; y en Agosto del 2003 el mismo chip costaba $5.05 por unidad y $3.6093

c/u por ciento en el mismo proveedor (Digi-Key).

3

3

Aunque el empleado en el laboratorio es el mencionado, est dejando de fabricarse ese modelo a favor del

ATmega8L-PU cuyo precio a Agosto del 2007 es $3.66 por unidad y $2.13 c/u por ciento. La razn del cambio

es para que el circuito integrado no tenga materiales que perjudiquen el medio ambiente. En Europa est vigente

la directiva RoHS 2002/95/EC (Restriction of the Use of certain Hazardous Substances in Electrical and

Electronic Equipment) que prohbe el uso de ciertas sustancias, como el plomo, en la fabricacin de equipos

elctricos o elctrnicos.

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 15 12/03/2011

Lneas de control de las memorias: (todas son lneas de entrada)

Como se indic anteriormente, las memorias cuentan con lneas de control. En el caso de las

memorias de acceso paralelo, algunas de estas lneas son:

Habilitador de chip CE CS (chip enable, chip select)

Cuando esta lnea est activa, se puede tener acceso la memoria por medio de las

dems lneas.

Cuando est inactiva, las lneas de datos permanecen en alta impedancia y no se

puede leer o escribir la memoria.

Habilitador de salida OE (Output enable)

Esta lnea permite efectuar la lectura de un registro.

Cuando est activa, la informacin que hay en el registro seleccionado (mediante

las lneas de direccin) aparece en las lneas de datos.

Cuando est inactiva, las lneas de datos permanecen en alta impedancia.

Escritura WR (write)

Esta lnea, que tienen las memorias de lectura/escritura, se debe activar para

efectuar una escritura en un registro de la memoria (que tiene que ser seleccionado

con las lneas de direccin) . Para ello debe estar presente en las lneas de datos el

valor que se desea escribir en el registro.

En general, no puede leerse y escribirse simultneamente en una memoria, por lo que las

lneas OE y WR jams deben estar activas simultneamente. Adems, ello significara tener

una colisin de informacin.

Los chips de memoria Flash y EEPROM tambin cuentan con lneas de control de escritura.

Pero como se explic anteriormente, son consideradas memorias de slo lectura.

Ejemplo de un chip de memoria de 256Kb, 32Kx8

En la figura se muestra la disposicin de patitas (pin-out) de una memoria EPROM 27C256,

que muestra qu seal corresponde a qu patita del circuito integrado. La presentacin puede

ser en forma de diagrama (diagrama de conexiones) o como una tabla, en la que se indica el

nmero de patita en el chip y la seal que le corresponde. En este caso se muestra como

diagrama de conexiones.

Esta memoria tiene un arreglo de 32Kx8. Es decir, cuenta con 32K registros de 8 bits cada

uno. Pero 32K =2

5

*2

10

=2

15

. Esto significa que se requeren 15 lneas de direcciones para

poder accesar a cualesquiera de los 32K registros. stas son las lneas A0 hasta A14 que

aparecen en la figura.

Como los registros son de 8 bits, se requieren 8 lneas de datos para leer simultneamente el

contenido de todas las celdas de memoria de un registro. stas son las lneas DQ0 hasta DQ7

que aparecen en el diagrama.

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 16 12/03/2011

Como es una memoria EPROM, que es de slo lectura, debe contar con las lneas de control

de habilitacin de chip, y de habilitacin de salidas. stas lneas son CE#y OE#de la figura

respectivamente.

Las lneas Vcc y Vss son las de la fuente de alimentacin de 5V (Vcc terminal positivo).

Vpp es una lnea de programacin, que slo se utiliza para programar la memoria en un

equipo programador de memorias EPROM. Esta lnea en un computador debera estar

conectada al pin Vcc.

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 17 12/03/2011

Fig. 1 Diagrama de Bloques

Fig. 2 Diagrama de Conexiones

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 18 12/03/2011

El CPU y los buses de datos, de direcciones y de control

El CPU de un computador requiere acceder a dispositivos de memorias donde estn tanto los

programas que debe ejecutar como los datos a procesar. Por lo tanto, los CPUs deben contar

con lneas que permitan su fcil conexin a las memorias. Estas se describen a continuacin.

Bus de datos: Es el conjunto de lneas por donde el CPU enva o recibe datos. Un CPU

puede tener ms de un bus de datos, dependiendo de su arquitectura.

Bus de direcciones: Es el conjunto de lneas por medio de las cuales el CPU indica qu

nmero de registro desea acceder para su lectura o escritura.

Bus de control: Se denomina as al conjunto de todas las lneas de control con que cuenta el

CPU para poder controlar el acceso a los dispositivos de memoria, interfases de

entrada/salida, y otros elementos especiales con los que puede contar un computador.

Tambin se les conoce simplemente como lneas de control.

Observacin:

Realmente los tres trminos anteriores deberan ser lneas de datos, lneas de direcciones y

lneas de control. En la prctica, es comn llamarlos buses, pues necesariamente estas lneas

se conectarn a los dems dispositivos que forman el computador, y por tanto esas lneas

conectadas formarn buses.

CPU de n bits: Una caracterstica importante de un CPU es el nmero de lneas de datos

con las que cuenta, pues ello significar acceder a mayor o menor informacin (nmero de

bits) en el mismo tiempo. Se dice que un CPU es de "n" bits cuando cuenta con "n" lneas de

datos. Si el CPU es de arquitectura Harvard, entonces se refiere a las lneas de datos utilizadas

para transferir informacin de la memoria de datos a los registros del CPU.

Por ejemplo, el ATmega8 que tiene arquitectura Harvard, cuenta con dos buses de datos. Uno

de 16 bits para la memoria de instrucciones, y otro de 8 bits para la memoria de datos. En este

caso, este microcontrolador tiene un CPU de 8 bits.

Como ejemplos de arquitectura Von Neuman tenemos al microcontrolador 68HC11, que tiene

un CPU de 8bits; el microprocesador 8088 con un CPU de 16 bits, a pesar que externamente

slo cuente con 8 lneas de datos (internamente el bus de datos es de 16 bits); y el 8086 que

tiene el mismo CPU que el 8088 (de 16 bits) pero externamente tambin cuenta con 16 lneas

de datos.

Rango de direccionamiento del CPU:

Para poder acceder a "2

N

" registros de una memoria, se requieren N bits para identificar sin

ambigedad a cada registro. Por lo tanto se requieren N lneas de direcciones. Por ello,

cuando un CPU tiene N lneas de direcciones, se dice que su capacidad de direccionamiento

es de 2

N

registros.

Por ejemplo, el CPU del 68HC11 tiene 16 lneas de direcciones, por lo tanto tiene un rango de

direccionamiento de 2

16

registros 64K.

El 8088 tiene 20 lneas de direcciones, por lo que su capacidad de direccionamiento es de 1M.

Es comn que en vez de registro se indique la capacidad de cada uno. En los ejemplos

anteriores se dira que el Z80 puede direccionar 64KB y el 8088 1MB.

Curso: Sistemas Digitales

Especialidad: Ing. Electrnica Profesor: Ing. Hugo Pratt

Pontificia Universidad Catlica del Per rea de circuitos y sistemas

Captulo1Parte1 rev. 8 19 12/03/2011

En el caso del microcontrolador ATmega8, que tiene arquitectura Harvard, se tienen dos

rangos de direccionamiento: para la memoria de programa el rango de direccionamiento es de

4K registros de 16 bits, y para la memoria de datos es de 1KB.

Lista de trminos

1. Arquitectura de un computador

2. Organizacin de un computador

3. Memoria

4. CPU

5. microprocesador

6. perifrico

7. interfaz, interfaces

8. Unidad de procesos

9. Unidad de control

10. ALU

11. registro del CPU

12. Arquitectura Von Neuman

13. Arquitectura Harvard

14. memoria de instrucciones, memoria de

programa

15. memoria de datos

16. microcontrolador

17. registro de memoria

18. celda de memoria

19. direccin de memoria

20. lneas de datos

21. lneas de direcciones

22. lneas de control de memoria

23. Palabra

24. Byte

25. Longitud de palabra

26. capacidad de una memoria

27. kilobyte KB

28. kilobit Kb

29. megabyte MB

30. megabit Mb

31. seal

32. seal binaria

33. buses

34. modelo de memoria

35. memorias no voltiles

36. memorias voltiles

37. memoria RAM

38. memorias estticas (SRAM)

39. memorias dinmicas (DRAM)

40. memorias seriales

41. memorias de acceso paralelo

42. memorias de solo lectura

43. memorias de lectura/escritura

44. memoria ROM

45. memoria PROM

46. memoria EPROM

47. memoria OTP-EPROM

48. memoria EEPROM

49. memoria Flash

50. habilitador de chip CE de las memorias

51. habilitador de salida OE de las memorias

52. lnea de escritura WR de las memorias

53. Bus de datos

54. Bus de direcciones

55. Bus de control

56. CPU de n bits

57. Rango de direccionamiento de un CPU

You might also like

- Tiristores y Triacs 2Document61 pagesTiristores y Triacs 2AmeliaTouchNo ratings yet

- Sesion 1Document28 pagesSesion 1Roger Elias Casanova CorreaNo ratings yet

- Electronica de Potencia PolifasicaDocument16 pagesElectronica de Potencia PolifasicaAmeliaTouchNo ratings yet

- Control AvanzadoDocument7 pagesControl AvanzadoAmeliaTouchNo ratings yet

- 78Document30 pages78jrbermudNo ratings yet

- Separata Nro 4 FasoresDocument8 pagesSeparata Nro 4 Fasoresmartin190386No ratings yet

- 1 Estrategia S DecontrolDocument27 pages1 Estrategia S DecontrolAmeliaTouchNo ratings yet

- Im 006Document3 pagesIm 006Christopher RoblesNo ratings yet

- Diagnóstico de Fallas en Intercambiadores de Calor: Enfoque Multi-ModelosDocument6 pagesDiagnóstico de Fallas en Intercambiadores de Calor: Enfoque Multi-ModelosAmeliaTouchNo ratings yet

- Inform Á TicaDocument5 pagesInform Á TicaMERY DOMINGUEZNo ratings yet

- Cadena ElectroacusticaDocument16 pagesCadena Electroacusticarudyzapetah11No ratings yet

- Electronica Digital 1bgu 2022-2023Document34 pagesElectronica Digital 1bgu 2022-2023Victor Felix Mora Moran100% (1)

- Ebook Masterizacion Audiocursosweb 1 PDFDocument49 pagesEbook Masterizacion Audiocursosweb 1 PDFMymmusicpro Estudiourbano100% (1)

- Capítulo 3 - Tipos de Datos y Expresiones en C PDFDocument23 pagesCapítulo 3 - Tipos de Datos y Expresiones en C PDFRholvis BritoNo ratings yet

- ASI Administracion de Sistemas Informaticos McGraw Hill Redes de Area Local RAL El LibroDocument220 pagesASI Administracion de Sistemas Informaticos McGraw Hill Redes de Area Local RAL El LibroluisNo ratings yet

- 3 Arquitectura Interna Del PLCDocument41 pages3 Arquitectura Interna Del PLCRicardo Gutierrez HdzNo ratings yet

- CDP2P4E1Document7 pagesCDP2P4E1Luis Fernando Cortez PeñuelasNo ratings yet

- Hoja de Datos - Mul2b With SelectDocument6 pagesHoja de Datos - Mul2b With SelectAlejandro BarajasNo ratings yet

- Conexión A Ethernet Del dsPIC30F4013 (Ver 2.0)Document77 pagesConexión A Ethernet Del dsPIC30F4013 (Ver 2.0)Sergio Date FugitaNo ratings yet

- 1 Apunte Introducción Al PLC Delta Pag 1 A 18Document18 pages1 Apunte Introducción Al PLC Delta Pag 1 A 18Maximo GamaNo ratings yet

- Unidad 2Document10 pagesUnidad 2guillermoNo ratings yet

- Inf Labor 4Document6 pagesInf Labor 4Jonathan LiscanoNo ratings yet

- Funcionamiento Del ComputadorDocument3 pagesFuncionamiento Del ComputadorERIKA YULIETH IBARRA HIGUITANo ratings yet

- Arquitecturas Paralelas y DistribuidasDocument32 pagesArquitecturas Paralelas y DistribuidasgigipaezespinosaNo ratings yet

- infoPLC - Net - Configuracic3b3n y Puesta en Marcha de Una Red Mpi PDFDocument15 pagesinfoPLC - Net - Configuracic3b3n y Puesta en Marcha de Una Red Mpi PDFSergio Mudarra ChavezNo ratings yet

- Comunicacion Serial PicDocument6 pagesComunicacion Serial Picjose_suarez_suxeNo ratings yet

- Contador Síncrono PDFDocument4 pagesContador Síncrono PDFZeider MartinNo ratings yet

- Vag Com Golf mk5 CodificacionesDocument11 pagesVag Com Golf mk5 CodificacionesLuis Olivera100% (1)

- Timer PWMDocument9 pagesTimer PWMIngeniero Jeffer Maya SanchezNo ratings yet

- Convertidores ADDocument9 pagesConvertidores ADEmanuel CarrilloNo ratings yet

- Mapeo de MemoriasDocument12 pagesMapeo de MemoriasKarlita M.No ratings yet

- Practica 8Document4 pagesPractica 8Carlos Charly XP100% (1)

- Mapas ConceptualesDocument5 pagesMapas ConceptualesRicardo de la ParraNo ratings yet

- Tarea 1 - Sistemas Digitales y PerifericosDocument8 pagesTarea 1 - Sistemas Digitales y PerifericosManuel67% (3)

- Encendido de lámparas con interruptores S7-300Document110 pagesEncendido de lámparas con interruptores S7-300Jose Elias Victorero PaivaNo ratings yet

- Ccna Semestre 1 Examen 1 (100%)Document6 pagesCcna Semestre 1 Examen 1 (100%)Maria Victoria Ortiz LópezNo ratings yet

- Laboratorio 1 uso inicial del lenguaje ensamblador PIC18F4550Document6 pagesLaboratorio 1 uso inicial del lenguaje ensamblador PIC18F4550jsofiabeltranNo ratings yet

- Tipos de Datos en MatlabDocument24 pagesTipos de Datos en MatlabDavid LópezNo ratings yet

- Cortex Vers 3 - Parte 3Document26 pagesCortex Vers 3 - Parte 3Marcelo RomeoNo ratings yet