Professional Documents

Culture Documents

Flip Flop

Uploaded by

Jhonn C Ccopa SupoCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Flip Flop

Uploaded by

Jhonn C Ccopa SupoCopyright:

Available Formats

www.monografias.

com

Circuitos digitales Flip Flops

1. 2. 3. 4. 5. 6. . #. &. Generalidades Flip-Flop Contadores de pulsos Divisores de frecuencia Multiplicadores de frecuencia Comparadores digitales !egistros de despla"amientos Multiple$or % de-multiple$or 'i(liograf)a

G*+*!,-.D,D*/ Una red combinacional es aquella que "combina" compuertas Y, O, Negadas y del 3 Estado. Una secuencial es sta pero realimentada. En las salidas preferiremos llamar a los estados anteriores con letra min!scula "q# para diferenciarlos de los presentes que se $ar% con may!scula "&#, y los de la entrada con may!scula porque siendo presentes, tampoco cambiaron durante la transici'n "( ) *#.

F-.0-F-10 Generalidades +iendo los ,lip-,lop las unidades b%sicas de todos los sistemas secuenciales, e(isten cuatro tipos. el /+, el 01, el 2 y el 3. Y los !ltimos tres se implementan del primero 4pudi ndose con posterioridad con cualquiera de los resultados confeccionar quienquiera de los restantes. 2odos pueden ser de dos tipos, a saber. ,lip-,lop acti5ado por ni5el ",,-6N# o bien ,lip-,lop maestro-escla5o ",,-7E#. El primero recibe su nombre por actuar meramente con los "ni5eles" de amplitud 8-9, en cambio el segundo son dos ,,-6N combinados de tal manera que uno "$ace caso" al otro. Un circuito flip-flop puede mantener un estado binario indefinidamente "+iempre y cuando se le este suministrando potencia al circuito# $asta que se cambie por una se:al de entrada para cambiar estados. ;a principal diferencia entre 5arios tipos de flip-flops es el numero de entradas que poseen y la manera en la cual las entradas afecten el estado binario. Circuito (2sico de un flip-flop +e menciono que un circuito flip-flop puede estar formado por dos compuertas N6N3 o dos compuertas NO/. Estas construcciones se muestran en los diagramas l'gicos de las figuras. <ada circuito forma un flip-flop b%sico del cual se pueden construir uno mas complicado. ;a cone(i'n de acoplamiento intercru=ado de la salida de una compuerta a la entrada de la otra constituye un camino de retroalimentaci'n. >or esta ra='n, los circuitos se clasifican como circuitos secuenciales asincr'nicos. <ada flip-flop tiene dos salidas, & y &? y dos entradas + "set# y / "reset#. Este tipo de flip-flop se llama ,lip-,lop /+ acoplado directamente o bloqueador +/ "+/ latc$#. ;as letras / y + son las iniciales de los nombres en ingl s de las entradas "reset, set#. Circuito flip-flop (2sico con compuertas +1! >ara anali=ar la operaci'n del circuito de la figura anterior se debe recordar que la salida de una compuerta NO/ es 8 si cualquier entrada es 9 y que la salida es 9 solamente cuando todas las entradas sean 8. <omo punto de partida as!mase que la entrada de puesta a uno "set# es 9 y que la

entrada de puesta a 8 "reset# sea 8. <omo la compuerta @ tiene una entrada de 9, su salida &? debe ser 8, lo cual coloca ambas entradas de la compuerta 9 a 8 para tener la salida & como 9. <uando la entrada de puesta a uno "set# 5uel5a a 8, las salidas permanecer%n iguales ya que la salida & permanece como 9, deAando una entrada de la compuerta @ en 9. Esto causa que la salida &? permane=ca en 8 lo cual coloca ambas entradas de la compuerta n!mero 9 en 8 y asB la salida & es 9. 3e la misma manera es posible demostrar que un 9 en la entrada de puesta a cero "reset# cambia la salida & a 8 y &? a 9. <uando la entrada de puesta a cero cambia a 8, las salidas no cambian. <uando se aplica un 9 a ambas entradas de puesta a uno y puesta a cero ambas salidas & y &? 5an a 8. Esta condici'n 5iola el $ec$o de que las salidas & y &? son complementos entre si. En operaci'n normal esta condici'n debe e5itarse asegur%ndose que no se aplica un 9 a ambas entradas simult%neamente. Un flip-flop tiene dos entradas !tiles. <uando &)9 y &?)8 estar% en el estado de puesta a uno "o estado 9#. <uando &)8 y &?)9 estar% en el estado de puesta a cero "o estado 8#. ;as salidas & y &? son complementos entre si y se les trata como salidas normales y de complemento respecti5amente. El estado binario de un flip-flop se toma como el 5alor de su salida normal. CaAo operaci'n normal, ambas entradas permanecen en 8 a no ser que el estado del flip-flop $aya cambiado. ;a aplicaci'n de un 9 moment%neo a la entrada de puesta a uno causar% que el flip-flop 5aya a ese estado. ;a entrada de puesta en uno debe 5ol5er a cero antes que se aplique un uno a la entrada de puesta a cero. Un 9 moment%neo aplicado a la entrada de puesta a cero causar% que el flip-flop 5aya al estado de borrado "o puesta a cero#. <uando ambas entradas son inicialmente cero y se aplica un 9 a la entrada de puesta a uno o se aplica un 9 a la entrada de puesta a cero mientras que el flip-flop este borrado, quedaran las salidas sin cambio. <uando se aplica un 9 a ambas entradas de puesta a uno y puesta a cero, ambas salidas ir%n a cero. Este estado es indefinido y se e5ita normalmente. +i ambas salidas 5an a 8, el estado del flip-flop es indeterminado y depende de aquella entrada que permane=ca por mayor tiempo en 9 antes de $acer la transici'n a cero. Circuito flip-flop (2sico con compuertas +,+D El circuito b%sico N6N3 de la figura anterior opera con ambas entradas normalmente en 9 a no ser que el estado del flip-flop tenga que cambiarse. ;a aplicaci'n de un 8 moment%neo a la entrada de puesta a uno, causar% que & 5aya a 9 y &? 5aya a 8, lle5ando el flip-flop al estado de puesta a uno. 3espu s que la entrada de puesta a uno 5uel5a a 9, un 8 moment%neo en la entrada de puesta a cero causar% la transici'n al estado de borrado "clear#. <uando ambas entradas 5ayan a 8, ambas salidas ir%n a 9D esta condici'n se e5ita en la operaci'n normal de un flip-flop. Flip-Flop ,ctivados por +ivel Flip-Flop !/ 2iene tres entradas, + "de inicio#, / "reinicio o borrado# y < "para reloA#. 2iene una salida &, y a 5eces tambi n una salida complementada, la que se indica con un circulo en la otra terminal de salida. Eay un peque:o tri%ngulo en frente de la letra <, para designar una entrada din%mica. El sBmbolo indicador din%mico denota el ec$o de que el flip-flop responde a una transici'n positi5a " de 8 a 9# de la se:al de reloA. +u unidad b%sica "con compuertas N6N3 o NO/# se dibuAa a continuaci'n que, como act!a por "ni5eles" de amplitud "8-9# recibe el nombre de ,lip-,lop /+ acti5ado por ni5el ",,-/+-6N#. <uando no se especifica este detalle es del tipo ,lip-,lop /+ maestro-escla5o ",,-/+-7E#. +us ecuaciones y tabla de funcionamiento son & ) + F q /G /+ ) 8

;a operaci'n del flip-flop es como sigue. +i no $ay una se:al en la entrada del reloA <, la salida del circuito no puede cambiar independientemente de cu%les sean los 5alores de entrada de + y /. +'lo cuando la se:al de reloA cambia de 8 a 9 puede la salida afectarse de acuerdo con los 5alores de la entrada + y /. +i + ) 9 y / ) 8 cuando < cambia de 8 a 9, la salida & se inicia en 9. +i + ) 8 y / ) 9 cuando < cambia de 8 a 9 la salida & se reinicia o borra en 8. +i tanto + como / son 8 durante la transici'n de reloA, la salida no cambia. <uando tanto + como / son iguales a 9, la salida es impredecible y puede ser 8 o 9 dependiendo de los retrasos internos de tiempo que ocurran dentro del circuito. Flip-flop !/ tempori"ado El flip-flop b%sico por si solo es un circuito secuencial asincr'nico. 6gregando compuertas a las entradas de circuito b%sico, puede $acerse que el flip-flop responda a los ni5eles de entrada durante la ocurrencia del reloA. El flip-flop /+ tempori=ado mostrado en la siguiente figura consiste en un flipflop b%sico NO/ y dos compuertas N6N3. ;as salidas de las dos compuertas 6N3 permanecen en cero mientras el pulso del reloA "abre5iado en ingl s <># sea 8, independientemente de los 5alores de entrada + y / se permite llegar al flip-flop b%sico. El estado de puesta a uno se logra con +)9, /)8 y <>)9. >ara cambiar el estado de puesta a cero "o borrado# las entradas deben ser +)8, /)9 y <>)9. <on +)9 y /)9, la ocurrencia de los pulsos de reloA causar% que ambas salidas 5ayan moment%neamente a 8. <uando quite el pulso, el estado del flip-flop ser% indeterminado, es decir, podrBa resultar cualquier estado, dependiendo de si la entrada de puesta a uno o la de puesta a cero del flip-flop b%sico, permane=ca el mayor tiempo, antes de la transici'n a 8 al final del pulso. Flip-flop !/ tempori"ado El sBmbolo gr%fico del flip-flop /+ sincroni=ado se muestra en la figura anterior. 2iene tres entradas. +, / y <>. ;a entrada <> no se describe dentro del recuadro debido a que se reconoce f%cilmente por un peque:o tri%ngulo. El tri%ngulo es un sBmbolo para el indicador din%mico y denota el $ec$o que el flip-flop responde a una transici'n del reloA de entrada o flanco de subida de una se:al de un ni5el baAo "o binario# a un ni5el alto "9 binario#. ;as salidas del flip-flop se marcan con & y &? dentro del recuadro. +e le puede designar al flip-flop un nombre de 5ariable diferente aunque se escriba una & dentro del recuadro. En este caso la letra escogida para la 5ariable del flip-flop se marca por fuera del recuadro y a lo largo de la lBnea de salida. El estado del flip-flop se determina del 5alor de su salida normal &. +i se desea obtener el complemento de salida normal, no es necesario usar un in5ersor ya que el 5alor complementado se obtiene directamente de la salida &?. ;a tabla caracterBstica del flip-flop se muestra en la figura antes presentada. Esta tabla resume la operaci'n del flip-flop en forma de tabulado. & es el estado binario del flip-flop en un tiempo dado "refiri ndose al estado presente#, las columnas + y / dan los 5alores posibles de las entradas y &"t F 9# es el estado del flip-flop despu s de la ocurrencia de un pulso de reloA "refiri ndose al siguiente estado#. ;a ecuaci'n caracterBstica de un flip-flop se deduce del mapa de la figura antes mencionada. Esta ecuaci'n especifica el 5alor del siguiente estado como una funci'n del presente estado y de las entradas. ;a ecuaci'n caracterBstica de una e(presi'n algebraica para la informaci'n binaria de la tabla caracterBstica. ;os dos estados indeterminados se marcan con una * en el mapa, ya que pueden resultar como 9 o como 8. +in embargo la relaci'n +/)8 debe incluirse como parte de la ecuaci'n caracterBstica para especificar que + y / no pueden ser iguales a 9 simult%neamente. Flip-Flop 34 Un flip-flop 01 es un refinamiento del flip-flop +/ en el sentido que la condici'n indeterminada del tipo +/ se define en el tipo 01. ;as entradas 0 y 1 se comportan como las entradas + y / para iniciar y reinicia el flip-flop, respecti5amente. <uando las entradas 0 y 1 son ambas iguales a 9, una transici'n de reloA alterna las salidas del flip-flop a su estado complementario. +u unidad b%sica se dibuAa a continuaci'n que, como act!a por "ni5eles" de amplitud "8-9# recibe el

nombre de ,lip-,lop 01 acti5ado por ni5el ",,-01-6N#. <uando no se especifica este detalle es del tipo ,lip-,lop 01 maestro-escla5o ",,-01-7E#. +u ecuaci'n y tabla de funcionamiento son & ) 0 qG F 1G q

+e da detalle de su confecci'n l'gica a partir del ,,-/+-6N.

y si simplificamos por eAemplo usando Heic$-1arnaug$

/ ) 1q + ) 0 qG resulta el circuito

Flip-flop 34 Un flip-flop 01 es un refinamiento del flip-flop /+ ya que el estado independiente del termino /+ se define en el tipo 01. ;as entradas 0 y 1 se comportan como las entradas / y + para poner a uno o cero "set o reset# al flip-flop "n'tese que en el flip-flop 01 la entrada 0 se usa para la entrada de puesta a uno y la letra 1 para la entrada de puesta a cero#. <uando ambas entradas se aplican a 0 y 1 simult%neamente, el flip-flop cambia a su estado de complemento, esto es, si &)9 cambia a &)8 y 5ice5ersa. Un flip-flop sincroni=ado se muestra en la figura anterior. ;a salida & se aplica con 1 y <> a una compuerta 6N3 de tal manera que el flip-flop se ponga a cero "clear# durante un pulso de reloA solamente si & fue 9 pre5iamente. 3e manera similar la salida &? se aplica a 0 y <> a una compuerta 6N3 de tal manera que el flip-flop se ponga a uno con un pulso de reloA, solamente si &? fue 9 pre5iamente. Flip-flop 34 tempori"ado <omo se muestra en la tabla caracterBstica de la figura, el flip-flop 01 se comporta como un flip-flop /+ e(cepto cuando 0 y 1 sean ambos 9. <uando 0 y 1 sean 9, el pulso de reloA se transmite a tra5 s de una compuerta 6N3 solamenteD aquella cuya entrada se conecta a la salida del flip-flop la cual es al presente igual a 9. 6sB, si &)9, la salida de la compuerta 6N3 superior se con5ertir% en 9 una 5e= que se aplique un pulso de reloA y el flip-flop se ponga a cero. +i &?)9 la salida de la compuerta 6N3 se con5ierte en 9 y el flip-flop se pone a uno. En cualquier caso, el estado de salida del flip-flop se complementa. ;as entradas en el sBmbolo gr%fico para el flip-flop 01 deben marcarse con una 0 "debaAo de &# y 1 "debaAo de &?#. ;a ecuaci'n caracterBstica se da en la figura y se deduce del mapa de la tabla caracterBstica. N'tese que debido a la cone(i'n de retroalimentaci'n del flip-flop 01, la se:al <> que permanece en 9 "mientras que 0)1)9# causar% transiciones repetidas y continuas de las salidas despu s que las salidas $ayan sido completadas. >ara e5itar esta operaci'n indeseable, los pulsos de reloA deben de tener un tiempo de duraci'n que es menor que la demora de propagaci'n a tra5 s del flip-flop. Esta es una restricci'n, ya que la operaci'n del circuito depende del anc$o de los pulsos. >or esta ra='n los flip-flops 01 nunca se construyen como se muestra en la figura. ;a restricci'n del anc$o del pulso puede ser eliminada con un maestro escla5o o una construcci'n acti5ada por flanco de la manera discutida en la siguiente secci'n. El mismo ra=onamiento se aplica al flip-flop 2 presentado a continuaci'n. Flip-Flop 5 El flip-flop 2 se obtiene del tipo 01 cuando las entradas 0 y 1 se conectan para proporcionar una entrada !nica designada por 2. El flip-flop 2, por lo tanto, tiene s'lo dos condiciones. <uando 2 ) 8 " 0 ) 1 ) 8# una transici'n de reloA no cambia el estado del flip-flop. <uando 2 ) 9 "0 ) 1 ) 9# una transici'n de reloA complementa el estado del flip-flop. +u unidad b%sica se dibuAa a continuaci'n que, como act!a por "ni5eles" de amplitud "8-9# recibe el nombre de ,lip-,lop 2 acti5ado por ni5el ",,-2-6N#. <uando no se especifica este detalle es del tipo ,lip-,lop 2 maestro-escla5o ",,-2-7E#. +u ecuaci'n y tabla de funcionamiento son & ) 2 q

6 partir del ,,-/+-6N puede dise:arse este ,,-2-6N siguiendo los pasos mostrados anteriormente, pero no tiene sentido ya que al ser acti5ado por ni5el no tiene utilidad.

Flip-Flop D El flip-flop 3 "datos# es una ligera modificaci'n del flip-flop +/. Un flip-flop +/ se con5ierte a un flip-flop 3 insertando un in5ersor entre + y / y asignando el sBmbolo 3 a la entrada !nica. ;a entrada 3 se muestra durante la ocurrencia de uan transici'n de reloA de 8 a 9. +i 3 ) 9, la salida del flip-flop 5a al estado 9, pero si 3 ) 8, la salida del flip-flop 5a a el estado 8. +u unidad b%sica se dibuAa a continuaci'n que, como act!a por "ni5eles" de amplitud "8-9# recibe el nombre de ,lip-,lop 3 acti5ado por ni5el ",,-3-6N#. <uando no se especifica este detalle es del tipo ,lip-,lop 3 maestro-escla5o ",,-3-7E# com!nmente denominado tambi n <erroAo 4;atc$. +u ecuaci'n y tabla de funcionamiento son & ) 3

6 partir del ,,-/+-6N puede dise:arse este ,,-3-6N siguiendo los pasos mostrados anteriormente, pero no tiene sentido ya que al ser acti5ado por ni5el no tiene utilidad.

Flip-flop D El flip-flop 3 mostrado en la figura anterior es una modificaci'n del flip-flop /+ sincroni=ado. ;as compuertas N6N3 9 y @ forman el flip-flop b%sico y las compuertas 3 y I las modifican para conformar el flip-flop /+ sincroni=ado. ;a entrada 3 5a directamente a la entrada + y su complemento se aplica a la entrada / a tra5 s de la compuerta J. 7ientras que el pulso de reloA de entrada sea un 8, las compuertas 3 y I tienen un 9 en sus salidas, independientemente del 5alor de las otras entradas. Esto esta de acuerdo a los requisitos de que las dos entradas del flip-flop b%sico N6N3 permane=can inicialmente en el ni5el de 9. ;a entrada 3 se comprueba durante la ocurrencia

del pulso de reloA. +i es 9, la salida de la compuerta 3 5a a 8, cambiando el flip-flop al estado de puesta a uno "a no ser que ya este en ese estado#. +i en 8, la salida de la compuerta I 5a a 8, cambiando el flip-flop al estado de borrado. Flip-flop D tempori"ado El flip-flop tipo 3 recibe su nombre por la $abilidad de transmitir "datos" a un flip-flop. Es b%sicamente un flip-flop /+ con un in5ersor en la entrada /. el in5ersor agregado reduce el numero de entradas de dos a uno. Este tipo de flip-flop se llama algunas 5eces bloqueador 3 con compuertas o flip-flop de bloqueo. ;a entrada <> se le da a menudo la designaci'n 5ariable K "de gate# para indicar que esta entrada esta $abilita el flip-flop de bloqueo para $acer posible que los datos entren al mismo. El sBmbolo para el flip-flop 3 sincroni=ado se muestra en la figura. ;a tabla caracterBstica se lista en la parte "c# y la ecuaci'n caracterBstica se lista en la parte "d#. la ecuaci'n caracterBstica muestra que el siguiente estado del flip-flop es igual a la entrada 3 y es independiente del 5alor del presente estado. Flip-Flop Maestro-*sclavo 2odos los cuatro ,,-6N pueden implementarse siguiendo las 'rdenes de un ,,-3-6N a su entrada como muestra el dibuAo esquem%tico. El ,,-3 $ace de puerta "<erroAo#. <ada pulso en el clocL $ar% que la se:al entre al sistema "como salida del ,,-3-6N# y salga la misma a la salida final respetando la tabla de 5erdad del ,, escla5o. 6sB, si el escla5o es un ,,-*-6N, todo el conAunto se comporta como un ,,-*-7E 4aquB * puede ser un ,, o bien tambi n un sistema secuencial compleAo.

,ccesorios de los Flip-Flop ;os ,lip-,lop, normalmente y si no se especifica otro detalle, son siempre 7aestro-Escla5o, y suelen traer patas accesorias combinacionales. Nombramos las siguientes. 4 /eset pone a cero & 4 +et pone a 9 a & 4 <locL 4 Mn$ibici'n in$ibe "no deAa pasar# la entrada de se:al C1+5,D1!*/ D* 06-/1/ Generalidades +on sistemas de ,, en cascada y relacionados con redes combinacionales de tal manera que cuentan, baAo un c'digo binario cualquiera ya predeterminado "binario puro, C<3, 0$onson, etc., u otro in5entado por uno que necesite# los pulsos que ingresan al clocL del sistema. 6sB, si todos los reloAes se conectan en paralelo o no, los contadores se denominan, respecti5amente 4 sincr'nicos 4 asincr'nicos y nosotros estudiaremos a los primeros. ;a cantidad 7 de pulsos a contar "incluyendo el correspondiente reposo# est% relacionada con el n!mero n de ,, a utili=ar mediante la f'rmula @n-9 N 7 @n *7emplo de Dise8o +e pretende contar los pulsos de un c'digo, por eAemplo binario natural $asta el n!mero JD o sea que a partir del pulso O se reiniciar% el conteo "autoborrado#. En efecto, podemos elegir la mBnima cantidad de ,, a usar "y que por tanto se usar%n# 7 ) O @n-9 N 7 @n n ) 3

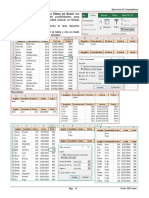

6doptamos seguidamente el tipo de ,, que dispongamos, por eAemplo el /+. 6$ora completamos las tablas de dise:o

+implificamos los resultados, por eAemplo por Heic$-1arnaug$ /8 ) q9Gq@ +8 ) q9q@ /9 ) q9q@ +9 ) q8Gq9Gq@ /@ ) q@ +@ ) q@G y armamos finalmente con ella el circuito

D.9./1!*/ D* F!*C6*+C., Generalidades >ueden reali=arse con contadores asincr'nicos o sincr'nicos. ,sincr:nico +eguidamente 5emos un di5isor de frecuencia asincr'nico reali=ado con ,,-2 "recu rdese que un ,, puede ser fabricado a partir de cualquier otro ,,# que poseen la propiedad de sacar un pulso por cada dos de entrada. >or ello la di5isi'n final es sal ) ent @n

/incr:nico

*7emplo de Dise8o 6$ora bien, supongamos que no deseamos di5idir por un n!mero @n sino por otro cualquiera. >ara ello nos 5aldremos del contador sincr'nico. <uando la cantidad de pulsos llega a la cantidad 7 se dise:ar% al !ltimo ,, de tal manera que cambie el estado detectando asB con ello la di5isi'n. +iguiendo los pasos de dise:o como reci n se $a e(puesto al dise:ar un contador cualquiera sincr'nico, podemos lograr nuestro cometido. +upongamos que nuestro dato sea di5idir por 3. 6doptamos, por eAemplo ,,-01 y entonces, con el criterio anterior, lo dise:amos de la siguiente manera 7 ) 3 @n-9 N 7 @n n ) @

M6-5.0-.C,D1!*/ D* F!*C6*+C., Generalidades >ueden reali=arse con un ;a=o de ,iAaci'n de ,ase ";,,# y un di5isor por 7 que lo realimente 47 es la cuenta de pulsos del contador como se 5io precedentemente. Estando enganc$ado y mantenido el ;,,, el O<H interno deber% mantener la ent multiplicada por 7. 6sB entonces, la frecuencia de salida ser% un m!ltiplo 7 del de la entrada sal ) O<H ) 7 ent

*7emplo de Dise8o +upongamos que se tiene una frecuencia de entrada que 5arBa entre un m%(imo f entma( y un mBnimo f entmin y se la quiere multiplicar 7 5eces f entma( P) ... f entmin P) ... 7 P) ... El circuito siguiente muestra una implementaci'n posible. >ara dise:ar al O<H debe recurrirse al capBtulo de multi5ibradores con los datos f ma( P) ... Q f entma( P f min P) ... N f entmin P

;a red /8<8 del filtro se la aconseAa que sea e(perimental, aunque puede estimarse su constante de tiempo de tal manera que filtre los pulsos detectados 8 ) /8<8 P) ... QQ @ 2 entma( ) I R f entmin El rango de mantenimiento /7 del la=o deber% resultar satisfactoriamente /7 SE=T ) 7 "f ma( - f min # ) ... Q f entma( PUf entmin P C1M0,!,D1!*/ D.G.5,-*/ +e comparar%n dos palabras digitales "bytes# 6 y C de m bits cada una de ellas seg!n el ordenamiento 6 ) 6m ... 69 68 C ) Cm ... C9 C8 con m el bit de mayor peso 6 6 6 6 6 Q C C ) C C N C 6 CG 6 F CG "6 C#G 6G F C 6G C

En efecto, para determinar el caso de igualdad bastar% comparar cada uno de los bits en forma respecti5a con compuertas O-E(clusi5a "6 ) C# ) "6m Cm#G ... "69 C9#G "68 C8#G

>ara e(plicar el proceso de detecci'n de la diferencia en e(ceso o d ficit nos 5aldremos de un eAemplo. +ea m ) @ y siendo 6 Q CD entonces con s'lo que el bit de mayor peso lo sea ser% suficiente 6@ Q C @ o bien 6@ ) C @ y 69 Q C9 6@ ) C @ y 6 9 ) C 9 y 6 8 Q C8 lo que nos permitir% armar la red combinatoria siguiente "6 Q C# ) "6@ Q C@# F "6@ ) C@# S "69 Q C9# F "69 ) C9# "68 Q C8# 6@C@G F "6@ C@#G S 69C9G F "69 C9#G F 68C8G T

y de la tabla "6 N C# ) "6 Q C#G "6 ) C#G ) S "6 Q C# F "6 ) C# TG !*G./5!1/ D* D*/0-,;,M.*+51/ +on cadenas de ,,-3 en cascada alimentados sincr'nicamente, de tal manera que por cada pulso en clocL la informaci'n digital se 5a despla=ando de ,, en ,, sin sufrir alteraci'n 4 recu rdese que la tabla de 5erdad del ,,-3 asB lo permite. >uede salirse del mismo de una manera serie o paralelo.

M6-5.0-*<1! = D*-M6-5.0-*<1! <onsiste en una lla5e digital y, por ende, puede ser selectora "multiple(or# o de-selectora "de-multiple(or#. +u diagrama como multiple(or es dado en el dibuAo que sigue, donde $emos llamado con q al n!mero de canales y p al n!mero de entradas de selecci'n 4combinaciones que los

seleccionar%n. +e cumplir% entonces que @p ) q

Dise8o de !edes Com(inacionales con Multiple$or Es !til el dise:o de esta manera y no en forma discreta porque se a$orran muc$as compuertas y complicaciones en las plaquetas dise:adas, pero claro deber% estar, que las mismas en su densidad ya se encuentran igual dentro de la sofisticaci'n integrada por el fabricante dentro del multiple(or.

+upongamos como dato tener una funci'n cualquiera , "6,C,<# "elegida al a=ar# como muestra la tabla siguiente que dise:aremos.

>rimeramente elegimos un multiple(or de la mayor cantidad de canales posibles pues esto minimi=ar% las compuertas adicionales. +upongamos que $emos obtenido uno de @ selecciones "p ) @# que para este eAemplo bastar%. +eguidamente armamos la tabla como sigue y luego simplificamos su resultado por Heic$-1arnaug$.

'.'-.1G!,F., $ttp.RRgaleon.$ispa5ista.comRedigiRflipflop.$tm $ttp.RRAlucas.$ome.cern.c$RAlucasRtffRflipflopRnode9.$tmlV+E<2MON88898888888888888888 $ttp.RRdet.bp.e$u.esR5$dlRpaginaRe(pressRsimula.$tm $ttp.RRmailweb.udlap.m(RWedAimRflipXflop.$tm $ttp.RRwww.monografias.comRtrabaAos3RbcdRbcd.s$tml

ma(el gon"ales urmac>ea

You might also like

- Informe Previo 2 Digitales 2 CasimiroDocument11 pagesInforme Previo 2 Digitales 2 CasimiropaoloNo ratings yet

- Diseño secuencial circuitosDocument20 pagesDiseño secuencial circuitosMichael IzarraNo ratings yet

- Contador Binario de 4 Bits Utilizando Flip - Flop J-KDocument7 pagesContador Binario de 4 Bits Utilizando Flip - Flop J-KCarlos MichelNo ratings yet

- Flip FlopDocument13 pagesFlip Flop28792kymmNo ratings yet

- Flip FlopDocument13 pagesFlip FlopFranklin AldanaNo ratings yet

- PRÁCTICA 9 FLIP-FLOPSDocument18 pagesPRÁCTICA 9 FLIP-FLOPSChamín AlcántaraNo ratings yet

- Circuitos Digitales Flip FlopDocument13 pagesCircuitos Digitales Flip FlopCorimayo MaximilianoNo ratings yet

- Circuitos y MicroDocument26 pagesCircuitos y MicroSlayerMcboNo ratings yet

- Reporte de Lab 03 - Chapa Electronica - SDI-215Document19 pagesReporte de Lab 03 - Chapa Electronica - SDI-215Nestor VasquezNo ratings yet

- Lab13 - C16A - Quispe Romero, Steven - Alvarez Cahuana, ManuelDocument14 pagesLab13 - C16A - Quispe Romero, Steven - Alvarez Cahuana, ManuelSteven Dave QRNo ratings yet

- Resumen de Flip FlopsDocument10 pagesResumen de Flip FlopserickNo ratings yet

- Informe Previo 2Document13 pagesInforme Previo 2CarlosVillavicencioGNo ratings yet

- El Flip Flop y Los Circuitos SecuencDocument26 pagesEl Flip Flop y Los Circuitos Secuencb4tipibeNo ratings yet

- Labo 1Document21 pagesLabo 1Jhoselyn Nikol Jimenez AcevedoNo ratings yet

- Motor A Pasos ReporteDocument13 pagesMotor A Pasos ReporteEmmanuel Migueles Perdomo100% (1)

- Previo Labo 4 DigitalesDocument11 pagesPrevio Labo 4 DigitalesRafael RamoscordovaNo ratings yet

- Contador 0-15 Flip Flop DDocument4 pagesContador 0-15 Flip Flop Dluis13071980No ratings yet

- Universidad Nacional de PiuraDocument7 pagesUniversidad Nacional de PiurasergioabelramirezzapNo ratings yet

- Ejercicio Feedback - Puente de LavadoDocument10 pagesEjercicio Feedback - Puente de LavadoEsparza Oliver100% (5)

- Flip FlopsDocument13 pagesFlip FlopsAnonymous FA8ihqLMB5No ratings yet

- Multvibradores BiestablesDocument12 pagesMultvibradores BiestablesAnimalXXX89No ratings yet

- UNIDAD IV Circuitos SecuencialesDocument23 pagesUNIDAD IV Circuitos SecuencialesRommel JimenezNo ratings yet

- Flip FlopsDocument24 pagesFlip FlopsEdison IANo ratings yet

- Flip-Flops RS JK DDocument10 pagesFlip-Flops RS JK DEduardo FajardoNo ratings yet

- Digitales Flip FlopDocument12 pagesDigitales Flip FlopRodrigo Herrera GodosNo ratings yet

- Flip Flop D IeeDocument7 pagesFlip Flop D IeeJosé Omar López HdzNo ratings yet

- Practica de LabDocument13 pagesPractica de LabAlexis EspinosaNo ratings yet

- 04 Flip-Flop Introduccion & ExplicacionDocument11 pages04 Flip-Flop Introduccion & ExplicacionValentina Gonzalez NavarroNo ratings yet

- Flip FlopDocument6 pagesFlip FlopJulian Andres EcheverryNo ratings yet

- Flip Flop RsDocument4 pagesFlip Flop RsLiliana Maria Plata SarmientoNo ratings yet

- Circuito Integrado Ne555 y 4017.doc y Transistores MedirlosDocument16 pagesCircuito Integrado Ne555 y 4017.doc y Transistores MedirlosSarai CortesiaNo ratings yet

- Practica Flip Flop Sistemas Digitales 1Document17 pagesPractica Flip Flop Sistemas Digitales 1Carlos FrancoNo ratings yet

- Flip-Flops SincrónicosDocument6 pagesFlip-Flops SincrónicosjuanNo ratings yet

- TP 14 LocoDocument12 pagesTP 14 LocoNombre PendienteNo ratings yet

- Diseño Contadores SíncronosDocument5 pagesDiseño Contadores SíncronosNirza Carolina Torres BlancoNo ratings yet

- Flip Flop JKDocument7 pagesFlip Flop JKJesus Emilio ValenzuelaNo ratings yet

- Informe FINAL 3 DigiDocument15 pagesInforme FINAL 3 DigiYean Guere LavadoNo ratings yet

- Sistemas Digitales - Casemiro - UnmsmDocument29 pagesSistemas Digitales - Casemiro - UnmsmPaulNo ratings yet

- Diana Muñoz - Flip FlopsDocument12 pagesDiana Muñoz - Flip FlopsDianaMuñozNo ratings yet

- Flip FlopDocument11 pagesFlip FlopJhon WilliamNo ratings yet

- cd2 Final1Document8 pagescd2 Final1Eleazar CastilloNo ratings yet

- Cuestionario Previo 10 PDFDocument8 pagesCuestionario Previo 10 PDFROBERTO GASPAR ESCOBEDO CONTRERASNo ratings yet

- Lab Cir Digitales 07Document12 pagesLab Cir Digitales 07Joel Cad PadNo ratings yet

- Aplicaciones Flip Flop Tipo DDocument8 pagesAplicaciones Flip Flop Tipo DLaddy Martha Rojas Román50% (2)

- Circuitos de RegistroDocument7 pagesCircuitos de RegistroRockjon SkrocNo ratings yet

- Flip-flop D: funcionamiento y ventajasDocument8 pagesFlip-flop D: funcionamiento y ventajasMartin Ennis Delzo GutierrezNo ratings yet

- Previo 2 Sistemas DigitalesDocument17 pagesPrevio 2 Sistemas DigitalesMigvel Angel Soncco XDNo ratings yet

- Laboratorio 1 Biestables Asíncronos y SincronosDocument16 pagesLaboratorio 1 Biestables Asíncronos y SincronosdaniNo ratings yet

- Flip Flop RS Implementado Con Compuertas NANDDocument17 pagesFlip Flop RS Implementado Con Compuertas NANDDaniel CanaviriNo ratings yet

- Flip FlopTarDocument28 pagesFlip FlopTarcokitoNamiNo ratings yet

- SISTEMAS DIGITALES Asignacion 9 y 10Document25 pagesSISTEMAS DIGITALES Asignacion 9 y 10jose2001No ratings yet

- Circuitos ContadoresDocument11 pagesCircuitos Contadoresdark_0No ratings yet

- Informe de Laboratorio 9Document10 pagesInforme de Laboratorio 9juan13uNo ratings yet

- Clase 10 - Latches y Flip-FlopsDocument24 pagesClase 10 - Latches y Flip-FlopsYony MenjivarNo ratings yet

- Circuitos Secuenciales SincronosDocument7 pagesCircuitos Secuenciales SincronosAndrea RamosNo ratings yet

- 02 Filtros AvanzadosDocument2 pages02 Filtros AvanzadosJhonn C Ccopa SupoNo ratings yet

- Procesador Digital de SeñalesDocument4 pagesProcesador Digital de SeñalesJhonn C Ccopa SupoNo ratings yet

- 06 Tablas DinamicasDocument2 pages06 Tablas DinamicasJhonn C Ccopa SupoNo ratings yet

- 03 Funciones BuscarDocument2 pages03 Funciones BuscarJhonn C Ccopa SupoNo ratings yet

- AdewDocument4 pagesAdewJhonn C Ccopa SupoNo ratings yet

- Computacion 1Document4 pagesComputacion 1Jhonn C Ccopa SupoNo ratings yet

- Página 1Document427 pagesPágina 1Jhonn C Ccopa SupoNo ratings yet

- 01 BD Excel 2021 FiltrosDocument4 pages01 BD Excel 2021 FiltrosJhonn C Ccopa SupoNo ratings yet

- Formato Asiento ContableDocument2 pagesFormato Asiento ContableJhonn C Ccopa SupoNo ratings yet

- Conceptos BásicosDocument2 pagesConceptos BásicosJhonn C Ccopa SupoNo ratings yet

- 35 ErDocument27 pages35 ErJhonn C Ccopa SupoNo ratings yet

- Reporte Del Examen PrácticoDocument8 pagesReporte Del Examen PrácticoJhonn C Ccopa SupoNo ratings yet

- Universidad Nacional Del AltiplanoDocument2 pagesUniversidad Nacional Del AltiplanoJhonn C Ccopa SupoNo ratings yet

- Indumentaria en La Antigua GreciaDocument1 pageIndumentaria en La Antigua GreciaJhonn C Ccopa SupoNo ratings yet

- Conceptos BásicosDocument2 pagesConceptos BásicosJhonn C Ccopa SupoNo ratings yet

- Convolución de SeñalesDocument4 pagesConvolución de SeñalesJuan SepúlvedaNo ratings yet

- UnDocument12 pagesUnJhonn C Ccopa SupoNo ratings yet

- Transformada de LaplaceDocument3 pagesTransformada de Laplacemarcus1818No ratings yet

- Sabías Que Es Posible Consultar Wikipedia Sin Conexión A InternetDocument7 pagesSabías Que Es Posible Consultar Wikipedia Sin Conexión A InternetJhonn C Ccopa SupoNo ratings yet

- UnDocument12 pagesUnJhonn C Ccopa SupoNo ratings yet

- Modelo OSIDocument11 pagesModelo OSIJhonn C Ccopa SupoNo ratings yet

- Modelo OSIDocument11 pagesModelo OSIJhonn C Ccopa SupoNo ratings yet

- Sabías Que Es Posible Consultar Wikipedia Sin Conexión A InternetDocument7 pagesSabías Que Es Posible Consultar Wikipedia Sin Conexión A InternetJhonn C Ccopa SupoNo ratings yet

- The Big Bang TheoryDocument14 pagesThe Big Bang TheoryJhonn C Ccopa SupoNo ratings yet

- Quieres Tu Calculadora IpDocument3 pagesQuieres Tu Calculadora IpJhonn C Ccopa SupoNo ratings yet

- Sensor EsDocument6 pagesSensor EsJhonn C Ccopa SupoNo ratings yet

- IntroducciónDocument5 pagesIntroducciónJhonn C Ccopa SupoNo ratings yet

- 23 TelecoDocument5 pages23 TelecoJhonn C Ccopa SupoNo ratings yet

- DipoloDocument12 pagesDipoloJhonn C Ccopa SupoNo ratings yet

- Modelos de RedDocument7 pagesModelos de RedJhonn C Ccopa SupoNo ratings yet

- Diseño Contadores SíncronosDocument5 pagesDiseño Contadores SíncronosNirza Carolina Torres BlancoNo ratings yet

- Re-10-Lab-138 Sistemas Digitales I v5Document23 pagesRe-10-Lab-138 Sistemas Digitales I v5Jhon AyllonNo ratings yet

- Seguidor de línea blanca con sensor infrarrojo y motorreductorDocument3 pagesSeguidor de línea blanca con sensor infrarrojo y motorreductorDayana Guzman SierraNo ratings yet

- Receptor 4 Canales RX-4: Manual Usuario e InstaladorDocument8 pagesReceptor 4 Canales RX-4: Manual Usuario e InstaladortetocastroNo ratings yet

- Informe de Grabado y LectorDocument15 pagesInforme de Grabado y LectorJouleshans BradleyNo ratings yet

- Generador Electromagnético InmóvilDocument48 pagesGenerador Electromagnético Inmóvilalexmen7_411847196No ratings yet

- Capitulo Vi - Analisis y Sintesis de Circuitos Secuenciales Sincronos-LibreDocument72 pagesCapitulo Vi - Analisis y Sintesis de Circuitos Secuenciales Sincronos-LibrePiieriitho Vilca Ramirez100% (1)

- 7305-03 - Funciones Instrumentadas de Seguridad de DeltaV IDocument94 pages7305-03 - Funciones Instrumentadas de Seguridad de DeltaV IJefferson Villalba Jacome0% (1)

- Contadores y Divisores de FrecuenciaDocument8 pagesContadores y Divisores de Frecuenciadavis ledezmaNo ratings yet

- Análisis y diseño de sistemas secuenciales con Boole-DeustoDocument9 pagesAnálisis y diseño de sistemas secuenciales con Boole-DeustoTomas Sanchez TronoNo ratings yet

- Proyecto N°2 (Parra-Quispe)Document21 pagesProyecto N°2 (Parra-Quispe)danidicilloNo ratings yet

- Circuitos digitales con Flip FlopsDocument9 pagesCircuitos digitales con Flip FlopsRomario Gonzales Leon100% (1)

- AplausometroDocument7 pagesAplausometroLuisacifuentesRNo ratings yet

- Tipos de Circuitos SecuencialesDocument2 pagesTipos de Circuitos SecuencialesE&GNo ratings yet

- Medición capacitanciaDocument10 pagesMedición capacitanciaJhonatan LopezNo ratings yet

- Capitulo 6. Sistemas SecuencialesDocument24 pagesCapitulo 6. Sistemas SecuencialesOsvaldo MeliNo ratings yet

- Electronica Digital BasicaDocument3 pagesElectronica Digital BasicaDavid DavichoNo ratings yet

- Presentacion PLDsDocument112 pagesPresentacion PLDsAlejandro BejaranoNo ratings yet

- Generadores de Señal y Osciladores 2010Document31 pagesGeneradores de Señal y Osciladores 2010Sebastian Eduardo Demelas MiersNo ratings yet

- Circuitos Osciladores: Caracteristicas, Funciones y EjemplosDocument9 pagesCircuitos Osciladores: Caracteristicas, Funciones y EjemplosLuisDavidSrrds100% (1)

- 8 Diseño de Contadores FisicosDocument31 pages8 Diseño de Contadores FisicosBaez VullaNo ratings yet

- Diseño de Circuitos Secuenciales AsincronosDocument6 pagesDiseño de Circuitos Secuenciales AsincronoshectorfmirandaNo ratings yet

- SD Gr5-2 Cachumba Francisco Practica#9 InformeDocument2 pagesSD Gr5-2 Cachumba Francisco Practica#9 InformeFranconos 21No ratings yet

- Entrega 3Document4 pagesEntrega 3Gabo FrancoNo ratings yet

- INFORME Previo 4Document12 pagesINFORME Previo 4Nefasto -No ratings yet

- P2 EL245 EL32 - 2021 00 UPC2 Solucion638Document4 pagesP2 EL245 EL32 - 2021 00 UPC2 Solucion638Edgarciito Bryan Nino CcosccoNo ratings yet

- Multibibrador Monoestable TransistorizadoDocument5 pagesMultibibrador Monoestable TransistorizadoAlejandro RodriigzNo ratings yet

- Informe de Laboratorio #5-César Díaz, 9-749-2475Document16 pagesInforme de Laboratorio #5-César Díaz, 9-749-2475César D. MarioNo ratings yet

- Elt-279 1er Parcial (Segunda Parte)Document13 pagesElt-279 1er Parcial (Segunda Parte)Luis Yucra Pizarro LuisNo ratings yet

- CEA Lab4Document10 pagesCEA Lab4Shanella ChallcoNo ratings yet