Professional Documents

Culture Documents

E2.11/ISE2.22 - Digital Electronics II

Uploaded by

kolhejayantOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

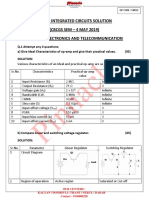

E2.11/ISE2.22 - Digital Electronics II

Uploaded by

kolhejayantCopyright:

Available Formats

E2.11/ISE2.

22 – Digital Electronics II

Problem Sheet 5

(Question ratings: A=Easy, …, E=Hard. All students should do questions rated A, B or C as a minimum)

6B. Signals on a compact disc are stored as sequences of 16-bit numbers. Determine the

1B. A 3½ digit Digital Voltmeter has a display range of ±1999 and an accuracy of ±2 on maximum undistorted signal-to-noise ratio obtainable for a music signal whose peak

the display. How many bits would a binary A/D converter need to have for its ±0.5 amplitude is 10 times as great as its RMS value.

LSB accuracy to be as good as that of the DVM?

7B. Traingular pdf dither, q, of amplitude ±1 mV is added to an input signal, w, before

2B. A 12-bit converter has a resolution of 1 mV (i.e. 1 LSB = 1 mV) and input voltages in conversion to a 12 bit number Y11:0. This is then sent to a DAC to generate an output

the range ±0.5 mV are converted to the value 0. What range of input voltages will be voltage z. If all voltages are measured in mV then z = round(w + q ) and the pdf of q is

converted to –2047 ? equal to p(q ) = 1− | q | for | q |< 1 .

3B. A 10-bit converter converts an input voltage x to the value floor(x / 10mV). If 1 V < x <

8 V, what range of output values will be obtained ?

w x Y11:0 z

+ ADC DAC

4C. X3:0 is a 4-bit signed RF=10kΩ

number whose value,

X3

1

V3 R3

q

X, lies in the range –8

R2

Assuming that | w |< 0.5 , show that the probability that z = −1 is given by

to +7. If the logic X2 V2

1 (a)

levels of V3:0 are 0 V – VOUT

R1 pr ( z = −1) = 0.125 × (2 w − 1) 2 .

and +5 V, choose X1 V1 +

1 R4

values for R0 to R4 so

that VOUT is equal to X0 V0 R0 (b) Derive similar expressions for pr ( z = 0) and pr ( z = +1) for | w |< 0.5 .

X/8 volts. 1

(c) Determine the mean and variance of z in terms of w.

8C. A sample-hold circuit is used to store the input voltage of a 12-bit A/D converter

5C. The composite video signal to drive a monochrome TV monitor takes one of three during each conversion. The sample-hold circuit has an aperture uncertainty of 5 ns and

different voltages according to the values of two digital signals DATA and SYNC: a leakage current of ±1 nA. The A/D converter has an input voltage range of ±10 V.

If the input voltage is a sine wave of amplitude 10 V, calculate the input frequency at

DATA SYNC VOUT which the aperture uncertainty will result in an error of ±0.5 LSB [surprisingly low].

0 0 0.0

If the sample-hold uses a storage capacitor of 200 pF calculate how long the input

1 0 0.7 voltage can be held before it changes by 0.5 LSB due to the leakage current.

0 1 –0.3

1 1 Don’t Care

Design a circuit to generate VOUT having a 50 Ω output impedance. You may assume

that output logic levels are 0 and 5 V and that +5 V and –5 V power supplies are

available should you need them. You do not need any op-amps although you will need

at least one logic gate.

Rev: Sep-07 Digital Electronics II: Problem Sheet 5 Page 1

9D. The circuit and state diagrams for a successive approximation converter are shown 10B. In the questions below, u represents a 4-bit unsigned binary number in the range 0 to 15

below. The output signals X2:0 and DONE are also used as the state bits. Derive and x represents a signed 4-bit binary number in the range –8 to +7. Determine the

Boolean equations for NX2:0 and NDONE. You should ensure that your circuit can range of possible values that each expression can take and give a Boolean expression

never get stuck. for each bit of the corresponding binary number (signed or unsigned as appropriate).

The function floor(x) denotes the largest integer less than x.

CLOCK (a) 15 – u (b) floor(u/8) (c) u – 8

START

(d) floor(u/2) (e) –(x+1) (f) floor(x/2)

VIN C1

+

Logic

HI

– NX2:0 X2:0 (g) –floor(x/8) (h) x – 8×floor(x/8) (i) x – 16×floor(x/8)

1D

X2:0 NDONE DONE

DAC (j) floor(u/2) – 4×floor(u/8) (k) 2u – 15×floor(u/8) (l) u – 16×floor(u/8)

1,?

?,1 /1,7

/0,7 ?,0

?,1 1,?

/1,6

/0,6

?,0 ?,1 1,?

/1,5

?,1

/0,5 ?,0

1,?

/1,4

/0,4

?,1 1,?

?,0 /1,3

/0,3 ?,0

?,1 1,?

/1,2

/0,2

?,0 ?,1 1,?

/1,1

/0,1 ?,0

1,?

/1,0

I/O Signals: START,HI/DONE,X0:2

Rev: Sep-07 Digital Electronics II: Problem Sheet 5 Page 2

E2.11/ISE2.22 – Digital Electronics II

Solution Sheet 5

(Question ratings: A=Easy, …, E=Hard. All students should do questions rated A, B or C as a minimum)

1B. Full-scale range = 3998 so the accuracy is 2/3998 of full-scale range. For an N-bit SYNC V1 R1

binary A/D converter, the full-scale range is (2N–1) LSB giving an accuracy of 0.5/(2N–

1

1). R2

DATA V2

1

0.5 2 VOUT

Hence ≤ ⇒ 2 N ≥ 1000.5 ⇒ N ≥ 9.96 ⇒ N = 10 R3

2 − 1 3998

N –5V

2B. –2047 mV ±0.5 mV, i.e. –2047.5 mV to –2046.5 mV. 0V R4

3B. 1 V and 8 V correspond to output values of 100 and 800 respectively, so if 1 V < x <

Taking Gn = 1/Rn we must have G1+G2+G3+G4 = 1/50Ω = 20 mS.

8 V, the output will be in the range 100 to 799.

Then VOUT = (V1G1 + V2G2 – 5G3) / 20 mS.

4C. A change of 5 V in V3 must give a change of –1 V in VOUT, a gain of –0.2. Hence

From the truth table, we see that changes of 5 V in V1 and V2 must give changes in

RF/R3 = 0.2 ⇒ R3 = 50 kΩ.

VOUT of 0.3 and 0.7 volts respectively; this means we need gains of 0.06 and 0.14.

Hence:

When V3=0, the op-amp may be viewed an a non-inverting amplifier with a gain of

(1 + RF/R3) = 1.2. The voltage at VOUT due to V2:0 is therefore given by:

G1 = 0.06 × 20 mS = 1.2 mS ⇒ R1 = 833Ω.

G2 = 0.14 × 20 mS = 2.8 mS ⇒ R2 = 357Ω.

G2V2 + G1V1 + G0V0 To generate the –0.3 V offset: 5G3 = 0.3 × 20 mS = 6 mS ⇒ R3 = 833Ω.

VOUT = 1.2 × G4 = 20 mS – G1 – G2 – G3 = 14.8 mS ⇒ R4 = 67.6Ω.

G4 + G2 + G1 + G0

Note it is possible to take R4 to +5 V instead in which case R3 and R4 are 116Ω and

where G4:0 are the reciprocals of R4:0. 135Ω.

This circuit is very fast since it has no op-amps.

To minimize the effect of op-amp bias currents, we should make the Thévenin

impedances at the input terminals equal. This means that G4+G2+G1+G0 = G3+GF =

120 µS.

The gains from V2, V1 and V0 to VOUT must be 0.1, 0.05 and 0.025 respectively.

Thus we have G2 = 120 µS × 0.1/1.2 = 10 µS ⇒ R2 = 100 kΩ. Similarly, R1 = 200 kΩ

and R0 = 400 kΩ.

Finally G4 = 120 µS – G2 – G1 – G0 = 102.5 µS ⇒ R4 = 9.8 kΩ.

5C. The SYNC signal needs inverting because SYNC going high must cause the output to

decrease. We will need a negative bias voltage in order to obtain –0.3 V. Our circuit is

therefore:

Rev: Sep-07 Digital Electronics II: Solution Sheet 5 Page 1

6B. The range of a 16-bit signed number is ±32767 and so to avoid distortion, the RMS

value must be no higher than 3276.7. From the notes, the RMS value of quantisation

noise is 0.289 LSB which gives a signal-to-noise ratio of 11338 which equals 81 dB 9D. We send the all zero state to the initial state of a conversion.

7B. (a) z will equal –1 when x < −0.5 , so NDONE = DONE ⋅ START + DONE ⋅ X 0

NX 2 = DONE ⋅ ( X 2 + START ) + DONE ⋅ X 2 ⋅ ( X 0 + X 1 + HI ) + DONE ⋅ X 2 ⋅ X 1⋅ X 0

pr ( z = −1) = pr ( x < −0.5) = pr (q < −0.5 − w)

− 0.5 − w − 0.5 − w − 0.5 − w

NX 1 = DONE ⋅ X 1⋅ START + DONE ⋅ X 1⋅ ( X 0 + HI ) + DONE ⋅ X 2 ⋅ X 1⋅ X 0

= ∫ p(q)dq =

q = −1

∫1− | q | dq =

q = −1

∫1 + q dq

q = −1

NX 0 = DONE ⋅ X 0 ⋅ START + DONE ⋅ X 0. HI + DONE ⋅ X 1 ⋅ X 0

[

= q + 0.5q 2 ] − 0.5 − w

q = −1 = 0.125 × (2 w − 1) 2 10B. We call the answer w or z according to whether it is unsigned or signed:

(a) 0<=w<=15, Wi=!Ui

Note that because | w |< 0.5 is given in the question, both integration limits are (b) 0<=w<=1, W0=U3

always negative and so we can replace | q | → − q in the integrand. You can also (c) –8<=z<=7, Z3=!U3, Zi=Ui for i=0,1,2

get this answer graphically (and more easily) by drawing the pdf and finding the (d) 0<=w<=7, Wi=Ui+1

area of the triangle representing pr (q < −0.5 − w) . (e) –8<=z<=7, Zi=!Xi

(f) –4<=z<=3, Zi=Xi+1

(b) pr ( z = +1) = 0.125 × (2 w + 1) 2 (g) 0<=w<=1, W0=X3

(h) 0<=w<=7, Wi=Xi for i=0,1,2

pr ( z = 0) = 1 − pr ( z = −1) − pr ( z = +1) = 0.75 − w2 (i) 0<=w<=15, Wi=Xi

(j) 0<=w<=3, Wi=Ui+1 for i=0,1

(c) We have

(k) 0<=w<=15, W0=U3, Wi=Ui-1 for i=1,2,3

E ( z ) = 1 × pr ( z = +1) − 1 × pr ( z = −1) (l) –8<=z<=7, Zi=Ui

(

= 0.125 × (2 w + 1) − (2 w − 1) = w 2 2

)

Var ( z ) = E ( z 2 ) − E ( z ) 2 = E ( z 2 ) − w2

= 1 × pr ( z = +1) + 1 × pr ( z = −1) − w2

(

= 0.125 × (2 w + 1) 2 + (2w − 1) 2 − w2 )

= w + 0.25 − w = 0.25

2 2

8C. Full-scale range of 20 V equals 4096 LSB so 0.5 LSB = 0.5 × 20/4096 = 2.44 mV.

The peak rate of change of a 10 V sinewave is 20πf volts per second. The voltage

change in 5 ns is therefore πf × 10-7. These are equal when f = 2.44 × 10-3 × 107 / π =

7.77 kHz.

For the second part I = C dV/dt from which Δt = C×ΔV/I = 2×10-10×2.44×10-3/10-9 =

488 µs.

Rev: Sep-07 Digital Electronics II: Solution Sheet 5 Page 2

You might also like

- Experinment 10Document5 pagesExperinment 10mano17doremonNo ratings yet

- Sedra8e - BonusTextTopics x1Document6 pagesSedra8e - BonusTextTopics x1Akik BiswasNo ratings yet

- Digital To Analog Converters (DAC) : What Is A DAC?Document9 pagesDigital To Analog Converters (DAC) : What Is A DAC?Sujatha ReddyNo ratings yet

- MOS Transistors and CMOS InvertersDocument34 pagesMOS Transistors and CMOS InverterssivapothiNo ratings yet

- Easy(er) Electrical Principles for General Class Ham License (2019-2023)From EverandEasy(er) Electrical Principles for General Class Ham License (2019-2023)No ratings yet

- Real Time (problems) Lec (2) ADC: Resolution ( Q ) , LSB=V refDocument9 pagesReal Time (problems) Lec (2) ADC: Resolution ( Q ) , LSB=V refMohamd barcaNo ratings yet

- Chapter 5 Digital-To-Analog Converter DACDocument12 pagesChapter 5 Digital-To-Analog Converter DACDr Senthilkumar GNo ratings yet

- Ade Mod5Document8 pagesAde Mod5BasNo ratings yet

- July-Nov 2019 Practice Problems: A s ω s sDocument4 pagesJuly-Nov 2019 Practice Problems: A s ω s sswarajboishya17No ratings yet

- AC CIRCUITS FORMULAEDocument11 pagesAC CIRCUITS FORMULAEjayaditya soniNo ratings yet

- 04-MB-4 Version Anglaise - Mai 2014Document4 pages04-MB-4 Version Anglaise - Mai 2014LuisAranaNo ratings yet

- Smith Charts: Appendix ADocument10 pagesSmith Charts: Appendix Aani18100% (4)

- Tutorial 1 PDFDocument2 pagesTutorial 1 PDFJohn HopkinsNo ratings yet

- MSC361 02 CircuitsDocument9 pagesMSC361 02 CircuitsAxtronNo ratings yet

- DA Converters: DigitalelectronicsiicourseDocument24 pagesDA Converters: DigitalelectronicsiicourseLeonardo Franzua Giraldo CardosoNo ratings yet

- D-A Converter (Weighted Resistor Method)Document3 pagesD-A Converter (Weighted Resistor Method)neha yarrapothuNo ratings yet

- Electronic Circuits 1 Mid-Term Exam 1Document5 pagesElectronic Circuits 1 Mid-Term Exam 1정연종No ratings yet

- Expt02 - Characteristics of Common Passive DevicesDocument2 pagesExpt02 - Characteristics of Common Passive DevicesMadhurimaNo ratings yet

- Lec 24Document14 pagesLec 24sadaf asmaNo ratings yet

- DAC CONVERSION TECHNIQUESDocument28 pagesDAC CONVERSION TECHNIQUESSivasankar PoovaragavanNo ratings yet

- Logic Design With MosfetsDocument80 pagesLogic Design With MosfetsFroGMaN - AlNo ratings yet

- 01 TutorialDocument3 pages01 Tutorialee23m052No ratings yet

- Chapter 1 - Circuit Characterization of CMOS CircuitsDocument60 pagesChapter 1 - Circuit Characterization of CMOS CircuitsYean TernNo ratings yet

- Review Problems SolutionsDocument6 pagesReview Problems SolutionsDimitrios PanaNo ratings yet

- ADC and DACDocument54 pagesADC and DACM. D AdarshNo ratings yet

- DAC and ADC Fundamentals: Digital to Analog Conversion and Analog to Digital ConversionDocument63 pagesDAC and ADC Fundamentals: Digital to Analog Conversion and Analog to Digital ConversionMohammad ja'farNo ratings yet

- Expt9 - Buck ConvDocument6 pagesExpt9 - Buck ConvNitin KhetadeNo ratings yet

- Double Stub and LC Matching CircuitDocument31 pagesDouble Stub and LC Matching CircuitVijay ReddyNo ratings yet

- Adc Dac 2Document7 pagesAdc Dac 2sabin3sNo ratings yet

- Transmission Line: Prof. M M SharmaDocument28 pagesTransmission Line: Prof. M M SharmaJaiverdhanNo ratings yet

- Assignment ECT1016Document6 pagesAssignment ECT1016raihan.kuet.bmeNo ratings yet

- Solns 28Document22 pagesSolns 28DarshilShahNo ratings yet

- Lic Solution 2Document26 pagesLic Solution 2Muiz TankiNo ratings yet

- Adding hysteresis to comparators to eliminate multiple switchingDocument1 pageAdding hysteresis to comparators to eliminate multiple switchingVsn Raju BNo ratings yet

- 12 6 CMPLX Impedance PDFDocument4 pages12 6 CMPLX Impedance PDFKhaled BazaNo ratings yet

- 4 Analog To Digital Conversion: 4.1 Mode of OperationDocument4 pages4 Analog To Digital Conversion: 4.1 Mode of OperationYassine DjillaliNo ratings yet

- Lesson 5 DACDocument18 pagesLesson 5 DACmarkangelobautista86No ratings yet

- Tutorial 1Document3 pagesTutorial 1Putrevu SaiprakashNo ratings yet

- Isro 2018Document71 pagesIsro 2018gnanarani nambiNo ratings yet

- DTL NOR and NAND GatesDocument7 pagesDTL NOR and NAND Gateseng_magdyNo ratings yet

- ELE302 NotesDocument70 pagesELE302 NotesAnmol PanchalNo ratings yet

- Solns - MSD by ZongalezDocument56 pagesSolns - MSD by ZongalezWon won Ron ronNo ratings yet

- EEE109 Midterm Exam II ReviewDocument5 pagesEEE109 Midterm Exam II ReviewkakagoNo ratings yet

- Transmission Gate Characteristics: DS DSDocument17 pagesTransmission Gate Characteristics: DS DSradeonleonNo ratings yet

- Assign 6Document3 pagesAssign 6DivyanshNo ratings yet

- A Digital-To-Analog Converter (DAC) Block Diagram.: Introduction To Microprocessor-Based ControlDocument3 pagesA Digital-To-Analog Converter (DAC) Block Diagram.: Introduction To Microprocessor-Based Controlnovo orderNo ratings yet

- Experiment 6: Pulse Code Modulation: T x T t + 2x (t) cos 4πf t + 2x (t) cos 6πf t + - . .) x (t) T t)Document6 pagesExperiment 6: Pulse Code Modulation: T x T t + 2x (t) cos 4πf t + 2x (t) cos 6πf t + - . .) x (t) T t)Pruthvi TrinathNo ratings yet

- Bits, Noise, and Linearity The Imperfections of ADCs - Chemistry LibreTextsDocument4 pagesBits, Noise, and Linearity The Imperfections of ADCs - Chemistry LibreTextsketkyhuNo ratings yet

- Electronic Circuits Lab Manual Clippers and AmplifiersDocument29 pagesElectronic Circuits Lab Manual Clippers and AmplifiersAshwath NadahalliNo ratings yet

- Lab 11 DAC and ADC Full PackageDocument5 pagesLab 11 DAC and ADC Full PackageLoveWorldCanadaNo ratings yet

- EE 369 Power System Analysis Transmission Line ModelsDocument33 pagesEE 369 Power System Analysis Transmission Line ModelsShuhan Mohammad Ariful HoqueNo ratings yet

- Unit-III Adc & DacDocument20 pagesUnit-III Adc & DacK Krishna Murthy 184450No ratings yet

- Week 3Document97 pagesWeek 3abbazh rakhondeNo ratings yet

- Review Problems: 40 k Ω 4 kΩ Vo +Document16 pagesReview Problems: 40 k Ω 4 kΩ Vo +NajmoAdenNo ratings yet

- Lic Combined SlidesDocument288 pagesLic Combined SlidesMadhuNo ratings yet

- Lic Solution 1Document29 pagesLic Solution 1Muiz TankiNo ratings yet

- Syllabus Aei IV SemDocument18 pagesSyllabus Aei IV Semkolhejayant100% (1)

- Intro 013Document5 pagesIntro 013kolhejayantNo ratings yet

- Probc 3Document4 pagesProbc 3kolhejayantNo ratings yet

- Media, 19031, enDocument1 pageMedia, 19031, enkolhejayantNo ratings yet

- School of Electrical and Electronics Engineering Department of EceDocument5 pagesSchool of Electrical and Electronics Engineering Department of EcekolhejayantNo ratings yet

- IntroElectro AdderDocument4 pagesIntroElectro AdderkolhejayantNo ratings yet

- Introduction To Digital ElectronicsDocument10 pagesIntroduction To Digital ElectronicsblueskyderNo ratings yet

- Ece 4TH SemDocument11 pagesEce 4TH SemkolhejayantNo ratings yet

- Lecture Notes For Digital ElectronicsDocument43 pagesLecture Notes For Digital ElectronicsShruti GuptaNo ratings yet

- RF Amp TutorialDocument17 pagesRF Amp TutorialMihailNo ratings yet

- Digital ElectronicsDocument2 pagesDigital ElectronicskolhejayantNo ratings yet

- SAIC-P-3017 Rev 7 FinalDocument14 pagesSAIC-P-3017 Rev 7 FinalEnginerShahzadGhaffarNo ratings yet

- Gnucap ManualDocument136 pagesGnucap ManualDaniel RodríguezNo ratings yet

- Parts List From Pacific SemicondutorsDocument7 pagesParts List From Pacific SemicondutorsNeville McBeanNo ratings yet

- The Framework of Advanced Distribution Management SystemDocument5 pagesThe Framework of Advanced Distribution Management SystemBehrouz AzimianNo ratings yet

- Sonic Hub BrugermanualDocument24 pagesSonic Hub Brugermanualparamo23No ratings yet

- Physics Practical Set-BDocument35 pagesPhysics Practical Set-BKeshab Chandra BihariNo ratings yet

- Tensan 4109A one-component epoxy adhesive technical data sheetDocument1 pageTensan 4109A one-component epoxy adhesive technical data sheetthe hoangNo ratings yet

- Bef45203 HV Chapter 2 - Breakdown in GassesDocument99 pagesBef45203 HV Chapter 2 - Breakdown in GassesNUR AQILAH MOHD AZMANNo ratings yet

- Denyo CatalogueDocument9 pagesDenyo CatalogueEslam MahfouzNo ratings yet

- HFCF-En (Full Detailed Catalogue)Document17 pagesHFCF-En (Full Detailed Catalogue)aries26marchNo ratings yet

- Controller Exeron ManualDocument29 pagesController Exeron ManualSufi Shah Hamid JalaliNo ratings yet

- Electrical system service guideDocument301 pagesElectrical system service guideVygintas Balcius92% (12)

- Case Construction Backhoe Loader Tier3Document23 pagesCase Construction Backhoe Loader Tier3Nick E100% (1)

- S1L2-J1 - Technical Data SheetDocument9 pagesS1L2-J1 - Technical Data SheetthainarimeNo ratings yet

- GSM Vs Cdma PresentationDocument39 pagesGSM Vs Cdma Presentationaaki_2005No ratings yet

- Chapter 1 Fundamentals of Computer DesignDocument40 pagesChapter 1 Fundamentals of Computer DesignAbdullahNo ratings yet

- Machine Experiment 1Document7 pagesMachine Experiment 1Ujin MalabananNo ratings yet

- Tata Solar SunJeevini (Screen)Document2 pagesTata Solar SunJeevini (Screen)vijayrajbpNo ratings yet

- CYMGRD Wind Turbine Grounding PDFDocument4 pagesCYMGRD Wind Turbine Grounding PDFjaneth lozanoNo ratings yet

- Downloadable Version - Electronic H&S IdenitfierDocument13 pagesDownloadable Version - Electronic H&S IdenitfierasadiqbalansariNo ratings yet

- Difference Between IIR and FIR FiltersDocument2 pagesDifference Between IIR and FIR FiltersSaroj TimsinaNo ratings yet

- Digital Compass using CMPS03 ModuleDocument7 pagesDigital Compass using CMPS03 ModuleJuita JunidNo ratings yet

- DC Motors: - Construction Very Similar To A DC GeneratorDocument35 pagesDC Motors: - Construction Very Similar To A DC GeneratorDeepak Ganachari100% (1)

- 4Gb, 8Gb, 16Gb: x8, x16 NAND Flash Memory FeaturesDocument132 pages4Gb, 8Gb, 16Gb: x8, x16 NAND Flash Memory FeaturesVasil StoianovNo ratings yet

- Thermo Plus 230 Thermo Plus 300 Thermo Plus 350: Heating SystemsDocument63 pagesThermo Plus 230 Thermo Plus 300 Thermo Plus 350: Heating SystemsДмитро ПоловнякNo ratings yet

- Constant Voltage Constant Current DC Power SupplyDocument56 pagesConstant Voltage Constant Current DC Power SupplySeven HillsNo ratings yet

- E LynX Family - BrochureDocument12 pagesE LynX Family - Brochure573563876luNo ratings yet

- ClocksDocument4 pagesClocksluizcpimentaNo ratings yet

- Transistor Tester with AVR microcontroller: A device for determining and measuring electronic componentsDocument140 pagesTransistor Tester with AVR microcontroller: A device for determining and measuring electronic componentsEdgard MachadoNo ratings yet

- XL4015 5A 180KHz 36V Buck DC to DC Converter DatasheetDocument9 pagesXL4015 5A 180KHz 36V Buck DC to DC Converter DatasheetJose M PeresNo ratings yet

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionFrom EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionRating: 4.5 out of 5 stars4.5/5 (542)

- Get Into UX: A foolproof guide to getting your first user experience jobFrom EverandGet Into UX: A foolproof guide to getting your first user experience jobRating: 4.5 out of 5 stars4.5/5 (5)

- How to Do Nothing: Resisting the Attention EconomyFrom EverandHow to Do Nothing: Resisting the Attention EconomyRating: 4 out of 5 stars4/5 (421)

- Ultimate Guide to LinkedIn for Business: Access more than 500 million people in 10 minutesFrom EverandUltimate Guide to LinkedIn for Business: Access more than 500 million people in 10 minutesRating: 5 out of 5 stars5/5 (5)

- Ten Arguments for Deleting Your Social Media Accounts Right NowFrom EverandTen Arguments for Deleting Your Social Media Accounts Right NowRating: 4 out of 5 stars4/5 (388)

- Secrets of the Millionaire Mind: Mastering the Inner Game of WealthFrom EverandSecrets of the Millionaire Mind: Mastering the Inner Game of WealthRating: 4.5 out of 5 stars4.5/5 (197)

- The Social Media Bible: Tactics, Tools, and Strategies for Business SuccessFrom EverandThe Social Media Bible: Tactics, Tools, and Strategies for Business SuccessRating: 3.5 out of 5 stars3.5/5 (19)

- Web Copy That Sells: The Revolutionary Formula for Creating Killer Copy That Grabs Their Attention and Compels Them to BuyFrom EverandWeb Copy That Sells: The Revolutionary Formula for Creating Killer Copy That Grabs Their Attention and Compels Them to BuyRating: 4 out of 5 stars4/5 (13)

- Ultimate Guide to YouTube for BusinessFrom EverandUltimate Guide to YouTube for BusinessRating: 5 out of 5 stars5/5 (1)

- High Performance Loudspeakers: Optimising High Fidelity Loudspeaker SystemsFrom EverandHigh Performance Loudspeakers: Optimising High Fidelity Loudspeaker SystemsRating: 4 out of 5 stars4/5 (1)

- The Internet Con: How to Seize the Means of ComputationFrom EverandThe Internet Con: How to Seize the Means of ComputationRating: 5 out of 5 stars5/5 (6)

- Understanding Automotive Electronics: An Engineering PerspectiveFrom EverandUnderstanding Automotive Electronics: An Engineering PerspectiveRating: 3.5 out of 5 stars3.5/5 (16)

- Conquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeFrom EverandConquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeRating: 5 out of 5 stars5/5 (8)

- How to Create Cpn Numbers the Right way: A Step by Step Guide to Creating cpn Numbers LegallyFrom EverandHow to Create Cpn Numbers the Right way: A Step by Step Guide to Creating cpn Numbers LegallyRating: 4 out of 5 stars4/5 (27)

- Build Your Own Electric Vehicle, Third EditionFrom EverandBuild Your Own Electric Vehicle, Third EditionRating: 4.5 out of 5 stars4.5/5 (3)

- Off-Grid Projects: Step-by-Step Guide to Building Your Own Off-Grid SystemFrom EverandOff-Grid Projects: Step-by-Step Guide to Building Your Own Off-Grid SystemNo ratings yet

- Digital Gold: The Beginner's Guide to Digital Product Success, Learn Useful Tips and Methods on How to Create Digital Products and Earn Massive ProfitsFrom EverandDigital Gold: The Beginner's Guide to Digital Product Success, Learn Useful Tips and Methods on How to Create Digital Products and Earn Massive ProfitsRating: 5 out of 5 stars5/5 (3)

- The Graphene Revolution: The Weird Science of the Ultra-thinFrom EverandThe Graphene Revolution: The Weird Science of the Ultra-thinRating: 4.5 out of 5 stars4.5/5 (4)

- TikTok Algorithms 2024 $15,000/Month Guide To Escape Your Job And Build an Successful Social Media Marketing Business From Home Using Your Personal Account, Branding, SEO, InfluencerFrom EverandTikTok Algorithms 2024 $15,000/Month Guide To Escape Your Job And Build an Successful Social Media Marketing Business From Home Using Your Personal Account, Branding, SEO, InfluencerRating: 4 out of 5 stars4/5 (4)

- 8051 Microcontroller: An Applications Based IntroductionFrom Everand8051 Microcontroller: An Applications Based IntroductionRating: 5 out of 5 stars5/5 (6)

- Photographic Rendering with VRay for SketchUpFrom EverandPhotographic Rendering with VRay for SketchUpRating: 5 out of 5 stars5/5 (2)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XFrom EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XRating: 3 out of 5 stars3/5 (2)