Professional Documents

Culture Documents

VLSI - Memory Design (SRAM)

Uploaded by

Karthik RamasamyOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VLSI - Memory Design (SRAM)

Uploaded by

Karthik RamasamyCopyright:

Available Formats

EE 577a VLSI DESIGN I FALL 2013 INSTRUCTOR: M.

PEDRAM LAB ASSIGNMENT 1

Submitted by

KARTHIK RAMASAMY 5539 4733 38

SPECIFICATION:

Supply Vdd = 1.8V. Data and Clock transitions are 10ps. Clock signal has 50% duty cycle. Both true and the complement signals are available.

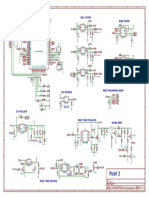

SRAM CELL DESIGN:

1. 256 bit SRAM DESIGN: a) Read Delay (ns) 0.33 0.28 Write Delay (ns) 0.065 0.06

i. ii.

All 6T of 4/2 6/2 Inverter Nmos 4/2 Nmos Access 4/3 Inverter Pmos

I have chosen the case ii. The area for the 6T SRAM cell of Case ii: 4.6 * 5.05 = 22.725 b) Comparison of Architectures: The following observations are from the schematic simulations mimicking the load capacitances of the different Architectures. Read Delay (ns) 0.33 0.33 0.328 Write Delay (ns) 0.225 0.203 0.22

i. ii. iii.

One 644 Bit Two 324 Bit (2-1 Mux) Four 164 Bit (4-1 Mux)

Model: = 50.14 = 225.78 fF The elmore delay = 0.69 /2 = 3.9 ps

c) The Architecture chosen is 32 8 with 4 (2-1) Mux.

i. ii. iii.

The BIT BIT line bar time is 226 ps. Sense Amplifier delay is 58 ps. The write delay is less than the read delay.

Sizing: Sense Amplifier (Optimized) = 3um = 800nm = 800nm = 600nm = 600nm = 1um = 1um

Mux: (Read,Write) Mux has the sizing of W = 4um L = 200nm The write and the Precharge circuitry has the default sizing.

2. DECODER DESIGN: The pre decoding implementation is done with the 3 input NAND, 2 input NAND and 3 input NOR gates with a enable signal.

3. OUTPUT REGISTER: The D-FLIP FLOP (4 FF) using Transmission Gate is used at the output of the Sense Amplifier with the Clock Period of 3ns.

4. SRAM LAYOUT: The 256 bit SRAM Layout is done using the optimized 6T SRAM cell, Row Decoder, Write Circuitry, Read Circuitry, Column Muxes and the output Registers. Metal 1,2,3 are used for routing.

DELAY OF SRAM:

READ DELAY OF SRAM 256bits = 3ns AREA = 13,348.68

LVS OUTPUT: @(#)$CDS: LVS version 6.1.4-64b 09/21/2011 03:25 (sjfdl054) $ Command line: /usr/local/cadence/IC610/tools.lnx86/dfII/bin/64bit/LVS -dir 13/kramasam/cds/LVS -l -s -t /home/scf-13/kramasam/cds/LVS/layout 13/kramasam/cds/LVS/schematic Like matching is enabled. Net swapping is enabled. Using terminal names as correspondence points. Compiling Diva LVS rules... Net-list summary for /home/scf-13/kramasam/cds/LVS/layout/netlist count 808 nets 36 terminals 864 pmos 1412 nmos Net-list summary for /home/scf-13/kramasam/cds/LVS/schematic/netlist count 808 nets 36 terminals 840 pmos 1340 nmos /home/scf/home/scf-

Terminal correspondence points N778 N33 A0 N799 N94 A0_b N776 N87 A1 N785 N91 A1_b N775 N83 A2 N800 N101 A2_b N774 N98 A3 N786 N105 A3_b N773 N97 A4 N801 N104 A4_b N772 N38 A5 N787 N100 A5_b N805 N14 D0 N804 N99 D1 N803 N26 D2 N802 N103 D3 N784 N92 D_b0 N783 N86 D_b1 N782 N52 D_b2 N780 N74 D_b3

N806 N792 N795 N791 N797 N790 N777 N789 N798 N788 N779 N796 N807 N793 N781 N794

N50 N22 N27 N82 N79 N13 N96 N12 N95 N15 N20 N49 N19 N17 N1 N0

Precharge Read_en Write_en Z0 Z0_b Z1 Z1_b Z2 Z2_b Z3 Z3_b clk clk_b en gnd! vdd!

Devices in the netlist but not in the rules: pcapacitor Devices in the rules but not in the netlist: cap nfet pfet nmos4 pmos4 The net-lists match. layout schematic instances 0 0 0 0 0 0 0 0 2276 2180 2276 2180 nets 0 0 0 808 808

un-matched rewired size errors pruned active total

un-matched merged pruned active total

0 0 0 808 808

un-matched matched but different type total

terminals 0 0 0 36 0 36

Probe files from /home/scf-13/kramasam/cds/LVS/schematic devbad.out: netbad.out: mergenet.out: termbad.out: prunenet.out: prunedev.out: audit.out: Probe files from /home/scf-13/kramasam/cds/LVS/layout devbad.out: netbad.out: mergenet.out: termbad.out: prunenet.out: prunedev.out: audit.out:

WAVEFORMS: SCHEMATIC:

LAYOUT WAVEFORMS:

You might also like

- RV12 RISC-V CPU Core DatasheetDocument73 pagesRV12 RISC-V CPU Core DatasheetJoão VictorNo ratings yet

- MOS Transistor IV Modeling and Regions of OperationDocument47 pagesMOS Transistor IV Modeling and Regions of OperationRaga LasyaNo ratings yet

- Design of A RISC Microcontroller Core in 48 HoursDocument11 pagesDesign of A RISC Microcontroller Core in 48 HoursPulkit TrivediNo ratings yet

- DFT For SRAMDocument9 pagesDFT For SRAMsuneeldvNo ratings yet

- Using Oracle Erp Cloud Adapter Oracle IntegrationDocument91 pagesUsing Oracle Erp Cloud Adapter Oracle Integrationswapnil khokeNo ratings yet

- Layout ExamplesDocument13 pagesLayout Examplesnazibhd786No ratings yet

- Resource Efficient LDPC Decoders: From Algorithms to Hardware ArchitecturesFrom EverandResource Efficient LDPC Decoders: From Algorithms to Hardware ArchitecturesNo ratings yet

- Embedded Systems Model Paper PDFDocument4 pagesEmbedded Systems Model Paper PDFසම්පත් චන්ද්රරත්නNo ratings yet

- Hspice 2005Document173 pagesHspice 2005何明俞No ratings yet

- Zipper Cmos Logic CircuitDocument15 pagesZipper Cmos Logic CircuitShreerama Samartha G BhattaNo ratings yet

- 6t Sram CellDocument4 pages6t Sram CellKhushi SidNo ratings yet

- MOSFETDocument21 pagesMOSFETParul Trivedi100% (1)

- 6T SRAM SimulationDocument9 pages6T SRAM SimulationAzza FaiadNo ratings yet

- Mos Transistor TheoryDocument144 pagesMos Transistor TheorymailtolokiNo ratings yet

- DelayDocument31 pagesDelayvarun186No ratings yet

- VLSI Lab CompendiumDocument52 pagesVLSI Lab CompendiumSaad Ali Khan SherwaniNo ratings yet

- Flash ADC MidsemDocument9 pagesFlash ADC MidsemBikashKumarMoharanaNo ratings yet

- Wire ModelingDocument68 pagesWire ModelingprocatellNo ratings yet

- Mississippi State University Dallas Semiconductor: Standard Cell TutorialDocument133 pagesMississippi State University Dallas Semiconductor: Standard Cell Tutorialshri3415No ratings yet

- Vlsi - CalculatorDocument14 pagesVlsi - CalculatorKarthik RamasamyNo ratings yet

- A Comparative Study of 6T, 8T and 9T SRAM CellDocument4 pagesA Comparative Study of 6T, 8T and 9T SRAM CellijaertNo ratings yet

- VLSI Design Assignment ReportDocument18 pagesVLSI Design Assignment ReportAlamgir MohammedNo ratings yet

- ESDynamic Logic CircuitsDocument61 pagesESDynamic Logic CircuitsMandovi BorthakurNo ratings yet

- 33 7 LM V1 S1 Delay ModelingDocument39 pages33 7 LM V1 S1 Delay ModelingPriyanka AshishNo ratings yet

- VLSI UNIT 1 Part - III PDFDocument35 pagesVLSI UNIT 1 Part - III PDFKARTHIKAYEN ANo ratings yet

- Logical Effort: Boris Murmann Center For Integrated Systems Stanford UniversityDocument10 pagesLogical Effort: Boris Murmann Center For Integrated Systems Stanford UniversitysatyajtiNo ratings yet

- Lecture 8 - Circuits Design Issues and Layout FormationDocument18 pagesLecture 8 - Circuits Design Issues and Layout FormationevildoctorbluetoothNo ratings yet

- Sensori A Stato Solido LS Presentazione TCAD Sentaurus PDFDocument27 pagesSensori A Stato Solido LS Presentazione TCAD Sentaurus PDFBharath KumarNo ratings yet

- Lecture 12 SRAMDocument37 pagesLecture 12 SRAMSachin MalikNo ratings yet

- CMOS OpAmp Design FundamentalsDocument62 pagesCMOS OpAmp Design FundamentalsNikitaPrabhuNo ratings yet

- Two Stage Op-AmpDocument4 pagesTwo Stage Op-AmpShreerama Samartha G BhattaNo ratings yet

- Elmore Delay in RC Networks: September 16, 2010Document3 pagesElmore Delay in RC Networks: September 16, 2010Siddharth SabharwalNo ratings yet

- MOS Device Physics for Analog Circuit DesignDocument59 pagesMOS Device Physics for Analog Circuit DesignNana Sarkodie KwakyeNo ratings yet

- CMOS Digital Integrated Circuits: Lec 5 SPICE Modeling of MOSFETDocument16 pagesCMOS Digital Integrated Circuits: Lec 5 SPICE Modeling of MOSFETNIET14No ratings yet

- Lab 5 Music Player and Audio Amp Fall 2014Document8 pagesLab 5 Music Player and Audio Amp Fall 2014SteveNo ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument84 pagesDigital Integrated Circuits: A Design PerspectivedurraizaliNo ratings yet

- VLSI Design Timing Analysis and Closure TechniquesDocument47 pagesVLSI Design Timing Analysis and Closure TechniquesErshad ShaikNo ratings yet

- Microcontroller Lab Manual (10ESL47) BY RAGHUNATHDocument87 pagesMicrocontroller Lab Manual (10ESL47) BY RAGHUNATHRaghunath B HNo ratings yet

- Lecture3 PartitionDocument24 pagesLecture3 Partitionapi-3834272No ratings yet

- Remove Glitches in Physical DesignDocument120 pagesRemove Glitches in Physical Designసుశీల్ శరత్No ratings yet

- TriennaleDocument129 pagesTriennaleJesus UrrestiNo ratings yet

- Lecture 3 Single Stage AmplifiersDocument76 pagesLecture 3 Single Stage Amplifierstranhieu_hcmutNo ratings yet

- ECE 4141-Experiment 3 - CMOS NAND Transistors Sizing Simulation Using PSPICEDocument6 pagesECE 4141-Experiment 3 - CMOS NAND Transistors Sizing Simulation Using PSPICEAnwar Zainuddin100% (2)

- CMOS Transistor Theory LectureDocument44 pagesCMOS Transistor Theory Lecturesadia santaNo ratings yet

- Introduction To Cmos Vlsi Design: SPICE SimulationDocument28 pagesIntroduction To Cmos Vlsi Design: SPICE SimulationSarthak SharmaNo ratings yet

- Aulas15 16Document16 pagesAulas15 16Pramod Reddy RNo ratings yet

- Cadence Virtuoso Inverter Front End To Back End Design TutorialDocument7 pagesCadence Virtuoso Inverter Front End To Back End Design TutorialEr Sourav NathNo ratings yet

- Ec1354 Vlsi by Suresh.mDocument75 pagesEc1354 Vlsi by Suresh.mSuresh Muthu100% (1)

- Mosfet 1Document33 pagesMosfet 1Palash SwarnakarNo ratings yet

- gpdk090 PDK ReferencemanualDocument31 pagesgpdk090 PDK ReferencemanualAshish JoshiNo ratings yet

- VLSIDocument12 pagesVLSIPeer MohamedNo ratings yet

- VLSI & Embedded Systems Lab ManualDocument137 pagesVLSI & Embedded Systems Lab Manualganga avinash reddyNo ratings yet

- Clocked CmosDocument24 pagesClocked CmosAnil KumarNo ratings yet

- Delay Time Estimation in Digital DesignDocument12 pagesDelay Time Estimation in Digital DesignSandeep PaulNo ratings yet

- Hspice OptimizationDocument8 pagesHspice OptimizationAnand ThibbaiahNo ratings yet

- Cmos Design Lab Manual: Developed by University Program Team Coreel Technologies (I) Pvt. LTDDocument69 pagesCmos Design Lab Manual: Developed by University Program Team Coreel Technologies (I) Pvt. LTDRasool NayabNo ratings yet

- 32k-Bit Sleepy SramDocument18 pages32k-Bit Sleepy Sramapi-19668941No ratings yet

- Design of Variable Resolution Flash ADC Using TIQDocument30 pagesDesign of Variable Resolution Flash ADC Using TIQJoHnson TaYeNo ratings yet

- Systemc-Ams Tutorial: Institute of Computer Technology Vienna University of Technology Markus DammDocument26 pagesSystemc-Ams Tutorial: Institute of Computer Technology Vienna University of Technology Markus DammAamir HabibNo ratings yet

- Standard Cell TutorialDocument133 pagesStandard Cell TutorialHasib Hamidul HaqueNo ratings yet

- 512MbDDR2 1Document129 pages512MbDDR2 1Naizath AmirNo ratings yet

- Data Path Design (Adder and Multiplier)Document76 pagesData Path Design (Adder and Multiplier)Karthik RamasamyNo ratings yet

- VLSI Fabrication and CharacterizationDocument40 pagesVLSI Fabrication and CharacterizationKarthik RamasamyNo ratings yet

- VLSI - Data Path Design (Adders)Document58 pagesVLSI - Data Path Design (Adders)Karthik RamasamyNo ratings yet

- VLSI - Neuron and Neural Network DesignDocument25 pagesVLSI - Neuron and Neural Network DesignKarthik Ramasamy100% (1)

- Phase Noise Cancellation in OFDM SystemsDocument66 pagesPhase Noise Cancellation in OFDM SystemsKarthik RamasamyNo ratings yet

- Vlsi - CalculatorDocument14 pagesVlsi - CalculatorKarthik RamasamyNo ratings yet

- Tarifa PVD Five 09-10-12Document20 pagesTarifa PVD Five 09-10-12Txetxu_No ratings yet

- Desktop Virtualization Assessment ReportDocument4 pagesDesktop Virtualization Assessment ReportOhms BrangueloNo ratings yet

- 422 Touch Flat LGPDocument1 page422 Touch Flat LGPNathan BukoskiNo ratings yet

- MSI PS63 Modern-085 PDFDocument1 pageMSI PS63 Modern-085 PDFVandyNo ratings yet

- Intelligent Security Time Attendance SolutionDocument2 pagesIntelligent Security Time Attendance SolutionchensomNo ratings yet

- Schematic of 4 Way Set Associative Cache With LRUDocument1 pageSchematic of 4 Way Set Associative Cache With LRUVishakhNo ratings yet

- 8086 Microprocessor Instruction Set OverviewDocument9 pages8086 Microprocessor Instruction Set Overviewsiddharth singhNo ratings yet

- 9032 005 PresentationDocument138 pages9032 005 PresentationBillcNo ratings yet

- PickitDocument1 pagePickitshubhamformeNo ratings yet

- MIC QB Units 2.5Document2 pagesMIC QB Units 2.5Ojaswini BorseNo ratings yet

- External MemoryDocument46 pagesExternal Memorybe adabNo ratings yet

- 01.Ansv - giới Thiệu Vmware-Ao HoaDocument16 pages01.Ansv - giới Thiệu Vmware-Ao HoaQuốc Việt TrầnNo ratings yet

- Debug 1214Document16 pagesDebug 1214PeachBlossomNo ratings yet

- Memory Management in xv6Document14 pagesMemory Management in xv6MeghanaNo ratings yet

- LENOVO Ideacentre k410 User GuideDocument57 pagesLENOVO Ideacentre k410 User GuideGLOCK35No ratings yet

- Tabela PrecosDocument72 pagesTabela PrecosJhoni OlingerNo ratings yet

- Intel's PENTIUM-II III PROCESSORSDocument24 pagesIntel's PENTIUM-II III PROCESSORSgovindamittal07No ratings yet

- Epelsa Eco Multifunction PDFDocument57 pagesEpelsa Eco Multifunction PDFMárcioNo ratings yet

- Clas Note 2Document88 pagesClas Note 2yusNo ratings yet

- Bahasa Assembly 1 (Compatibility Mode)Document29 pagesBahasa Assembly 1 (Compatibility Mode)itmyNo ratings yet

- Instruction Set ArchitectureDocument10 pagesInstruction Set ArchitecturejoNo ratings yet

- DX DiagDocument33 pagesDX DiagAnonymous IRgjScvBNo ratings yet

- COMPUTER SYSTEM HARDWARE COURSE OVERVIEWDocument3 pagesCOMPUTER SYSTEM HARDWARE COURSE OVERVIEWyadhu krishnanNo ratings yet

- Transforming The Data Center: Dell Poweredge 12Th Generation ServersDocument13 pagesTransforming The Data Center: Dell Poweredge 12Th Generation ServersblussierttNo ratings yet

- Bios Interrupt ProgrammingDocument14 pagesBios Interrupt ProgrammingsaliksiddiquiNo ratings yet

- Upa Usb PDFDocument57 pagesUpa Usb PDFTomas FleitasNo ratings yet

- Asas Pengaturcaraan Arduino Menggunakan Mblocks: User Guide V3.0Document56 pagesAsas Pengaturcaraan Arduino Menggunakan Mblocks: User Guide V3.0Mohdzamri Shari100% (1)

- Caution: Multi-Series Truck Download Tool Operating InstructionsDocument4 pagesCaution: Multi-Series Truck Download Tool Operating InstructionsNuylan AnjoNo ratings yet