Professional Documents

Culture Documents

9A15502 Digital System Design

Uploaded by

sivabharathamurthyCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

9A15502 Digital System Design

Uploaded by

sivabharathamurthyCopyright:

Available Formats

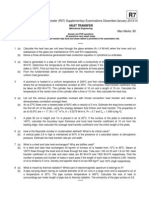

Code: 9A15502

B.Tech III Year I Semester (R09) Regular & Supplementary Examinations December/January 2013/14

DIGITAL SYSTEM DESIGN

(Computer Science & Systems Engineering)

Time: 3 hours Answer any FIVE questions All questions carry equal marks ***** 1 Draw an ASM chart to design a FSM which directs 11001 and 10001 bit sequences and set output Z = 1. For all offer sequences Z = 0. Realize the sequence detector using D-flip-flops and MUXs. (a) Describe some important features of an FPGA and a CPLD. (b) With an example, explain how an FPGA is useful in the design of a digital circuit. What is the significance of Kohavi algorithm? Explain how it is useful in the detection of faults in digital circuits. (a) With an example, explain, the transition count testing method. (b) Describe the algorithm steps involved in PODEM. Design a fault diagnosable machine for the 101 sequence detector. Use successor tree. (a) Describe the advantages of PLA minimization and folding. (b) Design a 3 bit BCD to grey code converter and realize the circuit using PLA and then show that how folding will reduce the number of cross points on the PLA. Describe the various DFT schemes used in digital circuits. (a) With respect to an Asynchronous sequential machine, explain about minimal closed covers. (b) Explain the following with examples: (i) Flow table. (ii) State reduction. Max. Marks: 70

5 6

7 8

*****

Code: 9A15502

B.Tech III Year I Semester (R09) Regular & Supplementary Examinations December/January 2013/14

DIGITAL SYSTEM DESIGN

(Computer Science & Systems Engineering)

Time: 3 hours Answer any FIVE questions All questions carry equal marks ***** 1 (a) Draw an ASM chart to design a control logic of a binary multiplier. Realize the same using MUX decoder and D-type flip-flops. (b) What is difference between Melay and Moore state machine? Draw the general structure of an FPGA and explain how a logic function can be realized on FPGA with a suitable example. What are the different faults found in combinational circuits? How can they be categorized? With an example, explain the transition count testing method, signature analysis and random testing. (a) Find a preset distinguish experiment that determine the initial state of the machine shown in table given below. Given that it cannot be initially in state E. (b) Can you identify the initial state when the initial uncertainty is (ABCDE)? Table Ns Z Ps X=0 X=1 A B,1 A,1 B E,0 A,1 C A,0 E,1 D C,1 D,1 E E,0 D,1 Apply PLA maximization procedure and obtain the minimized expression to be implemented on PLAF = 2021 + 0022 + 1200. Discuss the steps involved in the PLA folding algorithm compact. Write a short notes on: (i) Fundamental mode model. (ii) Races, cycles and hazards. Max. Marks: 70

3 4

7 8

*****

Code: 9A15502

B.Tech III Year I Semester (R09) Regular & Supplementary Examinations December/January 2013/14

DIGITAL SYSTEM DESIGN

(Computer Science & Systems Engineering)

Time: 3 hours Answer any FIVE questions All questions carry equal marks ***** 1 (a) Develop an ASM chart of D-flip-flop and realize it using only NAND gates. (b) Discuss in detail about reduction of state table and state assignments. Explain the steps involved in system design using PLA with an example. (a) List out the Boolean difference properties and explain them. (b) Apply Kohavis algorithm to the given POS function F = (A+ ) (C+BD). (a) Briefly describe about the different types of fault model and fault types in a PLA. (b) Explain briefly about random testing and transition count testing. (a) Discuss the BIST scheme for PLD and CPLDs. (b) With an example, explain the principle of operation of path sensitizations method. (a) Explain briefly, the occurrence of various types of hazards in digital circuits. (b) With an example, explain how faults are detected in a PLA. Describe a square generator of a given 3-bit input using PROM. Describe an asynchronous BCD down counter using JK flip-flops and explain its operation. Max. Marks: 70

2 3

7 8

*****

Code: 9A15502

B.Tech III Year I Semester (R09) Regular & Supplementary Examinations December/January 2013/14

DIGITAL SYSTEM DESIGN

(Computer Science & Systems Engineering)

Time: 3 hours Answer any FIVE questions All questions carry equal marks ***** 1 (a) What are the basic fault model in digital systems? How they are diagonized? (b) Write a brief note on cube based operations. Apply CAMP II algorithm to the following 5 variable function and obtain the minimized function. F( A,B,C,D,E) = (a) Draw the table giving the set of all possible single struck faults and the faulty-free responses and also construct the fault cover table for circuit in figure. Max. Marks: 70

(b) Explain compact algorithm used in PLA folding. 4 Apply D-algorithm to detect h SAO fault in the given circuit and derive the test vectors. A B f C X h

(a) Draw the general structure of a CPLD and explain how a logic function can be realized on CPLD with simple example. (b) How does the ASM chart differ from a software flow chart. Write a short note on: (a) Design for testability. (b) Field programmable gate arrays. (a) Apply PLA maximization procedure and obtain the minimized expression to be implemented on PLA. F = 2021 + 0022 +1200. (b) Obtain the minimum test vector set for the above function F in 7(a). What is testing? Explain briefly test generation and testable PLA design. *****

You might also like

- Tableau Cheat Sheet 25 Feb 2014 PDocument5 pagesTableau Cheat Sheet 25 Feb 2014 Pjjlorika100% (1)

- Strategic Planning Worksheets 4-17-121Document11 pagesStrategic Planning Worksheets 4-17-121Syed Qaiser HussainNo ratings yet

- Computer Architecture Question BankDocument7 pagesComputer Architecture Question BankSalma Mehajabeen ShajahanNo ratings yet

- Sheet Metal CATIA PDFDocument398 pagesSheet Metal CATIA PDFdottorgt5845No ratings yet

- VLSI DesignDocument19 pagesVLSI DesignEr Deepak GargNo ratings yet

- Scope Management Plan Template With InstructionsDocument6 pagesScope Management Plan Template With InstructionsshimelisNo ratings yet

- U Boot AbcdgeDocument232 pagesU Boot AbcdgeDineshkumarparamesNo ratings yet

- GCCG e-Banking Portal SOWDocument3 pagesGCCG e-Banking Portal SOWAnonymous CZAc9juNo ratings yet

- MUltimedia Compression Techniques Question PaperDocument2 pagesMUltimedia Compression Techniques Question PaperPurush Jayaraman100% (1)

- Microprocessor and Interfacing Questions for UCET ExamDocument4 pagesMicroprocessor and Interfacing Questions for UCET ExamDarshan SharmaNo ratings yet

- Py Open GLDocument324 pagesPy Open GLMartin Cruz OtinianoNo ratings yet

- Cs9251 Mobile Computing Question BankDocument16 pagesCs9251 Mobile Computing Question BankNivithaNo ratings yet

- Plan Reconciliation of Internal ActivitiesDocument7 pagesPlan Reconciliation of Internal ActivitiesZakir ChowdhuryNo ratings yet

- VL7301 Testing of VLSI CircuitsDocument8 pagesVL7301 Testing of VLSI Circuitsmanojece80100% (1)

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)Val GinNo ratings yet

- 54208-mt - Design For TestabilityDocument2 pages54208-mt - Design For TestabilitySRINIVASA RAO GANTA100% (1)

- Embedded Syatem Question Paper.Document1 pageEmbedded Syatem Question Paper.Saurabh SinghNo ratings yet

- Ap5191 Embedded System DesignDocument3 pagesAp5191 Embedded System DesignHasib Al-ariki100% (1)

- Microprocessor and Microcontroller Anna University Question PapersDocument3 pagesMicroprocessor and Microcontroller Anna University Question PapersthennishaNo ratings yet

- Computer Architecture & OrganizationDocument4 pagesComputer Architecture & OrganizationUma MaheswariNo ratings yet

- Software Design For Low PowerDocument20 pagesSoftware Design For Low PowerGokul B S MandyaNo ratings yet

- Cao Imp QuestionsDocument3 pagesCao Imp QuestionsTejas Nage PatilNo ratings yet

- Introduction to DSP Processors ArchitectureDocument45 pagesIntroduction to DSP Processors ArchitectureLavanya KattaNo ratings yet

- HDL Model QPDocument5 pagesHDL Model QPSubramanyaAIyerNo ratings yet

- Advanced Embedded Systems (10EC118)Document2 pagesAdvanced Embedded Systems (10EC118)Shashank HollaNo ratings yet

- Electronic Devices Model Question PapersDocument2 pagesElectronic Devices Model Question Papersk_kunarajNo ratings yet

- Dica Unit-1Document18 pagesDica Unit-1PrasannaKumar KaraNamNo ratings yet

- 18CS44 Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)Document2 pages18CS44 Model Question Paper-1 With Effect From 2019-20 (CBCS Scheme)M.A rajaNo ratings yet

- ACN Question BankDocument3 pagesACN Question BankPreeti Julian D'souzaNo ratings yet

- Compiler Lab Manual RCS 652Document33 pagesCompiler Lab Manual RCS 652Afsana SaleemNo ratings yet

- EC8791 Important QuestionsDocument27 pagesEC8791 Important QuestionsSurendar PNo ratings yet

- VLSI Design and Testing Techniques for CMOS ChipsDocument22 pagesVLSI Design and Testing Techniques for CMOS Chipskashi vissu100% (1)

- MKC ES Units 3&4 ARM 1Document105 pagesMKC ES Units 3&4 ARM 1Varun ChilukuriNo ratings yet

- CU7202-MIC and RF System DesignDocument16 pagesCU7202-MIC and RF System DesignSaadNo ratings yet

- Important Questions Board Point of ViewDocument4 pagesImportant Questions Board Point of ViewUbaid SaudagarNo ratings yet

- WSN Question Bank For Mid 1Document6 pagesWSN Question Bank For Mid 1praneetha ChowdaryNo ratings yet

- Anna University CS2354 Advanced Computer Architecture Question PaperDocument2 pagesAnna University CS2354 Advanced Computer Architecture Question PaperpraveenaprabhuNo ratings yet

- 1 Semester Model Question PapersDocument17 pages1 Semester Model Question PapersBalaji MohantyNo ratings yet

- Digital Logic Design FundamentalsDocument3 pagesDigital Logic Design FundamentalssalmanNo ratings yet

- Operating Systems Study GuideDocument8 pagesOperating Systems Study GuideRAJESH100% (1)

- Computer Organisation and ArchitectureDocument6 pagesComputer Organisation and ArchitectureChalumuri JyothiswaroopNo ratings yet

- VLSI for Wireless Communication Question BankDocument13 pagesVLSI for Wireless Communication Question Bankjebas_ece100% (2)

- RTL Simulation and Synthesis With PLDs QP Mid-1Document1 pageRTL Simulation and Synthesis With PLDs QP Mid-1baburao_kodavati0% (1)

- Analog & Digital VLSI Design Practice QuestionsDocument24 pagesAnalog & Digital VLSI Design Practice QuestionsAbhinav MishraNo ratings yet

- Computer Organization and Microprocessor BasicsDocument7 pagesComputer Organization and Microprocessor Basicsjitesh100% (1)

- I-O PortsDocument20 pagesI-O PortsPradeep V DevNo ratings yet

- Electronically Tunable Chaotic Oscillators Using OTA-C Derived From Jerk ModelDocument23 pagesElectronically Tunable Chaotic Oscillators Using OTA-C Derived From Jerk ModelKhunanon KarawanichNo ratings yet

- DICA Question Bank Units - 1,2,3Document4 pagesDICA Question Bank Units - 1,2,3mkrNo ratings yet

- MCQ's DSP 201-300Document18 pagesMCQ's DSP 201-300Rohit NegiNo ratings yet

- Low Power VLSI Unit 2Document14 pagesLow Power VLSI Unit 2JAI ROYALNo ratings yet

- ARM7 LP2148 Tyro V4 User's Guide: Pantech Prolabs India PVT LTDDocument28 pagesARM7 LP2148 Tyro V4 User's Guide: Pantech Prolabs India PVT LTDAmbedkar RajanNo ratings yet

- Compiler Design exam questionsDocument1 pageCompiler Design exam questionsRasamsetty AnuNo ratings yet

- Lesson Plan Microprocessor and Micro COntrollerDocument7 pagesLesson Plan Microprocessor and Micro COntrollerRaja Pirian0% (2)

- 09 - Thread Level ParallelismDocument34 pages09 - Thread Level ParallelismSuganya Periasamy50% (2)

- ACP Question BankDocument5 pagesACP Question BanksunithaNo ratings yet

- M.tech Advanced Digital Signal ProcessingDocument2 pagesM.tech Advanced Digital Signal Processingsrinivas50% (2)

- Question Paper Distributed Systems - ECS-701 (12-13)Document2 pagesQuestion Paper Distributed Systems - ECS-701 (12-13)mukesh.iilm144100% (1)

- Assignments - NOC - MATLAB Programming For Numerical ComputationDocument9 pagesAssignments - NOC - MATLAB Programming For Numerical ComputationPraghashrajaNo ratings yet

- Switching & ForwardingDocument23 pagesSwitching & ForwardingK Sai AnirudhNo ratings yet

- 3408-Data StructureDocument3 pages3408-Data StructurecomtotapelNo ratings yet

- 9D57205 Scripting Language For VLSI Design AutomationDocument1 page9D57205 Scripting Language For VLSI Design AutomationNagarjuna Reddy100% (2)

- Ec2051 QBDocument3 pagesEc2051 QBBalajee Kowshik0% (1)

- 9A05704 Advanced Computer ArchitectureDocument4 pages9A05704 Advanced Computer ArchitecturesivabharathamurthyNo ratings yet

- 7th ITDocument6 pages7th ITYashika JindalNo ratings yet

- 9A12301 Digital Logic Design and Computer OrganizationDocument4 pages9A12301 Digital Logic Design and Computer OrganizationsivabharathamurthyNo ratings yet

- Simulation Modeling of Manufacturing Systems Exam QuestionsDocument8 pagesSimulation Modeling of Manufacturing Systems Exam QuestionsSrimanthula SrikanthNo ratings yet

- Control Systems (CS) Notes As Per JntuaDocument203 pagesControl Systems (CS) Notes As Per Jntuasivabharathamurthy100% (3)

- 07A4EC01 Environmental StudiesDocument1 page07A4EC01 Environmental StudiessivabharathamurthyNo ratings yet

- SSC Telugu (FL) (AP)Document232 pagesSSC Telugu (FL) (AP)sivabharathamurthyNo ratings yet

- R5410201 Neural Networks & Fuzzy LogicDocument1 pageR5410201 Neural Networks & Fuzzy LogicsivabharathamurthyNo ratings yet

- R7410407 Operating SystemsDocument1 pageR7410407 Operating SystemssivabharathamurthyNo ratings yet

- SSC Social Textbook (AP)Document100 pagesSSC Social Textbook (AP)sivabharathamurthyNo ratings yet

- R7410506 Mobile ComputingDocument1 pageR7410506 Mobile ComputingsivabharathamurthyNo ratings yet

- 9A05707 Software Project ManagementDocument4 pages9A05707 Software Project ManagementsivabharathamurthyNo ratings yet

- R7310406 Digital CommunicationsDocument1 pageR7310406 Digital CommunicationssivabharathamurthyNo ratings yet

- R7311506 Operating SystemsDocument1 pageR7311506 Operating SystemssivabharathamurthyNo ratings yet

- 9A13701 Robotics and AutomationDocument4 pages9A13701 Robotics and AutomationsivabharathamurthyNo ratings yet

- R7310506 Design & Analysis of AlgorithmsDocument1 pageR7310506 Design & Analysis of AlgorithmssivabharathamurthyNo ratings yet

- Code: R7311306: (Electronics & Control Engineering)Document1 pageCode: R7311306: (Electronics & Control Engineering)sivabharathamurthyNo ratings yet

- R7312301 Transport Phenomena in BioprocessesDocument1 pageR7312301 Transport Phenomena in BioprocessessivabharathamurthyNo ratings yet

- R7311205 Distributed DatabasesDocument1 pageR7311205 Distributed DatabasessivabharathamurthyNo ratings yet

- R5310204 Power ElectronicsDocument1 pageR5310204 Power ElectronicssivabharathamurthyNo ratings yet

- R7311006 Process Control InstrumentationDocument1 pageR7311006 Process Control InstrumentationsivabharathamurthyNo ratings yet

- R7310306 Heat TransferDocument1 pageR7310306 Heat Transfersivabharathamurthy100% (1)

- 9A05505 Operating SystemsDocument4 pages9A05505 Operating SystemssivabharathamurthyNo ratings yet

- R7310206 Linear Systems AnalysisDocument1 pageR7310206 Linear Systems AnalysissivabharathamurthyNo ratings yet

- R7310106 Engineering GeologyDocument1 pageR7310106 Engineering GeologysivabharathamurthyNo ratings yet

- 9A03505 Heat TransferDocument4 pages9A03505 Heat TransfersivabharathamurthyNo ratings yet

- 9A14503 Principles of Machine DesignDocument8 pages9A14503 Principles of Machine DesignsivabharathamurthyNo ratings yet

- R5310406 Digital CommunicationsDocument1 pageR5310406 Digital CommunicationssivabharathamurthyNo ratings yet

- 9A23501 Heat Transfer in BioprocessesDocument4 pages9A23501 Heat Transfer in BioprocessessivabharathamurthyNo ratings yet

- 9A21506 Mechanisms & Mechanical DesignDocument8 pages9A21506 Mechanisms & Mechanical DesignsivabharathamurthyNo ratings yet

- 9A10505 Principles of CommunicationsDocument4 pages9A10505 Principles of CommunicationssivabharathamurthyNo ratings yet

- 9A02505 Electrical Machines-IIIDocument4 pages9A02505 Electrical Machines-IIIsivabharathamurthyNo ratings yet

- 9A04504 Digital IC ApplicationsDocument4 pages9A04504 Digital IC ApplicationssivabharathamurthyNo ratings yet

- Strategic Analysis Decisions in The Next Five YearsDocument3 pagesStrategic Analysis Decisions in The Next Five YearsGeofrey Nyaga100% (5)

- DevOps Guide for Cynics Highlights Benefits for Developers, Leaders and MoreDocument16 pagesDevOps Guide for Cynics Highlights Benefits for Developers, Leaders and MoreraidenbrNo ratings yet

- Google RobotsDocument5 pagesGoogle RobotsNESTOR HERRERANo ratings yet

- Practical Programming 09Document257 pagesPractical Programming 09Mayank DhimanNo ratings yet

- Why Are Some OSPF Routes in The Database But Not in The Routing TableDocument19 pagesWhy Are Some OSPF Routes in The Database But Not in The Routing TableNapster KingNo ratings yet

- A 05Document33 pagesA 05Salman ShahidNo ratings yet

- Case A HRIS For Mid TermDocument4 pagesCase A HRIS For Mid Termwaqasfarooq75_396423No ratings yet

- ANSYS Known Issues 14 0Document4 pagesANSYS Known Issues 14 0Humayun NawazNo ratings yet

- Introduction To PHPDocument17 pagesIntroduction To PHPyunusmoha1970No ratings yet

- Assignment ON Microprocessor AND Microcontroller: Joyal Jose AugustineDocument63 pagesAssignment ON Microprocessor AND Microcontroller: Joyal Jose Augustineajas777BNo ratings yet

- Call and Delay InstructionsDocument7 pagesCall and Delay Instructionsnawazish_nehalNo ratings yet

- Cormen 2nd Edition SolutionsDocument99 pagesCormen 2nd Edition SolutionsManu ThakurNo ratings yet

- Java Programming For Human BeingsDocument80 pagesJava Programming For Human BeingsMiguel León NogueraNo ratings yet

- Wet DesignDocument1 pageWet DesigncharathNo ratings yet

- Micom S1 V2 For Micom Px40Document58 pagesMicom S1 V2 For Micom Px40Insan AzizNo ratings yet

- C# - Loops: Loop Control StatementsDocument2 pagesC# - Loops: Loop Control Statementspbc3199No ratings yet

- Macos Mojave Compatibility 02 07Document11 pagesMacos Mojave Compatibility 02 07Elnegro NegroNo ratings yet

- 2 Decimals and PercentDocument27 pages2 Decimals and PercentMonic RomeroNo ratings yet

- Consolidated Unpaid Dividend List As On 7 August 2018Document60 pagesConsolidated Unpaid Dividend List As On 7 August 2018Hari KNo ratings yet

- Noc18 cs48 Assignment3Document4 pagesNoc18 cs48 Assignment3shweta100% (1)

- OS_ISO_CollectionDocument10 pagesOS_ISO_CollectionWin TecNo ratings yet