Professional Documents

Culture Documents

EK-8A002-MM-002 PDP-8A Miniprocessor Users Manual Dec76

Uploaded by

kgrhoadsCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

EK-8A002-MM-002 PDP-8A Miniprocessor Users Manual Dec76

Uploaded by

kgrhoadsCopyright:

Available Formats

PDP-8/A MINIPROCESSOR

USERS MANUAL

E K-SA002-MM-002

digital equipment corporation maynard. massachusetts

1st Edition, November 1975

2nd Printing (Rev), December 1976

Copyright 1976 by Digital Equipment Corporation

The material in this manual is for informaticmal

purpOSElS and is subject to change without notice.

Digital Equipment Corporation assumes no respon-

sibility for any errors which may appear in this

manual..

Printed in U.S.A.

This document was set on DIGITAL'S DECset-8000

computerized typesetting system.

The following are trademarks of Digital Equipment

Corporation, Maynard, Massachusetts:

DEC

DECCOMM

DECsystnm-l0

DECSYSTEM-20

DECtape

DECUS

DIGITAL

MASSBUS

6/77-14

PDP

RSTS

TYPESET-S

TYPESET-11

UNIBUS

CHAPTER 1

1.1

1.1.1

1.1.2

1.1.3

1.1.4

1.1.5

1.1.6

1.1.7

1.1.S

1.1.9

1.1.10

1.1.11

1.1.12

1.1.13

1.1.14

1.1.15

1.2

1.2.1

1.2.2

1.2.3

1.2.4

1.2.5

CHAPTER 2

2.1

2.1.1

2.1.2

2.1.3

2.2

2.3

2.3.1

2.3.2

2.4

2.4.1

2.4.2

2.4.3

2.4.3.1

2.4.3.2

2.4.3.3

2.4.3.4

2.4.3.5

2.4.3.6

2.4.3.7

2.4.3.S

2.4.3.9

2.4.3.10

2.4.3.11

CONTENTS

INTRODUCTION AND DESCRIPTION

SYSTEM DESCRIPTION

Central Processor Unit (CPU)

KCS-AA Programmer's Console

Limited Function Panel

Memory .......... .

MMS-A Core Memory

MSS-A ReadIWrite Semiconductor Memory (RAM)

M RS-A Read Memory (ROM) .......... .

MRS-FB Reprogrammable Read Only Memory (PROM)

GS016 Power Supply Regulator Module

GS01S Power Supply Regulator Module

Interfacing ........... .. "

Option Modules ........... .

DKCS-AA I/O Option Board (MS316) .

KMS-A Extended Option Board (MS317)

Peripheral Options ..

CONSOLE OPERATION

Limited Function Panel

Programmer's Console

Entering Data From the Programmer's Console

Examining Memory Locations

Entering Data in Memory ...... .

INSTALLATION AND ACCEPTANCE TEST

SITE CONSIDERATIONS .. .

Power Source ..... .

I/O Cabling Requirements

Fire and Safety Precautions

UNPACKING INSTRUCTIONS

PACKING INSTRUCTIONS ..

BAS-C Chassis Assembly .

Other PDP-Sf A Chassis Assemblies

PDP-S/A BASIC SYSTEM COMPONENTS

Chassis Descriptions

Expansion Techniques ...... .

PDP-SI A Module Descriptions

KKS-A Central Processor Unit (CPU)

MSS-A ReadIWrite Random Access Memory (RAM)

MR8-A Read Only Random Access Memory (ROM)

MMS-AA SK Core Memory

MMS-AB 16K Core Memory

DKCS-AA 1/0 Option Board

KMS-A Extended Option Board

Semiconductor Memory Power Supply

Core Memory Power Supply Regulator

Limited Function Panel

KCS-AA Programmer's Console

iii

Page

1-4

l-S

1-S

l-S

l-S

l-S

l-S

1-9

1-9

1-9

1-9

1-9

1-10

1-10

1-10

1-10

1-10

1-10

1-10

1-10

1-11

1-11

2-1

2-2

2-2

2-2

2-2

2-3

2-3

2-3

2-7

2-S

2-14

2-14

2-14

2-16

2-16

2-21

2-21

2-24

2-2S

2-30

2-32

2-34

2-35

2.5

2.5.1

2.5.2

2.6

2.6.1

2.6.2

2.6.3

2.6.4

2.7

2.7.1

2.7.2

2.7.3

2.7.4

2.8

2.8.1

2.9

2.9.1

2.9.2

2.9.3

2.9.4

2.10

CHAPTER 3

3.1

3.2

3.3

3.3.1

3.3.2

3.3.3

3.3.4

3.4

3.5

3.6

3.6.1

3.6.2

3.6.2.1

3.6.2.2

3.6.3

3.6.4

3.6.5

3.6.6

3.6.7

3.6.8

3.6.9

3.6.10

3.6.11

3.7

3.7.1

CONTENTS (Cont)

INSTALLING THE PDP-8/A AND TURNING POWER ON FOR THE FI RST TIME

Environmental and Power Requirements ....... .

Turning on the Computer for the First Time ..... .

TESTING PDP-8/A WITHOUT PAPER TAPE DIAGNOSTICS

Programmer's Console ................ .

Central Processor Test Houtines ........... .

Entering Test Routines from the Programmer's Console

Central Processor Test Houtines .....

LOADING THE RIM AND BINARY LOADERS

Loading the RIM Loader .

Checking the RIM Loader ...... .

Loading the Binary Loader ...... .

Loading Binary Formatted Paper Tapes

TESTING THE PDP-8/A USING MAINDEC DIAGNOSTIC PROGRAMS

Central Processor Unit (CPU) Test

ADDITIONAL DIAGNOSTIC TESTS

Memory Test .......... .

DKC8-AA Test ......... .

KM8-A Extended Option Board Test

Testing Extended Memories

BASIC PDP-8/A MAINTENA.NCE .

INTERFACING TO THE OMNIBUS

OMNIBUS PHYSICAL DESCRIPTION

BUS SPECIFICATIONS ." ....

METHODS OF DATA TRANSFER

Programmed 1/0 Transfer

Interrupt Facility

Data Break Transfer

The External Bus . .

MODULE CONFIGURATION ON THE OMNIBUS

OMNIBUS PIN ASSIGNMENT

MAJOR GROUPS OF SIGNALS ......... .

Memory Address - 15 Lines ........ .

Memory Data and Memory Direction Control - 13 Lines

MD<0:11>L .

MD DIR L

Data Bus - 12 Lines .....

1/0 Control Signals - 10 Lines

DMA Control Signals -8 Lines

Timing Signals - 9 Lines ...

CPU States - 6 Lines

Memory Timing Signals - 5 Lines

Miscellaneous Signals -- 18 Lines

Special Signals ......... .

Interconnections ........ .

DETAILED DESCRIPTION OF THE 96 OMNIBUS SIGNALS

Memory Address - 15 Lines .............. .

iv

Page

2-35

2-35

2-35

2-36

2-37

2-37

2-38

2-38

2-40

2-40

2-41

2-41

2-43

2-43

. 2-44

2-45

2-45

2-46

2-50

2-54

2-55

3-1

3-3

3-3

3-3

3-3

3-3

3-4

3-4

3-5

3-8

3-8

3-8

3-8

3-8

3-8

3-8

3-8

3-8

3-8

3-8

3-8

3-9

3-9

3-9

3-9

3.7.1.1

3.7.1.2

3.7.2

3.7.2.1

3.7.2.2

3.7.3

3.7.4

3.7.4.1

3.7.4.2

3.7.4.3

3.7.4.4

3.7.4.5

3.7.4.6

3.7.4.7

3.7.4.8

3.7.5

3.7.5.1

3.7.5.2

3.7.5.3

3.7.5.4

3.7.5.5

3.7.5.6

3.7.5.7

3.7.5.8

3.7.6

3.7.7

3.7.7.1

3.7.7.2

3.7.8

3.7.8.1

3.7.8.2

3.7.8.3

3.7.8.4

3.7.9

3.7.9.1

3.7.9.2

3.7.9.3

3.7.9.4

3.7.9.5

3.7.9.6

3.7.9.7

3.7.9.8

3.7.9.9

3.7.9.10

3.7.9.11

3.7.9.12

3.7.9.13

3.7.9.14

CONTENTS (Cont)

EMA<0:2>L

MA<O:ll>L

Memory Data and D"irection Control - 13 Lines

MD<O:ll>L . . ....

MD DIR L ....... .

Data Bus - 12 Lines .... .

I/O Control Signals - 10 Lines .

I/O PAUSE L - Pin COl .

INTERNAL I/O L - Pin CLl

SKIP L - Pin CSl .....

INT RQST L - Pin CPl

C<0:2>L - Pins CEl (CO L); CHl (Cl L); CJl (C2 L)

BUS STROBE L - Pin CKl

NOT LAST XFER L - Pin CLl

INITIALIZE H - Pin CRl ..

DMA Control Signals - 8 Lines

BRK IN PROG L - Pin BE2 .

CPMA DISABLE L - Pin CUl

MS, IR DISABLE L - Pin CVl

MA, MS LOAD CONT L - Pin BH2

BREAK DATA CONT L - Pin BK2

OVERFLOW L - Pin BJ2

BK CYCLE L - Pin BL2

RUN L - Pin BU2

Timing Signals - 9 Lines

CPU STATE - 6 Lines

Major State Lines

IR<0:2>L ...

Memory Timing Signals - 5 Lines

SOURCE H - Pin AL2, and RETURN H - Pin AR2

WRITE H - Pin AS2 .

INHIBIT H - Pin AP2 ..

STROBE H - Pin AM2

Miscellaneous Signals - 18 Lines

INDl L - Pin CU2, and IND2 L - Pin CV2

MEM START L - Pin AJ2

STOP L - Pin DS2 ............ .

LINK L - Pin AV2

LINK LOAD L - Pin CS2, and LINK DATA L - Pin CR2

F SET L - Pin DP2

USER MODE L - Pin DM2 .............. .

INT IN PROG H - Pin BP2

LA ENABLE L - Pin BM2, and KEY CONTROL L - Pin DU2

PULSE LA H - Pin DR2 ...

ROM ADDRESS L - Pin AU2

NTS STALL L - Pin BR2

SW - Pin DV2 ..... .

POWER OK H - Pin BV2

v

Page

3-9

3-10

... 3-10

. 3-10

. 3-10

. 3-11

. 3-11

. 3-11

3-12

3-12

3-12

3-12

3-12

3-12

3-13

3-13

3-14

3-14

3-14

3-14

3-14

3-14

3-14

3-14

3-15

3-15

3-15

3-15

3-16

3-16

3-16

3-16

3-16

3-16

3-16

3-16

3-17

3-17

3-17

3-17

3-17

3-18

3-18

3-19

3-19

3-19

3-20

3-20

3.7.9.15

3.7.9.16

3.8

3.8.1

3.8.2

3.8.3

3.8.4

3.8.5

3.8.6

3.8.6.1

3.8.6.2

3.8.7

3.8.7.1

3.8.7.2

3.8.8

3.9

3.10

3.11

3.11.1

3.11.2

3.11.3

3.12

3.13

3.14

3.14.1

3.14.2

3.14.3

3.14.4

3.14.5

3.14.6

3.14.7

3.15

3.15.1

3.15.2

3.15.3

3.16

3.17

3.18

3.19

3.19.1

3.19.2

3.19.3

3.19.4

3.19.4.1

3.19.4.2

3.19.4.3

3.19.4.4

3.19.4.5

CONTENTS (Cont)

TIMING

RES - Pin BS2

Special Signals

Time Pulses and Time States

Memory Timing ..... .

Relationship Between CPU and Memory Timing

Basic 1/0 Timing ..

Expanded 1/0 Timing

Data Break Timing .

Data Exchange

Final Operations

CPU Major States

IR (FETCH Cycle) .

Interrupt Recognition

Timing Start and Stop .

ASYNCHRONOUS SIGNALS ..

SPECIAL SIGNALS ...... .

ELECTRICAL CHARACTERISTICS AND INTERFACING

Logic Levels

Bus Loads

Driving the Omnibus ......... .

DRIVE AVAILABLE FOR PERIPHERALS

RECEIVERS AND LOAD RELIEF TECHNIQUES

INTERFACE EXAMPLES ....... .

Programmed 1/0 Interface Example

Flag Logic

Interrupt Request

Output Buffer

Input Buffer

1/0 Control

Input/Output Timing for Programmed I/O Interfaces

PROGRAM INTERRUPT TRANSFERS

Interrupt Timing ...... .

Data Break Interface Ex,ample

Data Break Timing ..... .

THREE-CYCLE DATA BREAK ..

GENERAL CAUTIONS REGARDING INTERFACE DESIGN

TRANSMISSION LINE EFFECTS

EXTERNAL BUS ........ .

Positive 1/0 Bus Interfacing

The Nature of the Extemal Bus

External Bus Signals

External Bus Signals

BAC 00-11

AC 00-11

BMB 00--11

BIOP 1,2, and 4

BTS1,BTS3

vi

Page

3-20

3-21

3-21

3-21

3-21

3-22

3-22

3-23

3-23

3-23

3-23

3-24

3-24

3-24

3-24

3-25

3-25

3-25

3-25

3-25

3-25

3-28

3-28

3-30

3-30

3-32

3-32

3-32

3-33

3-33

3-33

3-33

3-33

3-33

3-35

3-37

3-38

3-39

.. 3-39

3-39

3-39

3-40

3-40

3-40

3-40

3-41

3-41

3-41

3.19.4.6

3.19.4.7

3.19.4.8

3.19.4.9

3.19.4.10

3.19.4.11

3.19.4.12

3.19.4.13

3.19.4.14

3.19.4.15

3.19.4.16

3.19.4.17

3.19.4.18

3.19.4.19

3.19.4.20

3.19.4.21

CHAPTER 4

4.1

4.2

4.2.1

4.2.2

4.2.3

4.2.4

4.2.5

4.2.6

4.3

4.3.1

4.3.2

4.3.2.1

4.3.2.2

4.3.2.3

4.3.2.4

4.3.2.5

4.3.2.6

4.3.2.7

4.3.2.8

4.3.2.9

4.4

4.4.1

4.4.2

4.4.3

4.4.4

4.4.5

4.4.6

4.5

4.5.1

4.5.2

CONTENTS (Cont)

B RUN ..

AC CLEAR

SKIP ...

B INITIALIZE 1

DATA 00-11

B BREAK

DATA OUT

DATA ADD 00-11

BRK RQST

ADD ACCEPTED

MBINCREMENT

CA INCREMENT INH

3 CYCLE ...... .

WC OVE RF LOW .. .

EXT DATA ADD 0-2

B INITIALIZE 2 ..

CENTRAL PROCESSOR UNIT

CENTRAL PROCESSOR UNIT, GENERAL DESCRIPTION

TIMING GENERATOR

Power On/Run Logic

Timing Register Logic

CPU Timing Logic

Memory Timing Logic

I/O Transfer Stall Logic

Memory Stall Logic

FRONT PANEL OPERATIONS

Limited Function Panel

Programmer's Console

Clock Timing Logic

Register Logic

Multiplexer Logic

Register/Multiplexer Gating Logic Timing

ADDRS/DISP Readout Circuit Logic

Function Button Logic

DISP Button Logic ...

THIS, HL T, BOOT Logic

Console Control Logic

INSTRUCTION DECODER

Instruction Register Logic

Major State Register Logic

DATA ENA/DATA CMP Logic

Address Update Logic

Major Register Load Signal Logic

AC Register Control Logic

MAJOR REGISTER GATING

Page Logic

Carry In Logic

vii

Page

3-41

3-41

3-41

3-41

3-41

3-42

3-42

3-42

3-42

3-42

3-42

3-42

3-42

3-42

3-43

3-43

4-1

4-3

4-4

4-5

4-7

4-7

4-8

4-11

4-11

4-14

4-16

4-22

4-22

4-26

4-27

4-30

4-32

4-36

4-39

4-40

4-41

4-45

4-46

4-49

4-50

4-51

.4-53

.. 4-54

4-57

.. 4-59

4.5.3

4.5.4

4.6

4.6.1

4.6.2

4.6.3

4.6.4

CHAPTER 5

5.1

5.1.1

5.1.2

5.2

5.2.1

5.2.2

5.2.3

5.3

5.3.1

5.3.2

5.3.2.1

5.3.2.2

5.4

5.4.1

5.4.2

5.4.3

5.4.4

5.4.5

5.4.6

5.4.6.1

5.4.6.2

5.4.6.3

5.4.6.4

5.4.7

5.4.7.1

5.4.7.2

5.4.7.3

. 5.4.7.4

5.4.7.5

5.5

5.6

5.6.1

5.6.2

CONTENTS (Cont)

Skip Logic

Link Logic

I/O TRANSFER LOGIC

Programmed I/O Transfer Logic

Processor lOT Logic

Program Interrupt Logic

Data Break Transfers

MEMORY OPTIONS

SECTION 1

MRS-A READ ONLY MEMORY (ROM)

MRS-A READ ONLY MEMOBY (ROM) DESCRIPTION

MRS-A Physical Description

M RS-A Specifications

FUNCTIONAL DESCRIPTION

Addressing ...... .

Timing and Control

Input and Output Signal Definition

PROGRAMMING ..... .

Programming Operation

Programming Procedure .....

Preparation of the Paper Tape

Blasting .......... .

DETAILED LOGIC DESCRIPTION '"

Addressing Block Diagram Description

Field and Size Selection

Chip Select Decoder

The 13th Bit '"

Timing and Control

Timing Generation

Control Flip-Flops

Sequence of Control Operations

Initial Conditions ..... .

Single Stepping . . . . . . . .

Memory Data and Memory Register

Memory Chips ....... .

Address and Chip Enable Inputs

Memory Output Register

Data Transfer Lines

Physical Layout

MRS-A SWITCH LIST ....

SECTION 2

RANDOM ACCESS MEMORY (RAM)

SEMICONDUCTOR RANDOM ACCESS MEMORY (RAM-MSS-A) DESCRIPTION

Physical Description

MSS-A Specifications

viii

Page

4-63

4-65

4-67

4-67

4-67

4-73

4-73

5-3

5-3

5-3

5-3

5-5

5-5

5-S

5-S

5-S

5-S

5-9

5-9

5-9

5-9

5-10

5-12

5-12

5-14

5-16

5-16

5-16

5-16

5-16

5-17

5-1S

5-19

5-19

5-19

5-19

5-19

5-21

5-21

5-23

5.7

5.7.1

5.7.2

5.7.3

5.7.4

5.7.5

5.S

5.9

5.10

5.10.1

5.10.2

5.10.3

5.10.4

5.11

5.11.1

5.11.2

5.11.2.1

5.11.2.2

5.11.3

5.11.4

5.12

5.13

5.13.1

5.13.2

5.13.3

5.13.4

5.13.5

5.13.6

5.13.7

5.13.S

5.13.9

5.13.10

5.13.11

5.13.12

5.14

5.14.1

5.15

5.15.1

5.15.2

5.15.3

5.15.4

5.15.5

5.15.6

5.15.7

5.15.S

5.15.9

5.16

CONTENTS (Cant)

FUNCTIONAL DESCRIPTION

Address Select Logic

Timing and Control

Memory Chip Array

Memory Data

Operation .....

INPUT AND OUTPUT SIGNALS

PROGRAMMING ........ .

DETAILED LOGIC DESCRIPTION

Address Selection Logic

Field Selection ....

Starting Address

Memory Size Selection

TIMING AND CONTROL LOGIC

MSS-A Timing Chain ...

Operation of a RAM Cycle

Read Cycle .....

Write Cycle . . . . .

Operation of a ROM-RAM Cycle

Memory Data and Memory Output Register

SWITCH DEFINITIONS .......... .

SECTION 3

MRSFB REPROGRAMMABLE READ ONLY MEMORY (PROM)

MRS-FB 1 K MEMORY

M RS-FB Specifications

M RS-FB Description .

Address Decoder ...

Starting Address Decoder

Bootstrap Operation ..

Memory Control and Timing Logic

Rear or ReadlWrite

1K PROM

13th Bit PROM

ROM Address Flag

ReadlWrite Memory (RAM)

Data Multiplexer ....

MRS-FB PROGRAMMING

PROM Erasing Procedure

DETAILED LOGIC DESCRIPTION

Address Decoder ......

Timing and Processor Control for SW Start of Memory

Field and Starting Address Select Logic

Memory Address Control Signal Generation

NTS STALL ............ .

ROM ADDR ............... .

1 K PROM Memory and Control Logic .. .

256 ReadlWrite Memory and Control Logic

ROM and RAM Data Multiplexer

MAl NTENANCE . . . . . . . . . .

ix

Page

5-23

5-23

5-24

5-24

5-25

5-25

5-25

5-26

5-26

5-27

5-27

5-2S

5-2S

5-29

5-29

5-30

5-30

5-33

5-33

5-37

5-37

5-41

5-42

5-42

5-42

5-44

5-44

5-44

5-44

5-44

5-44

5-45

5-45

5-4S

5-4S

551

5-51

5-51

5-51

5-54

5-55

5-55

5-55

5-55

5-57

5-57

5-59

5.17

5.18

5.19

5.19.1

5.19.2

5.19.3

5.19.4

5.19.5

5.19.6

5.19.7

5.19.8

5.19.9

5.19.10

5.19.11

5.19.12

5.19.13

5.19.14

5.19.15

5.19.16

5.19.17

5.19.18

5.19.19

5.19.20

5.19.21

5.19.22

5.19.23

5.19.24

5.19.25

5.19.26

5.19.27

5.19.28

5.19.29

5.19.30

5.19.31

5.19.32

5.19.33

5.19.34

5.19.35

5.20

5.20.1

5.20.2

5.20.3

5.20.4

5.20.5

5.20.6

CONTENTS (Cont)

SECTION 4

CORE MEMORY SYSTEMS

MEMORY SYSTEM, GENERAL DESCRIPTION

MEMORY SYSTEM, FUNCTIONAL DESCRIPTION

MM8-AA 8K CORE MEMORY SYSTEM

Memory Core

Hysteresis Loop

X/Y Select Lines

Read Operations

Write Operations

Magnetic Core In Two-Dimension Array

Assembly Of 12-Stacked Core Mats

Core Selection System ........ .

Organization Of X/Y Drivers And Current Source

X And Y Current Sources - General Description

Stack Charge Circuit ..

Power Fail Circuit

Core Selection Decoders

Address Decoding Scheme

Diode Selection Matrix ..

Operation Of Selection Switches

Operation Of The Core Selection Switches

Sense/Inhibit Function

Sense/Inhibit Line

ReadlWrite Operation

Inhibit Control Logic

Field Select Control LO!Jic

Sense Register Enable Logic

Sense Register Clear Timing

Strobe Control Logic

Strobe Setting Jumpers

Sense Amplifiers ...

Sense Register

Inhibit Driver Load Gates

Inhibit Drivers

Current Source

POWER NOT OK

Test Points ...

Circuit Variables

Core Memory Troubleshooting

MM8-AB 16K CORE MEMOHY SYSTEM

Assembly Of Twelve Core Mats

Address Decodi ng Scheme .....

Operation Of The Core Selection Switches

ReadlWrite Operation

Field Select Control Lo'gic

Inhibit Control Logic

x

Page

5-61

5-61

5-63

5-63

5-63

5-64

5-65

5-65

5-65

5-65

5-65

5-69

5-69

5-70

5-70

5-70

5-73

5-73

5-73

5-79

5-79

5-79

5-79

5-81

5-81

5-82

5-82

5-84

5-84

5-86

5-86

5-87

5-87

5-88

5-90

5-91

5-93

5-93

5-94

5-94

5-94

5-100

5-100

5-104

5-105

5.20.7

5.20.8

5.20.9

5.20.10

5.20.11

5.20.12

5.20.13

5.20.14

5.20.15

5.20.16

CHAPTER 6

6.1

6.1.1

6.1.2

6.1.3

6.1.4

6.2

6.2.1

6.3

6.3.1

6.3.2

6.3.3

6.3.4

6.3.5

6.3.6

6.4

6.5

6.5.1

6.5.2

6.5.3

6.5.4

6.5.5

6.5.5.1

6.5.5.2

6.5.6

6.5.7

6.5.8

6.6

6.7

6.8

6.8.1

6.8.2

6.8.3

CONTENTS (Cont)

Sense Register Enable Logic

Sense Register Clear Timing

Strobe Control Logic . .

Strobe Setting Jumpers

Inhibit Driver Load Gates

Sense Amplifier

Inhibit Drivers

Current Source

POWER OK

Test Points ..

PDP-8/A OPTION MODULES

SECTION 1

DKC8-AA I/O OPTION MODULE (M8316)

DKC8-AA I/O OPTION MODULE BLOCK DIAGRAM DESCRIPTION

Serial Line Unit (SLU) ..... .

General Purpose 12-Bit Parallel I/O

Real Time Crystal Clock

Front Panel Control

SERIAL LINE UNIT .... .

SLU Specifications .. .

SLU FUNCTIONAL DESCRIPTION

Methods of Data Transfer

Transmit Operation

Receive Operation

SLU Timing Generator

Parity Generation

Number of Bits Per Character

SLU PROG RAMM I NG . . . . . .

SLU DETAILED LOGIC DESCRIPTION

Device Select Logic .... .

SLU Operation Decoder ..... .

SLU Interrupt and Skip Logic

SLU Timing Generator and Baud Rate Select Logic

Universal Asynchronous ReceiverlTransmitter (UART)

UART Receive Operation

UART Transmit Operation

Level Converters

Reader Run Logic ...... .

Request to Send and Terminal Ready

REAL TIME CLOCK .......... .

REAL TIME CLOCK PROGRAMMING ..

REAL TIME CLOCK DETAILED LOGIC DESCRIPTION

Device Select and Operation Decoder Logic

Real Time Clock Frequency Dividers

Real Time Clock Interrupt and Skip Logic

xi

Page

5-105

5-105

5-106

5-106

5-107

5-108

5-108

5-109

5-109

5-109

6-3

6-4

6-4

6-4

6-4

6-4

6-4

6-5

6-6

6-6

6-7

6-7

6-8

6-9

6-9

6-9

6-10

6-10

6-11

6-12

6-14

6-14

6-17

6-18

6-18

6-21

6-21

6-21

6-21

6-21

6-22

6-23

6.9

6.10

6.11

6.11.1

6.11.2

6.11.3

6.11.3.1

6.11.3.2

6.11.4

6.11.5

6.11.6

6.12

6.12.1

6.12.2

6.12.3

6.12.4

6.13

6.14

6.14.1

6.14.2

6.14.3

6.14.4

6.14.5

6.15

6.16

6.16.1

6.16.2

6.17

6.17.1

6.17.2

6.17.3

6.17.4

6.17.5

6.17.6

6.17.7

6.17.8

6.17.9

6.18

6.18.1

6.18.2

6.18.3

6.19

6.19.1

6.19.2

CONTENTS (Cont)

GENERAL PURPOSE PARALLEL I/O BLOCK DIAGRAM DESCRIPTION

GENERAL PURPOSE PARALLEL I/O PROGRAMMING

DETAILED LOGIC DESCRIPTION .....

Device Select and Operations Decoder

Interrupt and Skip Logic ....

Receive and Transmit Operations

Transmit Operation

Receive Operation

Strobe ........ '.

Parallel I/O Output Reg!ister

Parallel I/O Input Buffer and Data Gates

SECTION 2

KM8A EXTENDED OPTION MODULE (M8317)

KM8-A EXTENDED OPTION BOARD (M8317)

Memory Extension ...

Timeshare Option

Power Fail/Auto Restart

Bootstrap Loader

MEMORY EXTENSION AND TIMESHARE DESCRIPTION

MEMORY EXTENSION BLOCK DIAGRAM DESCRIPTION

Control Logic ....... .

Instruction Field Register (I F) .

Data Field Register (DF) ...

Instruction Buffer Register (lB)

Save Field Register (SFI

TIMESHARE CONTROL BLOCK DIAGRAM DESCRIPTION

MEMORY EXTENSION AND TIMESHARE PROGRAMMING

Memory Extension ........... .

Timeshare ................ .

MEMORY EXTENSION AND TIMESHARE DETAILED LOGIC DESCRIPTION

Memory Extension/Timeshare Device Select .... .

Memory Extension and Timeshare Operation Decoder

Input Multiplexer ......... .

Instruction Field Register and Controls

Data Field Register and Controls . . .

Output Multiplexer ........ .

Timeshare User Buffer and Control Logic

Trap Detect Logic ...............,.

Interrupt Inhibit Logic ..... , ....... .

POWER FAIL/AUTO RESTJ\RT AND BOOTSTRAP LOADER

Power Fail! Auto Restart Block Diagram Description

Power Fail/Auto Restart Programming ......... .

Bootstrap Loader Block. Diagram Description ..... .

BOOTSTRAP ROM ORGANilZATION AND PROGRAMMING

ROM Organization ....... .

Auto-Restart/Bootstrap Sequence

xii

Page

623

624

624

624

6-27

627

627

629

629

.. 629

630

6-32

.. 6-33

633

633

633

633

633

633

635

635

6-35

635

6-35

635

636

638

6-38

6-38

639

641

6-41

6-46

646

646

651

6-51

6-51

651

653

6-54

6-54

6-55

6-55

6.19.3

6.19.4

6.19.5

6.20

6.21

6.21.1

6.21.2

6.21.3

6.22

6.22.1

6.22.2

6.22.3

6.22.4

6.22.5

6.22.6

6.22.7

6.22.S

CHAPTER 7

7.1

7.2

7.2.1

7.2.2

7.2.2.1

7.2.2.2

7.2.2.3

7.2.2.4

7.2.2.5

7.2.2.6

7.2.2.7

7.3

7.3.1

7.3.2

7.3.2.1

7.3.2.2

7.3.2.3

7.3.2.4

7.3.2.5

7.3.2.6

7.4

7.4.1

7.4.2

7.4.3

7.4.4

7.4.5

CONTENTS (Cont)

ROM Programming Examples

Bootstrap Example . . .

Obtaining Blank ROMs ...

ROM PROGRAM LISTING

POWER FAIL/AUTO RESTART AND BOOTSTRAP OPERATION AND TIMING

Power Fail Operation ...... .

Auto-Restart Operation and Timing ..................

Bootstrap Operation and Timing .. . . . . . . . . . . . . . . . . . . . .

POWER FAIL/AUTO-RESTART AND BOOTSTRAP OPERATION DETAILED

LOGIC DESCRIPTION ...................... .

Power Fail/Auto-Restart Device Select and Operation Decoder

Power Fail Interrupt and Skip Logic ... . ....

Bootstrap and Auto-Restart Timing Clock

Bootstrap Initialization Logic ..... .

Auto-Restart Initialization Logic .... .

Auto-Restart and Bootstrap Address Counters

ROM Memory Control and Multiplexers ...

Bootstrap and Auto-Restart Operation Control Logic

POWER SUPPLY

GENERAL ........................ .

PDP-S/A SEMICONDUCTOR BASIC POWER ASSEMBLY

Power Board ..... .

Regulator Board (GS016) ........ .

+5 Vdc Regulator Circuit ........ .

+5 Vdc Regulator Circuit, Battery Operation

Battery Empty Circuit .

Battery Charging Circuit

15 Vdc Circuit

POWER OK H Circuit

AC LOW L Circuit ..

SA400/600/S00 BASIC POWER ASSEMBLY

H9194 Connector Block Assembly

Regulator Board (GS01S)

+5 Vdc Regulator Circuit

-5 Vdc Regulator Circuit

+20 Vdc Regulator Circuit

15 Vdc Circu it

POWER OK H Circuit

AC LOW L Circuit ..

SA420/620/S20 BASIC POWER ASSEMBLY

General ................

Interlock and Triac Control Circuit

Line Level Transformer and Peak Detector

Thermistor/Thermostat and Emergency Shutdown

POWER OK H Circuit ............. .

xiii

Page

6-56

6-56

6-56

6-57

6-57

6-57

6-6S

6-70

6-70

6-71

6-71

6-73

6-73

6-73

6-75

6-75

6-75

7-1

7-2

7-2

7-4

7-5

7-6

7-S

7-S

7-9

7-9

7-11

7-12

7-12

7-16

7-16

7-16

7-16

7-1S

7-1S

7-19

7-20

7-20

7-22

7-22

7-22

7-26

CHAPTER 8

8.1

8.1.1

8.1.2

8.2

8.2.1

8.2.2

8:3

8.3.1

8.3.2

8.3.3

8.3.4

8.3.5

8.3.6

8.3.7

8.3.8

8.3.9

8.4

8.4.1

8.4.1.1

8.4.2

8.4.2.1

8.4.2.2

8.5

8.5.1

8.5.2

8.6

8.6.1

8.6.2

8.6.3

CONTENTS (Cant)

MAINTENANCE AND TROUBLESHOOTING

MAINTENANCE AND TROUBLESHOOTING REQUIREMENTS

Diagnostic Programs ...........

Equipment ................ .

PREVENTIVE MAINTENANCE INSPECTIONS

Scheduled MaintenancEl

The Importance of a Preventive Maintenance Schedule

PDP-8/A TROUBLESHOOTIING .

Operator Errors ..... .

Troubleshooting Procedures

Validation Tests

Cable Problems . . . . . . .

Log Entry ........ .

Removal and Replacement of Modules

Removal and Replacement of Regulator Board

Removal and Replacement of LEOs on the Limited Function Panel

Removal and Replacement of LEOs on the Programmer's Console

POWER SUPPLY ADJUSTMENTS

G8016 Power Supply Adjustment

+5 V Adjustment (G8016} .

G8018 Power Supply Adjustment

+5 V Power Supply Adjustment

+20 V Power Supply Adjustment

POWER FAIL/AUTO-RESTART LEVEL ADJUSTMENT (G80l6 AND G8018)

G8018 Power Fail/Auto-Restart Adjustment

G8016 Power Fail/Aut()-Restart Adjustment

LINE VOLTAGE AND FREOUENCY COMBINATIONS

8A400/600/800

8A420/620/820

PDP-8/A Semiconductor

CHAPTER 9 SPARE PARTS

APPENDIX A INSTRUCTION SUMMARY

APPENDIX B OMNIBUS SIGNAL LOCATOR

APPENDIX C MODULE ASSIGNMENT AND POWER REQUIREMENTS

APPENDIX D PROGRAM LOADING PROCEDURES

0.1 TURNING THE SYSTEM ON ..

0.2 READ-IN MODE (RIM) LOADER

0.3 BINARY (BIN) LOADER

0.4 LOADING BINARY TAPES

APPENDIX E ASCII CHARACTER CODES

xiv

Page

8-1

8-1

8-3

8-3

8-3

8-3

8-3

8-3

8-4

8-4

8-4

8-5

8-5

8-5

8-5

8-6

8-6

8-6

8-6

8-6

8-6

8-6

8-6

8-9

8-9

8-9

8-9

.. 8-11

. 8-11

0-1

0-2

0-3

0-4

CONTENTS (Cant)

APPENDIX F DEVICE CODES

APPENDIX G MEMORY CYCLE TIME SUMMARY

APPENDIX H ENGINEERING DRAWINGS

Figure No.

11

12

13

1-4

15

1-6

21

22

23

2-4

25

26

2-7

28

29

210

211

212

213

2-14

2-15

216

217

218

219

220

2-21

222

223

2-24

225

226

31

3-2

3-3

3-4

ILLUSTRATIONS

Title

PDP-8/A Miniprocessor .....

PDP-81 A System Block Diagram

PDP-8/A Limited Function Panel

PDP-81 A Programmer's Console

Status Information ....... .

State Information ...... .

8A420, 8A620, 8A820 Packaging

PDP-8/A Computer Packaging (Inner)

PDP8/A Computer Packaging (Outer)

Part of M8320 Module Showing R55 which is Removed for 8A Operation

PDP-8/A Semiconductor Chassis ............ .

PDP-8/A Semiconductor Computer Chassis Dimensions

PDP-8/A Chassis (H9300) (Transformer Cover Removed)

PDP-8/A Chassis (8A420, 8A620, 8A820)

8A420/620/820 Chassis Dimensions

8A600/8A620 Expansion ....... .

KK8A (M8315) CPU Module ..... .

MS8-A (M8311) ReadIWrite Random Access Memory

MR8-A (M8312) Read Only Memory (ROM)

MM8-AA Core Memory ...... .

MM8-AB Core Memory ......... .

DKC8-AA (M8316) I/O Option Board .. .

o Etch Revision of DKC8AA (M8316) I/O Option Board

KM8-A (M8317) Extended Option Board .....

Semiconductor Memory Regulator Board (GS016)

8A MASTER/SLAVE Switch

G8018 Core Memory Regulator Board

Limited Function Panel

KC8-AA Programmer's Console

PDP8/A Electrical Connections

Paper Tape Leader ....

L T33 Teletype Controls

PDP8/A Omnibus (H9194)

PDPS/ A Hex and Quad Modules

SA Chassis (H9300) ..... .

Modules Connected With H851 Type Connector

xv

Page

Page

1-6

1-7

1-8

1-11

1-16

1-16

2-4

2-5

2-6

2-7

2-9

2-10

2-11

2-12

2-13

2-14

2-15

2-17

2-19

2-22

2-23

2-25

226

2-28

2-31

2-32

2-33

2-34

235

2-37

242

2-42

3-2

33

3-4

3-6

Figure No.

3-5

3-6

3-7

3-8

3-9

3-10

3-11

3-12

3-13

3-14

3-15

3-16

3-17

3-18

3-19

3-20

3-21

3-22

3-23

3-24

3-25

3-26

3-27

3-28

3-29

3-30

3-31

3-32

3-33

4-1

4-2

4-3

4-4

4-5

4-6

4-7

4-8

4-9

4-10

4-11

4-12

4-13

4-14

4-15

4-16

4-17

4-18

4-19

4-20

ILLUSTRATIONS (Cont)

Omnibus Signal Locator .'...

Timing For One Memory Cyc:le

Title

Time State and Time Pulse Change Timing

TP3 Timing During lOT Transfer

Memory Timing

Memory Timing

Write Timing .

Basic I/O Timing

CAF Instruction Timing

Timing to Stop CPU Using Not Last XFER L

Transfer Timing ....."..

External Loading of Link Timing

CPU Restart Timing

Data Break Timing ....

Data Exchange Timing ..

End of Data Break Timing

CPU Major States Timing

FETCH Cycle Timing

Interrupt Timing

Start Timing

Stop Timing

Typical I/O Decoder

Sample Programmed I/O Interface

Timing for Sample Programmed I/O

Sample One Cycle Data Break Interface

Data Break Control Timing Diagram ..

Three Cycle Data Break Simplified Block Diagram

Parallel Connection of Peripherals ....... .

External Bus Signals and Relalted Omnibus Signals

CPU Block Diagram ..... .

Timing Generator Block Diagram

Power ON/RUN Logic .... .

Timing Register Logic .... .

Timing Register Normal Timing

CPU Timing Logic

CPU Timing Signals

Memory Timing Logic

Memory Timing Signals

I/O Transfer Stall Logic

I/O Timing (NOT LAST XFER L Asserted)

Memory Stall Logic ........... .

Timing, NTS STALL L Asserted ..... .

Limited Function Panel Circuit Board Schematic, 8A Computers

Limited Function Panel Circuit Board Schematic, PDP-8/ A Semiconductor Computer

Programmer's Console Block Diagram

Clock Timing Logic

Timing, Clock Timing Logic

Register Logic

Multi plexer Logic .....

xvi

Page

3-7

3-21

3-21

3-22

3-22

3-22

3-22

3-23

3-23

3-23

3-23

3-23

3-24

3-24

3-24

3-24

3-24

3-24

3-25

3-25

3-25

3-30

3-31

3-35

3-36

3-37

3-38

3-40

3-41

4-2

4-3

4-4

4-6

4-7

4-8

4-9

4-9

4-10

4-10

.. 4-12

4-14

4-15

4-17

4-18

.4-20

4-23

4-24

.. 4-25

4-27

Figure No.

4-21

4-22

4-23

4-24

4-25

4-26

4-27

4-28

4-29

4-30

4-31

4-32

4-33

4-34

4-35

4-36

4-37

4-38

4-39

4-40

4-41

4-42

4-43

4-44

4-45

4-46

4-47

4-48

4-49

4-50

4-51

4-52

4-53

4-54

4-55

4-56

4-57

5-1

5-2

5-3

5-4

5-5

5-6

5-7

5-8

5-9

5-10

5-11

ILLUSTRATIONS (Cont)

Title

MPX/Enable Signal Relationship .

Register/Multiplexer Gating Logic

Register/Multiplexer Gating Signal Timing

ADD RS/D ISP Readout Circuits .....

OCTAL Designations - Resultant Displays

Function Button Logic .

o ISP Button Logic ...... . . . .

THIS, HLT, BOOT Logic ..... .

Console Control Logic - STATE, MD

Console Control Logic - MA, DATA, SR ENAB LE

ROM A Logic

ROM B Logic

ROM C Logic

ROM 0 Logic

ROM E Logic

ROM F Logic

ROM H Logic

ROM J Logic

Instruction Registers Logic

Major State Registers Logic

Data ENA/Data CMP Logic

Address Update Logic

Major Register Load Signal Logic

AC Register Control Logic ...

Block Diagram, Major Register and Gating (BITO)

Page Logic

Carry In Logic

Skip Logic

Link Logic

Major Register Gating (BITOO)' Prpgrammed I/O Transfer

Programmed I/O Transfer Logic

Processor lOT Logic .............. .

Program Interrupt Logic ............ .

Major Register Gating (BITO), Data Break Transfer

Data Break Transfer Control Signal Logic

AUTO-START Timing ........ .

AUTO-START Timing, CPU Logic .. .

MR8-A ROM Memory Module (M8312)

ROM/RAM Configuration

ROM Block Diagram ......... .

ROM Timing Diagram ........ .

Detailed Block Diagram of Address Select Logic

Field and Size Selection ..... .

Chip Select Decoding ...... .

13th Bit Mapping into 1 K X 1 Array

13th Bit Mapping into 4K X 1 Array

Timing and Control Logic

ROM-RAM Selection Timing ....

xvii

Page

4-28

4-29

4-30

4-31

4-32

4-33

4-37

4-39

4-40

4-41

4-42

4-42

4-43

4-43

4-44

4-44

4-44

4-44

4-45

4-47

4-49

4-50

4-51

4-53

.4-55

4-59

4-62

4-64

.4-66

4-68

4-69

4-71

4-74

4-75

.4-77

4-78

4-79

5-4

5-4

5-6

5-7

5-10

5-11

5-13

5-13

5-14

5-15

5-17

Figure No.

5-12

5-13

5-14

5-15

5-16

5-17

5-18

5-19

5-20

5-21

5-22

5-23

5-24

5-25

5-26

5-27

5-28

5-29

5-30

5-31

5-32

5-33

5-34

5-35

5-36

5-37

5-38

5-39

5-40

5-41

5-42

5-43

5-44

5-45

5-46

5-47

5-48

5-49

5-50

5-51

5-52

5-53

5-54

5-55

5-56

5-57

5-58

5-59

IL.LUSTRATIONS (Cont)

Title

Single Step Operation ...... .

Arrangement of 1 K Memory .. .

ROM 4K Memory - Physical Layout of Module

RAM MS8-A Module M8311

MS8-A Block Diagram

Read Cycle Flow Chart

Write Cycle Flow Chart

Address Selection Logic

ROM (lC8223) Truth Table

Memory Timing Chain

Read Cycle Timing Diagram

TP4 Logic

Source Time Logic

Operations at TPl

Stall + 400 ns Logic

Write Cycle Timing Diagram

Write Cycle Logic .....

ROM-RAM Initial Delay Logic

ROM-RAM Initial Delay Timijng Diagram

Detailed Timing of Initial Delay in ROM-RAM Cycle

Memory Array and Output Register

Simplified MR8-FB Block Diagram

M R8-FB Block Diagram

Bootstrap Operation Timing

Read Timing ....... .

13th Bit ReadtWrite Timing

PROM Block Diagram

PROM Addressing Scheme .

Address Decoder Logic . . .

ML8-F Timing and SW Operation Control Logic

Field and Starting Address Select Logic

Memory Address Control Signal Generator

PROM and Control Logic ....... .

ROM and RAM Data MultiplE!xer and Latch

RAM Memory (256 Word) ........ .

Core Memory System Functional Block Diagram

Core Memory Timing Diagram ....

MM8-AA Core Memory Block Diagram

Magnetic Core ......... .

Magnetic Core Hysteresis Loop

Three Wire Memory Configuration

Core Stack Layout ....... .

8K + 12 Bit Stack and Sense Lines

Current Path For Write Current

Current Path For Read Currel1t

Decoding of X and Y Driver Current Sources Block Diagram

Stack Charge Circuit

Power Fail Circuitry ................... .

xviii

Page

5-17

5-18

5-18

5-22

5-24

5-26

5-27

5-28

5-29

5-30

5-31

5-32

5-32

5-33

5-33

5-34

5-34

5-35

5-36

5-37

5-38

5-41

5-43

5-45

5-48

5-49

5-49

5-50

5-52

5-53

5-54

5-55

5-56

5-57

5-58

5-62

5-62

5-63

5-64

5-64

5-66

5-67

5-68

5-69

5-70

5-71

5-72

5-72

Figure No.

5-60

5-61

5-62

5-63

5-64

5-65

5-66

5-67

5-68

5-69

5-70

5-71

5-72

5-73

5-74

5-75

5-76

5-77

5-78

5-79

5-80

5-81

5-82

5-83

5-84

5-85

5-86

5-87

5-88

5-89

5-90

5-91

5-92

5-93

6-1

6-2

6-3

6-4

6-5

6-6

6-7

6-8

6-9

6-10

6-11

6-12

6-13

6-14

ILLUSTRATIONS (Cont)

Title

Decoding Relationships ..... . ........ .

Organization of Planar Stack Diode Matrix for X Select Lines

Operation Of Selection Switches To Select Line XO

Detailed Operation Of Selection Switches

Inhibit Operation For Bit 0

Inhibit Control Logic ......... .

Field Select Control Logic ....... .

Memory Sense Register Enable Logic for Bit 0

Clear Time Control Logic

Strobe and Clear Timing

Strobe Control Logic

Strobe Adjustment ...

Sense Amplifiers

Inhibit Drivers Load Gates

Inhibit Drivers Bit 0

Current Source ..... .

POWER NOT OK Circuit

Margining Test Fixture Connections

Test Point Signals ........ .

MM8-AB 16K Core Memory

MM8-AB 16K Core Memory Stack Layout

16K X 12 Stack and Sense Lines .....

16K Core Memory Module Wiring Assembly

Decoding of X and Y Driver Current Sources Block Diagram

Decoding Relationships

Inhibit Operation For Bit 0

Field Selection Logic ..

Clear Time Control Logic

Strobe and Clear Timing

Strobe Control Logic . .

Inhibit Driver Load Gates

Inhibit Drivers for Bit 0

Current Source .....

POWER NOT OK Circuit

DKC8-AA I/O Option Module Block Diagram

Serial Line Unit Block Diagram

Transmitter Block Diagram (UART)

UART Receiver Block Diagram

Timing Generator Block Diagram

SLU and Real Time Clock Device Select Logic

SLU Operation Decoder .......... .

SLU Interrupt and Skip Logic ....... .

SLU Timing Generator and Baud Rate Select Logic

Format of I nput/Output Character

Receiver Timing Diagram ............ .

Transmitter Timing ............... .

EIA and 20 mA to TTL Converters and Reader Run Logic

TTL to EIA and 20 mA Converters .......... .

xix

Page

5-73

5-78

5-78

5-80

5-81

5-82

5-82

5-83

5-83

5-85

5-85

5-86

5-87

5-88

5-88

5-89

5-91

5-92

5-92

5-95

5-96

5-97

5-98

5-99

5-100

5-103

5-104

5-105

5-106

5-107

5-107

5-108

5-110

5-111

6-3

6-6

6-7

6-8

6-8

6-10

6-11

6-12

6-13

6-15

6-17

6-18

6-19

6-20

Figure No.

6-15

6-16

6-17

6-18

6-19

6-20

6-21

6-22

6-23

6-24

6-25

626

6-27

6-28

6-29

6-30

6-31

6-32

6-33

6-34

6-35

6-36

6-37

6-38

6-39

6-40

6-41

6-42

6-43

6-44

6-45

6-46

6-47

6-48

6-49

6-50

7-1

7-2

7-3

7-4

7-5

7-6

7-7

7-8

7-9

7-10

7-11

7-12

7-13

IL.LUSTRATIONS (Cant)

Title

Real Time Crystal Clock Block Diagram ........ .

Real Time Clock lOT Decoder and Interrupt and Skip Logic

Real Time Clock Frequency Dividers ..... .

General Purpose Parallel 1/0 Block Diagram .... .

Parallel 1/0 Device Select and Operation Decoder

General Purpose Parallel 1/0 Interrupt and Skip Logic

Parallel 1/0 Strobe Logic ... . . . . .

Parallel 1/0 Output Register ..... .

Parallel 1/0 Input Buffer and Data Gates

KM8-A Block Diagram ........ .

Memory Extension and Timeshare Block Diagram

Memory Extension and Timeshare Device Select Logic

Memory Extension/Time Share Operation Decoder

Input Multiplexer ......... .

I F Register and Control Logic

IF and DF Field Address Enable Logic

Data Field Register and Control Logic

Output Multiplexer ........ .

Time Share User Buffer Register and Control

Trap Detect Logic ............ .

Interrupt Inhibit Logic .......... .

Power Fail and Auto Restart Block Diagram

Bootstrap Loader Block Diagram

16 Bit Word ROM Format

Auto Restart Example

Bootstrap Example . . . . . . .

Auto Restart and Bootstrap Timing

Bootstrap Timing ........ .

Power Fail Auto Restart Device Select and Operation Decoder

Bootstrap and Auto Start Clock

Bootstrap and Auto Start Clock

CLK 1 and CLK2 Timing ....

Auto Restart Initialization Logic

Auto Restart and Bootstrap FlOM Address Counters

ROM Memory Control and MUX ........ .

Bootstrap and Auto Restart Operation Control Logic

Interconnections, PDP-8/A Semiconductor Basic Power Assembly

Power Board Circuits ..... .

G8016 Regulator Block Diagram

+5 Vdc Regulator Circuit

Regulator Board Edge Connector

+5 Vdc Regulator Circuit, Battery Operation

Battery Empty Circuit

Battery Charging Circuit

15 Vdc Power Supply

POWE R OK L Circuit

AC LOW L Circuit

Voltage Monitor Waveforms

Battery Hold-up Time, Minimum Line Voltage vs % of Full-Rated Load

xx

Page

6-20

6-22

6-22

6-23

6-27

6-28

6-29

6-30

6-31

6-32

6-34

6-39

6-40

6-42

6-43

6-45

6-47

6-48

6-49

6-50

6-52

6-53

6-54

6-55

6-56

6-57

6-69

6-70

6-71

6-72

6-74

6-75

6-76

6-77

6-78

6-79

7-2

7-3

7-4

7-5

7-6

7-7

7-8

7-9

. 7-10

7-10

7-11

7-12

7-13

Figure No.

7-14

7-15

7-16

7-17

7-18

7-19

7-20

7-21

7-22

7-23

7-24

7-25

7-26

7-27

8-1

8-2

8-3

8-4

B-1

Table No.

1-1

1-2

1-3

1-4

2-1

2-2

2-3

2-4

2-5

2-6

2-7

2-8

2-9

2-10

2-11

2-12

2-13

2-14

2-15

2-16

3-1

3-2

ILLUSTRATIONS (Cont)

Title

Interconnections, 8A400/600/800 Basic Power Assembly

Connector Block Assembly Circuits

+5 Vdc Regulator Circuit

- 5 Vdc Regulator Circuit

+20 Vdc Regulator Circuit

15 Vdc Circuit

POWE R OK H Circuit

AC LOW L Circuit

Timing, AC LOW L Circuit (60 Hz Operation)

Interconnections, 8A420/620/820 Basic Power Assembly

Interlock and Triac Control Circuit

Line Level Transformer/Peak Detector ..... .

Thermistor/Thermostat and Emergency Shutdown

POWER OK Circuit ....... .

G8016 Regulator Board Adjustments

G8018 Regulator Board Adjustments

H9194 Connector Block Assembly .

50 Hz and 60 Hz Connections on 10 Slot Machines

Omnibus Signal Locator

TABLES

Title

PDP-8/ A Functional Characteristics . . . . . . . .

PDP-8/A Computer Assemblies ....... .

PDP-8/A Limited Function Panel Controls and Indicators

PDP-8/A Programmer's Console Controls and Indicators

Summary of Installation Functions ......... .

PDP-8/A Computers, Dedicated Omnibus Slots

KK8-A (M8315) Central Processor Unit Switch Settings

MS8-A ReadIWrite Memory Switch Settings ..

MR8-A Read Only Memory Switch Settings

MM8-AA 8K Core Memory Jumper Installation

MM8-AB 16K Core Memory Jumper Installation

DKC8-AA I/O Option Board Switch Settings for C Etch Module

DKC8-AA Option Board Switch Settings for 0 Etch Module

Auto-Restart Select Switch Settings ........... .

Bootstrap Select Switch Settings (for ROMs Labeled 87 A2 and 88A2)

Bootstrap Select Switch Settings (for ROMs Labeled 158A2 and 159A2)

Bootstrap/Auto-Restart Switch Settings ................ .

Bootstrap Switch Settings for ROMs (E82 and E87) Labeled 87A2 and 88A2

Bootstrap Switch Settings for ROMs (E82 and E87) Labeled 158A2 and 159A2

Basic PDP-8f A Troubleshooting ...... .

Slot Assignments for Modules on the Omnibus

Load Resistor and Drivers Summary .....

xxi

Page

7-14

7-15

7-16

7-17

7-17

7-18

7-18

7-19

7-20

7-21

7-23

7-24

7-25

7-26

8-7

8-8

8-10

8-11

8-3

Page

1-3

1-5

1- 'J1

1-12

2-1

2-8

2-16

2-18

2-20

2-21

2-21

2-26

2-27

2-29

2-29

2-29

2-30

2-52

2-53

2-55

3-5

3-26

Table No.

3-3

3-4

3-5

4-1

4-2

4-3

4-4

4-5

4-6

4-7

4-8

4-9

4-10

4-11

4-12

4-13

4-14

4-15

4-16

5-1

5-2

5-3

5-4

5-5

5-6

5-7

5-8

5-9

5-10

5-11

5-12

5-13

5-14

5-15

5-16

5-17

5-18

5-19

5-20

5-21

6-1

6-2

6-3

6-4

6-5

6-6

6-7

7-1

TABLES (Cont)

Omnibus Signal Drive Currents

lOTs For Sample Interface

Transfer Control Signals

Time State Stall Results

Primary Power Control .

Clock Timing Control Signals

Register Logic Bus Line Data

DEC7447 A Input/Output Signals

Function Button Control Signals

Display Control Signals ...;

ROM H Input/Output Signals

DATA ENA/DATA CMP Gating

PC, AC, MQ ClK Signal loading

ROM D Input/Output Signals

ROM C Input/Output Signals

ROM B Input/Output Signals

ROM E Input/Output Signals

ROM J Input/Output Signals

ROM A Input/Output Signals

M R8-A Specifications

MR8-A Signal Definitions

Title

Switch Setting to Select Memory Field

MAO and MA 1 States for Memory Field Sizes

Switch Settings for States MAO and MA 1

Address Decoding ............. .

States of MA3 and MA2 to Select and Address Range

MS8-A Specifications .......... .

MS8-A Signal Descriptions ........ .

MS8-A ReadIWrite Memory Switch Settings

MR8-FB Signals ............. .

Core Selection Decoding Scheme "X" READ

Core Selection Y READ

Address Block Selection

Strobe Select Jumpers

V REF Jumpers

Voltage Test Points

Memory Data Errors Possible Causes

Core Selection Decoding Scheme "V" READ

Core Selection, V Read ......... .

Address Block Selection ......... .

COL and C1 l levels for Data Bus Transfers

D Etch SLU Baud Rate Select Chart

UART Signal Functions .....

J4 Input Signal Pin

J5 Output Signal Pin Assignments

ROM No.1 and ROM No.2 Listings (for ROMs Labeled 87 A2 and 88A2)

ROM No.1 and ROM No.2 Listings (for ROMs labeled 158A2 and 159A2)

PDP-8/A Family, Primary Power Assemblies ................. .

xxii

Page

3-29

3-32

3-34

4-16

4-19

4-24

4-26

4-32

4-34

4-38

.4-48

.4-50

4-52

4-58

4-60

4-61

4-70

4-72

4-76

5-5

5-6

5-11

5-12

5-12

5-13

5-14

5-23

5-25

5-39

5-46

5-74

5-80

5-82

5-84

5-90

5-92

5-93

5-101

5-103

5-104

6-11

6-13

6-16

6-25

6-26

6-58

6-63

7-1

Table No.

8-1

8-2

8-3

9-1

9-2

0-1

F-l

TABLES (Cont)

Title

Maintenance Equipment ..... . ..... .

Preventive Maintenance (3 Months or 500 Hours)

PDP-8/A Line Sets, Fuses, and Transformer Assemblies

PDP-SI A Semiconductor Recommended Spare Parts

8A Recommended Spare Parts

RIM Loader Programs

Device Codes ........ .

xxiii

Page

8-3

8-4

8-9

9-1

9-2

0-2

F-l

CHAPTER 1

INTRODUCTION AND DESCRIPTION

This manual provides the user with the necessary information to operate. interface to. maintain. and troubleshoot the

PDP-B/A Miniprocessor manufactured by Digital Equipment Corporation. Maynard. Massachusetts.

The PDP-B/A is the newest model of the PDP-B family consisting of the PDP-B/E. PDP-B/F. PDP-B/M and PDP-B/A. The

following illustrates how the PDP-B/A relates to its family members.

KIT-B/A

Modules

PDP-B/A

Small to Medium

Configu rations

PDP-B/M

Medium to Large

Configu rations

PDP-B/E

Large

Configurations

KIT-8/A is a module set version of the PDP-B/A configured to solve application problems that do not require a com-

plete computer package with power. front panel. chassis. and cooling. Kits consist of processor, memory, option

boards, and mounting hardware including:

Central Processor Unit. Hex Module (MB315)

ReadlWrite Random Access Memory (RAM). Quad Module (MB311)

Read Only Memory (ROM). Quad Module (MB312)

Reprogrammable Read Only Memory (PROM). Quad Module (MB349)

DKC8-AA 1/0 Option Board with Serial 1/0, Parallel 1/0, Real-Time Crystal Clock, and Programmer's Panel Control.

Hex Module (M8316)

KMB-AA Extended Option Board with Memory Extension. Timeshare Control. Power FaiI/Auto-Restart. and Bootstrap

Loader, Hex Module (M8317)

M M8-AA(8K) and M M8-AB( 16K) Core Memory Modules

PDP-8/A - There are two basic types of computers in the PDP-B/A family. The first type is the PDP-B/A, which uses

semiconductor memories (MSB and MRB). The second type is represented by a series of computers. each of which uses

BK or 16K core memory (MMB); this series consists of the BA400. BA420. BA600. BA620. BABOO. and BAB20

computers. When a reference applies to both types of computers. the designation "PDP-B/A" is used. "PDP-B/A Semi-

conductor" refers to the semiconductor-memory computer. while "BA400." for example. refers to a specific core-memo-

ry machine and "BA" refers to the core-memory machines in general.

1-1

PDP-Sf A Semiconductor (Semiconductor ME.mory); designed to provide the security and data integrity of hard wired.

solid state logic and relay controllers. and in addition. provide the flexibility. power. and low cost of a computer. Space is

available to install 10 modules.

Semiconductor memory:

RAM 1 K. 2K. 4K (M8311)

ROM 1K. 2K. 4K (M8312)

PROM 1 K with 256 word RAM (M8349l

Battery backup:

On Quad Modules

System 1 to 7 minutes with provision for additional external batteries

SA (Core Memory); provides the lowest cost c:omputers in the 8K to 32K memory range for small computer systems

and mainframes. The PDP-8/A Central Processor Unit and two new core memories are used. Space is available for 12 or

20 modules.

Core memory:

8K (M M8-AA) and 16K (M M8-AS) Hex Modules (two slot spaces are reqUlired for each module).

Most of the options available for other members of the PDP-8 family are compatible with the PDP-8/A (see Paragraph

2.4 for a list of those that are not compatible). However. the DKC8-AA 1/0 Option module. the KM8-AA Extended Option

module. and several memory modules have beEm designed exclusively for the PDP-8/A.

Companion Documents include:

1. Introduction to Programming - 1973

2. OSl8 Handbook

3. PDP-BIA Miniprocessor Handbook - 1975-1976

4. PDP-BIA Operators Handbook(DEC-8A-HOPHS-A-D)

5. PDP-BIA Engineering Drawings

6. PDP-8IE Maintenance Manual Volume II (OEC-8E-HMM2A-D-D) and III (DEC-8E-HMM3A-C-D).

All of these documents are available from Communications Services. Digital Equipment Corporation. Maynard. Mas-

sachusetts. 01754.

Table 1-1 lists the functional characteristics of the PDP-81 A.

1-2

Type

Word Length

Cycle Time

Memory Types

Memory Expansion

Hardware Registers

Auto Index

Addressing Capability

Instruction Set

Instruction Execution Time

Input/Output Capability

Auto Start Feature

*Cycle times reflect 1.5 J.lS memory.

Table 1-1

PDP-8/ A Functional Characteristics

Single address, fixed word length, parallel transfer programmed data processor.

12 bits.

1.5 ps minimum (See memory speeds).

Memory Type Cycle Time (ps)

Fetch Major State All Other States

ROM Only

ROM/RAM (ROM Cycle)

ROM/RAM (RAM Cycle)

RAM Only

Core Memory

RAM

ROM

PROM

Core

Up to 32K.

1 K, 2K, 4K

1 K, 2K, 4K

1K

8K,16K

5(AC, MQ, M B, PC, CPMA).

8 Auto Index registers per 4K memory field.

1.5

1.6

2.7

2.4

1.5

1.5

1.6

3.1

2.8

1.5

One instruction may address 256 locations directly or 4096 locations indirectly.

6 memory reference instructions, 20 microprogrammable operate microinstructions,

and 8 input/output transfer instructions for the CPU and each of up to 60 I/O

devices.

Operate microinstruction

Directly addressed M R I

Indirectly addressed MRI

1.5 ps*

3.0 ps*

4.5 ps*

Programmed data transfer, program interrupt system transfer, and 12 channels of

internal and/or external direct memory access (data break).

The CPU contains an auto-start which can start the CPU at one of six switch select-

able addresses upon application of power.

1-3

Options

Size (W X H X D)

Weight

Operating Environment

Power Requirement

1.1 SYSTEM DESCRIPTION

Table 1-1 (Cont)

PDP-8! A Functional Characteristics

Two new option boards which may be used separately or together.

1. Front Panel Control

Serial Line Unit

Parallel I/O

Real Time Clock

2. Power Fail/Auto Restart

Memory Extension

Timeshare Control

Bootstrap Loader

19 X 10.5 X 10.5 in. (48 X 27 X 27 cm) - PDP-8/A Semiconductor, 8A400,

8A600,8A800.

19 X 10.44 X 23 in. (48 X 26.52 X 58.42 cm) - 8A420, 8A620, 8A820.

55 Ib (25 kg) - PDP-8/A Semiconductor. 8,01400. SA600. SASOO.

117 Ib (5:3 kg) - 8A420. SA620. SAS20.

Ambient temperature

Relative humidity

41 to 122 F (5 to 50 C)

10010 to 95% maximum, Wet bulb 90 F (32 C)

Approximately 150 W at 115 Vac, 50 or 60 Hz or 230 Vac, 50 or 60 Hz (voltage

and frequEmcy specified at time of order).

The PDP-S/A is a general purpose miniprocessor. Its processor structure is single-address, fixed word length. parallel

transfer, using 12-bit. two's complement arithmetic. The cycle time of the processor is 1.5 J,lS. Standard features include

one level of indirect addressing and facilities for instruction skipping. program interrupts as a function of inputloutput

device conditions. and auto-restart features.

Five 12-bit registers are used to control computer operations, address memory, perform arithmetic or logical oper-

ations, and store data. An optional Programmer's Console provides switches and indicators that permit convenient

monitoring and modification of machine operation.

The flexible, high capacity inputloutput capabilities of the PDP-S/A allow it to operate a great variety of peripheral

devices. More than 60 inputloutput device options including high-speed paper-tape equipment. card readers, line

printers, disk and magnetic tape bulk storage devices, and a wide range of data acquisition, transmission, and display

peripherals are available from DIGITAL for the PDP-S/A.

Each PDP-S/A system is completely self-contained. A single source of 115 or 230 Vac power is required: internal power

supplies produce all the necessary operating voltages for the system. The basic PDP-S/A computer consists of a rack-

mountable chassis with a power supply and an Omnibus (backplane) into which Clre inserted the central processor. the

memory system. and the optional Programmer's Console and console terminal control. In the PDP-S/A, a bus .is defined

as a group of signal lines carrying related information. such as the 12 bits of an instruction or data word. The Omnibus

may be considered a wide bus containing several buses along with many other signal lines. Each PDP-SI A Omnibus has a

slot for the central processor unit. two slots reserved for the two option boards, plus several identical nondedicated

module slots. Each slot will accept a 144-pin quad or hex-sized module. (Some slots will accept a 1 SO-pin hex module.)

The Omnibus provides two-way signal paths between corresponding pins of the modules that are plugged into it.

1-4

A PDP-8/A computer pictured in Figure 1-1 shows both the Limited Function Panel (the panel on the bottom with three

switches and three indicators) and the Programmer's Console. The Programmer's Console can be located remotely from

the chassis; in such a case, or when the system does not include a console, a blank panel is attached.

PDP-8/A computers have three different mechanical assemblies that can be characterized by the number of available

Omnibus slots; that is, the PDP-8/A semiconductor computer assembly has a 10-slot Omnibus, while the 8A computer

assemblies have either a 12-slot or a 20-slot Omnibus. Table 1-2 relates the various PDP-81 A computers to some of the

basic system components. Note that the 8A400 can be considered the basic 8A computer, having a core memory, an 8A

CPU, and a 12-slot Omnibus. Thus, the 8A420 differs only in that it has a 20-slot Omnibus: the 8A600 differs in that it

has a PDP-8/E CPU; the 8A620 differs in that it has a PDP-8/E CPU and a 20-slot Omnibus: the 8A8DO differs in that it

has an FPP-8/A (not indicated in Table 1-2); and, the 8A820 differs in that it has an FPP-8/A and a 20-slot Omnibus.

Also, note that only 8A computers that use a PDP-8/E CPU can be expanded.

Table '-2

PDP8f A Computer Assembl ies

Computer CPU Memory* Basic Power Assembly Omnibus Expandable

PDP-8fA KK8-A Semiconductor H763 H9192 (1 O-Slot) No

8A400 KK8-A Core H9300 H9194 (12-Slot) No

8A420 KK8-A Core BAS-C H9195 (20-Slot) No

SA 600 KKS-E Core H9300 H9194 (12-Slot) Yes. As many as 20 slots

can be added.

SA620 KKS-E Core BAS-C H9195 (20-Slot) Yes. As many as 20 slots

can be added.

SASOO KKS-A Core H9300 H9194 (12-Slot) No

8A820 KKS-A Core BA8-C H9195 (20-Slot) No

* A KMS-A (or KMS-E) Extended Memory Option module must be included in all the SA computers, since their basic memory capacity

is SK or 16K; the KMS is optional with the PDP-S! A Semiconductor computer, since the basic memory can be less than, greater than,

or equal to 4K.

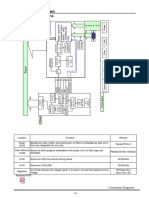

Figure 1-2 represents, pictorially, the PDP-8/A Omnibus and the relationship of the fundamental system components

(i.e., CPU, memory, power supply, option, and peripheral interfaces). These components are described briefly in the

following paragraphs.

1-5

....

-

Figure 1-1 PDP-8/ A Miniprocessor

1-6

7288-5

I

'-I

KKB-E

TELETYPE

OR

MODEM

CENTRAL PROCESSOR UNIT (M8300,

M831O), TIMING GENERATOR (M8330),

115VAC/230 VAC BUS LOADS (MB320)

I OR

POWER SUPPLY

I I

POWER POWER FAIL

KKB-A CENTRAL

PROCESSOR UNIT

(M83151

I f

CONTROL DATA

I

TIMING

PROGRAMMERS

CONSOLE

(KC8-AA)

DKC8-AA I/O OPTION BOARD

(M831S1

(1) SERIAL LINE UNIT.

(2) REAL TIME CRYSTAL CLOCK.

(3) GENERAL PURPOSE PARALLEL I/O

(4) PROGRAMMERS FRONT PANEL

CONTROL.

CONTROL DATA TIMING

CUSTOMER

OPTION

KMB-E MEMORY

EXTENSION AND TIME

SHARE

(M837)

OR

KM8-A EXTENDED OPTION BOARD

(M8317)

( 1) MEMORY EXTENSION AND TIME

SHARE CONTROL.

(2) POWER FAIL AND AUTO

RESTART.

(3) BOOTSTRAP LOADER

PERIPHERAL

CONTROLLER

OR

INTERFACE

( SUPPLIED

BY CUSTOMER

OR DEC)

Iff

CONTROL DATA TIMING STATUS CONTROL DATA

<

* * *

* * * *

+

*

*

OMNIBUS

I f I f I f f I f

~ - - ~ ~ - - - - ~ ~ - - ~ - - - - ~ ~ - - ~ - - - - ~ f - ~ I - ~ f - I - - _ :>

TIMING DATA CONTROL

~ ~

MS8-A RANDOM ACCESS

MEMORY (RAM)

(M8311 I

lK ,2K OR 4K

CONTROL TIMING DATA CONTROL TIMING DATA

~ ~ I

J 1

MR8-A READ ONLY MEMORY MR8-FBIK PROGRAMMABLE

(ROM) READ ONLY MEMORY WITH

256 WORD RAM

(M83121

(PROM)

lK ,2K OR 4K (M8349)

Figure 1-2 PDP-8/A System Block Diagram

CONTROL TIMING DATA

MM-AA CORE MEMORY (8K)

H219A AND G649

MM8-AB CORE MEMORY !16K)

H219B AND G650

08-1107

1.1.1 Central Processor Unit (CPU)

The KK8-A is contained on one hex module and has all the circuitry needed to manipulate data and generate control

signals; this circuitry includes the major registers and gating. the instruction decoder. the timing generator. and the auto-

start logic. The KK8-E is comprised of 4 hex modules. Two of these. M8300 and M831 O. constitute the CPU; another is

the Timing Generator (M8330). and the last is the Bus Loads (M8320).

1.1.2 KCS-AA Programmer's Console

The DKC8-AA 1/0 Option board contains the circuitry required to connect the PDP-8/A Programmer's Console to the

Omnibus. This console consists of an array of cCtntrols and indicators that facilitate c:omputer operation and maintenance.

Key pad switches provide convenient control of the system by allowing the operatOll' to start and stop program execution.

examine and modify the contents of memory. select various modes of operation. and load and execute short machine

language programs.

1.1.3 Limited Function Panel

The Limited Function Panel (Figure 1-3). which is often used without the Programmer's Console in dedicated appli-

cations. provides the necessary controls to apply power to the computer and start a program. A PANEL LOCK switch.

which is significant only when a Programmer's Console is present, allows the operator to disable most of the console

switches. This feature protects an operating program from being disturbed by accidental closure of a switch.

71185

Figure 1-3 PDP-8/A Limited Function Panel

1.1.4 Memory

The PDP-B/A memory can be configured from ROM. RAM. PROM. or core memory to meet the user's particular re-

quirements. Memory sizes below 4K. (such as 1 K RAM. 1 K ROM. and 1 K PROM) are allowed. and the memory sys-

tem can be expanded to 32K provided there! is adequate current available from the power supply. Each of the

various memory options available is discussed in the following paragraphs.

1.1.5 MMS-A Core Memory

The MMB-A is a 12-bit word, random access core memory system for the 8A computer. There are two versions available,

the M M8-AA (8192 12-bit words) and M M8-AI3 (16,384 12-bit words). Memory c:ycle time is 1.5 J..Ls. A one inch thick

hex module board contains the core stack. drive circuits. sense circuits. address decoders, etc. These circuits perform all

the operations required to transfer data into or out of core memory. The system plugs into one Omnibus slot but occupies

two spaces on the Omnibus because of the thickness of the module.

1.1.6 MS8-A Read/Write Semiconductor Memory (RAM)

The readlwrite semiconductor memory is a random access memory (RAM) mounted on a single quad board with a

capacity of 1 K. 2K. or 4K 12-bit words. Memory cycle time is 2.4 J..LS for instruction fetches and 2.B J..Ls for all other

states.

1-8

1.1.7 MR8-A Read Memory (ROM)

The MRB-A is a semiconductor read only memory mounted on a single quad board with a capacity of 1 K, 2K, or 4K

12-bit words. Memory cycle time with ROM memory only is 1.5 J.ls.

For those systems containing both ROM and RAM, a 13th bit in each memory location containing ROM and RAM

may be set to a logical 1 when the ROM is programmed to allow the program to address a word in readlwrite mem-

ory. When the 13th bit is on, the content of that memory location is interpreted as a memory address instead of an

operand and used to address the desired RAM memory location. This allows the programmer to use instructions that

require readlwrite operations (i.e., JMS, DCA, ISZ Instructions) when writing the ROM program.

1.1.8 MR8-FB Reprogrammable Read Only Memory (PROM)

The MRB-FB is an ultraviolet-erasable semiconductor memory mounted on a single quad board with a capacity of

1024 12-bit words of PROM and 256 words of readlwrite memory. PROM memory also has a 13th bit which can

be set to one, to address one of the 256 RAM locations. When the 13th bit is one, the eight least significant bits

read from a PROM location are used as an address to select one of the RAM locations. This allows the programmer

to use instructions that require readlwrite operations.

1.1.9 G8016 Power Supply Regulator Module

The GB016 Power Supply module provides + 5 Vdc and -15 Vdc and + 15 Vdc for the semiconductor versions of

the PDP-B/A Miniprocessor. The supply consists of a quad size board containing all the power generation and regu-

lation circuitry necessary to provide these voltages. The power available is:

+5 Vdc

+15 Vdc

-15 Vdc

1.1.10 G8018 Power Supply Regulator Module

20A

0.75 A max }

0.75 A max

sum < 1 A

The G80 18 module supplies power for core memory systems for the BA. It differs from the semiconductor power supply

module in that more power is available:

1.1.11 Interfacing

-5 V 2 A

+5 V 25 A

+15 V 2 A

-15V 2A

+20 V 4 A

NOTE

The G8016 and G8018 Power Supply modules are not

interchangeable. The semiconductor supply (G8016) will

operate only with the PDP-8/A Semiconductor com-

puter; the core memory supply (G8018) will operate only

with the 8A computers.

The PDP-8/A Omnibus is an internal inputloutput bus designed to eliminate random wiring and provide convenient

access to data and control signals. Interfacing is accomplished by inserting modules into non-dedicated slots.

The KA8-E positive 110 bus interface provides an extension to the bus system that facilitates interfacing PDP-B fam-

ily positive bus equipment with the PDP-B/A. The positive 110 bus was designed for use with PDP-B/I and PDP-B/l

compatible peripherals, but it may be employed with almost any positive bus equipment.

1-9

PO P-81 A systems provide three types of data transfer: program med data transfers. program interrupt transfers. and

direct memory access transfers. Programmed data transfer is the easiest to implement and is the most direct method

of handling data 110. Program interrupt transfers provide an extension of 110 capabilities by allowing

liD operations involving two or more devices to be performed concurrently. The' data break system uses direct mem-

ory access for applications involving extremely fast data transfer rates. All three 110 techniques are described in

Chapter 9 of the Miniprocessor Handbook. A detailed description of the Omnibus and its signals is contained in

Chapter 3 of this manual.

1.1.12 Option Modules

The PDP-8/A has two mUlti-option hex modules available. The M8316 module. which contains four separate PDP-8/A

options. and the M8317 module. which contains three options. Each of these modules and the options provided by them

are discussed in the following paragraphs and more fully described in Chapter 6.

1.1.13 DKCS-AA I/O Option Board (MS316)

The M8316 module contains a Serial Line Unit (SLU), a Real Time Crystal Clock. a General Purpose 12-Bit Parallel

liD. and the Programmer's Console control.

1.1.14 KMS-A Extended Option Board (MlS317)

The M8317 module contains the Memory E)(tension and Timeshare Control. Power Fail and Auto Restart. and the

Bootstrap Loader options.

1.1.15 Peripheral Options

Digital Equipment Corporation designs and manufactures many of the peripheral devices offered with the PDP-81 A.

All peripheral options purchased from Digital include the necessary cables. controllers. interfaces. etc. required for

system operation. Most options can be added to the system simply by inserting the modules into the Omnibus and

making cable connections between the modult3s and the peripherals.