Professional Documents

Culture Documents

01 Handout

Uploaded by

Herdian NugrahaOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

01 Handout

Uploaded by

Herdian NugrahaCopyright:

Available Formats

Slide 1

Computer Organization

01

Introduction Computer Evolution & Performance

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 2

KONTRAK PERKULIAHAN

Link to Dokumen Kontrak Perkuliahan

Materi kuliah dan praktikum dapat diunduh dari LMS

Enrolement key untuk LMS: orkom1p8genap1314

DEPARTEMEN ILMU KOMPUTER INSTITUT PERTANIAN BOGOR

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 3

Architecture & Organization 1

Architecture is those attributes visible to the programmer

Instruction set, number of bits used for data representation,

I/O mechanisms, addressing techniques.

e.g. Is there a multiply instruction?

Organization is how features are implemented

Control signals, interfaces, memory technology.

e.g. Is there a hardware multiply unit or is it done by repeated

addition?

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 4

Architecture & Organization 2

All Intel x86 family share the same basic architecture

The IBM System/370 family share the same basic

architecture

This gives code compatibility

At least backwards (with some notes)

Virtual machine?

Emulator?

Organization differs between different versions

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 5

Structure & Function

Structure is the way in which components relate to each

other

Function is the operation of individual components as part of

the structure

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 6

Function

All computer functions are:

Data processing

Data storage

Data movement

Control

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 7

Functional View

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 8

Operations (a) Data movement

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 9

Operations (b) Storage

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 10

Operation (c) Processing from/to

storage

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 11

Operation (d)

Processing from storage to I/O

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 12

Structure - Top Level

Peripherals

Computer

Central

Processing

Unit

Computer

Main

Memory

Systems

Interconnection

Input

Output

Communication

lines

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 13

Microcontroller: computer miniature

Computer miniature: Processor, Memory, and I/O

Usually used for specific applications (not general

purpose)

Home security

Calculator

Youll learn microcontroller 8051 (the most widely

used in the market)

@Practical Course (this afternoon)

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 14

Structure - The CPU

CPU

Computer

Arithmetic

and

Logic Unit

Registers

I/O

System

Bus

Memory

CPU

Internal CPU

Interconnection

Control

Unit

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 15

Structure - The Control Unit

Control Unit

CPU

Sequencing

Logic

ALU

Internal

Bus

Registers

Control

Unit

Control Unit

Registers and

Decoders

Control

Memory

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 16

First Generation Computers

ENIAC - background

Electronic Numerical Integrator And Computer

Eckert and Mauchly

University of Pennsylvania

Trajectory tables for weapons

Started 1943

Finished 1946

Too late for war effort

Used until 1955

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 17

ENIAC - details

Decimal (not binary)

20 accumulators of 10 digits

Programmed manually by switches

18,000 vacuum tubes

30 tons

1,800 square feet (167.225 m2)

140 kW power consumption

5,000 additions per second (faster than other mechanical

computers available at that time)

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 18

von Neumann/Turing

Stored Program concept

Main memory storing programs and data

ALU operating on binary data

Control unit interpreting instructions from memory and

executing

Input and output equipment operated by control unit

Princeton Institute for Advanced Studies

IAS

Completed 1952

Prototype for all other general purpose computers

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 19

Structure of von Neumann machine

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 20

IAS - details

1000 memory space (words) x 40 bit

Binary number

Number bits: 1 sign bit and 39 value bits

Instruction bits: 2 x 20 instruction

8 opcode or operating code to specify the operation

12 address bits

Set of registers (storage in CPU)

Memory Buffer Register (MBR)

Memory Address Register (MAR)

Instruction Register (IR)

Instruction Buffer Register (IBR)

Program Counter (PC)

Accumulator (AC)

Multiplier Quotient (MQ)

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 21

Structure of IAS

detail

Memory Buffer Register

(MBR)

Memory Address Register

(MAR)

Instruction Register (IR)

Instruction Buffer Register

(IBR)

Program Counter (PC)

Accumulator (AC)

Multiplier Quotient (MQ)

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 22

Commercial Computers

1947 - Eckert-Mauchly Computer Corporation

UNIVAC I (Universal Automatic Computer)

US Bureau of Census 1950 calculations

Became part of Sperry-Rand Corporation

Late 1950s - UNIVAC II

Faster

More memory

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 23

IBM

Punched-card processing equipment

1953 - the 701

IBMs first stored program computer

Scientific calculations

1955 - the 702

Business applications

Lead to 700/7000 series

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 24

Second Generation Computers

Transistors

Replaced vacuum tubes

Smaller

Cheaper

Less heat dissipation

Solid State device

Made from Silicon (Sand)

Invented 1947 at Bell Labs

William Shockley et al.

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 25

Transistor Based Computers

Second generation machines

NCR & RCA produced small transistor machines

Followed by IBM 7000 series

DEC (Digital Equipment Corporation) - 1957

Produced PDP-1

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 26

Third Generation Computers

Microelectronics

Literally - small electronics

A computer is made up of gates, memory cells and

interconnections

These can be manufactured on a semiconductor

e.g. silicon wafer

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 27

Moores Law

Increased density of components on chip

Gordon Moore co-founder of Intel

Number of transistors on a chip will double every year

Since 1970s development has slowed a little

Number of transistors doubles every 18 - 24 months

Cost of a chip has remained almost unchanged

Higher packing density means shorter electrical paths, giving

higher performance

Smaller size gives increased flexibility

Reduced power and cooling requirements

Fewer interconnections increases reliability

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 28

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 29

IBM 360 series

1964

Replaced (& not compatible with) 7000 series

First planned family of computers

Similar or identical instruction sets

Similar or identical O/S

Differentiated by: speed, number of I/O ports (i.e. more

terminals), memory size, and cost

Multiplexed switch structure

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 30

IBM 360 series: multiplexed switch

structure

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 31

DEC PDP-8

1964

First minicomputer

Did not need air conditioned room

Small enough to sit on a lab bench

$16,000

$100k+ for IBM 360

Embedded applications & OEM (Original Equipment

Manufacturers)

BUS STRUCTURE

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 32

DEC - PDP-8 Bus Structure

Omnibus: 96 separated signal channel

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 33

Later generation computers

Semiconductor Memory

1970

Fairchild

Size of a single magnetic core

i.e. 1 bit of storage

Holds 256 bits

Non-destructive read

Much faster than core, but price per bit was higher than core

Capacity approximately doubles each year price per bit

decreased significantly

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 34

Intel: Microprocessor

1971 Intel 4004

First microprocessor

All CPU components on a single chip

4 bit

Followed in 1972 by Intel 8008

8 bit

Both designed for specific applications

1974 Intel 8080

Intels first general purpose microprocessor

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 35

Speeding it up

Pipelining

On board cache

On board L1 & L2 cache

Branch prediction

Data flow analysis

Speculative execution

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 36

Performance Balance

Processor speed increased

Memory capacity increased

Memory speed lags behind processor speed

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 37

Processor and Memory Performance

Gap

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 38

Solutions

Increase number of bits retrieved at one time

Make DRAM wider rather than deeper

Change DRAM interface

Cache

Reduce frequency of memory access

More complex cache and cache on chip

Increase interconnection bandwidth

High speed buses

Hierarchy of buses

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 39

Handling I/O Devices

Peripherals with intensive I/O demands

Large data throughput demands

Processors can handle this demand, but there is a problem on

moving the data between processor and peripheral

Solutions:

Caching

Buffering

Higher-speed interconnection buses

More elaborate bus structures

Multiple-processor configurations

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 40

Typical I/O Device Data Rates

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 41

The Key is Balance

Processor components

Main memory

I/O devices

Interconnection structures

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 42

Intel Microprocessor Performance

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 43

New Approach Multiple Cores

Multiple processors on single chip

Large shared cache

Within a processor, increase in performance proportional to

square root of increase in complexity

If software can use multiple processors, doubling number of

processors almost doubles performance

So, use two simpler processors on the chip rather than one more

complex processor

With two processors, larger caches are justified

Power consumption of memory logic less than processing logic

Example: IBM POWER4

Two cores based on PowerPC

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 44

Pentium Evolution (1)

8080

first general purpose microprocessor

8 bit data path

Used in first personal computer Altair

8086

much more powerful

16 bit machine

instruction cache, pre-fetch few instructions

8088 (8 bit external bus) used in first IBM PC

80286

16 MByte memory addressable

80386

32 bit

Support multitasking

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 45

Pentium Evolution (2)

80486

sophisticated powerful cache and instruction pipelining

built in math co-processor

Pentium

Superscalar

Multiple instructions executed in parallel

Pentium Pro

Increased superscalar organization

Aggressive register renaming

branch prediction

data flow analysis

speculative execution

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 46

Pentium Evolution (3)

Pentium II

MMX technology

graphics, video & audio processing

Pentium III

Additional floating point instructions for 3D graphics

Pentium 4

Note Arabic rather than Roman numerals

Further floating point and multimedia enhancements

Itanium

64 bit

see chapter 15

Itanium 2

Hardware enhancements to increase speed

See Intel web pages for detailed information on processors

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 47

Summary

Generations of Computer

Vacuum tube - 1946-1957

Transistor - 1958-1964

Small scale integration - 1965 on

Up to 100 devices on a chip

Medium scale integration - to 1971

100-3,000 devices on a chip

Large scale integration - 1971-1977

3,000 - 100,000 devices on a chip

Very large scale integration - 1978 -1991

100,000 - 100,000,000 devices on a chip

Ultra large scale integration 1991 Over 100,000,000 devices on a chip

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 48

Tugas 1: Benchmark

Pelajari:

Processor time,T

MIPS rate

MFLOPS rate

Ratio of reference run-time to the system run

time

Amdahls Law (Speedup)

Materi-materi di atas akan menjadi bahan Quiz minggu

depan (quiz sebelum praktikum)

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 49

Tugas 1: Benchmark

Bandingkan 2 komputer dengan spesifikasi yang berbeda

Baca contoh-contoh software perbandingan di

www.tomshardware.com dan www.anandtech.com

3dmark

SiSoft Sandra

Windows Experience Index

Buat laporan benchmark tidak lebih dari 5 halaman

Kelompok: sesuai dengan kelompok untuk praktikum,

satu kelompok 2 orang

Pembagian kelompok untuk P1, P2, dan P3; dan

Pergantian jadwal untuk P1

akan didiskusikan saat praktikum

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

Slide 50

References

Stallings W., Computer Organization and Architecture, 9th

Ed., 2012, Prentice Hall

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

________________________________________________________________________________

____________________________________________________________

You might also like

- Gunadarma Workshopsecurity 170310091703Document31 pagesGunadarma Workshopsecurity 170310091703Herdian NugrahaNo ratings yet

- Prediksi Tingkat Keberhasilan Mahasiswa Tingkat I Ipb Dengan Metode K-Nearest NeighborDocument31 pagesPrediksi Tingkat Keberhasilan Mahasiswa Tingkat I Ipb Dengan Metode K-Nearest NeighborHerdian NugrahaNo ratings yet

- Price List Pahala ExpressDocument17 pagesPrice List Pahala ExpressHerdian NugrahaNo ratings yet

- Joomla Guide FinalDocument41 pagesJoomla Guide FinalHerdian NugrahaNo ratings yet

- MY ResumeDocument3 pagesMY ResumeHerdian NugrahaNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5782)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- BeamSmokeDetectors AppGuide BMAG240 PDFDocument8 pagesBeamSmokeDetectors AppGuide BMAG240 PDFMattu Saleen100% (1)

- Fundamental of ICT: Study PresentationDocument12 pagesFundamental of ICT: Study PresentationBikal ShresthaNo ratings yet

- Getting Started With v6Document13 pagesGetting Started With v6Eder ApazaNo ratings yet

- Huawei IPCC SolutionDocument12 pagesHuawei IPCC Solutionsimonpeter02No ratings yet

- Schema Instrument Air-01Document1 pageSchema Instrument Air-01OudadLeO-marNo ratings yet

- IGCSE Syllabus Checklist - ICT (0417)Document15 pagesIGCSE Syllabus Checklist - ICT (0417)Melissa Li100% (1)

- 6.6 Evaluation Rating Sheet For Non PrintDocument10 pages6.6 Evaluation Rating Sheet For Non PrintMichele AlfecheNo ratings yet

- Machine Coverage and Area DetrminationDocument4 pagesMachine Coverage and Area DetrminationMaria Lourdes samontinaNo ratings yet

- Galaxy 3C at 95Document3 pagesGalaxy 3C at 95Edson Manuel Solorzano BelisarioNo ratings yet

- Centum VP 7 ENG Advanced Labs - GlobalDocument6 pagesCentum VP 7 ENG Advanced Labs - GlobalNikhilesh Muraleedharan100% (1)

- Design of Experiments - Wikipedia, The Free EncyclopediaDocument12 pagesDesign of Experiments - Wikipedia, The Free EncyclopediaKusuma ZulyantoNo ratings yet

- (Ye-Tm) Thread Mills PDFDocument12 pages(Ye-Tm) Thread Mills PDFdavidNo ratings yet

- Proof of Stock OwnershipDocument5 pagesProof of Stock OwnershipSebastian GarciaNo ratings yet

- Learjet 60 MMEL Revision 5 SummaryDocument102 pagesLearjet 60 MMEL Revision 5 SummaryHonorio Perez MNo ratings yet

- Procedural Due Process - Refers To The Mode of Procedure Which GovernmentDocument13 pagesProcedural Due Process - Refers To The Mode of Procedure Which GovernmentCharlene M. GalenzogaNo ratings yet

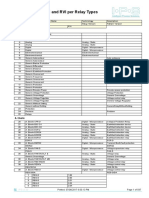

- IPS-ENERGY - Available Relay ModelsDocument597 pagesIPS-ENERGY - Available Relay Modelsbrahim100% (2)

- Regulating Admin AccountsDocument5 pagesRegulating Admin Accountsami pritNo ratings yet

- Syllabus For The 2019 Bar Examinations Labor Law and Social Legislation I. General ProvisionsDocument3 pagesSyllabus For The 2019 Bar Examinations Labor Law and Social Legislation I. General ProvisionsBret MonsantoNo ratings yet

- Isye 6669 HW 2: 1 2 3 3 I 1 I 2 I 1 4 J 2 Ij I 3 T 1 X T! 1 K 1 2 K 1 3 I 1 I J 1 I+J 4 N 2 N+2 M N N MDocument2 pagesIsye 6669 HW 2: 1 2 3 3 I 1 I 2 I 1 4 J 2 Ij I 3 T 1 X T! 1 K 1 2 K 1 3 I 1 I J 1 I+J 4 N 2 N+2 M N N MMalik KhaledNo ratings yet

- Solutions For Smarter and Smoother People FlowDocument12 pagesSolutions For Smarter and Smoother People FlowMichelle SusantoNo ratings yet

- Chapter 03 - Coding in The SAPScript EditorDocument25 pagesChapter 03 - Coding in The SAPScript EditorLukas CelyNo ratings yet

- Detecting Improvements in Forecast Correlation SkiDocument15 pagesDetecting Improvements in Forecast Correlation SkiDiki ZulfahmiNo ratings yet

- Ima612s - Intermediate Macroeconomics - 2nd Opp - Jan 2020Document7 pagesIma612s - Intermediate Macroeconomics - 2nd Opp - Jan 2020Martha EeluNo ratings yet

- (National Lampoon, April 1970 (Vol. 1 No. 1 - Sexy Cover Issue) ) Doug Kenney, Henry Beard and Robert Hoffman-National Lampoon Inc. (1970) PDFDocument90 pages(National Lampoon, April 1970 (Vol. 1 No. 1 - Sexy Cover Issue) ) Doug Kenney, Henry Beard and Robert Hoffman-National Lampoon Inc. (1970) PDFBruno Ferreira67% (6)

- Revenue Memorandum Order No. 021-20: I. BackgroundDocument8 pagesRevenue Memorandum Order No. 021-20: I. BackgroundHADTUGINo ratings yet

- Michael Haid Four Key HR Practices That Drive RetentionDocument6 pagesMichael Haid Four Key HR Practices That Drive RetentionBiswajit SikdarNo ratings yet

- TL594 Pulse-Width-Modulation Control Circuit: 1 Features 3 DescriptionDocument33 pagesTL594 Pulse-Width-Modulation Control Circuit: 1 Features 3 Descriptionاحمد زغارىNo ratings yet

- ABB Connectivity PackagesDocument102 pagesABB Connectivity Packagestin_gabby4876100% (1)

- Tek Radius ManualDocument42 pagesTek Radius ManualjesusvpctNo ratings yet

- NetSDK Programming Manual (Camera)Document93 pagesNetSDK Programming Manual (Camera)Bat-Erdene NasanbatNo ratings yet