Professional Documents

Culture Documents

Analisis de Multietapa PDF

Uploaded by

alexepn23Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Analisis de Multietapa PDF

Uploaded by

alexepn23Copyright:

Available Formats

Escuela Politcnica Nacional

Facultad de Ingeniera Elctrica y Electrnica

IEE544 Circuitos Electrnicos

Ricardo LLugsi Caar 1

Escuela Politcnica Nacional

Facultad de Ingeniera Elctrica y Electrnica

Materia: IEE544 Circuitos Electrnicos

Profesor: Ricardo LLugsi Caar, Ing. MSc.

Objetivo

Revisar los conceptos relacionados a Amplificadores Multietapa

Escuela Politcnica Nacional

Facultad de Ingeniera Elctrica y Electrnica

IEE544 Circuitos Electrnicos

Ricardo LLugsi Caar 2

Amplificadores multietapa

Un amplificador multietapa bsicamente es un circuito que agrupa varios circuitos o sistemas.

Dichos circuitos pueden estar implementados en base a: transistores (BJT, FET, etc) o

amplificadores operacionales. La amplificacin multietapa es utilizada para cubrir las falencias

relacionadas a ganancia, impedancia de entrada (Zin), impedancia de salida (Zout), inversin de

fase, ancho de banda, entre otros.

Existen diferentes formas de conectar transistores (TBJ, FET, etc) pero bsicamente se busca

utilizar las propiedades descritas para cada configuracin. Por ejemplo para el caso de base

comn, este tipo de amplificadores es utilizado para adaptar fuentes de seal de baja impedancia

de salida como, por ejemplo, micrfonos dinmicos, ya que la impedancia de entrada del mismo

es relativamente baja mientras que su impedancia de salida puede ser alta. Para el caso del

amplificador configurado como colector comn se tiene que la impedancia de entrada del mismo

es alta ( )

L

Z 1 + ~ | . Adems, mientras que su impedancia de salida es bastante baja.

Teniendo en cuenta lo anterior se puede decir que los requerimientos tcnicos del sistema en

donde ser requiera utilizar el amplificador multietapa, dictan cul ser la configuracin adecuada

para su uso. Cada circuito amplificador en las configuraciones antes nombradas se denomina

etapa.

Se puede mencionar que el uso de amplificadores multietapa abarca no solamente aplicaciones

de ingeniera electrnica, automatizacin o comunicaciones. El audio ha sido un tema imperante

siempre a la hora de buscar fidelidad y potencia, por ejemplo existen amplificadores que hacen

uso de dos o ms circuitos de amplificadores, cada uno diseado cuidadosamente para evitar

problemas de distorsin que son fcilmente detectables para el odo humano, para implementar

amplificadores de audio de alta potencia.

A manera de ejercicio a continuacin se plantea el diseo bsico de un amplificador multietapa

de emisor comn, para que cumpla con las siguientes condiciones:

21 =

v

A , O = k R

L

3 . 3 , O > K Z

in

1 . 5 , V V

in

3 . 0

= , kHz f 1 =

Escuela Politcnica Nacional

Facultad de Ingeniera Elctrica y Electrnica

IEE544 Circuitos Electrnicos

Ricardo LLugsi Caar 3

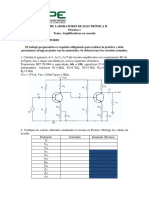

Fig. 1. Amplificador de multietapa

Para resolver el ejercicio primero se deben considerar primeramente ciertas condiciones de

operacin:

1. Comnmente 60

min

= | , 80 =

tip

| , 100

max

= | .

2. Amplificacin de la primera etapa menor a la amplificacin de la segunda (para cumplir

con impedancia de entrada).

3. En el caso requerir impedancias altas en el orden de decenas de k de entrada, se

recomienda el uso de FET en la primera etapa.

4. Siempre comenzar anlisis por la segunda etapa (con la respectiva consideracin de

impedancia de entrada correspondiente si se requiere).

a) Anlisis de segunda etapa

Fig. 2. Amplificacin de cada etapa asumida para el ejercicio

Escuela Politcnica Nacional

Facultad de Ingeniera Elctrica y Electrnica

IEE544 Circuitos Electrnicos

Ricardo LLugsi Caar 4

La impedancia de entrada deriva en que la segunda etapa tambin deber cumplir con una cierta

impedancia de entrada. Dicha impedancia de entrada se determinar de la siguiente forma:

1 _ 1 _

||

etapa B inT total in

R Z Z =

21 11 1 _

||

B B etapa B

R R R =

( )( )

11 1 1 1

1

E e inT

R r Z + + = |

total in inT

Z Z

_ 1

>

( )( )

total in E e

Z R r

_ 11 1 1

1 > + + | (2)

La definicin original de amplificacin es:

1

'

1

||

E e

L

E e

L C

R r

R

R r

R R

A

+

=

+

= , pero para el caso de

multietapa con impedancia de entrada es la siguiente:

11 1

'

1

11 1

2 1

1

||

E e

L

E e

in C

R r

R

R r

Z R

A

+

=

+

=

1

'

1

11 1

A

R

R r

L

E e

= + (1)

Reemplazando (1) en (2) se tiene entonces que:

( )

total in

L

Z

A

R

_

1

'

1

1

1 > + | , por lo tanto

( )

total in L

Z

A

R

_

1

1 '

1

1 +

>

|

Teniendo en cuenta lo anterior se puede decir que:

( )

O

+

> k R

L

3 . 3

1 60

3

'

1

O > 29 . 162

'

1 L

R

O > O 9 . 163 1 . 5 ||

1

k R

C

Escuela Politcnica Nacional

Facultad de Ingeniera Elctrica y Electrnica

IEE544 Circuitos Electrnicos

Ricardo LLugsi Caar 5

O > 9 . 163

1 C

R

Del anlisis de amplificador en emisor comn se tiene que:

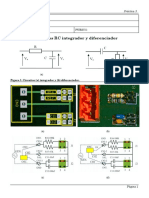

Fig. 3. Curva de operacin del transistor en regin activa (limitantes zona de corte y zona de saturacin)

op C

i I > , se realiza esto para que no exista distorsin a la salida del circuito

'

L

op

C

RC

R

V

R

V

>

Por lo que

op

L

C

RC

V

R

R

V

'

>

Fig. 4. Curva de operacin del transistor. Voltaje en colector y emisor.

Escuela Politcnica Nacional

Facultad de Ingeniera Elctrica y Electrnica

IEE544 Circuitos Electrnicos

Ricardo LLugsi Caar 6

Si

L C

R R << entonces

op RC

V V >

Si

L C

R R = entonces

op RC

V V 2 >

Si

L C

R R >> , digamos

L C

R R 10 = , entonces

op RC

V V 10 >

Tomando en cuenta el criterio de impedancia de entrada relacionado a

C

R , se asume que

O = k R

C

1

1

. Este valor de resistencia se constituye ahora en el nuevo valor de

2 in

Z .

2 _ 2 2

||

etapa B inT in

R Z Z =

22 12 2 _

||

B B etapa B

R R R =

( )( )

12 2 2 2

1

E e inT

R r Z + + = |

2 2 in inT

Z Z >

( )( )

2 12 2 2

1

in E e

Z R r > + + | (2)

La definicin original de amplificacin es:

1

'

1

||

E e

L

E e

L C

R r

R

R r

R R

A

+

=

+

= , pero para el caso de la

segunda etapa del circuito multietapa con impedancia de entrada es la siguiente:

12 2

'

2

12 2

2

2

||

E e

L

E e

L C

R r

R

R r

R R

A

+

=

+

=

2

'

2

12 2

A

R

R r

L

E e

= + (1)

Reemplazando (1) en (2) se tiene entonces que:

( )

2

2

'

2

2

1

in

L

Z

A

R

> + | , por lo tanto

( )

2

2

2 '

2

1

in L

Z

A

R

+

>

|

Teniendo en cuenta lo anterior se puede decir que:

Escuela Politcnica Nacional

Facultad de Ingeniera Elctrica y Electrnica

IEE544 Circuitos Electrnicos

Ricardo LLugsi Caar 7

( )

O

+

> k R

L

1

1 60

7

'

2

O > 75 . 114

'

2 L

R

O > O 75 . 114 1 ||

2

k R

C

O > 75 . 114

2 C

R

Del anlisis de amplificador en emisor comn se tiene que (ver Fig. 3):

op C

i I > , se realiza esto para que no exista distorsin a la salida del circuito

'

L

op

C

RC

R

V

R

V

>

Por lo que

op

L

C

RC

V

R

R

V

'

> (ver Fig. 4)

Si

L C

R R << entonces

op RC

V V >

Si

L C

R R = entonces

op RC

V V 2 >

Si

L C

R R >> , digamos

L C

R R 10 = , entonces

op RC

V V 10 >

Tomando en cuenta el criterio de impedancia de entrada relacionado a

C

R , se asume que

O = k R

C

1

2

. Recordando que

op

L

C

RC

V

R

R

V

'

> se puede escribir a continuacin lo siguiente:

V

k k

k

V

RC

3 . 6

3 . 3 || 1

1

2

O O

O

>

V V

RC

2 . 8

2

>

3 . 1 % 30

2 . 1 % 20

1 . 1 % 10

Escuela Politcnica Nacional

Facultad de Ingeniera Elctrica y Electrnica

IEE544 Circuitos Electrnicos

Ricardo LLugsi Caar 8

3 . 1 * 2 . 8

2

V V

RC

> por lo que V V

RC

7 . 10

2

=

mA

k

V

R

V

I

C

RC

C

7 . 10

1

7 . 10

2

2

2

=

O

= =

2

2

26

E

e

I

mV

r = , teniendo en cuenta que

C E

I I = esto por | alto.

O = = 429 . 2

7 . 10

26

2

mA

mV

r

e

O =

O O

= = + 63 . 109

7

3 . 3 || 1

2

'

2

12 2

k k

A

R

R r

L

E e

Por lo tanto O = 2 . 107

12 E

R

Con O =120

12 E

R ,

in

Z se incrementa, A disminuye, la estabilidad se incrementa.

Con O =110

12 E

R ,

in

Z disminuye, A incrementa, la estabilidad disminuye.

En el caso de que el sistema fuera inestable, por ejemplo con O = 5 . 38

e

r , se debe asumir una

nueva

e

r y de esta manera determinar un nuevo valor de

C

I y por ende un nuevo valor de

RC

V .

2 min 2 2 2

in CE o CE

V V V V + + >

V V V V

CE

9 . 0 2 3 . 6

2

+ + >

V V

CE

2 . 9

2

>

>

>

in E

E

V V

V V

1

, este anlisis se desprende de la estabilidad trmica del circuito, teniendo en cuenta lo

anterior se puede decir que:

in E

V V V

1 + >

Escuela Politcnica Nacional

Facultad de Ingeniera Elctrica y Electrnica

IEE544 Circuitos Electrnicos

Ricardo LLugsi Caar 9

Fig. 5. Curva de operacin del transistor en regin activa (limitantes zona de corte y zona de saturacin) sin seal de

entrada y salida.

Forward active mode = regin activa

mA

mA I

I

C

B

178 . 0

60

7 . 10

min 2

2

2

= = =

|

Se asume que

2 22 B

I I >> , para obtener estabilidad de polarizacin

mA I 8 . 1

22

=

mA mA mA I I I

B

978 . 1 178 . 0 8 . 1

2 22 12

= + = + =

V V V V V V V V

BE CE RC RB

3 . 19 6 . 0 2 . 9 7 . 10

2 2 2 12

= + = + =

O = = = k

mA

V

I

V

R

RB

B

8 . 9

978 . 1

3 . 19

12

12

12

Con O = k R

B

10

12

,

12 RB

V se incrementa,

CE

V se incrementa,

in

Z se incrementa.

Con O = k R

B

1 . 9

12

,

2 RB

V disminuye,

CE

V disminuye,

in

Z disminuye.

Se escoge O = k R

B

10

12

.

Escuela Politcnica Nacional

Facultad de Ingeniera Elctrica y Electrnica

IEE544 Circuitos Electrnicos

Ricardo LLugsi Caar 10

Teniendo en cuenta que O > k Z

in

1

2

entonces:

( )( ) ( )( ) O = = + + = k R r Z

E e inT

9 . 6 43 . 112 61 1

12 2 2 2

|

O > k Z R R

inT B B

1 || ||

2 22 12

O > O O k k R k

B

1 9 . 6 || || 10

22

Por lo que O > k R

B

32 . 1

22

V k mA R I V

B B

38 . 2 32 . 1 * 8 . 1 .

22 22 22

= O = =

V V V

E

9 . 0 1

2

+ >

V V

E

9 . 1

2

>

Se asume que O = k R

B

8 . 1

22

por lo que V k mA R I V

B B

24 . 3 8 . 1 * 8 . 1 .

22 22 2

= O = =

V V V V V V

BE B E

64 . 2 6 . 0 24 . 3

2 2 2

= = =

2

2

22 12 2

E

E

E E E

I

V

R R R = + =

O = = + 73 . 246

7 . 10

64 . 2

22 12

mA

V

R R

E E

Habiendo ya calculado

12 E

R se puede entonces decir que:

O = 7 . 136

22 E

R , escogiendo finalmente O =130

22 E

R

+ =

+ + =

12 2

1 1 1

RB B

E CE RC

V V Vcc

V V V Vcc

V V V Vcc 68 . 21 . 3 . 19 38 . 2 = + =

Escogiendo finalmente V Vcc 22 =

Clculo de capacitores:

2 2 in CB

Z X <<

Escuela Politcnica Nacional

Facultad de Ingeniera Elctrica y Electrnica

IEE544 Circuitos Electrnicos

Ricardo LLugsi Caar 11

12 2 2 E e CE

R r X + << ,

22 2 E CE

R X <<

'

2 2 L CC

R X <<

b) Anlisis de primera etapa. (Opcin 1)

La impedancia de carga de la etapa 1 es la impedancia de entrada de la etapa 1. Dicha

impedancia es:

O = O O O = = = k k k k R Z Z R

etapa B inT in L

25 . 1 8 . 1 || 10 || 86 . 6 ||

2 _ 2 2 1

1 2

'

1

||

L C L

R R R =

Teniendo presente que

op

L

C

RC

V

R

R

V

'

>

V

k k

k

V

RC

9 . 0

25 . 1 || 1

1

1

O O

O

>

V V

RC

62 . 1

1

>

3 . 1 % 30

2 . 1 % 20

1 . 1 % 10

3 . 1 * 62 . 1

1

V V

RC

> por lo que V V

RC

1 . 2

1

=

mA

k

V

R

V

I

C

RC

C

1 . 2

1

1 . 2

1

1

1

=

O

= =

1

1

26

E

e

I

mV

r = , teniendo en cuenta que

C E

I I = esto por | alto.

O = = 38 . 12

1 . 2

26

1

mA

mV

r

e

Escuela Politcnica Nacional

Facultad de Ingeniera Elctrica y Electrnica

IEE544 Circuitos Electrnicos

Ricardo LLugsi Caar 12

O =

O O

= = + 19 . 185

3

25 . 1 || 1

1

'

2

11 1

k k

A

R

R r

L

E e

Por lo tanto O = 8 . 172

1 E

R

Con O =180

11 E

R ,

in

Z se incrementa, A disminuye, la estabilidad se incrementa.

Con O =160

11 E

R ,

in

Z disminuye, A incrementa, la estabilidad disminuye.

Nuevamente como en el caso de amplificador de una sola etapa en emisor comn si se tuviera un

sistema inestable, por ejemplo con O = 5 . 38

e

r , se debe asumir una nueva

e

r y de esta manera

determinar un nuevo valor de

C

I y por ende un nuevo valor de

RC

V .

>

>

in E

E

V V

V V

1

, este anlisis se desprende de la estabilidad trmica del circuito, teniendo en cuenta lo

anterior se puede decir que:

in E

V V V

1

1

+ > , asumiendo V V

E

2

1

= .

O = = = 38 . 952

1 . 2

2

1

1

1

mA

V

I

V

R

E

E

E

O = O O = = 4 . 792 160 38 . 952

11 1 21 E E E

R R R

Se asume finalmente O = 750

21 E

R

Ahora calculando V V V V V V

E B

7 . 2 7 . 0 2 7 . 0

1 1

= + = + =

A

mA I

I

C

B

|

35

60

1 . 2

min 1

1

1

= = =

Se asume que

1 21 B

I I >> , para obtener estabilidad de polarizacin

mA I 35 . 0

21

=

mA A mA I I I

B

385 . 0 35 35 . 0

1 21 11

= + = + =

O = = = k

mA

V

I

V

R

B

B

714 . 7

35 . 0

7 . 2

21

1

21

, con motivo de cumplimiento en impedancia de entrada se

escoge O = k R

B

2 . 8

21

Escuela Politcnica Nacional

Facultad de Ingeniera Elctrica y Electrnica

IEE544 Circuitos Electrnicos

Ricardo LLugsi Caar 13

O =

= k

mA

V V

I

V V

R

B CC

B

12 . 50

385 . 0

7 . 2 22

11

1

11

, con motivo de cumplimiento en impedancia de

entrada se escoge O = k R

B

51

11

Finalmente para definir cul es el valor definitivo de impedancia de entrada se hace calcula dicha

impedancia en funcin de los componentes de la etapa 1:

O = O O O = = k k k k R Z Z

etapa B inT total in

22 . 4 51 || 2 . 8 || 51 . 10 ||

1 _ 1 _

En este caso se puede decir que con O = k R

C

1

1

la impedancia del circuito no llega a ser la

requerida. Pero qu pasara si el valor de esta resistencia aumenta?

c) Anlisis de primera etapa. (Opcin 2)

La impedancia de carga de la etapa 1 es la impedancia de entrada de la etapa 1. Dicha

impedancia es:

O = O O O = = = k k k k R Z Z R

etapa B inT in L

25 . 1 8 . 1 || 10 || 86 . 6 ||

2 _ 2 2 1

1 2

'

1

||

L C L

R R R = , en este caso asumo O = k R

C

5 . 1

2

Teniendo presente que

op

L

C

RC

V

R

R

V

'

>

V

k k

k

V

RC

9 . 0

25 . 1 || 5 . 1

5 . 1

1

O O

O

>

V V

RC

98 . 1

1

>

3 . 1 % 30

2 . 1 % 20

1 . 1 % 10

3 . 1 * 98 . 1

1

V V

RC

> por lo que V V

RC

5 . 2

1

=

mA

k

V

R

V

I

C

RC

C

6 . 1

5 . 1

5 . 2

1

1

1

=

O

= =

Escuela Politcnica Nacional

Facultad de Ingeniera Elctrica y Electrnica

IEE544 Circuitos Electrnicos

Ricardo LLugsi Caar 14

1

1

26

E

e

I

mV

r = , teniendo en cuenta que

C E

I I = esto por | alto.

O = = 25 . 16

6 . 1

26

1

mA

mV

r

e

O =

O O

= = + 27 . 227

3

25 . 1 || 5 . 1

1

'

2

11 1

k k

A

R

R r

L

E e

Por lo tanto O = 022 . 211

1 E

R

Con O = 220

11 E

R ,

in

Z se incrementa, A disminuye, la estabilidad se incrementa.

Con O = 200

11 E

R ,

in

Z disminuye, A incrementa, la estabilidad disminuye.

>

>

in E

E

V V

V V

1

, este anlisis se desprende de la estabilidad trmica del circuito, teniendo en cuenta lo

anterior se puede decir que:

in E

V V V

1

1

+ > , asumiendo V V

E

2

1

= .

O = = = 1250

6 . 1

2

1

1

1

mA

V

I

V

R

E

E

E

O = O O = = 1050 200 1250

11 1 21 E E E

R R R

Se asume finalmente O = k R

E

1

21

Ahora calculando V V V V V V

E B

7 . 2 7 . 0 2 7 . 0

1 1

= + = + =

A

mA I

I

C

B

|

66 . 26

60

6 . 1

min 1

1

1

= = =

Se asume que

1 21 B

I I >> , para obtener estabilidad de polarizacin

mA I 26 . 0

21

=

mA A mA I I I

B

286 . 0 66 . 26 26 . 0

1 21 11

= + = + =

Escuela Politcnica Nacional

Facultad de Ingeniera Elctrica y Electrnica

IEE544 Circuitos Electrnicos

Ricardo LLugsi Caar 15

O = = = k

mA

V

I

V

R

B

B

38 . 10

26 . 0

7 . 2

21

1

21

, con motivo de cumplimiento en impedancia de entrada se

escoge O = k R

B

11

21

O =

= k

mA

V V

I

V V

R

B CC

B

5 . 67

286 . 0

7 . 2 22

11

1

11

, con motivo de cumplimiento en impedancia de

entrada se escoge O = k R

B

68

11

Finalmente para definir cul es el valor definitivo de impedancia de entrada se hace calcula dicha

impedancia en funcin de los componentes de la etapa 1:

O = O O O = = k k k k R Z Z

etapa B inT total in

5 . 5 68 || 11 || 19 . 13 ||

1 _ 1 _

En este caso se concluye que el valor de O = k R

C

5 . 1

2

permite alcanzar la impedancia requerida,

por lo que se puede decir que el valor de

2 C

R influye grandemente en la consecucin del

requerimientos del circuito.

Clculo de capacitores:

1 1 in CB

Z X <<

11 1 1 E e CE

R r X + << ,

12 1 E CE

R X <<

'

1 1 L CC

R X <<

You might also like

- Armónicas en Sistemas Eléctricos IndustrialesFrom EverandArmónicas en Sistemas Eléctricos IndustrialesRating: 4.5 out of 5 stars4.5/5 (12)

- Problemas resueltos de Hidráulica de CanalesFrom EverandProblemas resueltos de Hidráulica de CanalesRating: 4.5 out of 5 stars4.5/5 (7)

- Pares AcopladosDocument51 pagesPares AcopladosCristhianRodriguezNo ratings yet

- Respuesta en frecuencia de amplificador multietapaDocument18 pagesRespuesta en frecuencia de amplificador multietapaManuel Alexis Santillana GarabitoNo ratings yet

- Amplificadores Fet en CascadaDocument10 pagesAmplificadores Fet en CascadaOmar Ruiz Rodríguez50% (2)

- Amplificador Multietapa: El CasCodeDocument20 pagesAmplificador Multietapa: El CasCodeBayron Alexis Cárdenas EspitiaNo ratings yet

- Amplificadores SintonizadosDocument15 pagesAmplificadores SintonizadosBranco Costa OrtegaNo ratings yet

- Laboratorio N2Document17 pagesLaboratorio N2Alexander Lopez Villanueva100% (1)

- Regulador de tensión serie con LM723 para 5V y 4A de corrienteDocument9 pagesRegulador de tensión serie con LM723 para 5V y 4A de corrienteAnthony A NavarroNo ratings yet

- Lab 01 - Elc315Document17 pagesLab 01 - Elc315Nestor VasquezNo ratings yet

- Ea2 Lbo1 g01 01Document17 pagesEa2 Lbo1 g01 01diego.7971No ratings yet

- Aplicaciones Derivador IntegradorDocument5 pagesAplicaciones Derivador IntegradorEdwin SantiagoNo ratings yet

- Amplificador Emisor Comun PDFDocument5 pagesAmplificador Emisor Comun PDFKevin Esleiter LeónNo ratings yet

- El Oscilador en Puente de WienDocument9 pagesEl Oscilador en Puente de WienIsabel100% (1)

- S5 - Respuesta en Frecuencia Del BJT y Simulador Electrónico PartSimDocument8 pagesS5 - Respuesta en Frecuencia Del BJT y Simulador Electrónico PartSimMIGUELNo ratings yet

- Informe1 - LabEP (USO DE SOFTWARE DE SIMULACIÓN PARA CIRCUITOS DE ELECTRÓNICA DE POTENCIA)Document10 pagesInforme1 - LabEP (USO DE SOFTWARE DE SIMULACIÓN PARA CIRCUITOS DE ELECTRÓNICA DE POTENCIA)Mauricio LlanoNo ratings yet

- Circuito Electronicos II Informe Previo 4Document13 pagesCircuito Electronicos II Informe Previo 4fieeg4No ratings yet

- 01 Reporte de PracticaDocument12 pages01 Reporte de PracticaIsrael Pastelin MoralesNo ratings yet

- Configuracion DarlingtonDocument11 pagesConfiguracion DarlingtonedsonygisellaNo ratings yet

- Ampli Cadores MultietapaDocument12 pagesAmpli Cadores Multietapaalvin-jesus-coba-garcia-9437No ratings yet

- Guia de Laboratorio 1 Amplificadores en CascadaDocument7 pagesGuia de Laboratorio 1 Amplificadores en CascadaJeffersonLeonRapNo ratings yet

- ReportePráctica2 3Document9 pagesReportePráctica2 3Angel DiazNo ratings yet

- Ajuste de ancho de banda en amplificador sintonizadoDocument17 pagesAjuste de ancho de banda en amplificador sintonizadoBLANCO ZAMBRANO KEVIN JOELNo ratings yet

- Proyecto Electronica de PDocument11 pagesProyecto Electronica de PElias MartinezNo ratings yet

- Metronomo ElectronicoDocument4 pagesMetronomo ElectronicogermanNo ratings yet

- Configuración en cascada de amplificadores operacionalesDocument6 pagesConfiguración en cascada de amplificadores operacionalesNicolás VelásquezNo ratings yet

- Lab 01Document17 pagesLab 01Rog GarcíaNo ratings yet

- Laboratorio Amplificador Con BJTDocument14 pagesLaboratorio Amplificador Con BJTTextos de Ingenieria100% (6)

- Guía de Laboratorio 7 - Modalidad Presencial - TX Como Amplificador - Rta FrecDocument5 pagesGuía de Laboratorio 7 - Modalidad Presencial - TX Como Amplificador - Rta FrecJHON SEBASTIAN MEJIA CACERESNo ratings yet

- Informe 2Document12 pagesInforme 2FRANCISCO JIMENO YUCUMA MORALESNo ratings yet

- Practica 3Document5 pagesPractica 3ALFREDO SANTILLANNo ratings yet

- Amplificador transistor BJT emisor común: simulación y análisis de Zin y ZoutDocument8 pagesAmplificador transistor BJT emisor común: simulación y análisis de Zin y ZoutIVAN ALONSO CCAHUACHIA LETONANo ratings yet

- PL1. Efecto de La Impedancia de Entrada y Salida en Los AmplificadoresDocument8 pagesPL1. Efecto de La Impedancia de Entrada y Salida en Los AmplificadoresVladimir EstradaNo ratings yet

- Laboratorio de Circuitos Electrónicos 2Document4 pagesLaboratorio de Circuitos Electrónicos 2Daniel ZavalaNo ratings yet

- Informe Final LB03Document8 pagesInforme Final LB03Andrés SánchezNo ratings yet

- AMPLIFICADORES, Taller 8Document11 pagesAMPLIFICADORES, Taller 8Andres Felipe Pulgarin BermudezNo ratings yet

- CARACTERÍSTICAS DE UN CIRCUITO INTEGRADOR O DIFERENCIADORDocument12 pagesCARACTERÍSTICAS DE UN CIRCUITO INTEGRADOR O DIFERENCIADORRodrigo Alonso Flores PalaciosNo ratings yet

- Modulo Teoria de RedesDocument25 pagesModulo Teoria de RedesNicolasErosMondragonCordovaNo ratings yet

- Solucionario 1P Ii-2019Document5 pagesSolucionario 1P Ii-2019Marisol Llanos BarreraNo ratings yet

- Amplificador emisor comúnDocument22 pagesAmplificador emisor comúnEverezNo ratings yet

- Practica 10 Circuitos Resonantes 2019Document5 pagesPractica 10 Circuitos Resonantes 2019DANIEL PATRICIO CADENA MEDRANDA0% (2)

- Laboratorio 5 Respuesta en Frecuencia Del Amplificador Multietapa en CascadaDocument16 pagesLaboratorio 5 Respuesta en Frecuencia Del Amplificador Multietapa en CascadaJessica FernandezNo ratings yet

- Practica AWRDocument11 pagesPractica AWRCARLOS EDUARDO JOVEN GARCIANo ratings yet

- Configuraciones básicas OPAMP - Parte 2Document5 pagesConfiguraciones básicas OPAMP - Parte 2Zach BrianNo ratings yet

- Informe 2 Amplificador TipocDocument8 pagesInforme 2 Amplificador TipocDANIELA ALEJANDRA BUSTOS CASTELLANOSNo ratings yet

- Practica BJTDocument12 pagesPractica BJTPaola TveNo ratings yet

- Ee 443 M Lab 2019 2Document8 pagesEe 443 M Lab 2019 2Franco Gustavo JHNo ratings yet

- Informe Práctica 5 - Amplificador SumadorDocument8 pagesInforme Práctica 5 - Amplificador SumadorByronJorqueNo ratings yet

- Amplificador CascodeDocument28 pagesAmplificador CascodeMyriam JhoannaNo ratings yet

- Informe Final de RLC1Document17 pagesInforme Final de RLC1Carlos Chero Cueva100% (1)

- Analisis en DC en La Primera EtapaDocument7 pagesAnalisis en DC en La Primera EtapaJose Elias Perafan LealNo ratings yet

- Diseño ComversorDocument14 pagesDiseño ComversorVictor ChuquimiaNo ratings yet

- Lab 1 SEADocument21 pagesLab 1 SEA-LeDante-No ratings yet

- Trabajo Final Grupo-49 - Fase-4Document18 pagesTrabajo Final Grupo-49 - Fase-4anon_708234189No ratings yet

- Informe 5Document10 pagesInforme 5Cristian Aste PintoNo ratings yet

- Experiencias sobre circuitos eléctricos en serie operados por corriente directaFrom EverandExperiencias sobre circuitos eléctricos en serie operados por corriente directaNo ratings yet

- CombinatorioDocument1 pageCombinatorioalexepn23No ratings yet

- Memoria DescriptivaDocument2 pagesMemoria Descriptivaalexepn23No ratings yet

- Informe2 Beltran DonosoDocument7 pagesInforme2 Beltran Donosoalexepn23No ratings yet

- Imagenes para ColorearDocument15 pagesImagenes para Colorearalexepn23No ratings yet

- Capitulo 12 LuminotecniaDocument25 pagesCapitulo 12 LuminotecniacorazonpuroNo ratings yet

- Resumen Del Codigo ASCIIDocument2 pagesResumen Del Codigo ASCIIalexepn23No ratings yet

- Prácticas AvidemuxDocument4 pagesPrácticas Avidemuxalexepn23No ratings yet

- Regla de TresDocument1 pageRegla de Tresalexepn23No ratings yet

- CertificadoDocument1 pageCertificadoalexepn23No ratings yet

- Resumen de La Filosofia Gnu/linuxDocument3 pagesResumen de La Filosofia Gnu/linuxalexepn23No ratings yet

- Administracion de RRHHDocument3 pagesAdministracion de RRHHalexepn23No ratings yet

- Prueba de aptitud académica politécnica (2 horas sin calculadoraDocument10 pagesPrueba de aptitud académica politécnica (2 horas sin calculadoraromeofabianNo ratings yet

- Arh EpnDocument5 pagesArh Epnalexepn23No ratings yet

- AssemblerDocument85 pagesAssembleralexepn23100% (1)

- 1er Piso IluminacionDocument20 pages1er Piso Iluminacionalexepn23No ratings yet

- Calculo de Instalaciones ElectricasDocument9 pagesCalculo de Instalaciones Electricasalexepn23No ratings yet

- Prepa8.1 Sistemas MicroprocesadosDocument7 pagesPrepa8.1 Sistemas Microprocesadosalexepn23No ratings yet

- Actitud VerbalDocument87 pagesActitud Verbalalexepn23No ratings yet

- Ebook Tutorial Linux 6.0 0Document170 pagesEbook Tutorial Linux 6.0 0Hugo100% (1)

- Prepa8.1 Sistemas MicroprocesadosDocument7 pagesPrepa8.1 Sistemas Microprocesadosalexepn23No ratings yet

- Instalaciones ElectricasDocument80 pagesInstalaciones ElectricasalexandlyNo ratings yet

- Prueba 2Document14 pagesPrueba 2alexepn23No ratings yet

- Marta Harnecker - El Capital - Conceptos FundamentalesDocument119 pagesMarta Harnecker - El Capital - Conceptos FundamentalesaalmunozNo ratings yet

- La Contaminación y La GuerraDocument2 pagesLa Contaminación y La Guerraalexepn23No ratings yet

- Informe 7Document7 pagesInforme 7alexepn23No ratings yet

- Cap7 MosfetDocument51 pagesCap7 MosfetAldo SalazarNo ratings yet

- Funciones de E-S Alex Beltran PDFDocument4 pagesFunciones de E-S Alex Beltran PDFalexepn23No ratings yet

- JFETDocument6 pagesJFETalexepn23No ratings yet

- Funciones de E-S Alex Beltran PDFDocument4 pagesFunciones de E-S Alex Beltran PDFalexepn23No ratings yet

- Hardware Del OrdenadorDocument1 pageHardware Del OrdenadorCarla100% (1)

- Guia InformaticaDocument7 pagesGuia Informaticaeglen yuhehiler coronado amyaNo ratings yet

- Daewoo TVDocument3 pagesDaewoo TVAlcides Matias Roca PlacidoNo ratings yet

- Programación digital ensambladorDocument31 pagesProgramación digital ensambladorRJ DCNo ratings yet

- Practica 5Document7 pagesPractica 5gestradag-1No ratings yet

- Informatica para Agrimensura Tarea 8Document7 pagesInformatica para Agrimensura Tarea 8Jean OgandoNo ratings yet

- Afinador de Guitarra Con MicrocontroladoresDocument6 pagesAfinador de Guitarra Con MicrocontroladoresJosé Gregorio Rondón100% (1)

- Examen Parcial - Semana 4 - RA - SEGUNDO BLOQUE-ANALISIS Y VERIFICACION DE ALGORITMOS - (GRUPO1)Document6 pagesExamen Parcial - Semana 4 - RA - SEGUNDO BLOQUE-ANALISIS Y VERIFICACION DE ALGORITMOS - (GRUPO1)NELSON MAURICIO HERNANDEZ GOMEZNo ratings yet

- Cap2 ComunicacionDocument12 pagesCap2 Comunicacionkleber tecnologia primeNo ratings yet

- 4.2.2.13 Lab - Configuring and Verifying Extended ACLsDocument9 pages4.2.2.13 Lab - Configuring and Verifying Extended ACLsAlma YaritzaNo ratings yet

- Practica1Shell MohaDocument16 pagesPractica1Shell MohaGinés SaézNo ratings yet

- Izotope RX 9 Audio Editor Advanced (x64)Document2 pagesIzotope RX 9 Audio Editor Advanced (x64)shenNo ratings yet

- Lista de Precios Trascentek SAS 07 09 2020 PDFDocument19 pagesLista de Precios Trascentek SAS 07 09 2020 PDFMAKRO SERVERNo ratings yet

- Practica PAR Tema 2Document5 pagesPractica PAR Tema 2Manuel VazquezNo ratings yet

- Análisis e Implantación de Un Sistema en RedDocument10 pagesAnálisis e Implantación de Un Sistema en RedJavier3MNo ratings yet

- ManualDocument68 pagesManualJavierNo ratings yet

- Manual Actualizacion Conexion FTP - Atenas Grupo ConsultorDocument3 pagesManual Actualizacion Conexion FTP - Atenas Grupo ConsultorhenryNo ratings yet

- Microprocesadores y MicrocontroladoresDocument8 pagesMicroprocesadores y MicrocontroladoresA Gardenia100% (1)

- Aprendiendo Los LenguajesDocument58 pagesAprendiendo Los LenguajesHUMBERTO RIVASNo ratings yet

- Python V2Document27 pagesPython V2Oscar Eulate ChoqueNo ratings yet

- Sistema Cotización Con PC + Lector + BalanzaDocument3 pagesSistema Cotización Con PC + Lector + BalanzaginnaNo ratings yet

- Telemetria - Scada y DCSDocument34 pagesTelemetria - Scada y DCSHelen Cardozo SerranoNo ratings yet

- VTY1111 - Transformación DigitalDocument26 pagesVTY1111 - Transformación DigitalGUILLERMO SALVADOR MUÑOZ TELLONo ratings yet

- Taller Resuelto de La Guia de Hadware InteroDocument5 pagesTaller Resuelto de La Guia de Hadware InteroManuelNo ratings yet

- Diodos IR y LedDocument10 pagesDiodos IR y LedArte Y MecatrónicaNo ratings yet

- Tutorial Snap Preproc Acasella Et Al 2018 IntaDocument31 pagesTutorial Snap Preproc Acasella Et Al 2018 IntaDino Marcos100% (1)

- Evidencia de Aprendizaje - 2Document59 pagesEvidencia de Aprendizaje - 2Arias RobertoNo ratings yet

- Clase #1 - BienvenidaDocument17 pagesClase #1 - BienvenidaCarlos Mario Perez CastillaNo ratings yet

- Clases Abstractas e InterfazDocument10 pagesClases Abstractas e Interfazapower88No ratings yet

- ANALISIS DE ALGORITMO RECURSIVO E ITERATIVO OficialDocument13 pagesANALISIS DE ALGORITMO RECURSIVO E ITERATIVO OficialNestor Hernandez VidezNo ratings yet