Professional Documents

Culture Documents

Control Design For Integrated Switch-Mode Power Supplies A New Challanges

Uploaded by

anhnhamoiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Control Design For Integrated Switch-Mode Power Supplies A New Challanges

Uploaded by

anhnhamoiCopyright:

Available Formats

2W4 35th Annual IEEE Power Electronics Specialists Conference

Aachen, Germany. 2604

Control design for integrated switch-mode power a new challenge?

Bruno Allard', Senior Member, ZEEE, SBverin Trochutt , Xuefang Lin-Shi*, Jean-Marie RBtif'

'CEGELY, CNRS UMR 5005, INSA-Lyon Building L. De Vinci, 20 avenue A. Einstein, F-69621 Villeurbanne Cedex, France Email: {hruno.allard, xuefangshi, jean-marie.retif}@insa-lyon.fr t STMicroelectronics. TPA-Cellular Terminal Division 12, rue Jules Horowitz, BP 217, F-38019 Grenoble Cedex, France Email: severin.trochut@st.com

AbsIract- Hard switching DClDC converten have been studied for decades. Many control techniques have heen reported, and textbooks detail so-called classical control design methods. The Buck converter is known as a simple topology of satisfying stability. However the monolithic integration of a buck converter including the control system leads to a possible non-slable converter in c a s e of large load transienL More generally it is difficult to certify the accuracy of the control system. Integrated switchmode power supplies needs to he investigated focusing control design issues. Global efficiency dictates to limit the budgets in biasing current of control loops, hence limits their bandwidth. Among others, Ibis latter limitation renders the classical control design methods non satisfying. The paper investigates the control design challenge related to integration of switch-mode power supplies (SMF'Ss). Applications are discussed from simulation point-of-view. Particularly a trade-off must be set between control accuracy and performances on load transients. As it is not possible to specify the worst-case load transient, classical control design methods do not offer satisfying results. Alternative control design methods are investigated. Sensitivity transfer functions are introduced and an application method is detailed. Hybrid system methods are also investigated and their application is discussed. The design of integrated SMPSs requires adequate modifications of CAE-tools and design flows.

2002 '04 '06 '08 '10 '12 '14 '16

Year

Year

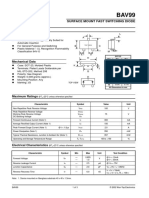

Fig. I . Predictable evolution of CMOS technology in terms of thickness. power supply voltage, transistor threshold voltage (left). switching power losses and leakage power losses (right).

Due to a poor efficiency, a linear voltage regulator is not a practical option particularly if large currents have to be processed, or multiple regulators have to be embedded inside the chip. Integrated synchronous switch-mode power supplies (SMPS) seem to he good candidates. Integration of synchronous SMPS is also boosted by the microprocessor demands in power [6], (71.Switched capacitor converters [8] had been originally studied but show a significant limit in current. They offer no tuning range. SMPS and its monolithic integration is not a new topic [9]. Fully monolithic SMPSs have been presented [IO] and many products are commercially available. The control circuit is not always included and controllers like [ I I ] are often encountered since they are optimized for synchronous converters and offer a predictive gate drive technology. However these demonstrators suffer several limits: the efficiency remains low (less than a minimum go%), the dynamic performances can not cop with large power transient, the design remains quite empirical what is not compatible with the development of Intellectual Properties (IP). The boost converter detailed in [I21 features a little bit more than 50% efficiency. Moreover the optimization procedure detailed in [I31 does not take into account the efficiency as a constraint. The authors only retain the following specifications ignoring the converter control issues.

I.

INTRODUCTION

Fig. 1 pictures the awaited evolution of CMOS technology thickness as published in various papers [I]. The power supply voltage is intended to decrease down to OSV in few years from now. The MOSFET transistor threshold voltage will also suffer a significant decrease. This effect will cause an increase in the transistor leakage current, hence an increase in steady-state power losses (Fig. I). To overcome this dangerous situation with regard to digital circuits, many solutions are already available to the design engineer, and other solutions are under development [2]. For example the dual-gate transistor offers a normal operating gate, and a second gate where a different voltage is applied to stop the drain leakage current when the transistor is in idle mode [3]. Many papers are promoting the adaptive variation of the power supply voltage: the technique is called "voltage hopping" 141. Threshold voltage and power supply voltage must be varied spatially inside the integrated circuit and temporarily during operation to create efficient active leakage control [5]. Embedded voltage regulators will he necessary to produce the variable voltages inside the chip.

0-7803-8399-0/04/$20.00 02004 IEEE.

4492

2004 35lh Annual lEEE Power Elecrronics Specialists Conference

Aachen, G e m n y , 2004

P . the m i m u m rated wwer Row. W

Vi , the w e q e input volmge. V

f, he switching frequency. Hz

A x the

output mak-to-@

"pple. V

v a , the BVErop ou,put " d l a p , v

..:.

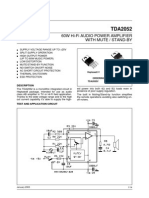

Fig. 3.

Schematic of a Convenient compensator network

delay should be kept at a minimum value to minimize bodydiode conduction loss. In addition, the body-diode reverserecovery related to EM1 is a big concern in high frequency operation. It is assumed here that the driver is optimal (it does not interact with the control design issue).

.".Fig. 4.

.I

.-

.*

. .-.-

Sawtooth, error signal and output voltage during steady-state

The corrector circuit is proposed to implement the following idea, The LC-circuit offers a limited bandwidth (L=IOpH, C=22fiF, fLsdB=lOkHz). An additional frequency decade is at least necessary to obtain the regulation performances. Near IOOkHz the corrector should bring 40dB amplification. The corrector then exhibits a significant gain at the switching frequency. A discrete implementation allows a sever cut-off at the switching frequency but not the monolithic implementation unless sacrifying the efficiency. It is considered a 3V inputvoltage SMPS that regulates a 1.8V output-voltage within a 3% bandwidth. The load current maximum rating is 1A. The error amplifier supply voltage is 3V. Fig. 4 pictures the error voltage during steady-state. Fig. 5 pictures the error voltage during a load transient (load-current demand rises from 6mA to 450mA in Ifis).Saturation appears. The output voltage oscillates and recoven to the regulated value. The 3% bandwidth is exceeded (Fig. 5 ) . Fig. 6 pictures an other case of load current transient that initiates a stable oscillation on the output voltage. This oscillation is not the consequence of a tremendous load transient but the behavior of a particular compensator optimization and the load transients observed in

4493

2w4 35111 A n n u l IEEE Power Electronics Specialisrs Conference

Aachpn, Germany, 2004

.*

^*,-.l:.cul:,

amplifier main pole. A third pole is not physicaly implemented as it should be less than the amplifier Miller pole. With respect to discrete converter, the amplifier main pole is assumed to be sufficiently large, what is not the case in integrated converters.

..

L .

.. .. ..

Fig.1. Small-signalmodel of the p i l o t SMPS

Fig.6. Saw-tooth, error signal and o~tput voltage during a large load transient

Fig. 5 . The controller has been optimized as explained in next section. It is obviously non satisfying. 111. T H ECLASSICAL

CONTROL DESIGN METHODS

Classicaly the first compensator pole, fplr is used to cancel the inductor ESR zero and provide controlled gain roll-off. The second compensator pole, fp2, is used to obtain maximum attenuation of the switching ripple and high frequency noise with minimum phase lag at close-loop crossover frequency fOdB. Two zeros are used to avoid the conditional stability related to L-C double pole and provide additional phase boost. When designing fz, and fi2, the trade-off between the stability margin and the regulator performance should% he considered. The settling time during a load transient is then related to the first zero. The higher is the first zero frequency, the faster is the settling time. Both zeros affect the stability margin and closed-loop overshoot voltage during a load transient. When the frequencies of these two zeros move higher, the stability margin decreases and the overshoot voltage decreases. In fact the design engineer has to settle a trade-off between stability and load transient performances. It is not practicable to test a design against all possible load transients, i.e. for the awaited variations of current starting from any conditions of load current, and for various settling times. Only corner simulations are affordable. Fig. 5 and Fig. 6 relate the limitations of the here-above optimized corrector. Fig. 5 indicates a saturation of the error voltage. In fact the PWM stage may be optimized to attain 100% duty ratio before the error voltage saturation. When including this non-linearity into the small-signal model in Fig. 7, the Nyquist representation in Fig. 8 is obtained. Instead of checking for the locus - I , the designer evaluates the system stability with respect to the curve h(c), related to the first harmonic effect of the considered non-linearity.

1 h(c) = - arcsinX

A

+ A.-,

V&t x=c

(1)

DC/DC converter topologies are presented in numerous textbooks [14][15]. Control of DC/DC converters is also presented. Several hypotheses are introduced. Among others, the network time-constants should be larger than the switching period. The so-called averaged modeling approach may be applied. This method yields in a systematic manner the various transfer functions required to build the control circuit (Fig. 7). The method is available in several commercial CAE-tools [16]. Fig. 3 pictures a convenient compensator circuit. The circuit provides 2 zeros and 3 poles including the operational

The Nyquist figure shows 2 regions. When the load transient is smooth enough to avoid saturation (region #I), the locus - I is not circled and a local stability is assessed. If saturation occurs (region #2), the local stability locus is circled (once) and the stability criterion is endangered. The error voltage saturation leads to an open-loop operation of the SMPS. The output voltage evolves until saturation disappears and the regulation capacity is recovered. The oscillating behavior is then unstable as shown in Fig. 5 . Unfortunately the duration of

4494

2004 35th Annual IEEE Power Electronics Specialists Conference

Aachen. G e m n y , 2W4

sensitivity functions.

%"

r.w + syy.wyi syB.wB +syu.w, r=-- K P -~LYY

I+KP

~

1+Lyy

1 syy = 1 + K P - 1 + L~~

1

(3)

(4)

-KP -Lyy SYB = =1+KP 1+Lyy P P -syu = 1+KP l+Lyy

(5)

Constraints or disturbance rejections are naturally expressed

in terms of frequency sensitivity shapes. For a given corrector optimization, the sensitivity functions allow to evaluate the

Fig. 8.

Nyquist represenlatian including the saturation effect

the oscillating behavior is uncontrolled and the output voltage surely exceeds the 3% bandwidth. The stable oscillation (Fig. 6 ) is related to a phenomenon called "period doubling" as detailed in [17]. It is a complex critical behavior behind the SMPS conditional stability analysis. It appears that the classical control design method shows limitations when applied to a monolithic SMPS compensator. Alternative control design methods must be evaluated. The compensator circuit may also be adapted, and design methods are required to guide the circuit synthesis.

corrector behavior in relation to the desired attenuation constraints. In addition, the margin module and the margin delay quantify the robustness of the modeling uncertainties. Fig. IO presents the Nyquist plot of L y y . The module margin A M is defined as the minimum distance of L y y to the critical locus -1. The delay margin AT is deduced from the phase margin A@ by A r =

/--h

IV. ALTERNATIVE METHODS

The paper investigates two alternative ways for control design.

A. Sensirivizy transfer matrix

Sensibility transfer functions may be considered instead of the output-to-duty-ratio and the output-to-input transfer functions. Fig. 9 represents the SMPS (P(s))and its corrector (K(s)) when adding control noise W u , output noise W y and measurement noise W E .The objective is the study of the system dynamics, robustness and noise rejection properties. From Fig. 9, it comes the following relation that leads to the

W"

Fig. 10. Typical Nyquist plot of L u y

wh

Fig. 9.

Flow-graph representation of the SMPS

Fig. I I illustrates the sensibility o f output-to-output S y y , the sensibility of measure to output and the sensitivity of control-to-output.The module and the delay margins in S y y evaluate the stability of the closed loop system; and the gradient of S y y on low frequency determines the dynamic behavior of the system. The bandwidth on S y s defines the close-loop bandwidth and the influence of noise on the output voltage. The gain on Syu verifies the rejection of control perturbations such as the noises introduced by the PWM. The gradient of S y y at low frequency determines the dynamic behavior of the system. The bandwidth of Sya defines the close-loop bandwidth and the influence of noise on the output voltage. The gain of Syu verifies the rejection of control perturbations such as the PWM-related noises. The robustness constraints and the knowledge on the disturbances leads to design the correctors in terms of poles and zeros assignments. The margin values depend on the model precision and the component dispersion. In order to ensure robustness, the

4495

2004 351h Annual IEEE Power Electronics Specialists Conference

Aachen, Germany, 2W4

On the same way, other membership functions and fuzzy

rules in relation with the sensitivity functions can he defined to

quantify disturbance rejection. The corrector design becomes an optimization problem in order to find the optimum of the global fuzzy cost function which takes into account constraints of robustness and satisfies the requirements of disturbance rejection performances. A stochastic genetic algorithm is generally used to realize this optimization. The authors have no results to include at time of edition.

B. Hybrid dynumicul systems

Hybrid system approaches [IS], [19], [ZO], [211, [22] have been introduced to solve control problems in case of complex systems. The synchronous buck converter may be seen as an hybrid system, with 2 or more states depending on current conduction conditions. I) Definition: A hybrid system is a dynamical system that cannot be represented and analyzed with sufficient precision either by the methods of the continuous systems theory or by the methods of the discrete systems theory ([231). A hybrid system is consistently a combination of continuous states and abrupt state jumps. The jump conditions and dates may not be easily predicted. Basically the jumps are classified between autonomous jumps and controlled state jumps. Autonomous and control switchings will then define the environment of the related jumps. The hybrid automaton in Fig. 14 comprises 3 states in discontinuous conduction mode. It combines 3 timeindependent models. The separate analysis of the 3 models is very easy but the analysis of the system as a whole is difficult. It is known for example that the system may be unstable even if the two matrices A. to A2 are stable ([24]). 2 ) Srabilify: The methods are based on hybrid automaton representations but may be separated in two classes. Methods rely on sensitivity matrices with varying eigenvalues, and tend to picture locuses of eigenvalues that correspond to converter stability. Worst-case corner of operating conditions are pictured on the locuses and a trade-off may be defined from graphical data. Other methods state the problem in terms of collections of states (trajectories during a transient), and try to define safe sets of state. called "safe balls". Trade-offs between stability and load transient performances may be accessed through graphical representation. Most of the papers detail the application to boost topologies,

as they are reputed of bad stability. The pilot SMPS hybrid

Fig. I I .

Sensitivity Functions

module margin AM is kept higher than 0.5, the phase margin is about 4 5 ' . Experience leads to set the delay margin at ahout half the switching period Tawitch. But the frontier is not so strict. Fuzzy logic is more suitable to quantify robustness, An example of membership functions qualifying the phase margin and delay margin is shown in Fig. 12.

Fig. 12. Membership functions based on AM and AT

The membership function of a cost on the output voltage is given in Fig. 13. The stability robustness can be expressed by

Fig. 13. Membership functions o f a cost on the output voltage

the fuzzy rules defined in the following table.

Medium

automaton is pictured in Fig. 14. 3) Simulation: Many simulators are able to handle hybrid system and perform some accurate simulations. Since many of them are not free of charges, the authors decided to implement their own simulator based on a free framework (scilab [E]) which is able to solve differential equation. Fig. 15 shows the simulation results of Fig. 14 hybrid model. Some subharmonics oscillations are present. This is due to numerical integration precision. But still, this result can be compared 10 Fig. 4.

4496

2004 35rh A n n u l IEEE Power Electronics Specialists Conference

Aachen. C e m n y , 2004

IC

IIFs

France, for the manufacturing o f SMPS ICs and for the financial support o f this study.

REFERENCES

111 T. Sakurai. "Perswctives no r~ nower-aware ofthe IEEE . electronics."Pmc. ~~~~~~~~~, r~~~~ lnternatinnnl Solid-Stare Circuit Conference, 2003, cdrom, paper 1.2.

L ~ 1 ~

~~~~ ~ ~~ ~~ ~

~1

VerrorcVramp

Lo_1

lI=O

x- = A,X + B , U 1' = CIX+ D I U

(21 MARLOW, " A comprehensive bibliography on low-power design:' www.1owp<>wernrg. 2002. [3] W. Kludge, L. Dathe, and R. Jaehne, "A 2.4GHz CMOS m s c e i v e r a n s : ' Pmc. of the IEEE hrernntionul Solid-State for 802.1 Ib wireless l Circuir Confennce, 2003. cdrom, paper 20.6. 141 S . Lee and T. Sakurai. "Run-time voltage happing for low-power reatime systems," Pmc. o f Design Auto,mtinn Conference. pp. 806-809.

lllne 2000~ .. [5] Y. Nakagome, M. Horiguchi, T. Kawahara. and K. Itoh, "Review and prospects of low-voltage RAM circuits," IBM Journal ofR&D, vol. 47, "0. 516. SeptINov 2003. [6] H. Wetrel, N. Fraehleke, F. Meier. and P. Ide, "Comparison of lowvoltage tooologies for voltage regulator modules:' P m . of the IEEE Indutry Applicorionr Society Annul Meering. 2002, cdrom. 171 "Center for Dower electronic svstems : Annual reoort." Wminia Tech

~~~~

Fig. 14. Hybrid model of the buck SMPS

,all

I -

,I -

- -

, M I

IWL

,rnM

1 %

-I

21%

I_

n u

. % . a

227-

'2-

>%

.-

..,_

. , h .

Fig. 15. Hybrid model simulation of the buck SMPS

V. CONCLUSION

The paper issue i s to enlighten the problem o f control design for integrated SMPSs. Classical methods have proved efficient on discrete SMPSs, hut lead to limited results in the case of integrated SMPSs. A large SMPS bandwidth i s desired and unstable compensators are required. Particularly the limited bandwidth of the amplifiers modifies the specifications of the control system. Ever-increasing switching frequencies will still harden the situation. Digital control systems are not practicable and the analog counter-parts require to fix values for poles and zeros i n order to satisfy a trade-off between accuracy and performances with regard to load transients. The paper explains the inner stability problem. Alternative control design methods are investigated. Sensibility functions appears more robust but do not solve the stability problems. Hybrid dynamical systems have proved efficient with boost technologies and could be fruitfully applied to the monolithic buck topology. However the method complexity increases and adequate design tools should be provided to the I C designer whose prime concerns are related to silicon implementation.

ACKNOWLEDGMENT

The authors wish to thank Dr Christophe Pr6mont for his technical support and also STMicroelectronics i n Grenoble,

"0.2, pp. 228-235. 1998. [9] A. Stratakos. S. Sanders, and R. Brodersen. "A low-voltage CMOS DCIDC convener for a portable batteryoprated system:' Pme. < f i h e IEEE Power Electmnics special is^'^ Conference, pp. 619426. 1994. [IO] K. S . A. Abedinpour, Trivedi, "DC-DC power converter for monolithic f the IEEE Industry Applicorims Society Animplementation," Pmc. o nu01 Meeting. pp. 2471-2475. 2000. [ I I] T12003. "TPS4002X datasheet, enhanced. low-input voltage-mode synchronous buck controller:' Tam Insrru,nents Literorure, vol. SLUS535, 2003. [I21 E. McShane and K. Shenai, "A CMOS monolithic 5MHz. SV,250mA. 56% efficiencv switch-mode boost converter with dvnamic PWM for embedded power management," Pmc. cfthe IEEE Industry Applicrrtions Sociefy Annual Meeting, pp. 653451, 2001. 1131 S . Musunuri and P. Chapman, "Optimization issues for fullyintegrated CMOS DC-DC conveners.'' Pmc. of the IEEE Industry Applicolions Society Annual Meeting. 2002, cdrom. I141 N. Mohan, T. Undelmd. and R. Robbins, Power electmnics cunve~ters,rrpplicrrtiunr ond design. Wiley Inter-Science. 1995. 2nd edition. f Power E1ectmnic.v. [IS] R. W. Erickson and D. Maksimavic, Fundomentdv o Kluwer, 2001, 2nd edition. [I61 N. Froehleke, D. H a m , H. Mundinger, H.Njiende. and P. Wallmeier, "Cae-tool for optimizing development of swichted mode power supf the IEEE Applied Power Electmnics Conference. vol. 2, plies,'' Pmc. o pp. 752-758. March 2001. [I71 G. Papafotiu and N. Margaris. "Calculation and stability investigation of periodic steady-states of the voltage-controlled buck DCfDC converter," IEEE Transactions Power Electmnics. 2003, to be published. 1181 K. Wong, "Stability study of a voltage-mode buck regulator using system poles approach," Pmc. ofthe IEEE. 2002. [I91 B. Wong and H. Chung. "Steady-state analysis of PWM DCIDC switching regulators using iterative cycle time-domain simulation," IEEE Tronsactionr Industry Applications, vol. 45, no. 3, pp. 421432, 1998. 1201 M. Senesky, F. Eirea, and T. Kao. "Hybrid modelling and control of power electronics:' P m . o f rhe Hybrid System Contml Conference, pp. 4 5 W 6 5 , 2003. [2 I] B. Wong, H. Chung, and S . Lee, "Computation of the cycle state-variable sensitivity matrix of PWM DCIDC eonvenem and its applications," IEEE Trmactiuns Circuitr&Systems-l. vol. 47, no. IO, pp. 1542-1548, 2000. [22] D. Liberaon, Switchin8 in sysemr and conrml. sec Foundations and Applications Series. Systems and Contml Ed.. 2003, 248p. 1231 J. Lunle and J . Raisch. Discrere models for hybrid sysretns, ser. Modelling, Analysis, and Design of Hybrid Systems. Springer, 2002. DD. 3-14. 1241 . . M. Bmickv. "StabiliN of switched and hybrid svstems:' Pmc of the IEEE Conference on Dension and Contml. pp. 3498-3503, 1994. [25] INRIA. Scilab [Online]. Available: www.scilal.org

~~

~I

4497

You might also like

- Nyquist Bode NicholsDocument22 pagesNyquist Bode NicholsanhnhamoiNo ratings yet

- LicenseDocument6 pagesLicenseevox777No ratings yet

- ch11 NewDocument74 pagesch11 NewshankarNo ratings yet

- Hanh Phuc LeDocument1 pageHanh Phuc LeanhnhamoiNo ratings yet

- FootprintDocument2 pagesFootprintanhnhamoiNo ratings yet

- Save FileDocument23 pagesSave FileanhnhamoiNo ratings yet

- Save FileDocument2,461 pagesSave FileanhnhamoiNo ratings yet

- Karnaugh For Counter DesignDocument2 pagesKarnaugh For Counter DesignanhnhamoiNo ratings yet

- Verbal - Advantage - 10 Easy Steps To A Powerful Vocabulary (Unabridged)Document489 pagesVerbal - Advantage - 10 Easy Steps To A Powerful Vocabulary (Unabridged)TanveerAli01No ratings yet

- ADocument1 pageAanhnhamoiNo ratings yet

- SaveDocument12 pagesSaveanhnhamoiNo ratings yet

- Trans Analysis1Document39 pagesTrans Analysis1anhnhamoiNo ratings yet

- English TutorialDocument1 pageEnglish TutorialanhnhamoiNo ratings yet

- DcopeDocument12 pagesDcopeanhnhamoiNo ratings yet

- SaveDocument1 pageSaveanhnhamoiNo ratings yet

- Minna No Nihongo - Mondai ScriptDocument60 pagesMinna No Nihongo - Mondai ScriptAlex84% (31)

- BooksDocument1 pageBooksanhnhamoiNo ratings yet

- OtlDocument18 pagesOtlanhnhamoiNo ratings yet

- ENGLISH WRITING SESSION ON THEMATIC DISTRIBUTIONDocument18 pagesENGLISH WRITING SESSION ON THEMATIC DISTRIBUTIONanhnhamoiNo ratings yet

- Vietnam Economic TimesDocument1 pageVietnam Economic TimesanhnhamoiNo ratings yet

- SMPSDocument6 pagesSMPSanhnhamoiNo ratings yet

- SWR - the persistent myth explainedDocument66 pagesSWR - the persistent myth explainedAliNo ratings yet

- Lec6 LNADocument33 pagesLec6 LNAanhnhamoiNo ratings yet

- ResearchDocument1 pageResearchanhnhamoiNo ratings yet

- Idct VDocument14 pagesIdct VanhnhamoiNo ratings yet

- Chapter 16Document53 pagesChapter 16morrisjrlNo ratings yet

- Noise in Solid-State Devices and LasersDocument29 pagesNoise in Solid-State Devices and LasersanhnhamoiNo ratings yet

- MesDocument1 pageMesanhnhamoiNo ratings yet

- Laplace Transforms and Circuit AnalysisDocument6 pagesLaplace Transforms and Circuit AnalysisanhnhamoiNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- B 3 Ga 012 ZDocument10 pagesB 3 Ga 012 Zgigel1980No ratings yet

- Magnetic Perovskites - Synthesis, Structure and Physical Properties-Springer India (2016)Document174 pagesMagnetic Perovskites - Synthesis, Structure and Physical Properties-Springer India (2016)Andrés Garzòn PosadaNo ratings yet

- A Two-Stage Isolated/Bidirectional DC/DC Converter With Current Ripple Reduction TechniqueDocument3 pagesA Two-Stage Isolated/Bidirectional DC/DC Converter With Current Ripple Reduction TechniqueariphineNo ratings yet

- Realization of Op-Amp as Integrator and DifferentiatorDocument3 pagesRealization of Op-Amp as Integrator and DifferentiatorNagendra KumarNo ratings yet

- Ampli 500W Manual For FM AmplifierierDocument66 pagesAmpli 500W Manual For FM Amplifierierkruna123No ratings yet

- Microcontroller Projects Digital Voting Using Pic MicrocontrollerDocument3 pagesMicrocontroller Projects Digital Voting Using Pic MicrocontrollerAbdullah Omar NasifNo ratings yet

- User Manual TV Power Demoboard TEA8818DB1440: TEA8818 + TEA1995 130W 13V and 90V Power SupplyDocument29 pagesUser Manual TV Power Demoboard TEA8818DB1440: TEA8818 + TEA1995 130W 13V and 90V Power SupplyCube7 Geronimo50% (2)

- PI8000 Frequency Inverter User ManualDocument187 pagesPI8000 Frequency Inverter User ManualLuis StevensNo ratings yet

- Dr. B.justus RabiDocument6 pagesDr. B.justus Rabianon_842868788No ratings yet

- Effects of Stress and Depolarization On Electrical Behaviors of Ferroelectric Field-Effect TransistorDocument3 pagesEffects of Stress and Depolarization On Electrical Behaviors of Ferroelectric Field-Effect TransistordabalejoNo ratings yet

- Memorex MT2206 TV Service ManualDocument64 pagesMemorex MT2206 TV Service ManualMalcolm RockNo ratings yet

- EC GATE 2017 Set I Key SolutionDocument21 pagesEC GATE 2017 Set I Key SolutionJeevan Sai MaddiNo ratings yet

- The ARM ProcessorDocument24 pagesThe ARM ProcessorJinto Chacko Mathew100% (2)

- A Low Voltage To High Voltage Level Shifter Circuit For MEMS Application PDFDocument4 pagesA Low Voltage To High Voltage Level Shifter Circuit For MEMS Application PDFoht993No ratings yet

- Polyhouse Automation1Document23 pagesPolyhouse Automation1Chaitanya GajbhiyeNo ratings yet

- Important MCQ on VLSI Design Logic Gates and CMOS TechnologyDocument4 pagesImportant MCQ on VLSI Design Logic Gates and CMOS TechnologyAkanksha DixitNo ratings yet

- Al2O3 Material Properties GuideDocument3 pagesAl2O3 Material Properties GuideRing MasterNo ratings yet

- CKG7507Document9 pagesCKG7507api-3800166No ratings yet

- VLSI Technology Course PlanDocument4 pagesVLSI Technology Course PlanMahendra BabuNo ratings yet

- User'S Manual: MODEL: MMA160/200Document9 pagesUser'S Manual: MODEL: MMA160/200Vlaovic GoranNo ratings yet

- FPGADocument122 pagesFPGANishit Gupta100% (2)

- Button debouncing explained in detailDocument2 pagesButton debouncing explained in detailAndrei Linca-TorjeNo ratings yet

- LDMOS Power Modules for Two-Way Mobile RadiosDocument14 pagesLDMOS Power Modules for Two-Way Mobile RadiosPhạm TuyểnNo ratings yet

- Tonio Buonassisi Associate Professor of Mechanical Engineering Thesis SupervisorDocument59 pagesTonio Buonassisi Associate Professor of Mechanical Engineering Thesis SupervisorMINH NGUYỄN THẾNo ratings yet

- This Test Contains A Total of 15 Objective Type Questions. Each Question Carries 1 Mark. There Is NO NEGATIVE MarkingDocument10 pagesThis Test Contains A Total of 15 Objective Type Questions. Each Question Carries 1 Mark. There Is NO NEGATIVE MarkingvarunkohliinNo ratings yet

- Mighty Press Hat PressDocument9 pagesMighty Press Hat PressJudy NeenaNo ratings yet

- Features: Surface Mount Fast Switching DiodeDocument4 pagesFeatures: Surface Mount Fast Switching DiodeDe faNo ratings yet

- Slag Attack Mag CarbDocument12 pagesSlag Attack Mag CarbAnindya RoyNo ratings yet

- 2052Document15 pages2052electroramos2011No ratings yet

- ABB's Comprehensive Range of LV Control ProductsDocument79 pagesABB's Comprehensive Range of LV Control Productsfairoos aliNo ratings yet