Professional Documents

Culture Documents

8 Bit Microcontroller Description

Uploaded by

phantom_nc91Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

8 Bit Microcontroller Description

Uploaded by

phantom_nc91Copyright:

Available Formats

ECE410 Design Project Spring 2013 Design and Characterization of a CMOS 8-bit pipelined Microprocessor Data Path

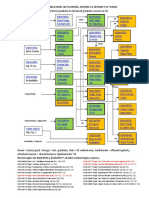

Project Summary This project involves the schematic and layout design of an 8-bit microprocessor data path, including an ALU, barrel shifter, and a register file using CMOS circuitry and Cadence VLSI design tools. The project will incorporate all the skills and knowledge students have gained from the individual lab assignments and provide a team of students with an opportunity to work on a more open-ended integrated circuits design problem. Data Path Overview The data path is the core element of a microprocessor that can perform many functions, including arithmetic and logic evaluation, data movement, and storage of results in a memory address specified by the instruction. In this design project, teams must design a complete 8-bit data path consisting of a register file, an ALU (arithmetic logic unit), shifter, memory unit, and program counter as shown in Figure 1. The data path will be capable of multiple instructions determined by several signals that comprise the operational code or opcode. The data path is pipelined, or broken into stages. Each stage is separated by a register (pipeline registers) containing all the signals required for operation. The pipeline registers provide latching for the signals between clock cycles.

Figure 1: Structure of the microprocessor data path [1]

[1] Patterson, David A., and John L. Hennessy. Computer organization and design: the hardware/software interface. Morgan Kaufmann, 2008.

The ALU can perform both arithmetic and bit-wise logical operations. The ALU will have two 8-bit data inputs and several control signals that specify the ALU function to be executed in a given clock cycle. The ALU input data is loaded from the pipeline register at the rising edge of the clock, and the output is generated after a delay due to propagation through the combinational logic of the ALU and the shifter. The central component of an ALU is an adder, and for this project a Manchester carry look-ahead adder will be used. The shifter provides data manipulation capabilities. In Lab 6, a simple shift register that can shift by one position per clock cycle was built. In this design project, a barrel shifter will be used because it has a very efficient layout and can perform n-bit shifts in a single clock cycle. A MUX is used to select the correct out from the ALU or the shifter. The output of the MUX goes to the input of the next pipeline register. The register file is a block of memory that provides the data inputs to and stores the ouputs from the ALU. The register file at read/write address is specified by bits included in the opcode. In this project, pipeline registers will be synchronized by a single clock that determines when new data is available to the register file and the ALU/shifter. Data Path The following specifications must be achieved by the data path you design Data width: 8-bits Inputs: 16-bit instructions from Instruction Memory 8-bit data from Data Memory Outputs: 8-bit program counter 8-bit address for Data memory 8-bit data to write to Data memory 1-bit Data memory write signal 1-bit Data memory read signal Power supply: VDD = 3V, GND = 0V Size specifications: No specific layout size is required, but optimization of physical size is a design priority, and higher scores will be awarded to groups with smaller layouts. The floorplan in Figure 2 will assist in achieving an optimal layout. Timing specifications: Singal timing requirements are defined below. The worst case propagation delay for all ALU+shifter functions must be less than 50ns. Instruction Set: All of the following instructions must be implemented The instruction set encoding is as follows:

oooo BLTZ BGEZ BEQ BNE BLEZ BGTZ ADDI SLTI ANDI ORI XORI LUI LW SW 1000 1000 1010 1010 1011 1011 1100 1100 1101 1101 1110 1110 1111 1111

I-Type instructions ---------------------------------------------------osss ttti iiii ---------------------------------------------------0sss 000i iiii Branch on Less than Zero

Branch on Greater Than or Equal

001i iiii Zero ttti iiii Branch on Equal ttti iiii Branch on Not Equal 000i iiii Branch on Less than or Equal Zero 000i iiii Branch on Greater than Zero ttti iiii ADD immediate ttti iiii Set on Less than Immediate ttti iiii AND immediate ttti iiii OR immediate ttti iiii XOR immediate ttti iiii Load Upper Immediate ttti iiii Load Word ttti iiii Store Word J-Type instructions ---------------------------------------------------oiii iiii iiii ---------------------------------------------------0iii iiii iiii Jump 1iii iiii iiii Jump and Link R-Type instructions ---------------------------------------------------osss tttd ddhh ---------------------------------------------------1--tttd ddhh Shift Left Logical 0--tttd ddhh Shift Right Logical 1--tttd ddhh Shift Right Arithmetic 0sss tttd dd00 Shift Left Logical Variable 1sss tttd dd00 Shift Right Logical Variable 0sss tttd dd00 Shift Right Arithmetic Variable 1sss 0000 0000 Jump Register 0sss 000d dd00 Jump and Link Register 1sss tttd dd00 NOR 0sss tttd dd00 ADD 1sss tttd dd00 SUB 1sss 0sss 1sss 0sss 1sss 0sss 1sss 0sss 1sss 0sss 1--0sss 1sss

oooo J JAL 1001 1001

oooo SLL SRL SRA SLLV SRLV SRAV JR JALR NOR ADD SUB 0000 0001 0001 0010 0010 0011 0011 0100 0100 0101 0101

AND OR XOR SLT NOOP

0110 0110 0111 0111 0000

0sss tttd dd00 AND 1sss tttd dd00 OR 0sss tttd dd00 XOR 1sss tttd dd00 Set on Less than ---------------------------------------------------0000 0000 0000

Table 1: ISA encoding s A 3-bit source register t A 3-bit source/destination register d A 3-bit destination register i A 5-bit immediate value, or a 11-bit immediate value h A 2-bit shift amount value Control Signals: 18 internal control signals will be generated from the 16-bit input instruction. They are as follows. NOTE: These are the primary control signals. You may decode and manipulate them as needed as secondary internal control signals. The truth table can be seen in Table 2. o SO Shift unit operation code (2-bits) o V asserted when instruction is a variable shift (1-bit) o MO math unit operation code (3-bits) o I invert second operand (1-bit) o M2 select source for second operand (2-bit) o F1 asserted when rs field identifies a source operand (1-bit) o F2 asserted when rt field identifies a source operand (1-bit) o MR asserted when instruction reads from the data Memory Unit (1bit) o MW asserted when instruction writes into the data memory Unit (1bit) o RW asserted when instruction writes into Register Unit (1-bit) o DR select destination register number (2-bit) o DO select operand to be written (2-bit) The truth table for the control signals is as follows:

Instr SLL SRL SRA SLLV SRLV Shift SO V 00 0 10 0 11 0 00 1 10 1 Math MO I XXX X XXX X XXX X XXX X XXX X M2 XX XX XX XX XX F1 F2 0 1 0 1 0 1 1 1 1 1 General MR MW RW 0 0 1 0 0 1 0 0 1 0 0 1 0 0 1 DR DO 10 10 10 10 10 10 10 10 10 10

SRAV JR JALR ADD SUB AND OR XOR NOR SLT ADDI SLTI ANDI ORI XORI LUI LW SW BLTZ BGEZ BEQ BNE BLEZ BGTZ J JAL

11 XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX

1 X X X X X X X X X X X X X X X X X X X X X X X X X

XXX XXX XXX 000 000 100 101 110 111 010 000 010 100 101 110 101 000 000 XXX XXX 000 000 000 000 XXX XXX

X X X 0 1 X X X X 1 0 1 X X X X 0 0 X X 1 1 1 1 X X

XX XX XX 00 00 00 00 00 00 00 01 01 10 10 10 11 01 01 XX XX 00 00 00 00 XX XX

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0

1 0 0 1 1 1 1 1 1 1 0 0 0 0 0 0 0 1 0 0 1 1 1 1 0 0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0

1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 1

10 XX 10 10 10 10 10 10 10 10 00 00 00 00 00 00 00 XX XX XX XX XX XX XX XX 01

10 XX 11 01 01 01 01 01 01 01 01 01 01 01 01 01 00 XX XX XX XX XX XX XX XX 11

Table 2: Truth table for control signals Data Path Layout The 8-bit datapath can be implemented by constructing a 1-bit slice horizontally and stacking 8 1-bit slices vertically. This layout floorplan for the data path is shown in Figure 2. The data flows horizontally from left to right. The control signals run vertically across each slice. You may implement some functional blocks as 8-bits, but make sure you organize it in 1-bit slices that can be pitch-matched to the other functional blocks.

Address ALU Op Shift Op

MUX MUX

Register Register

Pipeline Register Pipeline Register

ALU ALU

Shifter Shifter

Pipeline Register Pipeline Register

MUX

Register

.. Pipeline ALU Register

Shifter

Pipeline Register

Figure 2: Floorplan of the data path Register File Description The 8-bit register file should be implemented as an 9x8 SRAM. The first 8 registers are user available registers and the last and final register is a special register for Jump and Link instructions You should implement a precharge and a sense amplifier with the SRAM blocks. The register file should have two 8-bit read (output) ports and one 8bit write (input) port. Input to the register file can come either from the ALU output from the data memory. The register file uses an enable signal for the general task of enabling inputs to and outputs from the register file at the proper time. The register file must be carefully designed to properly implement the enable function. In the read cycle, register file output is passed to the pipeline register when enable is high; otherwise the output should be at high impedance, and goes to the ALU on the next clock cycle. The output should also be at high impedance during the entire write cycle, when the R/W signal is high. In the write cycle, data is stored in the SRAM only when enable is high; otherwise the data from the pipeline register should not be allowed to affect the SRAM register file. To accomplish this, the enable signal should act on the SRAM address decoder outputs. The register file address actually contains two independent 3-bit addresses. Address A should specify the address for data passed to the ALU input A, the address B should specify ALU input B. Address A is also used to specify the address for storing data to the SRAM during a write cycle. Pipeline Registers Four pipeline registers are needed for the different stages and can be seen in Figure 1. These pipeline registers should be clocked by the master clock. On the rising edge of the master clock the registers should latch on to the output from the previous stage and hold it constant for the next stage. Parallel load D-flip flop registers should be used for these pipeline registers. Clock/Timing Description One master clock is required for the data path. On each rising clock edge the register pipelines latch on to the result of the previous stage. This result is then held in the register for the next stage of the pipeline. This provides a latching effect allowing the combinatorial circuits to perform their operations. The clock frequency should be chosen

such that the worst case operation across all pipeline stages has time to complete. For example, say the worst case operation is the write to SRAM, then the clock frequency should be chosen such that it is greater than the propagation delay of the SRAM write operation. Project Requirements The following cell views for all circuit blocks must be created using Cadence tools and stored in your group project directory: Schematic Symbol Layout Extraction The complete data path cell must pass the following tests and verifications: Functional simulation of all data path functions DRC LVS Input and output signals must be named as follows: Inputs Outputs The following characteristics must be measured and reported: Slowest logic function and propagation delay for that function (ALU) Slowest arithmetic function and propagation delay for that function (ALU) Slowest propagation delay of the data path (ALU+Shifter) (Propagation delays are to be measured from the clock edge to the last output transition) Physical area of the complete data path layout Total number of transistors in the data path (available from the final LVS output) Total, static and dynamic power consumption for a full read and write cycle during an ADD and Shift_Left 2 operation. Circuit Requirements A Manchester carry look-ahead adder must be implemented A barrel shifter must be implemented The register file must be implemented with a multi-port 8x8 SRAM The pipeline registers must be implemented with parallel load DFFR registers Minimum sized transistors can be used, but are not required When possible, existing primitive cells (INV,NAND, etc.) should be used to construct circuit blocks. Any new primitive cells (such as the carry generation circuits and control logic) must be designed at the transistor level. All required functions must be implemented using only the specified control/select

inputs. You must employ hierarchical design where you instantiate lower level cells into higher level circuit block, both in schematic and layout design Buffers should be designed and included wherever fan-out is larger than 5 gates.

Layout Requirements Follow all previously established layout guidelines for cell size (pitch), internal routing, input/output pad placement, etc. All designed circuit schematics must be laid out, must pass DRC, and must pass LVS. All functional blocks should be designed using only metal 1 and metal 2, reserving metal 3 for routing chip-level control and data signals in the top level of hierarchy. All cell I/O signals and power traces must be connected to single points in the final cell. i.e., you cannot have multiple ports for VDD, GND, or any I/O signal. Attempt to consistently route metal 1 and metal 2 in perpendicular directions. You may need to twist cells around and stack them in seemingly odd ways to achieve your goals, but always make sure you have good power supply to all cells and that you have good access to run metal 2 and metal 3 in a single direction in your final data path cell. Project Planning and Considerations Your group should decide during the proposal stage exactly what cells you will need to complete your project. Although you can alter this plan slightly if necessary, you should identify early on what functions you will construct at the 1bit level, at the 4-bit level, and at the full 8-bit level. Your group must decide which tasks of this design project will be completed for each design phase (Labs 8-10). Since layout and final simulation/characterization take much more time than schematic capture and functional simulation, you must get beyond the schematic stage by Lab 9. It is always best to pass DRC and LVS on smaller cells BEFORE using them to construct larger cells. Final LVS can be very time consuming for many groups. Deliverables: All schematic and layout cells required to construct the data path must be within th group directory. Simulations should be performed to verify ALL data path functions, several of which will be tested during the project demonstration. In addition, the following must be provided within the final project report:

Data Path

1 2

Select schematics that demonstrate your design effort Final data path schematic and symbol

3 4 5 6 7 8

Truth table of control inputs and ALU/shifter functions Functional simulations, including loading data from memory, perform XOR, A+B, and AB operations on the data, and saving the result to another register in the register file. Final data path layout and any smaller cell layouts that you feel you did an exceptional job optimizing Discussion of LVS process, what problems did you have, how did you solve them, etc. Post layout simulations showing propagation delays as specified above Table of cell specifications including -Measured cell width, height, and area, number of transistors, and total area/transistor -Measured performance characteristics (worst-case delays and power)

You might also like

- 10 1 1 297 8953Document7 pages10 1 1 297 8953phantom_nc91No ratings yet

- 10 1109-Iciprm 2001 929178Document2 pages10 1109-Iciprm 2001 929178phantom_nc91No ratings yet

- 05 01 26Document5 pages05 01 26phantom_nc91No ratings yet

- SimulinkDocument32 pagesSimulinkthomasNo ratings yet

- Shape Memory Alloy and Elastomer Composite MEMS ActuatorsDocument4 pagesShape Memory Alloy and Elastomer Composite MEMS ActuatorsmsmaheshNo ratings yet

- Robert D. White and Jason Rife : Frank Saunders, Ethan GoldenDocument8 pagesRobert D. White and Jason Rife : Frank Saunders, Ethan Goldenphantom_nc91No ratings yet

- Minchul Shin, Vincent P. Manno, Chris B. Rogers, Edward Paul, Mansour Moinpour, Donald Hooper, and Robert D. WhiteDocument6 pagesMinchul Shin, Vincent P. Manno, Chris B. Rogers, Edward Paul, Mansour Moinpour, Donald Hooper, and Robert D. Whitephantom_nc91No ratings yet

- ComsolDocument34 pagesComsoladnan_ais123100% (1)

- Silicon Germanium Epitaxy: A New Material For MEMS J.T. Borenstein, N.D. Gerrish, R. White, M.T. Currie and E.A. FitzgeraldDocument6 pagesSilicon Germanium Epitaxy: A New Material For MEMS J.T. Borenstein, N.D. Gerrish, R. White, M.T. Currie and E.A. Fitzgeraldphantom_nc91No ratings yet

- Stick-Slip Transitions in Chemical Mechanical Planarization: J. Vlahakis, V. P. Manno, C. B. Rogers, and R. WhiteDocument3 pagesStick-Slip Transitions in Chemical Mechanical Planarization: J. Vlahakis, V. P. Manno, C. B. Rogers, and R. Whitephantom_nc91No ratings yet

- An2124 PDFDocument12 pagesAn2124 PDFphantom_nc91No ratings yet

- MEMS Pressure Sensor Array for Low Frequency Aeroacoustic AnalysisDocument4 pagesMEMS Pressure Sensor Array for Low Frequency Aeroacoustic Analysisphantom_nc91No ratings yet

- Linear Algebra and Differential Equation, By: BakerDocument426 pagesLinear Algebra and Differential Equation, By: BakersaharNo ratings yet

- Jpeg PDFDocument18 pagesJpeg PDFphantom_nc91No ratings yet

- Stability Routh HorwitzDocument8 pagesStability Routh Horwitzphantom_nc91No ratings yet

- Metric SpacesDocument149 pagesMetric Spacesphantom_nc91100% (2)

- ElectronicDocument1 pageElectronicphantom_nc91No ratings yet

- A Complete Course in Power PointDocument18 pagesA Complete Course in Power Pointphantom_nc91No ratings yet

- A Complete Course in Power PointDocument18 pagesA Complete Course in Power Pointphantom_nc91No ratings yet

- A Complete Course in Power PointDocument18 pagesA Complete Course in Power Pointphantom_nc91No ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5784)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Ec2203-Digital Electronics Question BankDocument22 pagesEc2203-Digital Electronics Question BankRamadhuraiNo ratings yet

- Anti-VM Detection Techniques and Hooking MethodsDocument26 pagesAnti-VM Detection Techniques and Hooking MethodsAnonymous LegionsNo ratings yet

- 10 Total Mark: 10 X 1 10: NPTEL Online Certification Courses Indian Institute of Technology KharagpurDocument7 pages10 Total Mark: 10 X 1 10: NPTEL Online Certification Courses Indian Institute of Technology KharagpurvitNo ratings yet

- Recent Topics For ELEN E6713, ELEN E677, & Other Related Topics CoursesDocument1 pageRecent Topics For ELEN E6713, ELEN E677, & Other Related Topics CoursesMangaka DomingosNo ratings yet

- IT AUDIT - Computer OperationsDocument45 pagesIT AUDIT - Computer Operationssax_worship0% (1)

- Vacon NXN Nfe User Manual Dpd01172a enDocument50 pagesVacon NXN Nfe User Manual Dpd01172a enTanuTiganuNo ratings yet

- Practical 9Document2 pagesPractical 9swapnil kaleNo ratings yet

- PSP EclipseDocument22 pagesPSP EclipseraphaelgtorresNo ratings yet

- Diagnostics Agent Troubleshooting PDFDocument36 pagesDiagnostics Agent Troubleshooting PDFAnkitSharmaNo ratings yet

- 55X8817 PC Convertable Technical Reference Volume 2 Feb86Document275 pages55X8817 PC Convertable Technical Reference Volume 2 Feb86kgrhoadsNo ratings yet

- InPage 2009 Professional Uninstall LogDocument13 pagesInPage 2009 Professional Uninstall LogsolypkNo ratings yet

- AZ-900 Microsoft Azure Fundamentals TitleDocument8 pagesAZ-900 Microsoft Azure Fundamentals Titlenagendra reddy panyamNo ratings yet

- FortiAnalyzer 6.0 Lab Guide-OnlineDocument85 pagesFortiAnalyzer 6.0 Lab Guide-OnlineКалоян ПетровNo ratings yet

- Important OOPs NotesDocument20 pagesImportant OOPs Notesrehan raoNo ratings yet

- CramPDF - Leading Exam Cram PDF ProviderDocument12 pagesCramPDF - Leading Exam Cram PDF ProviderratneshkumargNo ratings yet

- Internet of Things (Iot) /cloud Computing: Prameet P. PatilDocument6 pagesInternet of Things (Iot) /cloud Computing: Prameet P. PatilPrameet P PatilNo ratings yet

- ARM Mali™-450 MP: Next Generation Graphics Performance For Smart-TV and Smartphone Applications Taipei Multimedia SeminarDocument21 pagesARM Mali™-450 MP: Next Generation Graphics Performance For Smart-TV and Smartphone Applications Taipei Multimedia Seminaruclidesxpolloxx2No ratings yet

- Asus p5b - Bupdater Bios Upgrade ProcedureDocument4 pagesAsus p5b - Bupdater Bios Upgrade ProcedureSalvatore BonaffinoNo ratings yet

- Red Faction READMEDocument16 pagesRed Faction READMEjuttyNo ratings yet

- Edumips64 1.2.5 Manual enDocument39 pagesEdumips64 1.2.5 Manual enSdsaaNo ratings yet

- UntitledDocument12 pagesUntitledYudhik MarmerNo ratings yet

- 181389-1CD Ethernet Logix YRC1000Document30 pages181389-1CD Ethernet Logix YRC1000Daniel FloresNo ratings yet

- Introduction to SIWES and KAEDCODocument13 pagesIntroduction to SIWES and KAEDCOSamuel Geoffry100% (1)

- UdbsqlrefDocument1,050 pagesUdbsqlrefvangappan2No ratings yet

- PID Controller for a Self-balancing Pole Using Angle Sensor and MicroprocessorDocument9 pagesPID Controller for a Self-balancing Pole Using Angle Sensor and MicroprocessorDino Ligutan100% (2)

- Router eSIM v1 FaqDocument13 pagesRouter eSIM v1 FaqIlias AhmedNo ratings yet

- AOP methodology improves event management system designDocument11 pagesAOP methodology improves event management system designRatan DeepNo ratings yet

- Top 5 Cool Notepad TricksDocument10 pagesTop 5 Cool Notepad TricksJeeva SuriyanNo ratings yet

- IP Configuration Questions for Network Technician ExamDocument18 pagesIP Configuration Questions for Network Technician ExamИлиян БързановNo ratings yet

- OneDrive Log File Entries from December 1 2021Document69 pagesOneDrive Log File Entries from December 1 2021Valdemar Souza WeckNo ratings yet