Professional Documents

Culture Documents

TP Fpga

Uploaded by

kfawaz0 ratings0% found this document useful (0 votes)

666 views22 pagesOriginal Title

TP-FPGA

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

666 views22 pagesTP Fpga

Uploaded by

kfawazCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 22

Institut Universitaire de Technologie de CRETEIL-VITRY

Dpartement de Gnie lectrique et Informatique Industrielle

MC-ENSL1 - Composants programmables complexes

COURS / TP

FPGA

Anne universitaire 2012-2013

J. VILLEMEJANE - julien.villemejane@u-pec.fr

IUT Crteil - GEII - MC-ENSL1 - Composants programmables complexes COURS / TP

Consignes

Faites valider le code par lenseignant avant la programmation de la carte

Faites valider chacun des exercices par lenseignant

Il vous est conseill de faire un compte-rendu de chacun des TP

Rpartition des sances

Sance 1 (cours/TP) : Introduction (TP0 et TP1)

Sance 2 (cours/TP) : Structuration-Simulation (TP2)

Sance 3 (TP) : Structuration-Simulation (TP2)

Sances 4 et 5 : Achage multiplex (TP3)

Sance 6 : TP Test 1

Sances 7 9 : Projet

Sance 10 : TP Test 2

Table des matires

TP0 - Systmes logiques programmables 4

TP1 - Dveloppement dun systme numrique 10

TP2 - Structuration et simulation 16

TP3 - Achage multiplex 20

3

GEII - MC-ENSL1 TP 0

Systmes logiques programmables

Objectifs

Dcouvrir larchitecture des FPGA.

Dcouvrir la carte dtude BASYS de Digilent.

Dans le domaine des systmes numriques, il existe deux grandes sortes de composants :

les processeurs (et drivs : microcontroleurs, DSP...) qui font du traitement squentiel

les composants programmables qui font du traitement parallle

Il existe trois grandes catgories de systmes logiques programmables :

les CPLD (Complex Programmable Logic Device)

les FPGA (Field Programmable Gate Array)

les ASIC (Application Specic Integrated Circuit)

Les CPLD sont de conception plus anciennes et ont gnralement des capacits moindres que les FPGA. Cependant,

ils sont encore largement utiliss dans des systmes logiques (combinatoire ou squentiels).

Dans les deux cas, ce sont des rseaux logiques programmables composs de nombreuses cellules logiques l-

mentaires librement assemblables. Nous allons ici tudier plus en dtails les FPGA, les CPLD ayant dj t abords en

premire anne (module ENSL1).

IUT Crteil - GEII - MC-ENSL1 - Composants programmables complexes COURS / TP

1. Les FPGA

Ces systmes programmables sont initialement destins au prototypage de systmes numriques complexes. Ils

sont une bonne alternative aux circuits spciques, les ASIC (Application Specic Integrated Circuit), pour des petites ou

moyennes sries.

Il existe plusieurs grands fabricants : ALTERA, ACTEL (composants spcialiss) et XILINX. Pour les TP, nous

utiliserons des FPGA de chez Xilinx.

1.1. Implantation

Chaque fabricant propose aussi des composants de taille variable : de 100.000 10.000.000 portes logiques. Par

comparaison, les portes standards commerciales possdent entre 2 et 8 portes logiques pour une surface de silicium

quasiment identique.

Quelque soit la technologie utilise, aucune porte logique nest rellement implante. Il sagit en fait de blocs

logiques programmables, mais trs versatiles (RAM), et dune mer de connexions programmables. Chez Xilinx, ces

blocs logiques sont appels CLB (Common Logic Blocks).

1.2. Avantages et inconvnients

Trs haute densit

Grande vitesse (100 MHz quelques GHz)

Trs grand nombre dentres/sorties (botiers BGA)

Prix lev (mais en baisse)

Alimentation dicile (plusieurs tensions, courants levs, connexions multiples)

Volatiles (cellules RAM)

Circuits imprims (PCB - Printed Circuit Board) multicouches

2. Structure dun FPGA - Xilinx

Larchitecture, retenue par Xilinx, se prsente sous forme de deux couches : une couche circuit congurable et un

rseau de mmoire SRAM. La structure dun FPGA est donne dans la gure suivante. Lchelle est loin dtre relle,

les fonctions logiques noccupant quenviron 5% du circuit.

Figure 1 Structure dun FPGA

Les FPGA sont un rassemblement et une combinaison de dirents blocs : dentres/sorties (IOB - Input Output

Blocks), de routage (PSM - Programmable Switch Matrix), de logique programmable (CLB - Congurable Logic

5

IUT Crteil - GEII - MC-ENSL1 - Composants programmables complexes COURS / TP

Blocks) et dautres blocs plus spciques.

2.1. Spartan XL 3E

Les Spartan 3E, que nous allons utiliser par la suite, sont bass sur ce type de structure. La gure suivante dtaille leur

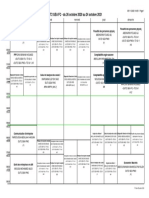

architecture. Le tableau rassemble les direntes caractristiques de cette famille de FPGA.

Figure 2 Structure et caractristiques des Spartan 3 - Xilinx

Les CLB (voir gure 3) sont dcomposs en 2 ou 4 SLICE (appellation de Xilinx). Ces SLICE sont eux-mmes

dcomposs en 2 LUT (Look-Up Table) et 2 bascules D.

Figure 3 Bloc logique congurable - Xilinx Spartan 3

6

IUT Crteil - GEII - MC-ENSL1 - Composants programmables complexes COURS / TP

2.2. LUT et bascule

Les fonctions combinatoires sont implantes sur des mmoires SRAM (LUT = Look-Up Table). La table de vrit

est alors charge dans ces LUT. La gure 4 montre le cas de LUT 2 entres. En gnral, les FPGA sont quips de LUT

4 ou 6 entres.

Figure 4 LUT - Xilinx Spartan 3

Les lments squentiels (synchrones sur front ou niveau) sont implants sur des bascules (D le plus frquemment).

3. Carte dtude BASYS2 - Digilent

Lensemble des exemples et applications qui seront demands dans ces TP seront raliss sur une carte de dveloppe-

ment BASYS2, propos par la socit Digilent. Ces cartes sont bases sur le FPGA Spartan 3E-250 de Xilinx.

Figure 5 Carte BASYS2 - Digilent

3.1. Entres-sorties logiques

Les entres logiques sont essentiellement ralises par 8 interrupteurs dnomms SW0 SW7 et par 4 boutons-

poussoirs dnomms BTN0 BTN3.

Les sorties pourront tre visualises sur 8 diodes lectroluminescentes (LD0 LD7) ou bien 4 acheurs 7 segments

multiplexs (DISP1).

7

IUT Crteil - GEII - MC-ENSL1 - Composants programmables complexes COURS / TP

lment broche lment broche lment broche lment broche

SW7 N3 LD7 G1 BTN3 A7 RED0 C14

SW6 E2 LD6 P4 BTN2 M4 RED1 D13

SW5 F3 LD5 N4 BTN1 C11 RED2 F13

SW4 G3 LD4 N5 BTN0 G12 BLU1 H13

SW3 B4 LD3 P6 MCLK B8 BLU2 J13

SW2 K3 LD2 P7 GRN0 F14

SW1 L3 LD1 M11 HS J14 GRN1 G13

SW0 P11 LD0 M5 VS K13 GRN2 G14

3.2. Horloges

Il y a trois horloges de caractristiques direntes produites par un circuit spcial : 25, 50 et 100 MHz.

Ces trois signaux sont connects la mme broche spcique du FPGA.

3.3. Acheurs 7 segments multiplexs

Le multiplexage de lachage permet de limiter le nombre de connexions

pour ces 4 acheurs. Mais son fonctionnement exige la mise en uvre

de composants squentiels.

Pour activer un segment (cathode), on doit placer un 0 (zro) sur

la sortie correspondant au segment seg. Pour activer un acheur, il faut

galement placer un 0 sur la sortie an dsire, (en raison de la prsence

dun transistor amplicateur inverseur).

a...g, dp = cathodes des segments et du point dcimal de tous les

acheurs ; an = commandes des anodes communes des acheurs.

lment broche type

an(0) F12 commande anode gauche

an(1) J12 commande anode

an(2) K14 commande anode

an(3) M13 commande anode droite

lment broche type

A, seg(6) L14 sortie

B, seg(5) H12 sortie

C, seg(4) N14 sortie

D, seg(3) N11 sortie

E, seg(2) P12 sortie

F, seg(1) L13 sortie

G, seg(0) M12 sortie

DP N13 sortie

3.4. Description en VHDL

Pour dcrire les dirents systmes numriques, nous utiliserons le logiciel de chez Xilinx : ISE Webpack (version

10.5). Cette version est disponible gratuitement, moyennant une inscription, sur le site de xilinx (www.xilinx.com).

Ce logiciel permet de dcrire des systmes en VHDL ou Verilog, de les tester (de manire fonctionnelle ou temporelle)

et de crer un chier binaire compatible avec la cible (ici un FPGA Spartan 3E). Les tapes de dveloppement seront

dcrites par la suite.

3.5. Contraintes

Il ne faut pas oublier dassigner les entres/sorties de votre systme aux broches relles du systme. Le systme nal

tant dj cbl, ces contraintes sont dj prdnies (voir tableaux prcdent - 7 segments - et suivant).

3.6. Implmentation du programme

Une fois que toutes les tapes de compilation sont russies, un chier binaire *.bit est gnr et peut alors tre

implant dans le FPGA.

Pour cela, il est ncessaire de relier la carte sur un des ports USB de lordinateur et dallumer la carte dtude (inter-

rupteur le plus gauche - SW8).

8

IUT Crteil - GEII - MC-ENSL1 - Composants programmables complexes COURS / TP

Lutilitaire Adept (Digilent) sera alors utiliser pour transfrer le chier binaire vers le FPGA.

9

GEII - MC-ENSL1 TP 1

Dveloppement dun systme numrique

Objectifs

Dvelopper des systmes numriques programmables simples (multiplexeur, compteur...).

Simuler un systme numrique.

Il existe 2 langages de description pour les FPGA :

VHDL : Very High Speed integrated circuit Hardware Description Language ;

Verilog.

Nous nous intresserons par la suite au VHDL, qui est un langage de description normalis (IEEE) et quasi-universel

pour dcrire des circuits intgrs.

1. Structure dun projet

Figure 6 Structure dun projet

Un projet VHDL est trs souvent dcompos en sous-structures,

appeles modules ou composants. Comme on pourrait le faire sur

un circuit imprim, il sagit dinstancier dirents composants et

de les relier entre eux par des ls (signaux en VHDL) pour raliser

le systme complet.

Chacun de ces modules est alors dcrit dans un chier source

indpendant. Chacun de ces chiers sources peut alors tre test

indpendamment en lui associant un chier de simulation (ou test-

bench).

Enn des chiers de contraintes permettent de faire le lien

entre la description logicielle et la structure matrielle de la cible

et de son environnement (position des entres, des sorties...).

2. Phases de dveloppement

IUT Crteil - GEII - MC-ENSL1 - Composants programmables complexes COURS / TP

Lcriture des dirents modules (ou composants) est la premire chose raliser. Ceux-ci peuvent tre dcrits et

tests sparment. Nous verrons par la suite comment dcrire un composant.

Ensuite, il est possible (et fortement conseill) de vrier la syntaxe de la description, en faisant appel la fonction

"Check Syntax" dans la partie "Synthetize XST". Cette tape est assez rapide et ne ncessite pas de connatre la cible,

contrairement ltape daprs.

Viens ensuite la phase de synthse ("Synthetize XST") puis de placement et de routage ("Implement Design"). Ces

tapes ncessitent la connaissance, dune part, de la cible (FPGA ou CPLD) et, dautre part, de lenvironnement du circuit

(entres/sorties associes aux autres composants de la maquette). Il est donc ncessaire, avant de raliser ces tapes-l,

de faire lassignation des broches du composant avec la description fournie. Pour cela, vous pouvez vous aider de la

fonction "Assign Package Pins" dans la partie "User Constraints" et de la documentation de la maquette fournie en dbut

de ce document.

Il est aussi possible ce stade de lancer direntes simulations :

fonctionnelle : permettant de savoir si le fonctionnement du systme est celui dcrit ;

post-synthse : permettant, aprs synthse, de vrier nouveau le fonctionnement du systme ;

temporelle : permettant, aprs ltape de routage, de valider les contraintes temporelles associes au placement des

"composants".

Ces direntes phases doivent tre rptes pour lensemble des modules composant lapplication. La dernire tape

consiste produire le chier de programmation ("Generate Programming File") et le transfrer dans la mmoire du

FPGA.

3. Structure dun module VHDL

La description dun systme numrique par le biais du langage VHDL passe par 3 tapes direntes :

la dclaration des ressources externes (bibliothques) ;

la description de lentit du systme, correspondant la liste des entres/sorties ;

la description de larchitecture du systme, correspondant la dnition des fonctionnalits du systme.

Lensemble est contenu dans un chier source portant lextension *.vhd.

3.1. Dclaration des ressources externes

Cette phase est ralise automatiquement pour les bibliothques courantes. On retrouve en en-tte du chier source

*.vhd les instructions suivantes :

1 l i br ar y IEEE ;

2 use IEEE . STD_LOGIC_1164 . ALL;

3 use IEEE . STD_LOGIC_ARITH. ALL;

4 use IEEE . STD_LOGIC_UNSIGNED. ALL;

11

IUT Crteil - GEII - MC-ENSL1 - Composants programmables complexes COURS / TP

3.2. Entit

Lentit permet de spcier les dirents ports dentres/sorties du systme. Pour

chacun dentre eux, il est indispensable de donner sa direction :

in entre simple

out sortie simple

buer sortie rtroactive

inout entre-sortie bidirectionnelle (conits possibles)

et son type (voir section suivante).

1 e nt i t y c our s i s

2 port (

3 a , b : i n STD_LOGIC; comment ai r e

4 s : out STD_LOGIC

5 ) ;

6 end c our s ;

3.3. Architecture

Une architecture est relie une entit et permet de dcrire le fonctionnement du systme. Cette description peut

tre de deux types :

description comportementale : le comportement du systme est dcrit (description la plus couramment utilise en

VHDL) ;

description structurelle : la structure meme du systme est dcrite base de portes logiques, bascules... (description

rserve des fonctions simples ou pr-calcules).

1 a r c hi t e c t ur e Be ha vor i a l of c our s i s

2 d e c l a r a t i o n des s i gna ux

3 begi n

4 pr oc e s s us 1 ;

5 pr oc e s s us 2 ;

6 . . .

7 end Be ha vor i a l ;

4. Objets et types en VHDL

4.1. Objets

signal objet physique, associ des vnements

variable intermdiaire de calcul, non physique

constant

4.2. Types

Types de base : bit, bit_vector, integer, boolean

Types IEEE : std_logic, std_logic_vector, signed, unsigned

Types dnis par lutilisateur :

- type numr, exemple : type jour is (lu, ma, me, je, ve, sa, di); (souvent utilis dans les ma-

chines tat)

- sous-type : subtype octet is bit_vector(0 to 7);

4.3. Notations

bit : 0 ou 1 ; bit_vector : "0100" ; ASCII : "Texte" ; Dcimal : 423 ; Hexadcimal : x"1A"

4.4. Oprateurs en VHDL

12

IUT Crteil - GEII - MC-ENSL1 - Composants programmables complexes COURS / TP

LOGIQUES : and, nand, or, nor, xor, xnor, not

DCALAGE : sll, slr, sla, sra, rol, ror

RELATIONNELS : =, /=, <, >, <=, >=

ARITHMTIQUES : +, -, *, /, MOD

CONCATENATION : &

AFFECTATION : <=

5. Instructions en VHDL

5.1. Hors processus

Ces instructions dcrivent le plus souvent des lments combinatoires (concurrentes).

5.1.1 Aectation conditionnelle

1 x <= a when cond1 e l s e

2 b when cond2 e l s e

3 . . .

4 z ;

5.1.2 Aectation slective

1 wi t h expr s e l e c t

2 x <= a when val 1 ,

3 b when val 2 ,

4 . . .

5 z when ot he rs ;

5.1.3 For... generate

1 f or i i n MIN t o MAX generat e

2 i n s t r u c t i o n s de d e s c r i p t i o n ;

3 end generat e ;

5.2. Dans un processus

Lexcution des instructions seectue dans un ordre squentiel (ordre dcriture). Le processus est activ lorsquun

des lments de la liste de sensibilit est modi.

La mise jour des objets seectue simultanment la n du processus.

5.2.1 Syntaxe

Label : process(liste des signaux de sensibilit)

Nom des objets internes : types ; si ncessaire

begin

...

end process;

13

IUT Crteil - GEII - MC-ENSL1 - Composants programmables complexes COURS / TP

5.2.2 Test : SI

1 i f x=" 00 " t hen

2 y <= 0 ;

3 e l s i f x=" 01 " t hen

4 y <= 1 ;

5 end i f ;

5.2.3 Test : CAS

1 cas e x i s

2 when " 00 " => y <= " 00 " ;

3 when " 01 " => y <= " 10 " ;

4 when ot he rs => y <= " 11 " ;

5 end cas e ;

5.2.4 Blocs rptitifs

1 f or i i n 0 t o 5 l oop

2 i n s t r u c t i o n s ;

3 end l oop ;

1 whi l e i < 5 l oop

2 i n s t r u c t i o n s ;

3 end l oop ;

5.2.5 Temporisation

1 wai t u nt i l CLK e ve nt and CLK= 1 ;

2 i n s t r u c t i o n s ;

6. Tournures frquentes en VHDL

6.1. Dtection dun front

1 i f cl k e ve nt and c l k =1 t hen . . . ; f r o n t mont ant

2 i f cl k e ve nt and c l k =0 t hen . . . ; f r o n t de s c e nda nt

6.2. Remplissage dun vecteur (bit_vector)

1 x <= ( ot he rs => 0 ) ; t ous l e s b i t s a 0

2 x <= ( ot he rs => 1 ) ; t ous l e s b i t s a 1

14

IUT Crteil - GEII - MC-ENSL1 - Composants programmables complexes COURS / TP

7. Prise en main de la maquette

On se propose ici de reprendre en main le logiciel Xilinx ISE Webpack. Pour cela, ils vous est demand de raliser

les systmes suivants.

EXERCICE 1

Dcrire un systme logique en VHDL dont le fonctionnement est donn par lquation :

s = a + a + b.

a et b seront des interrupteurs et s une LED.

EXERCICE 2

1. Dcrire un multiplexeur 4 vers 1 avec une entre de validation.

2. Dcrire un dmultiplexeur 1 vers 4.

Les entres seront ralises par des interrupteurs et les sorties par des LEDs.

EXERCICE 3

Raliser un compteur 4 bits.

Lhorloge sera ralise laide dun bouton poussoir et les sorties seront visualises sur des

LEDs.

Attention : pour les versions suprieures 10.1 de Xilinx ISE, an de pouvoir gnrer le chier de programma-

tion correctement, vous devrez ajouter la ligne : NET "clk" CLOCK_DEDICATED_ROUTE = FALSE; dans le chier de

contraintes (*.ucf).

15

GEII - MC-ENSL1 TP 2

Structuration et simulation

Objectifs

Structurer un systme en bloc fonctionnel (instanciation de composants).

Simuler des systmes numriques simples avec Xilinx ISE.

1. Structuration et instanciation de composants

An de simplier la description dun systme numrique, les concepteurs dcoupent leurs applications en sous-blocs

fonctionnels dcrivant une partie de cette dernire. En VHDL, ces sous-blocs sont appels modules ou composants.

Il est alors plus simple de dcrire et de tester chacun de ces modules sparment pour pouvoir les regrouper par la suite

dans un seul systme. A limage dun catalogue de composants et dun circuit imprim, il sera alors possible dinstancier

ces modules et de les relier entre eux par des signaux.

1.1. Dclaration dun composant

La dclaration pralable dun composant seectue soit dans un paquetage, soit dans la zone de dclaration dune

architecture.

1 component nom_e nt i t e

2 ge ne r i c ( param1 : i n t e g e r : = 3 ) ;

3 port ( e n t r e e : i n b i t ;

4 s o r t i e : out s t d _ l o g i c ) ;

5 end component ;

1.2. Structuration du systme

Chacun des modules doit tre dcrit dans un chier *.vhd spar, portant le nom de lentit quil dcrit. Il y aura

donc autant de chiers *.vhd que de types de composants.

EXERCICE 0

On souhaite raliser un additionneur de 3 nombres cods sur 4 bits : a, b et c ; laide

dadditionneurs 2 entres (4 bits).

1.2.1 Description du composant additionneur

Fichier additionneur.vhd

1 l i br ar y IEEE ;

2 use IEEE . STD_LOGIC_1164 . ALL;

3

4 e nt i t y a d d i t i o n n e u r i s

5 port ( a , b : i n STD_LOGIC_VECTOR( 3 DOWNTO 0 ) ;

6 s : out STD_LOGIC_VECTOR( 3 DOWNTO 0)

7 ) ;

8 end a d d i t i o n n e u r ;

9

10 a r c hi t e c t ur e s i mpl e of a d d i t i o n n e u r i s

11 d e c l a r a t i o n des s i gna ux s i be s oi n

12 begi n

13 p r o c e s s u s a e c r i r e

14 s <= a + b ;

15 end s i mpl e ;

IUT Crteil - GEII - MC-ENSL1 - Composants programmables complexes COURS / TP

1.2.2 Composants dclars dans la zone de dclaration de larchitecture

Fichier system.vhd

1 l i br ar y IEEE ;

2 use IEEE . STD_LOGIC_1164 . ALL;

3

4 e nt i t y s ys t em i s

5 Port (

6 a_sys , b_sys , c_s ys : i n STD_LOGIC_VECTOR( 3 DOWNTO 0 ) ;

7 s _s ys : out STD_LOGIC_VECTOR( 3 DOWNTO 0)

8 ) ;

9 end s ys t em ;

10

11 a r c hi t e c t ur e s i mpl e of s ys t em i s

12 component a d d i t i o n n e u r

13 port ( a , b : i n STD_LOGIC_VECTOR( 3 DOWNTO 0 ) ;

14 s : out STD_LOGIC_VECTOR( 3 DOWNTO 0)

15 ) ;

16 end component ;

17

18 s i g na l s _ s i g : STD_LOGIC_VECTOR( 3 DOWNTO 0 ) ;

19

20 begi n

21 add1 : a d d i t i o n n e u r

22 port map( a => a_sys , b => b_sys , s => s _ s i g ) ;

23 add2 : a d d i t i o n n e u r

24 port map( a => c_sys , b => s _s i g , s => s _s ys ) ;

25 end s i mpl e ;

1.3. Exercices

EXERCICE 1

1. Ralisez et testez un multiplexeur de 4 lignes (4 interrupteurs) vers 1 ligne, que vous

dcrirez dans un chier mux.vhd.

2. Ralisez et testez un dmultiplexeur 1 ligne vers 4 lignes, que vous dcrirez dans une

chier demux.vhd.

3. Assemblez ces deux chiers dans system.vhd an de simuler une ligne de trans-

mission srie ayant 4 interlocuteurs possibles de chaque cot.

La slection des voies du multiplexeur (AS) et la slection de la destination en sortie du

dmultiplexeur (AD) se feront par 2 x 2 interrupteurs.

Les donnes seront ralises par 4 interrupteurs et la visualisation des sorties par 4 LEDs.

On ralise ainsi une fonction de routage de donnes : slection dun metteur et dun rcepteur parmi des nombreux

lments, en utilisant un medium unique de communication (virtuel ici).

17

IUT Crteil - GEII - MC-ENSL1 - Composants programmables complexes COURS / TP

EXERCICE 2

La luminosit dun clairage (dans notre cas, une LED) peut tre rgle par lapplication

dun signal rectangulaire priodique de frquence assez leve et de rapport cyclique non

constant. On parle alors de gradateur.

Le rapport cyclique dun signal rectangulaire priodique est dni comme le rapport entre

le temps pendant lequel le signal est ltat haut et la priode. On exprime souvent ce

rapport en pourcentage. Ainsi :

la LED est teinte pour une rapport cyclique de 0%;

la luminosit est maximale pour une rapport cyclique de 100%;

la luminosit est environ moiti pour un rapport cyclique de 50%.

Cette application peut tre simplement ralise laide dun compteur 8 bits (synchrone)

et dun comparateur arithmtique 8 bits. Les interrupteurs dterminent le rapport cyclique.

Lhorloge choisir pour le compteur est CLK1 (50 Mhz).

1. Donner la structure que devra avoir cette application.

2. Dcrire en VHDL chacun des modules de cette application.

3. Raliser le chier source permettant de dcrire ce gradateur de LED en instanciant

les composants ncessaires.

2. Simulation

Il existe 2 niveaux de simulation :

comportementale (behavorial simulation) ;

physique (post-route simulation).

Dans la version allge de Xilinx ISE WebPack, seule la simulation comportementale est disponible.

2.1. Simulation comportementale

Pour tester un module VHDL, il faut lui associer un module gnrateur de signaux (non synthtisable) : le testbench.

Le testbench est un module VHDL spcial (disponible dans la liste des nouveaux modules lors de lajout de -

chier source). Il inclut le module tester comme un composant et lui associe des signaux. Lcriture dun testbench est

automatise avec Xilinx ISE.

Il reste ensuite crire un scnario de test animant les signaux dentre du module en test. On utilisera alors la mme

syntaxe quun module classique mais avec des instructions spciques.

2.1.1 Instructions spciales

La gestion du temps peut se faire hors processus :

1 c l k <= not c l k a f t e r 1000 us ;

2 hor l oge a 500 Hz

ou dans un processus :

1 hor l oge_500 : proces s

2 begi n

3 c l k <= 0 ;

4 wai t f or 500 us ;

5 c l k <= 1 ;

6 wai t f or 500 us ;

7 end proces s ;

Linstruction wait ; provoque larret de la simulation.

18

IUT Crteil - GEII - MC-ENSL1 - Composants programmables complexes COURS / TP

2.1.2 Exemple

1 e nt i t y p o r t e a b _ t b i s

2 end p o r t e a b _ t b ;

3

4 a r c hi t e c t ur e be ha vi or of p o r t e a b _ t b i s

5

6 component p o r t e a b

7 port ( a , b : i n s t d _ l o g i c ;

8 s : out s t d _ l o g i c ) ;

9 end component ;

10

11 i n p u t s

12 s i g na l a , b : s t d _ l o g i c : = 0 ;

13 o u t p u t s

14 s i g na l s : s t d _ l o g i c ;

15

16 begi n

17 i n s t a n c i a t i o n

18 uut : p o r t e a b port map( a => a , b => b , s => s ) ;

19

20 s c e n a r i o

21 s t i m_pr oc : proces s

22 begi n

23 wai t f or 50 ns ; a <= 0 ; b <= 0 ;

24 wai t f or 50 ns ; a <= 1 ; b <= 0 ;

25 wai t f or 50 ns ; a <= 0 ; b <= 1 ;

26 wai t f or 50 ns ; a <= 1 ; b <= 1 ;

27

28 wai t ;

29 end proces s ;

30

31 end be ha vi or ;

2.1.3 Exercices

EXERCICE 3

1. Associer ce chier de test la description de lexercice 1 du TP1 (fonction s =

a + a + b).

2. Lancer la simulation et vrier le bon fonctionnement du systme.

EXERCICE 4

1. Dcrire un compteur 4 bits avec une remise zro asynchrone.

2. Raliser le chier de test de ce module VHDL (en pensant remettre zro les sorties

ds le dbut de la simulation).

3. Lancer la simulation et vrier le bon fonctionnement du systme.

Lancer la simulation.

19

GEII - MC-ENSL1 TP 3

Achage multiplex

Objectifs

Raliser un module dachage hexadcimal sur 4 acheurs 7 segments fonctionnant en mode multiplex.

1. Principe dun achage multiplex

Dans un systme dachage, le multiplexage est un procd qui consiste utiliser plusieurs voyants ou plusieurs

acheurs et ne pas tous les allumer la fois, en vue dconomiser de lnergie et de limiter le nombre de ls de cblage.

Par exemple, lachage de votre radio rveil numrique, de votre machine laver ou de votre four micro-onde est fort

probablement multiplex.

Les donnes envoyer sur les acheurs transitent par un mme bus (7 ls dans le cas dun acheur 7 segments)

pour lensemble de ces acheurs. Ainsi le chire acher est envoy sur tous les acheurs en mme temps. Sans une

gestion particulire de ces acheurs, il nest pas possible dcrire des nombres.

Cest pourquoi, en parallle ce ces entres de donnes, il existe une entre de validation pour chacun des acheurs.

Ces entres sont souvent commands via des transistors pour permettre un gain de courant. Le schma ci-dessous donne

le cblage dun tel systme (3 acheurs 7 segments dans ce cas-l).

2. Etude du systme

An de dvelopper ce module de gestion dachage multiplex de manire la plus simple possible, nous allons

dcouper cette application en plusieurs blocs fonctionnels que nous allons par la suite dcrire en VHDL sparment :

un dcodeur dcimal 7 segments ;

un diviseur de frquence ;

un compteur pour le balayage des acheurs ;

un multiplexeur 4 vers 1 (4 x 4 bits dentre).

Pour pouvoir tester ce systme, des registres de stockage dentre seront ajouts.

EXERCICE 1

1. Faire le schma synoptique de ce systme en faisant ressortir les direntes entres

et sorties, ainsi que les signaux intermdiaires.

2. Rappeler le fonctionnement dun registre. Combien de bascules seront ncessaires

pour raliser ltage de stockage en entre ?

IUT Crteil - GEII - MC-ENSL1 - Composants programmables complexes COURS / TP

3. Module 1 - Dcodeur BCD / 7 segments

On souhaite raliser un dcodeur dcimal 7 segments utilisant un seul acheur (une des sorties an devra tre mise

0).

EXERCICE 2

1. Crer un chier source VHDL nomm BCD7seg.vhd.

2. Dcrire ce systme en utilisant uniquement des aectations conditionnelles ou slec-

tives (pas de process).

Les donnes convertir sont fournies par 4 interrupteurs.

4. Module 2 - Diviseur de frquence

La frquence de balayage des 4 acheurs sera xe 100 Hz. Il sera donc ncessaire de disposer dune horloge

400 Hz pour le balayage. Le diviseur de frquence concevoir sera actionn par lhorloge CLK1 de la carte (25 MHz).

EXERCICE 3

1. Crer un chier source VHDL nomm prediv.vhd.

2. Dcrire ce systme en VHDL, pour passer dune frquence de 25 MHz 400 Hz.

5. Module 3 - Compteur pour le balayage

An de pouvoir squentiellement slectionner un des acheurs, nous allons prsent nous intresser un compteur

synchrone.

EXERCICE 4

1. Combien dtats devra comporter ce compteur ? Combien de bascules seront alors

ncessaires ?

2. Crer un chier source VHDL nomm cpt.vhd.

3. Dcrire ce systme en VHDL.

6. Module 4 - Multiplexeur dentre

On souhaite pouvoir aecter lentre du dcodeur BCD/7segments une des 4 donnes prsentes en entre, an

quelles soient squentiellement aches.

EXERCICE 5

1. Quelle est la taille du mot binaire prsent chaque entre ? Quelle est la taille du mot

de sortie ?

2. Crer un chier source VHDL nomm muxBCD.vhd.

3. Dcrire ce systme en VHDL.

7. Module 5 - Dcodeur 2 vers 4

On souhaite raliser un dcodeur 2 vers 4 permettant partir du module "compteur" de slectionner un des 4 acheurs

7 segments. Ces acheurs sont actifs ltat bas.

21

IUT Crteil - GEII - MC-ENSL1 - Composants programmables complexes COURS / TP

EXERCICE 6

1. Crer un chier source VHDL nomm dec2v4.vhd.

2. Dcrire ce systme en utilisant uniquement des aectations conditionnelles ou slec-

tives (pas de process).

Les donnes convertir sont fournies par 4 interrupteurs.

8. Acheur complet

En regroupant lensemble des lments prcdents, il est possible de raliser un acheur multiplex complet.

EXERCICE 7

1. Crer un chier source VHDL nomm aff7seg.vhd.

2. Instancier les composants ncessaires au bon fonctionnement du systme dans ce

chier source.

3. Raliser alors un acheur multiplex prsentant un message constant (congur dans

le source, par exemple "1984").

9. Amlioration

Pour les exercices suivants, une source dentre sur 16 bits (4x4) et facilement rglable est ncessaire.

EXERCICE 8

1. Crer un chier source VHDL nomm regBCD.vhd.

2. Dcrire un registre parallle 4 bits ayant une entre de validation.

3. Ajouter la description contenue dans aff7seg.vhd la possibilit davoir 4 registres

en entre, en instanciant le composant prcdemment ralis.

4. Tester alors lacheur complet.

Les 4 entres de chacun des registres seront relies 4 interrupteurs. Les entres de validation de ces registres seront

relies aux 4 boutons-poussoirs. Lors de lappui sur lun deux, la donne prsente sur les 4 interrupteurs sera charge dans

le registre correspondant et ache sur lacheur correspondant.

An de pouvoir gnrer le chier de programmation correctement (Xilinx ISE version suprieure 10.1), vous devrez

ajouter la ligne : NET "clk" CLOCK_DEDICATED_ROUTE = FALSE; dans le chier de contraintes (*.ucf).

22

You might also like

- Les Circuits Logiques Programmables FPGADocument29 pagesLes Circuits Logiques Programmables FPGAOUSSAMA ELHJOUJI0% (1)

- TP Fpga Cyclone2Document3 pagesTP Fpga Cyclone2red-allNo ratings yet

- Travaux Dirigés FPGA & VHDLDocument28 pagesTravaux Dirigés FPGA & VHDLR.s. Félix75% (4)

- TP VHDL ModelSim20016 2017Document12 pagesTP VHDL ModelSim20016 2017Ayoub RahmouniNo ratings yet

- Cours 8086 2015-1Document105 pagesCours 8086 2015-1Dilane GhomsiNo ratings yet

- TP1Document12 pagesTP1Brad Mc Millen100% (1)

- Rapport de TP en VHDL Xilinx PDFDocument9 pagesRapport de TP en VHDL Xilinx PDFWalid AmriNo ratings yet

- CP FpgaDocument56 pagesCP FpgaHachemi Bhe100% (1)

- TP VHDL FpgaDocument13 pagesTP VHDL FpgaJoel Minkeu100% (1)

- Circuits Logiques ProgrammablesDocument23 pagesCircuits Logiques Programmablesben boubaker100% (1)

- DSP ExerciceDocument15 pagesDSP ExerciceMerit Khaled100% (1)

- 8 OscillateursDocument75 pages8 Oscillateursibamalick2008No ratings yet

- Communications Numeriques Master1 01Document70 pagesCommunications Numeriques Master1 01brezzy miraNo ratings yet

- Compte Rendu VHDLDocument6 pagesCompte Rendu VHDLSami FarsiNo ratings yet

- TP N2 - Circuits CombinatoiresDocument15 pagesTP N2 - Circuits CombinatoiresREDNANINo ratings yet

- Conception Numerique VHDL PDFDocument41 pagesConception Numerique VHDL PDFRomaysa jijiNo ratings yet

- Cours8Microprocesseurs ARM PDFDocument48 pagesCours8Microprocesseurs ARM PDFZied HouanebNo ratings yet

- Cours VHDL Tres ImportantDocument196 pagesCours VHDL Tres Importantbbaaziz2005100% (1)

- VHDLDocument133 pagesVHDLlarbi100% (1)

- Série Td2 #TS PDFDocument4 pagesSérie Td2 #TS PDFIlyas KendouciNo ratings yet

- Cours Technologie VHDL WE - V1.1Document46 pagesCours Technologie VHDL WE - V1.1Wajdi ElhamziNo ratings yet

- Questions Pre-Requis DSPDocument1 pageQuestions Pre-Requis DSPhasnaeNo ratings yet

- TP Integration Num FPGA V1.7Document22 pagesTP Integration Num FPGA V1.7Ouma ImaaNo ratings yet

- Tp3 Generation Correlation Produit Convolution Signaux Continus 2Document10 pagesTp3 Generation Correlation Produit Convolution Signaux Continus 2Hichem HamdiNo ratings yet

- Codage 1Document39 pagesCodage 1Youssef Jabrane100% (1)

- TD2 VHDL Et Logique ProgrammableDocument17 pagesTD2 VHDL Et Logique ProgrammableKais BahrouniNo ratings yet

- Cours - Composants Logiques Programmables Et VHDLDocument141 pagesCours - Composants Logiques Programmables Et VHDLYoussef Elalaoui0% (1)

- VHDLDocument16 pagesVHDLKhalil Fateh100% (2)

- Synthèse Et Application D'un Filtre RIF Passe-Bas Par La Méthode Des Fenêtres (Hanning, Hamming, Bartlett Et Blackman)Document3 pagesSynthèse Et Application D'un Filtre RIF Passe-Bas Par La Méthode Des Fenêtres (Hanning, Hamming, Bartlett Et Blackman)satima omNo ratings yet

- TP Filtrage Numerique DSPDocument7 pagesTP Filtrage Numerique DSPRACHID100% (1)

- Cours VHDL Et FPGADocument135 pagesCours VHDL Et FPGAMounira Tarhouni100% (1)

- TP de Traitement Numerique Du SignalDocument13 pagesTP de Traitement Numerique Du Signalratata2011No ratings yet

- tp3 Ing 2015 PDFDocument7 pagestp3 Ing 2015 PDFDorian GreyNo ratings yet

- Projet VHDLDocument19 pagesProjet VHDLbjm63100% (1)

- rOBOT SUIVEUR DE LIGNE À FPGA AlteraDocument23 pagesrOBOT SUIVEUR DE LIGNE À FPGA AlteraH. Seo100% (2)

- Fascicule de TP FpgaDocument32 pagesFascicule de TP FpgaHichem HamdiNo ratings yet

- TP Automatique LicenceDocument31 pagesTP Automatique LicenceABDELNASSER100% (1)

- Carte Numerique QuartusDocument26 pagesCarte Numerique QuartusAdiouma DiopNo ratings yet

- Compteur Synchrone - 2011 - 2012Document8 pagesCompteur Synchrone - 2011 - 2012Elmokh Lassaad100% (1)

- TD N 4 (Supplemetaire) FpgaDocument2 pagesTD N 4 (Supplemetaire) FpgaLE BARONNo ratings yet

- Boucle À Verrouillage de Phase (PLL)Document25 pagesBoucle À Verrouillage de Phase (PLL)Hachemi BheNo ratings yet

- TD N 3 FpgaDocument2 pagesTD N 3 FpgaLE BARON100% (1)

- Les Applications HyperfréquencesDocument8 pagesLes Applications HyperfréquencesEmna Kanzari0% (1)

- Synthèse Filtres Actifs - 1Document44 pagesSynthèse Filtres Actifs - 1db100% (4)

- Le Langage de Description VHDLDocument46 pagesLe Langage de Description VHDLHicham MahfoudiNo ratings yet

- Compatibilité Électromagnétique (CEM)Document12 pagesCompatibilité Électromagnétique (CEM)Mister R100% (1)

- TDuC 7 CorrectionDocument16 pagesTDuC 7 Correctionazeraqw2250% (2)

- TP Filtre NumériqueDocument8 pagesTP Filtre NumériqueAnouar BenlaqlibNo ratings yet

- PLLDocument21 pagesPLLKhalid ItachiNo ratings yet

- Rapport de Travaux Pratiques Conception Des Circuits AnalogiquesDocument31 pagesRapport de Travaux Pratiques Conception Des Circuits AnalogiquesYacine83% (6)

- Examen VHDL +correction 1ere Session 2008Document5 pagesExamen VHDL +correction 1ere Session 2008Med0% (1)

- Compte Rendu Du TP Sur Ofdm, Cdma, Et WDM: Encadré Par: Pr. Farid ABDIDocument22 pagesCompte Rendu Du TP Sur Ofdm, Cdma, Et WDM: Encadré Par: Pr. Farid ABDIrhariss97No ratings yet

- Rapport TP VHDLDocument16 pagesRapport TP VHDLimeness100% (1)

- Basys 2Document26 pagesBasys 2Hichem KhamallahNo ratings yet

- Fpga VHDLDocument22 pagesFpga VHDLAsmaheneNo ratings yet

- TP5 - Circuits Logiques Programmables CPLDDocument8 pagesTP5 - Circuits Logiques Programmables CPLDeya arfaouiNo ratings yet

- 01 - Les Circuits Logiques Programmables2013Document28 pages01 - Les Circuits Logiques Programmables2013Ran yaNo ratings yet

- Compte Rendu TP Electronique NumériqueDocument16 pagesCompte Rendu TP Electronique NumériqueEL YâssirNo ratings yet

- PIC16F877Document77 pagesPIC16F877Mandar Mehdi100% (1)

- Fiche1 Distribution Securite ElecDocument6 pagesFiche1 Distribution Securite EleckfawazNo ratings yet

- Arc Hi 3Document44 pagesArc Hi 3kfawazNo ratings yet

- Presentation Me 2007-08Document71 pagesPresentation Me 2007-08kfawazNo ratings yet

- Electrotechnique Cours (Edouard Laroche)Document94 pagesElectrotechnique Cours (Edouard Laroche)Samir SayahNo ratings yet

- Guide ApogéeDocument9 pagesGuide ApogéeSi Mohamed Almadani100% (1)

- Philips Chassis l01.2l L01.2a-Ab SMDocument68 pagesPhilips Chassis l01.2l L01.2a-Ab SMJuan BallonNo ratings yet

- Exchange 2003 - KHALID KATKOUTDocument54 pagesExchange 2003 - KHALID KATKOUTtoto TOTOROTONo ratings yet

- Les Bases de HTML 5Document82 pagesLes Bases de HTML 5Inès MskNo ratings yet

- TP1 Interpolation de LagrangeDocument9 pagesTP1 Interpolation de LagrangeMa RamNo ratings yet

- Architecture de L'ordinateur CoursDocument52 pagesArchitecture de L'ordinateur CoursImane lachgarNo ratings yet

- Compte Rendu TP3 SIBDDocument7 pagesCompte Rendu TP3 SIBDLaila MoussaouiNo ratings yet

- Documentation Paramétrage MyGed PDFDocument64 pagesDocumentation Paramétrage MyGed PDFJean-Joel LEKANGANo ratings yet

- TP C WordDocument21 pagesTP C WordWiem BaazouziNo ratings yet

- Unix: Commandes Et Expressions Régulières: Guy Tremblay ProfesseurDocument155 pagesUnix: Commandes Et Expressions Régulières: Guy Tremblay ProfesseurRandy NkamwaNo ratings yet

- Cours Base de Données Conception Et Manipulation Lic2 Maths Infos 2023Document35 pagesCours Base de Données Conception Et Manipulation Lic2 Maths Infos 2023ndembimarvinmarionNo ratings yet

- Business IntelligenceDocument89 pagesBusiness Intelligenceamine_lemagni100% (1)

- Scénario Pédagogique Du Module Réseaux Et Internet Pour Tronc CommunDocument4 pagesScénario Pédagogique Du Module Réseaux Et Internet Pour Tronc CommunChayma El HayaniNo ratings yet

- Rapport Conquete 2009 HananeDocument30 pagesRapport Conquete 2009 HananeBen Mlih AmineNo ratings yet

- Conception Et Réalisation D'une Application Web Pour La Gestion Des Congés - Allaoui NajatDocument55 pagesConception Et Réalisation D'une Application Web Pour La Gestion Des Congés - Allaoui NajatWork Clothing100% (1)

- Chap 0 Presentation ALSIDocument4 pagesChap 0 Presentation ALSIKnowlegde2016No ratings yet

- Couch DBDocument4 pagesCouch DBYasmina IzarrahneNo ratings yet

- Controle 1 Tsdi CdsDocument3 pagesControle 1 Tsdi CdsYacine BELGHARDNo ratings yet

- Je Crée Ma BDDocument36 pagesJe Crée Ma BDChatelain PatrickNo ratings yet

- Memoire LinuxDocument20 pagesMemoire LinuxKader AmhisNo ratings yet

- Synthèse Les Robots CorrigéDocument3 pagesSynthèse Les Robots CorrigéThomBlioNo ratings yet

- Emploi Du Temps GEA2 FC 2020-2021 PDFDocument1 pageEmploi Du Temps GEA2 FC 2020-2021 PDFHxmza HousseinNo ratings yet

- Activité N°1 ProgrammationDocument4 pagesActivité N°1 Programmationeras novaNo ratings yet

- 2 - BD - SQL - Prog - 3IL2 - 2017-2018Document32 pages2 - BD - SQL - Prog - 3IL2 - 2017-2018François-Xavier TekoudjouNo ratings yet

- TP STR n1Document1 pageTP STR n1Mouh Mab67% (3)

- Manuel de Nettoyage Des Donnes Lexmark - CX410Document11 pagesManuel de Nettoyage Des Donnes Lexmark - CX410NOVATEK MednineNo ratings yet

- Cours D'informatique Pour Debutant Complet - Cours InformatiqueDocument1 pageCours D'informatique Pour Debutant Complet - Cours InformatiqueChérif Tidiane DiopNo ratings yet

- Contrôle Final - AgileDocument20 pagesContrôle Final - Agilemtfat253No ratings yet

- CV Ludivine PeuretDocument1 pageCV Ludivine Peuretenividul28No ratings yet

- Rapport Final - Poubelle AutomatiqueDocument46 pagesRapport Final - Poubelle AutomatiqueYasmine Aouni100% (4)