Professional Documents

Culture Documents

Cours 1 Cmos

Uploaded by

Med LabbiCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cours 1 Cmos

Uploaded by

Med LabbiCopyright:

Available Formats

1 PHY 559 / C1 Alain Greiner

Cours 1 : Du silicium aux portes logiques CMOS

Programme dapprofondissement

Electrical Engineering

responsable :

Phy 559

Conception de circuits intgrs

numriques et analogiques

2 PHY 559 / C1 Alain Greiner

Plan

! Rappels sur lalgbre de Boole

! Le transistor MOS

! Des expressions Boolennes au silicium

! Principe des portes logiques CMOS

! Caractrisation de linverseur CMOS

3 PHY 559 / C1 Alain Greiner

Algbre de Boole (1)

! Variables Booleennes

X ! {0 , 1} = B

! Fonctions Booleennes

(X1,X2,X3,,Xn) " Y = f (X1,X2,X3,,Xn)

! B

n

! B

! Table de vrit

- La table de vrit dune fonction Booleenne

n variables contient 2

n

entres

- On peut dfinir 2 fonctions Booleennes

n variables.

X1 X2 X3 F(X1,X2,X3)

0 0 0 0

0 0 1 1

0 1 0 1

0 1 1 0

1 0 0 1

1 0 1 0

1 1 0 0

1 1 1 1

2

n

4 PHY 559 / C1 Alain Greiner

Algbre de Boole (2)

! Fonctions Booleennes de une seule variable

! Fonctions Booleennes de 2 variables

X1 X2 or (X1,X2)

X1 or X2

and(X1,X2)

X1 and X2

xor(X1,X2)

X1 xor X2

Imply(X1,X2)

X1 => X2

nor(X1,X2) nand(X1,X2)

0 0 0 0 0 1 1 1

0 1 1 0 1 1 0 1

1 0 1 0 1 0 0 1

1 1 1 1 0 1 0 0

X F(X) = 0 F(X) = 1 F(X) = X F(X) = not X

0 0 1 0 1

1 0 1 1 0

5 PHY 559 / C1 Alain Greiner

Algbre de Boole (3)

Les oprateurs boolens de base sont des fonctions

boolennes une ou deux variables.

S = not X S = X

S = X or Y S = X + Y

S = X and Y S = X . Y

S = not (X or Y) S = X + Y

S = not (X and Y) S = X . Y

S = X xor Y S = X + Y

X

Y

X

Y

X

Y

X

Y

X

Y

S

S

S

S

S

S X

6 PHY 559 / C1 Alain Greiner

Algbre de Boole (4)

! Identits remarquables

# X . 0 = 0 / X + 0 = X

# X . 1 = X / X + 1 = 1

# X . X = 0 / X + X = 1

! Commutativit des oprateurs or et and

# X . Y = Y . X

# X + Y = Y + X

! Associativit des oprateurs or et and

# (X . Y) . Z = X . (Y . Z) = X . Y . Z = and(X,Y,Z)

# (X + Y) + Z = X + (Y + Z) = X + Y + Z = or(X,Y,Z)

7 PHY 559 / C1 Alain Greiner

Algbre de Boole (5)

! Distributivit

# (X + Y) . Z = (X . Y) + (Y . Z)

# (X .Y) + Z = (X + Z) . (Y + Z)

! Consensus

# (X . Z) + (Y . Z) + X . Y = (X . Z) + (Y . Z)

! Lois de De Morgan

# (X + Y) = X . Y

# (X . Y) = X + Y

8 PHY 559 / C1 Alain Greiner

Expressions Booleennes

! Une Expression Booleenne est une reprsentation compacte

dune fonction Booleenne, construite partir dun nombre

quelconque de variables Booleennes, doprateurs Booleens,

et de parenthses imbriques :

E1 = or(and(A,C),and(B,not(C)))

E1 = (A.C) + (B.C)

! Il existe plusieurs expressions Booleennes quivalente

associes une mme fonction Boolenne :

E2 = (A.B.C) + (A.B.C) + (A.B.C) + (A.B.C)

E3 = (A+B+C).(A+B+C).(A+B+C).(A+B+C)

9 PHY 559 / C1 Alain Greiner

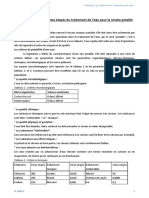

Simplification des expressions Booleennes

! Le cot de ralisation matrielle dune expression Boolenne (mesur en

nombre de transistors) est proportionnel sa complexit (mesure en

nombre de littraux).

! Les Tableaux de Karnaugh sont une reprsentation bidimensionnelle des

tables de vrits, qui permet de minimiser le nombre de littraux :

C A B E1 = E2 = E3

0 0 0 0

0 0 1 1

0 1 0 1

0 1 1 0

1 0 0 1

1 0 1 0

1 1 0 0

1 1 1 1

0 0 1 1

0 1 1 0

A 0 1 1 0

B 0 0 1 1

C

0

1

E1 = A.C + B.C

10 PHY 559 / C1 Alain Greiner

Plan

! Rappels sur lalgbre de Boole

! Le transistor MOS

! Des expressions Boolennes au silicium

! Principe des portes logiques CMOS

! Caractrisation de linverseur CMOS

11 PHY 559 / C1 Alain Greiner

Semi-Conducteurs

Conductivit / Rsistivit des matriaux

Pur Dop SILICON

12 PHY 559 / C1 Alain Greiner

Silicium

! Silicium intrinsque

# Densit d atomes N

A

= 5 10

22

cm

-3

# Densit de porteurs N

P

= 1.5 10

10

cm

-3

! Silicium dop

# Aux Pentavalents (P, As) > Type n = conduction par lectrons

Aux Trivalents (B) > Type p = conduction par trous

# Densit de porteurs N

P

= 10

15

10

16

cm

-3

! Conductivit et Mobilit

# Conductivit -> " = 1 / # = N

p

e <- Mobilit

# La mobilit ! des trous est infrieure celle des lectrons :

Mobilit :

! ( cm

2

. V

- 1

. s

-1

) Si pu r Si f or tement dop

El ectr ons l ibr es

1350 10 0

Tr ous 480 60

13 PHY 559 / C1 Alain Greiner

Ralisation du transistor MOS

CHANNEL WIDTH (W)

14 PHY 559 / C1 Alain Greiner

Fonctionnement du transistor NMOS

! Zone de dpltion pour V

GS

positif faible (V

GS

< V

T

)

! Canal d inversion pour VGS positif fort (V

GS

> V

T

)

15 PHY 559 / C1 Alain Greiner

NMOS V

GS

positif fort et V

DS

non nul

! V

DS

> 0 le courant dlectrons va de la Source au Drain

V

GS

> V

T

le canal conducteur est form

! Mode rsistif

(V

GD

> V

T

<==> V

DS

< V

GS

- V

T

)

! Mode satur

(V

GD

" V

T

<==> V

DS

# V

GS

- V

T

)

# Pincement du canal

# $L est trs petit

16 PHY 559 / C1 Alain Greiner

Modle de courant du transistor NMOS

! V

GS

< V

T

: Mode bloqu :

I

D

= 0

! V

GS

> V

T

et V

GD

> V

T

<==> V

DS

< V

GS

V

T

: Mode rsistif

! V

GS

> V

T

et V

GD

< V

T

<==> V

DS

> V

GS

V

T

: Mode satur

! Frontire Rsistif Satur : V

GD

= V

T

I

D

=

1

2

n

C

o x

W

L

V

GS

! V

T

( )

2

I

D

=

n

C

o x

W

L

V

GS

! V

T

( )V

DS

-

1

2

V

DS

2 "

#

$

%

k

n

=

n

C

o x

W

L

I

D

=

1

2

n

C

o x

W

L

V

DS

2

Transconductance

:

17 PHY 559 / C1 Alain Greiner

Graphe Courant-Tension du NMOS

Mode rsistif

Mode satur

18 PHY 559 / C1 Alain Greiner

Valeurs typiques des paramtres

! Mobilit

n

! 580 cm

2

/Vs

p

! 230 cm

2

/Vs

! Capacit dOxyde

# paisseur t

ox

= 0,02 0,1 m

# Permittivit %

ox

= 3,97 10

-13

F/cm

# Capacit/m

2

C

ox

= %

ox

/ t

ox

= 1,75 fF/m

2

pour t

ox

= 0,02 m

= 0,35 fF/m

2

pour t

ox

= 0,1 m

19 PHY 559 / C1 Alain Greiner

Fonctionnement du transistor PMOS

! Similaire au NMOS, mais avec :

V

DS

< 0 => le courant de trous va de la Source au Drain

V

T

< 0 => V

GS

est usuellement ngatif

! V

GS

> V

T

: Mode Bloqu

I

D

= 0

! V

GS

< V

T

et V

GD

< V

T

<==> V

DS

> V

GS

- V

T

: Mode rsistif

! V

GS

< V

T

et V

GD

> V

T

<==> V

DS

< V

GS

- V

T

: Mode satur

I

D

=

p

C

o x

W

L

V

GS

! V

T

( )V

DS

-

1

2

V

DS

2 "

#

$

%

I

D

=

1

2

p

C

o x

W

L

V

GS

! V

T

( )

2

20 PHY 559 / C1 Alain Greiner

Circuits CMOS

21 PHY 559 / C1 Alain Greiner

Rcapitulatif NMOS et PMOS

NMOS PMOS

Pour la conception des circuits numriques, les transistors MOS

peuvent tre considrs comme des interrupteurs commands par

la valeur de la tension de grille.

La rsistance quivalente (Ron) du transistor passant peut tre ajuste

en faisant varier la gomtrie : largeur W, et longueur L du canal.

A gomtrie gale, la rsistance quivalente du transistor P est plus

grande que celle du transistor N (facteur 2.3)

22 PHY 559 / C1 Alain Greiner

MAIS

Dans les schmas ci-dessous, on suppose quon impose une tension

connue et fixe sur la patte de gauche, et on cherche la propager vers la

patte de droite en rendant passant linterrupteur (0 logique $ 0V / 1 logique

$ 3.3V).

G = 3.3V

S = 0V

D -> 0V

G = 3.3V

D = 3.3V

S -> 3.3V - Vt

=> Les transistors NMOS sont de bons passeurs de 0

mais de mauvais passeurs de 1: on perd un seuil .

G = 0V

D = 0V

S -> |Vt|

G = 0V

S = 3.3V

D -> 3.3V

=> Les transistors PMOS sont de bons passeurs de 1,

mais de mauvais passeurs de 0 : on perd un seuil .

NMOS

PMOS

23 PHY 559 / C1 Alain Greiner

Plan

! Rappels sur lalgbre de Boole

! Le transistor MOS

! Des expressions Boolennes au silicium

! Principe des portes logiques CMOS

! Caractrisation de linverseur CMOS

24 PHY 559 / C1 Alain Greiner

Expressions Booleennes sur silicium

! Variables Booleennes

Les variables Boolennes sont reprsentes par des fils

mtalliques (appels signaux), qui vhiculent deux niveaux

de tension : Vss (0 logique) / Vdd (1 logique).

! Oprateurs Booleens

Les oprateurs Booleens sont raliss comme des

assemblages de transistors NMOS et PMOS (appeles

portes logiques), qui possdent gnralement N signaux

en entre et un seul signal en sortie.

25 PHY 559 / C1 Alain Greiner

Circuits en portes logiques

Le support de lexpression Booleenne S = A.C + B.C est lensemble {A,B,C}.

Le circuit logique ralisant cette expression Booleenne possde donc 3

signaux dentre (A,B,C), et un signal de sortie S.

En utilisant les lois de DeMorgan, on peut la re-crire : S = (A.C) . (B.C)

Elle peut tre ralise avec 3 portes nand et un inverseur :

A

C

B

S

X

Y

Z

On prfre utiliser des portes

inverseuses (not, nor, nand),

car ces portes utilisent moins

de transistors que les portes

non-inverseuses (or et and).

26 PHY 559 / C1 Alain Greiner

Plan

! Rappels sur lalgbre de Boole

! Le transistor MOS

! Des expressions Boolennes au silicium

! Principe des portes logiques CMOS

! Caractrisation de linverseur CMOS

27 PHY 559 / C1 Alain Greiner

Portes CMOS DUAL

Dualit : Les deux fonctions CN et CP doivent tre complmentaires,

pour que le nud S soit toujours connect une et une seule tension

dalimentation Vss ou Vdd.

Rseau de transistors PMOS permettant

de forcer la sortie S la tension Vdd (1 logique).

On utilise des transistors PMOS, qui sont des bons

passeurs de 1. Le rseau P est caractris par sa

fonction de conduction C

P

(entres)

Entres

Sortie S = C

P

= C

N

Vdd

Vss

CN

CP

Rseau de transistors NMOS permettant

de forcer la sortie S la tension Vss (0 logique).

On utilise des transistors NMOS, qui sont des bons

passeurs de 1. Le rseau N est caractris par sa

fonction de conduction C

N

(entres)

28 PHY 559 / C1 Alain Greiner

Inverseur CMOS

Linverseur CMOS possde trois entres E, Vss, Vdd, et une sortie S.

Les signaux Vss et Vdd sont des tension dalimentation constantes,

et sont connects aux sources des deux transistors N et P.

Le signal E est connect la grille des deux transistors.

Le signal de sortie S est connect aux drains des deux transistors

E

S = E

Vss

Vdd

E = 1

S = 0

Vss

Vdd

E = 0

S = 1

Vss

Vdd

29 PHY 559 / C1 Alain Greiner

Porte NOR 2 entres

E1

E2

E1

E2

S = (E1 + E2)

Vss

Vdd

E1 E2 S

0 0 1

0 1 0

1 0 0

1 1 0

30 PHY 559 / C1 Alain Greiner

Porte NAND 2 entres

E1 E2

E1

E2

S = (E1.E2)

Vss

Vdd

E1 E2 S

0 0 1

0 1 1

1 0 1

1 1 0

31 PHY 559 / C1 Alain Greiner

Portes CMOS DUAL complexes

S = E3 (E1 + E2)

E1

E2

E3

E1 E2

E3

VDD

VSS

Dans les portes logiques CMOS DUAL, les signaux dentres sont

toujours connectes aux grilles des transistors des deux rseaux

de conduction PMOS et NMOS

E1 E2 E3 S

0 0 0 1

0 0 1 1

0 1 0 1

0 1 1 0

1 0 0 1

1 0 1 0

1 1 0 1

1 1 1 0

32 PHY 559 / C1 Alain Greiner

Porte 3 tats (non DUAL)

Elles sont utilises pour raliser des bus multi-metteurs. A tout instant,

un seul metteur est autoris a mettre une valeur, et les autres doivent

tre isols du bus. On a donc 2 tats logiques (0 et 1), et un tat isol.

C

E S <= E when C

VDD

VSS

Dessin F.A.

E C S

0 0 HiZ

1 0 HiZ

0 1 1

1 1 0

C

E S

33 PHY 559 / C1 Alain Greiner

Plan

! Rappels sur lalgbre de Boole

! Le transistor MOS

! Des expressions Boolennes au silicium

! Principe des portes logiques CMOS

! Caractrisation de linverseur CMOS

34 PHY 559 / C1 Alain Greiner

Courbe de transfert statique de linverseur CMOS

Vin

Vout

VDD

VDD VL |Vtn| (VDD|Vtp|)

Vin

Vout

VL =

|Vtn| + & (VDD - |Vtp|)

avec & = = ' '

n

W

n

W

p

L

p

L

n

1 + &

W

n

/ L

n

W

p

/ L

p

Kn

Kp

Vss = 0V

Vdd

N bloqu

P rsistif

N satur

P rsistif

N satur

P satur

N rsistif

P satur

N rsistif

P bloqu

35 PHY 559 / C1 Alain Greiner

Comportement dynamique de linverseur CMOS

! La capacit de charge CL en sortie de

linverseur est la somme de plusieurs

termes :

# Capacit de grille des portes attaques

# Capacit des drains de la porte

# Capacit du fil dinterconnexion

! La capacit CL est alternativement charge

ou dcharge travers deux transistors qui

se comportent comme deux rsistances

RP

on

et RN

on

.

! Les temps de commutation sont donc :

# T

up

= Rp

on

* CL

# T

down

=

RN

on

* CL

S

CL

RP

on

RN

on

36 PHY 559 / C1 Alain Greiner

Temps de propagation de linverseur CMOS

temps

VDD

Tdown (out)

tension

90%

10%

VDD/2

Tup(in)

in

out

Tp(in->out

Le temps de propagation Tp(in->out) se mesure VDD/2.

Il est videmment diffrent des temps commutation Tup et Tdown,

mais dpend (au premier ordre) des mmes paramtres Ron et CL

37 PHY 559 / C1 Alain Greiner

Temps de propagation des portes CMOS

Les portes complexes sont dautant plus lentes quil y a plus de transistors

en srie (la rsistance quivalente est la somme des rsistances srie).

# Les transistors P tant intrinsquement 2 fois plus rsistifs que les

transistors P, il est prfrable de disposer les N en srie plutt que les P.

# On limite le nombre de portes attaques par une seule porte (fan-out)

pour minimiser la capacit de charge CL.

# La longueur L du canal est gnralement au minimum permis

par le procd de fabrication, et on augmente la largeur W du canal

quand il y a plusieurs transistors en srie pour minimiser RP

on

et RN

on

,

mais cela augmente la capacit dentre de la porte.

38 PHY 559 / C1 Alain Greiner

Consommation nergtique

! Consommation dynamique

Lie la charge et la dcharge de la capacit CL,

et proportionnelle la frquence de commutation.

Cest la consommation utile ...

P = CL * Vdd

2

* F (watts)

! Consommation dynamique de court-circuit

Lie au caractre non instantan de la commutation,

pendant laquelle les deux transistors sonN et P sont

simultanment passants.

! Consommation statique de fuites

Lie aux courants de fuites dans le substrat, ainsi

quau courant sous le seuil dans les procds de

fabrication sub-micronique.

S

CL

RP

on

RN

on

You might also like

- TP CmosDocument17 pagesTP CmosHiba TANTAOUINo ratings yet

- CC Reseaux Et Supervision Roi5 2020Document2 pagesCC Reseaux Et Supervision Roi5 2020Abdoul Bagui YaoubaNo ratings yet

- Compte Rendu: TP3: TFTD, TFD Et L'effet de FenêtrageDocument12 pagesCompte Rendu: TP3: TFTD, TFD Et L'effet de FenêtrageTakfarinas MezioudNo ratings yet

- Traitement Du Son Par DSP PDFDocument30 pagesTraitement Du Son Par DSP PDFAmira CNo ratings yet

- DevoirDocument2 pagesDevoirmohammed boufenziNo ratings yet

- Circuitsintegres LogiquesDocument53 pagesCircuitsintegres LogiquesSouhaib LoudaNo ratings yet

- TD TNSDocument69 pagesTD TNSAdil AbouelhassanNo ratings yet

- Fiche Maquette Modulation BPSKDocument1 pageFiche Maquette Modulation BPSKLynda MOKRANINo ratings yet

- GEL-16120 - Modulation NumeriqueDocument30 pagesGEL-16120 - Modulation NumeriqueIbrahimFaroukSolarNo ratings yet

- TPs Antennes1Document39 pagesTPs Antennes1Hiba TANTAOUINo ratings yet

- Compte Rendu TP 1 TSDocument10 pagesCompte Rendu TP 1 TSMohamed El Mehdi MEDDADNo ratings yet

- Chapitre 1 - Filtres Analogiques - Master RTDocument43 pagesChapitre 1 - Filtres Analogiques - Master RTIsak EscobarNo ratings yet

- Chapitre1 - Propagation Et AntennesDocument22 pagesChapitre1 - Propagation Et AntennesKoussaila KoussaNo ratings yet

- Mémoir 10Document39 pagesMémoir 10amal amoulaNo ratings yet

- Compte Rendu - Filtre Pass Haut - Altium DesignerDocument7 pagesCompte Rendu - Filtre Pass Haut - Altium DesignerCherry CandyNo ratings yet

- Compte-Rendu TP ModulationDocument24 pagesCompte-Rendu TP ModulationDaniel Camacho100% (1)

- Filtrage 1Document23 pagesFiltrage 1Franck LecocqNo ratings yet

- Cours de Technique de TransmissionDocument85 pagesCours de Technique de TransmissionThierry IlboudoNo ratings yet

- Support de Cours FH EtudiantDocument136 pagesSupport de Cours FH EtudiantbilllNo ratings yet

- TP N°02 Codage Shanon-FanoDocument2 pagesTP N°02 Codage Shanon-FanoMohamed MohamedNo ratings yet

- Tp4 Mesure Antennes1Document9 pagesTp4 Mesure Antennes1جمال سينغNo ratings yet

- Amplificateur de Puissance Classe B, ABDocument7 pagesAmplificateur de Puissance Classe B, ABKhaira ToulaNo ratings yet

- Théorie Du SignalDocument78 pagesThéorie Du SignalAboubacryNo ratings yet

- TP Transmission NumériqueDocument14 pagesTP Transmission NumériqueAdil EL AttarNo ratings yet

- TEL602 Serie 2Document1 pageTEL602 Serie 2Mohamed El Glafi100% (1)

- Chapitre 3 Bases Physiques Instrumentation Scientifique LP-MES ABybi PDFDocument28 pagesChapitre 3 Bases Physiques Instrumentation Scientifique LP-MES ABybi PDFilhamNo ratings yet

- Chapitre 8 Convertisseur Adc DacDocument9 pagesChapitre 8 Convertisseur Adc DacMedNo ratings yet

- Filtres A Capacité CommutéeDocument17 pagesFiltres A Capacité Commutéeyoussed88No ratings yet

- Microcontroleur PIC16F84Document33 pagesMicrocontroleur PIC16F84redaNo ratings yet

- Traitement Du Signal-Eln - L3 TD2: Analyse Et Synthèse Des Filtres AnalogiquesDocument4 pagesTraitement Du Signal-Eln - L3 TD2: Analyse Et Synthèse Des Filtres AnalogiquesSouha KhadraouiNo ratings yet

- Exercices Reseau CellulaireDocument2 pagesExercices Reseau Cellulaireahmed chaouki ChamiNo ratings yet

- TD-Ligne de TransmissionDocument1 pageTD-Ligne de TransmissionOumar KOITANo ratings yet

- Corrigé E3bDocument33 pagesCorrigé E3bOussama SlimaniNo ratings yet

- Simulation Et Implémentation en Temps Réel de La Technique OFDM en Utilisant Le Processeur DSP C6713Document89 pagesSimulation Et Implémentation en Temps Réel de La Technique OFDM en Utilisant Le Processeur DSP C6713Sokhna Fatou GueyeNo ratings yet

- TD N7Document10 pagesTD N7JesúsGambarteNo ratings yet

- TEL602Document1 pageTEL602badreddineNo ratings yet

- Ccma PDFDocument110 pagesCcma PDFJaouad AssagNo ratings yet

- Inter TDPDocument3 pagesInter TDPminaNo ratings yet

- Partiels2a PDFDocument314 pagesPartiels2a PDFchfakhtNo ratings yet

- Exercices2009 2010Document24 pagesExercices2009 2010Miss AmericanaNo ratings yet

- Ds 2009-2010 No1 CorrectionDocument8 pagesDs 2009-2010 No1 CorrectiongamalNo ratings yet

- TP2 MCC PrepaDocument6 pagesTP2 MCC PrepaAlfredho ShactarNo ratings yet

- Chapitre III AntenneDocument10 pagesChapitre III AntenneNa DaNo ratings yet

- Série 1 TD Traitement de SiganlDocument2 pagesSérie 1 TD Traitement de SiganlFatima Zohra ESSAKHAIRYNo ratings yet

- Compte Rendu EIDocument5 pagesCompte Rendu EIassia guzelNo ratings yet

- Tp1 Presentation Materiel Utilise TP Traitement Signal PDFDocument13 pagesTp1 Presentation Materiel Utilise TP Traitement Signal PDFFatma BelabedNo ratings yet

- Notion de Base Des RéseauxDocument72 pagesNotion de Base Des RéseauxJawadi HamdiNo ratings yet

- Chapitre 1 DispositifsDocument54 pagesChapitre 1 DispositifsAbdou SuperNo ratings yet

- Chap 1 Cours RFDocument38 pagesChap 1 Cours RFNadir Ait MoussaNo ratings yet

- CA Chapitre 2Document11 pagesCA Chapitre 2souadNo ratings yet

- Ch1 PDFDocument33 pagesCh1 PDFNabil EL Kassoumi100% (1)

- Circuit AnalogiqueDocument4 pagesCircuit AnalogiqueWilly TallaNo ratings yet

- Synthèse Des Filtres RIFDocument29 pagesSynthèse Des Filtres RIFÃmįrä ØùnõkïNo ratings yet

- Fonctionnement de La PLLDocument9 pagesFonctionnement de La PLLLahouari FatahNo ratings yet

- Modéle de RedactionDocument31 pagesModéle de RedactionBöuäbdälläh AïmenNo ratings yet

- TP2 TapDocument6 pagesTP2 TapReda BadroNo ratings yet

- TD N 4 ET 5 REGULATION NUMERIQUE INST94 - 2023 - CorrigéDocument17 pagesTD N 4 ET 5 REGULATION NUMERIQUE INST94 - 2023 - CorrigéGüzlãn Güzlã0% (1)

- Post FixDocument5 pagesPost FixMed LabbiNo ratings yet

- 6 - Résidentiel Très Haut Débit V5 (Light)Document15 pages6 - Résidentiel Très Haut Débit V5 (Light)Med LabbiNo ratings yet

- Config VPNDocument7 pagesConfig VPNMed LabbiNo ratings yet

- Tipe-Dang Hoang VuDocument31 pagesTipe-Dang Hoang VuJuliette VilatNo ratings yet

- Cours 12 Wifi ReseauDocument10 pagesCours 12 Wifi ReseauMed LabbiNo ratings yet

- Cna CanDocument4 pagesCna CanMed LabbiNo ratings yet

- 466 Cours Adressage IpDocument39 pages466 Cours Adressage IpAnonymous Wpl47Bwu4No ratings yet

- Chap 6 Codage Du SonDocument6 pagesChap 6 Codage Du SonMed LabbiNo ratings yet

- Introduction Aux SocketsDocument23 pagesIntroduction Aux SocketsZepher HatakeNo ratings yet

- CHAPITRE 1 Micro OndesDocument9 pagesCHAPITRE 1 Micro OndesMed LabbiNo ratings yet

- Chap 6 Codage Du SonDocument6 pagesChap 6 Codage Du SonMed LabbiNo ratings yet

- Cours9 AlgoDocument10 pagesCours9 AlgoMed LabbiNo ratings yet

- Matlab 1Document10 pagesMatlab 1Med LabbiNo ratings yet

- Cours de Réseaux (Maîtrise D'informatique Université D'angers)Document87 pagesCours de Réseaux (Maîtrise D'informatique Université D'angers)niko100% (8)

- ReseauDocument33 pagesReseaubchaib70No ratings yet

- Archi Cours 4Document206 pagesArchi Cours 4ksimathsuNo ratings yet

- Adc - Ps Annexes - MathsDocument11 pagesAdc - Ps Annexes - MathsMonCf MerrNo ratings yet

- Annexe 2 Identifiez Les Facteurs Déterminants La Position Concurrentielle D'essilor Avant L'opération de RapprochementDocument4 pagesAnnexe 2 Identifiez Les Facteurs Déterminants La Position Concurrentielle D'essilor Avant L'opération de RapprochementS.A O.CNo ratings yet

- Cheville TapconDocument5 pagesCheville TapconAnonymous FBFoaVMuNo ratings yet

- Bouchireb, NassimaDocument1 pageBouchireb, NassimaMbarka ManelNo ratings yet

- Schematique Psa 2Document36 pagesSchematique Psa 2Anonymous 7VmObaA7sL100% (1)

- Quels Sont Les Différents Acteurs Intervenants en Milieu Pénitentiaire - VieDocument2 pagesQuels Sont Les Différents Acteurs Intervenants en Milieu Pénitentiaire - VieAmane ImaneNo ratings yet

- L2 Lac Ana NumDocument7 pagesL2 Lac Ana NumReyririNo ratings yet

- Afficheurs Série 700Document10 pagesAfficheurs Série 700tlevageNo ratings yet

- Notes de Cours - Circuits Logiques CombinatoiresDocument34 pagesNotes de Cours - Circuits Logiques CombinatoiresAbdellah id ben omarNo ratings yet

- Travaux Dirigés - Série 1Document2 pagesTravaux Dirigés - Série 1MOHAND ES - SAADANYNo ratings yet

- 2020-Programme Master Genie Civil PDFDocument10 pages2020-Programme Master Genie Civil PDFForest SandlyNo ratings yet

- Processus Recrutement.2 PDFDocument3 pagesProcessus Recrutement.2 PDFAna RotaruNo ratings yet

- RSE-Concepts de Base - QCMDocument3 pagesRSE-Concepts de Base - QCMlahoucine.ihander0% (1)

- GCPaout19 SommaireDocument13 pagesGCPaout19 Sommairelouveau.antoineNo ratings yet

- DEVIS QUANTITATIF CENTRE D'ALPHABETISATION - ST - VideDocument7 pagesDEVIS QUANTITATIF CENTRE D'ALPHABETISATION - ST - VideBadara NdiayeNo ratings yet

- BiophysiqDocument69 pagesBiophysiqyouness.khalfaouiNo ratings yet

- Ite Missa Est, Op6-FS, VS, PX-PML PDFDocument28 pagesIte Missa Est, Op6-FS, VS, PX-PML PDFbry kaligayahanNo ratings yet

- PNEU - Les Pré-Actionneurs - Les Distributeurs - TP1.V2 (AP 1 À 5) - Nv4Document5 pagesPNEU - Les Pré-Actionneurs - Les Distributeurs - TP1.V2 (AP 1 À 5) - Nv4Maxime PeridyNo ratings yet

- CPS Cablage Info TéléphonieDocument13 pagesCPS Cablage Info TéléphonieAhmed LahroussiNo ratings yet

- 2022mulh5427 These ColardDocument190 pages2022mulh5427 These ColardReda AveNo ratings yet

- Chapitre 1 Normalisation Reperage Installation Electrique PDFDocument23 pagesChapitre 1 Normalisation Reperage Installation Electrique PDFstoufa73No ratings yet

- Chapitre 5 - Le Traitement Et L'épuration Des EauxDocument5 pagesChapitre 5 - Le Traitement Et L'épuration Des Eauxرضا بونعاسNo ratings yet

- 1491 Diuus Plato - Opera Platonis Ed. Marsilio Ficino .VeniceDocument3 pages1491 Diuus Plato - Opera Platonis Ed. Marsilio Ficino .VenicesalvadorNo ratings yet

- Mostafa Ami - Fiches 4 A.P - Séquence 2 - Projet 1 - Je Vais Chez MadjidDocument31 pagesMostafa Ami - Fiches 4 A.P - Séquence 2 - Projet 1 - Je Vais Chez MadjidNädïne Fërhätï100% (3)

- 9 GuebayaDocument10 pages9 GuebayaYassine RabhiNo ratings yet

- PFE - Corrigé Jusqu'a La Page 21 - 121427Document64 pagesPFE - Corrigé Jusqu'a La Page 21 - 121427Youness HriouichNo ratings yet

- Fibre OptiqueDocument100 pagesFibre OptiqueAbdelilah AchouriNo ratings yet

- Merged 20200609 172757.TextMarkDocument6 pagesMerged 20200609 172757.TextMarkAngeauden DidoNo ratings yet

- Commence Ici: Guide en Bref: Détails Sur Les Piles: +: On DanseDocument1 pageCommence Ici: Guide en Bref: Détails Sur Les Piles: +: On DansephigeramNo ratings yet

- Compte-Rendu 2 POODocument3 pagesCompte-Rendu 2 POOAbdelbaki MissaouiNo ratings yet

- RÉDACTION Niveau 6è Année Ou CM2Document17 pagesRÉDACTION Niveau 6è Année Ou CM2Sangaré Hamadou100% (4)