Professional Documents

Culture Documents

Support Microprocesseurs PDF

Uploaded by

RidhaNommaneOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Support Microprocesseurs PDF

Uploaded by

RidhaNommaneCopyright:

Available Formats

Support de cours

Microprocesseurs et

microcontrleurs

Niveau : deuxime anne Licence applique gnie lectrique

parcours Automatismes et Informatique Industrielle

UE : 4.4

Circuits programmables

Code ECUE : 4.4.1

Ralis par : MABROUK Issam

Anne universitaire 2013-2014

REPUBLIQUE TUNISIENNE

Ministre de lenseignement suprieur et de la recherche scientifique

Direction gnrale des tudes technologiques

ISET Rades

Avant propos

Ce cours est ddi aux tudiants de lISET inscrits en deuxime anne licence

applique en gnie lectrique (parcours Automatismes et Informatique Industrielle). Il

est enseign en tant que cours intgr en semestre 4 pour une charge horaire totale de

22,5 heures soit une sance dune heure et demie par semaine. Il porte sur des notions

avances de ltude et de la programmation des microprocesseurs, et en particuliers le

8086 dIntel, ainsi que sur des notions de bases sur les microcontrleurs.

Nous commenons le cours avec une prsentation gnrale des

microprocesseurs anctres des microprocesseurs actuels, dans un second lieu, nous

traitons les architectures et les fonctions de base des microprocesseurs, passant par une

explication des diffrents types de mmoires. Une fois les connaissances de bases

assimiles, nous continuant avec ltude et la programmation du 8086 dIntel ainsi que

la manire dont ce dernier sinterface avec les modules externes tels que linterface

parallle 8255 et linterface srie 8250. Nous terminons ce cours avec ltude et la

programmation des microcontrleurs en prenant comme exemple le PIC 16F 877 de

Microchip.

Ce support est ralis en collaboration avec dautres enseignants qui nont pas

hsit porter leur soutien et leur savoir faire commencer par Mme CHAOUCH

Khadouja enseignant technologue lISET de Rades ainsi que Mr RHAIEM Ramzi

ancien assistant technologue lISET de Rades.

Enfin, ce cours est entirement disponible sur le Web, ladresse suivante :

http://issammabrouk.weebly.com/ ou vous trouverez galement dautres cours et

documents utiles.

Sommaire

Titre Page Volume

horaire

Avant propos

Sommaire

Liste des figures

Liste des tableaux

1. Gnralits sur les microprocesseurs 1

1.1. Dfinition d'un microprocesseur 1

1.2. Historique 1

1.3. LES ANCTES 3

1.3.1. Les 4 bits : 3

1.3.2. Les 8 bits : 3

1.3.3. Les 16 bits 4

2. Architecture et fonctions de base des microprocesseurs 5

2.1. Arc!itecture de "#se d$un ordin#teur %

2.2. Structure de &# mmoire princip#&e '()* +

2.3. L$unit #rit!mtique et &o,ique +

2.-. L$unit de comm#nde et de contr.&e /

2.%. Les re,istres et &'#ccumu&#teur 0

2.+. E1cution d$un pro,r#mme 2 0

3. Les mmoires 10

3.1. 3r,#nis#tion d$une mmoire 14

3.2. C#r#ctristiques d$une mmoire 11

3.3. Diffrents t5pes de mmoires 12

3.3.1. Les ROMs : Mmoire Morte, la ROM (Read Only Memory) 12

3.3.2. Les RAMs : Mmoire Vive, la RAM (Random Access Memory) 13

. !tude et programmation d"un microprocesseur #$0$%& 15

-.1. LE (6C3)3CESSE7 040+ 1%

4.2. La segmentation de la mmoire 1/

4.3. Les registres du 8086 10

4.3.1. Les registres gnraux 19

4.3.2. Les registres d'adressage (offset) 19

4.3.3. Les registres de segments 19

4.3.4. Le registre d'tat (flags) 2

-.-. Les modes d$#dress#,e 21

-.%. T#i&&e des c!#n,es #8ec &# mmoire 23

1! 3

4h 30

3h

6h

4.6. La pile : 2-

4.6.1. Notion de pile 24

4.6.2. "nstru#tions $%&' et $($ 24

4.6.3. )egistres && et &$ 2*

-./. Les instructions du 040+ 2%

4.+.1. Les instru#tions de transfert 2*

4.+.2. Les instru#tions ,rit!mti-ues 26

4.+.3. Les instru#tions logi-ues 2+

4.+.4. Les mas-ues logi-ues : 28

4.+.*. Les instru#tions de d#alage 29

4.+.6. "nstru#tions agissant sur les indi#ateurs 3

4.7.7. Les instructions de contrle de boucle 31

4.+.8. Les instru#tions de bran#!ement 31

-.0. )rocdures 33

4.8.1. .otion de /ro#dure 33

4.8.2. 0#laration d1une /ro#dure 34

-.9. (t!odes de pro,r#mm#tion 3-

4.9.1. Les ta/es de ralisation 34

4.9.2. Langage ma#!ine et assembleur : 34

4.9.3. )alisation /rati-ue d1un /rogramme : 34

4.9.4. &tru#ture d1un fi#!ier sour#e en assembleur : 3*

4.9.*. 0ire#ti2es /our l1assembleur : 3*

-.14. Les interruptions 3+

4.1.1. Les interru/tions matrielles (externes) 36

4.1.2. Les interru/tions logi#ielles 36

4.1.3. Les ex#e/tions 3+

5. 'nterfa(age des microprocesseurs )$

%.1. Adress#,e des ports d$E:S 39

%.2. L$interf#ce p#r#&&;&e 02%% -1

%.3. L$interf#ce srie 02%4 -2

%. !tude et programmation des microcontr*leurs 5

+.1. Dfinition -%

+.2. Les compos#nts d$un microcontr.&eur 2 ')6C 1+<0//* -+

6.2.1. $rsentation du $"3 1648++ 46

6.2.2. (rganisation de la mmoire du 1648++ 48

6.2.3. $rsentation de -uel-ues registres internes 49

6.2.4. L5& $()6& 5.6)55 7 &()6"5 *

6.2.*. 3(.85)6"&&5%) ,70 *1

6.2.6. Les timers *3

6.2.+. L5 3'"5. 05 9,)05 (Le :at#!dog 6imer :06) *3

+.3. Les t#pes de r#&is#tion d$une #pp&ic#tion = "#se de pic 2 %-

6.3.1. Les outils n#essaires *4

6.3.2. ,r#!ite#ture d1un /rogramme 3 /our mi;ro3 **

6.3.3. mi<ro3 et exem/le *6

6.3.4. =uel-ues a//li#ations #lassi-ues : *+

+ibliographie

3h

4h 30

Liste des figures

Figure 1: Architecture Von Neumann 1

Figure 2: Architecture de base d'un ordinateur 5

Figure 3: structure de la mmoire principale 6

Figure 4: Unit arithmtique et logique 7

Figure 5: exemples d'instructions dans leurs diffrentes formes 9

Figure 6: schma d'une mmoire 10

Figure 7: Chronogramme dun cycle de lecture 11

Figure 8: les mmoires ROM 12

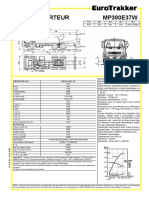

Figure 9: brochage du 8086 16

Figure 10: fonctionnement dune pile 25

Figure 11: fonctionnement d'une procdure 33

Figure 12: les interfaces d'E/S 38

Figure 13: Schma synoptique d'un circuit d'E/S 39

Figure 14: adressage des E/S par le 8086 40

Figure 15: Brochage du 8255 41

Figure 16: schma synoptique du 8255 42

Figure 17: exemple de transmission srie 43

Figure 18: Principe dune interface srie 43

Figure 19: les composants d'un microcontrleur 46

Figure 20: organisation de l'espace mmoire du 16F877 48

Figure 21: Brochage du 16F877 48

Figure 22: le registre OPTION 49

Figure 23: configuration des ports d'E/S 51

Figure 24: configuration du registre ADCON1 53

Figure 25: Schma sous ISIS 57

Liste des tableaux

Tableau 1: les principaux microprocesseurs 4 bits 3

Tableau 2: les principaux microprocesseurs 8 bits 4

Tableau 3:description des broches du 8086 17

Tableau 4: segmentation de la mmoire 17

Tableau 5: segments par dfaut 20

Tableau 6: registres d'tats 20

Tableau 7: les abrviations utilises 21

Tableau 8: lecture et criture d'un port d'E/S 40

Tableau 9: Configuration des registres du 8255 42

1. Gnralits sur les microprocesseurs

1.1. Dfinition d'un microprocesseur

On peut donner du terme microprocesseur la dfinition suivante: "Composant

renfermant dans un seul botier l'unit de contrle et l'unit de traitement d'une

machine informatique de type VON NEUMANN"

Cette dfinition exclut volontairement :

Les architectures non VON NEUMANN

Les microcontrleurs qui incluent d'autres composantes des systmes

informatiques (mmoire, entres/sorties)

Ces composants constituent luni

tlphones GSM etc.

1.2. Historique

L'histoire des microprocesseurs est intimement lie celle de la technologie

des semi-conducteurs dont voici les

1947 Invention du transistor

1958 TEXAS INSTRUMENTS produit le

1961 Mise au point des technologies bipolaires TTL et ECL

1964 Intgration petite chelle (SSI de 1 10 transistors)

1965 Intgration moyenne chelle (MSI de 10 500 transistors)

1970 Mise au

1971 Intgration grande chelle (LSI de 500 20 000 transistors)

1985 Intgration trs grande chelle (VLSI plus de 20000 transistors)

Gnralits sur les microprocesseurs

Dfinition d'un microprocesseur

On peut donner du terme microprocesseur la dfinition suivante: "Composant

dans un seul botier l'unit de contrle et l'unit de traitement d'une

machine informatique de type VON NEUMANN" (Figure 1)

Figure 1: Architecture Von Neumann

Cette dfinition exclut volontairement :

Les architectures non VON NEUMANN

Les microcontrleurs qui incluent d'autres composantes des systmes

informatiques (mmoire, entres/sorties)

constituent lunit centrale des ordinateurs, des serveurs, des

Historique

L'histoire des microprocesseurs est intimement lie celle de la technologie

conducteurs dont voici les principales tapes :

1947 Invention du transistor

1958 TEXAS INSTRUMENTS produit le 1er circuit intgr (CI)

1961 Mise au point des technologies bipolaires TTL et ECL

1964 Intgration petite chelle (SSI de 1 10 transistors)

1965 Intgration moyenne chelle (MSI de 10 500 transistors)

1970 Mise au point de la technologie MOS

1971 Intgration grande chelle (LSI de 500 20 000 transistors)

1985 Intgration trs grande chelle (VLSI plus de 20000 transistors)

1

Gnralits sur les microprocesseurs

On peut donner du terme microprocesseur la dfinition suivante: "Composant

dans un seul botier l'unit de contrle et l'unit de traitement d'une

Les microcontrleurs qui incluent d'autres composantes des systmes

t centrale des ordinateurs, des serveurs, des

L'histoire des microprocesseurs est intimement lie celle de la technologie

er circuit intgr (CI)

1961 Mise au point des technologies bipolaires TTL et ECL

1964 Intgration petite chelle (SSI de 1 10 transistors)

1965 Intgration moyenne chelle (MSI de 10 500 transistors)

1971 Intgration grande chelle (LSI de 500 20 000 transistors)

1985 Intgration trs grande chelle (VLSI plus de 20000 transistors)

Chapitre I : Gnralits sur les microprocesseurs

2

Cest lapparition de la technologie CMOS permettant un grand degr

dintgration qui a ouvert la voie la fabrication de composants capables de contenir

lunit de contrle et lunit de traitement dun ordinateur sur une seule puce.

Le premier microprocesseur a t fabriqu par INTEL en 1971. C'tait un 4

bits baptis 4004 destin quiper des calculatrices de bureau. En 1972 INTEL

produit le premier microprocesseur 8 bits baptis 8008 par rfrence au prcdent. Ce

microprocesseur tait destin rpondre un contrat de fabrication d'un terminal. En

ralit le 8008 s'est rvl trop lent pour satisfaire le cahier des charges du terminal et

INTEL a dcid de tenter le lancement de ce produit sur le march grand public.

L'norme succs de cette initiative fut l'origine de la fabrication massive des

microprocesseurs. Le 8008 est constitu de 3300 transistors et effectue 60000

instructions par seconde grce une horloge 300KHz.

A la suite du succs du 8008, INTEL produisit, ds 1974, le 8080 qui

constituera le premier lment de la future famille de microprocesseurs de ce

fabriquant. Fort de ses 6000 transistors, le 8080, dot d'une horloge 2MHz effectue

640000 instructions par seconde. En 1974, MOTOROLA, autre fondeur de silicium,

dcide de lancer le 6800 qui constituera lui aussi le dbut d'une grande famille.

Les annes 70 voient alors apparatre de petites entreprises de fabrication de

microprocesseurs parfois constitues par des transfuges des deux grandes compagnies.

On peut notamment citer MOS Technologies avec son 6502 trs inspir du 6800 mais

vendu seulement 25$ et ZILOG avec son Z80 qui constitue une amlioration

technique du 8080 (augmentation du nombre de registres, simplification de

l'alimentation...). Les autres grands constructeurs (TEXAS INSTRUMENT,

FAIRCHILD, RCA, SIGNETICS etc.) se lanceront aussi dans ce march.

Ces composants seront la base des premiers micro-ordinateurs tant

personnels (ALTAIR 8800 de MITS avec un 8080, TRS80 de TANDY avec un Z80

et le tout premier APPLE avec un 6502) que professionnels (EXORCISER de

MOTOROLA et multiples constructeurs dveloppant autour du format de carte S100

pour 8080 et Z80).

On peut remarquer que la conception mme du composant avait t chez

certains constructeurs (MOTOROLA, MOS Technologies ) plus guide par des

considrations informatiques qu'lectroniques (possibilit de tests selon la

reprsentation des nombres, sauvegarde automatique de contexte, distinction entre

interruption matrielle et logicielle...). Tandis que d'autres (INTEL, ZILOG )

avaient opt pour une approche plus matrielle (test de parit, pas de sauvegarde

automatique de contexte pour prendre en compte les interruptions plus rapidement,

rafrachissement de mmoires dynamiques).

Chapitre I : Gnralits sur les microprocesseurs

3

1.3. LES ANCTES

Les microprocesseurs 4 et 8 et 16 bits font dj partie du pass, nanmoins une

connaissance de ces microprocesseurs nous permet davoir une ide sur lvolution

qua connue la technologie et son impact sur ces derniers qui ont permis ceux

daujourdhui dexister.

1.3.1. Les ! "its #

Le Tableau 1 illustre les principaux microprocesseurs 4 bits :

Tableau 1: les principaux microprocesseurs 4 bits

Le 4004, apparu en Mars 1971, intgre 2250 transistors et est dot d'une

horloge 740KHz. Il traite des donnes sur 4 bits bien que la mmoire soit organise

en mots de 8 bits. Le jeu d'instructions comporte 46 instructions codes sur 8 bits.

La mmoire maximale adressable est de 1Ko pour les donnes (RAM) et 4Ko

pour le code (ROM). Le 4004 possde 16 registres de 4 bits utilisables aussi comme 8

registres de 8 bits. Il gre les appels de sous programmes par une pile interne 4

niveaux.

1.3.2. Les $ "its #

Le Tableau 2 prsente les principaux microprocesseurs 8 bits.

L'architecture interne de ces microprocesseurs est trs simple et directement

calque sur larchitecture de VON NEUMANN.

Constructeur

Rfrence

INTEL

4004

INTEL

4040

ROCKWELL

PPS4

FAIRCHILD

PPS25

No!re "#$nstruct$ons 4% %0 50 &5

Te's "#(""$t$on entre

re)$stres *en +(s,

- - 5 .

Es'(ce o$re 4K -K 4K %/5K

Re)$stres "#us()e )nr(0 1% 24 4 1

Chapitre I : Gnralits sur les microprocesseurs

4

Tableau 2: les principaux microprocesseurs 8 bits

1.3.3. Les 1% "its

L'Intel 8086 (galement appel iAPX 86) est un microprocesseur 16 bits

fabriqu par Intel partir de 1978. C'est le premier processeur de la famille x86, qui

est devenue l'architecture de processeur la plus rpandue dans le monde des

ordinateurs personnels, stations de travail et serveurs informatiques.

Il fut lanc en mai 1978 au prix de 360 dollars. Il est bas sur des registres 16

bits, et dispose d'un bus externe de donnes de 16 bits et d'un bus d'adresse de 20 bits,

qui lui permet d'adresser 1 Mio. Il contient 29 000 transistors gravs en 3 m. Sa

puissance de calcul varie de 0,33 MIPS (lorsqu'il est cadenc 4.77 MHz comme

dans l'IBM PC) jusqu' 0,75 MIPS pour la version 10 MHz.

Le 8086 a t conu et commercialis comme tant compatible et permettant

l'utilisation du mme langage assembleur que pour le 8008,8080, ou 8085 de manire

ce que l'excution des codes sources ne demande que peu voire aucune

modifications pour le 8086, Cependant, la conception du 8086 a t conu de manire

a support un traitement complet du 16 bits, au lieu des capacits 16 bits assez

basique du 8080/8085.

Constructeur

Rfrence

INTEL

-00-

INTEL

-0-0

INTEL

-0-5

2OTORO

LA

%-00

3ILO4

3-0

2OS

Tec5no0o)$es

%502

ROCKWELL

PPS-

NATIONAL

SC62P

No!re "#$nstruct$ons 4- %& 71 71 %& 71 &0 50

Te's "#(""$t$on entre

re)$stres

12/5 8

20

1/. 8 2 1/. 2 1/% 2 4 5 8 25

Es'(ce o$re 1%K %4K %4K %4K %4K %4K .2K %4K

Re)$stres "#us()e

)nr(0

7 7 7 . 17 . . %

No!re "e tr(ns$stors ..00 4000 %200 4000

Hor0o)e *en 2H9, 0/.

2 ou

2/%7 ou

./125

./5 ou

%

1 ou 1/5

ou 2

Anne 1&72 1&74 1&7% 1&74 1&7% 1&75 1&7% 1&7%

5

2. Architecture et fonctions de base

des microprocesseurs

Nous allons au cours de ce chapitre nous pencher sur larchitecture des

microprocesseurs ainsi que leurs fonctions de base.

2.1. Arc&itecture de "'se d(un ordin'teur

Larchitecture, dite architecture de Von Neumann dcompose lordinateur en

quatre parties distinctes : (Figure 2)

Le processeur est compos dune unit arithmtique et logique (UAL ou

ALU en anglais) ou unit de traitement : son rle est deffectuer les

oprations de base et dune unit de contrle, charge du squenage des

oprations ;

Les registres qui sont des petites mmoires de travail.

La mmoire principale qui contient la fois les donnes et le programme

excut par lunit de contrle.

Les dispositifs dentre-sortie, qui permettent de communiquer avec le

monde extrieur.

Les diffrents composants sont relis par des bus.

Mmoire principale

Processeur

Registres

Unit de

traitement (UAL)

Unit de

commande ET

DE contrle

programme Donnes

Unit dE/S

Figure 2: Architecture de base d'un ordinateur

Chapitre II : Architecture et fonctions de base des microprocesseurs

6

2.2. Structure de )' mmoire princip')e *+,-

La mmoire est divise en emplacements (des cases mmoires contigus) de

taille fixe (par exemple huit bits) utiliss pour stocker instructions et donnes. En

principe, la taille dun emplacement mmoire pourrait tre quelconque ; en fait, la

plupart des ordinateurs en service aujourdhui utilisent des emplacements mmoire

dun octet ( byte en anglais, soit huit bits, unit pratique pour coder un caractre

par exemple).

Seul le processeur peut modifier l'tat de la mmoire

.

Chaque emplacement

mmoire conserve les informations que le processeur y crit jusqu' coupure de

l'alimentation lectrique, o tout le contenu est perdu (contrairement au contenu des

mmoires externes comme les disquettes et disques durs).

Les seules oprations possibles sur la mmoire sont :

criture d'un emplacement : le processeur donne une valeur et une adresse, et

la mmoire range la valeur l'emplacement indiqu par l'adresse;

lecture d'un emplacement : le processeur demande la mmoire la valeur

contenue l'emplacement dont il indique l'adresse. Le contenu de

l'emplacement lu reste inchang.

2.3. L(unit 'rit&mtique et )o.ique

L'unit arithmtique et logique est une unit combinatoire permettant de

raliser plusieurs fonctions sur un couple d'entre. Elle permet d'excuter plusieurs

fonctions de type arithmtique (addition, soustraction, ...). Elle peut aussi excuter

plusieurs fonctions logiques (et, ou, ...). Figure 4 montre les diffrents lments

fournis l'unit arithmtique et logique, et les diffrents lments fournis par l'unit

arithmtique et logique.

05h 0002h

0001h

0 1 1 0 1 0 0 1 0000h

Contenu de la

mmoire

Adresse de la case

mmoire

Largeur des cases

mmoires gnralement

=8bits

Figure 3: structure de la mmoire principale

Chapitre II : Architecture et fonctions de base des microprocesseurs

7

Figure 4: Unit arithmtique et logique

Une commande mode permet de spcifier le type de calcul (arithmtique ou

logique). La commande fonction sur k bits, permet d'indiquer l'une parmi les 2

k

fonctions possibles dans le mode considr. La fonction slectionne s'appliquera sur

les donnes A et B pour fournir le rsultat F. L'entre Cin sera utilise dans le mode

arithmtique comme retenue entrante, tandis que la sortie Cout sera la retenue sortante

dans ce mme mode arithmtique. Dans le cas du mode logique, tant donn que la

retenue entrante ne sert pas, nous pourrons utiliser cette entre comme un bit de

commande supplmentaire, de manire obtenir 2

k+1

fonctions logiques diffrentes.

2.!. L(unit de comm'nde et de contr/)e

C'est l'unit de control qui supervise le droulement de toutes les oprations au

sein du Processeur. Elle est constitue principalement de :

l'horloge : C'est l'horloge qui gnre les signaux qui permettent le cadencement et

la synchronisation de toutes les oprations. Attention, l'horloge n'est pas une

montre au sens commun du terme, c'est juste un signal carr qui a une frquence

fixe (3 Ghz par exemple), a chaque coup (front) d'horloge, le microprocesseur (qui

ne l'oublions pas n'est qu'un circuit lectronique) ralise une tache lmentaire.

L'excution d'une instruction ncessite plusieurs coups d'horloges.

Le compteur programme PC : Le compteur programme (PC : program counter)

est un registre (pointeur) qui contient l'adresse de la case mmoire o est stocke

le prochain lment d'instruction qui devra tre charg dans le processeur pour

tre analys et excut. Au dbut de l'excution d'un programme, le PC est

initialis par le systme d'exploitation l'adresse mmoire o est stocke la

premire instruction du programme. Le compteur programme est incrment

automatiquement chaque fois qu'un lment d'instruction est charge dans le

processeur

Le registre d'instruction RI : C'est l o le CPU stocke l'instruction en cours

d'excution.

Le dcodeur : C'est lui qui va "dcoder" l'instruction contenue dans RI et gnrer

les signaux logiques correspondant et les communiquer au squenceur.

Chapitre II : Architecture et fonctions de base des microprocesseurs

8

Le squenceur : Il gre le squencement des oprations et gnre les signaux de

commande qui vont activer tous les lments qui participeront l'excution de

l'instruction et spcialement l'ALU.

Le registre d'tat : Le registre d'tat est form de plusieurs bits appels drapeaux

ou indicateurs (Flags) qui sont positionns par l'ALU aprs chaque opration. Par

exemple lindicateur Z indique quand il est positionn que le rsultat de

l'opration est gal Zro. Lindicateur C indique que l'opration a gnr une

retenue. Le bit N indique que le rsultat est ngatif

On dispose d'un jeu d'instructions conditionnes par l'tat de diffrents

drapeaux

2.0. Les re.istres et )''ccumu)'teur

Le processeur utilise toujours des registres, qui sont des petites mmoires

internes trs rapides d'accs utilises pour stocker temporairement une donne, une

instruction ou une adresse. Chaque registre stocke 8, 16 ou 32 bits.

Le nombre exact de registres dpend du type de processeur et varie

typiquement entre une dizaine et une centaine.

Parmi les registres, le plus important est le registre accumulateur, qui est

utilis pour stocker les rsultats des oprations arithmtiques et logiques.

L'accumulateur intervient dans une proportion importante des instructions.

Par exemple, examinons ce qu'il se passe lorsque le processeur excute une

instruction comme ``Ajouter 5 au contenu de la case mmoire d'adresse 180'' :

Le processeur lit et dcode l'instruction;

le processeur demande la mmoire la contenu de l'emplacement 180;

la valeur lue est range dans l'accumulateur;

l'unit de traitement (UAL) ajoute 5 au contenu de l'accumulateur;

le contenu de l'accumulateur est cris en mmoire l'adresse 180.

C'est l'unit de commande qui dclenche chacune de ces actions dans l'ordre.

L'addition proprement dite est effectue par l'UAL.

2.%. E1cution d(un pro.r'mme #

Le travail d'un processeur est d'excuter des programmes. Un programme est

une suite d'instructions crites une par ligne. Une instruction peut tre plus ou moins

sophistique selon le langage utilis. Pour un langage de bas niveau comme

l'assembleur, une instruction ralise une tache lmentaire comme une addition par

exemple. Avec un langage de haut niveau comme le C++, une instruction peut raliser

un ensemble de taches qui ncessiterait plusieurs instructions en Assembleur.

Un processeur quel qu'il soit sait excuter un ensemble bien dfini de codes

machines (jeux d'instructions). Chaque code machine est un nombre binaire de

quelques octets, il correspond une instruction lmentaire bien dfinie. Sur papier,

on a pris l'habitude de les reprsenter en hexadcimal pour faciliter.

Chapitre II : Architecture et fonctions de base des microprocesseurs

9

Figure 5: exemples d'instructions dans leurs diffrentes formes

Par exemple, l'instruction (assembleur) MOV BP,41h qui signifie : placer le

nombre 41h dans le registre BP est code (en hexadcimal) par les trois octets BD 41

00 , Dans la suite de ce cours, nous dsignerons ces octets par : lments d'instruction.

Quand on veut crire un programme, on dispose d'un choix trs important de

langages de programmation diffrents les uns des autres : Assembleur, Basic/Qbasic,

Pascal, C/C++, Visual Basic, Visual C++, Delphi, Java,

En fait, les lignes de programme que nous crivons constituent ce qu'on

appelle un programme source qui sera stock dans un fichier texte dont l'extension

dpend du langage choisi (test.pas pour le pascal, test.cpp pour le c++ etc.)

Ces programmes sources sont comprhensibles par nous mais pas par le

processeur. Pour que le processeur puisse les comprendre il faut les traduire

(compiler) en langage machine qui est une suite de codes machine. Sur les PCs, se

sont les fichiers avec l'extension .exe (test.exe). Chaque langage de programmation a

son compilateur qui permet de transformer le programme source en un programme

excutable comprhensible par le processeur. Tous les excutables se ressemblent et

le processeur ne sait pas avec quel langage ils ont t crits.

Avec un langage de haut niveau comme le C++, une instruction que nous

crivons peut tre trs sophistique. C'est le compilateur C++ qui la traduit en un

ensemble d'instructions lmentaires comprhensible par le processeur.

L'intrt du langage assembleur est que chaque instruction que nous crivons

correspond une instruction lmentaire du processeur. C'est comme si on travaillait

directement en langage machine. Ainsi, on sait exactement tout ce que fait le

processeur lors de l'excution d'un programme.

Quand on demande l'excution d'un programme, celui-ci est charg par le

systme d'exploitation ( partir du disque dur) dans une zone de la mmoire RAM.

Celle-ci tant organise en octets, chaque lment d'instruction est stock dans une

position mmoire. L'adresse (le numro) de la case mmoire de dbut est

communique au processeur pour qu'il commence l'excution au bon endroit.

10

3. Les mmoires

Une mmoire est un circuit semi-conducteur permettant denregistrer, de

conserver et de restituer des informations (instructions et variables). Cest cette

capacit de mmorisation qui explique la polyvalence des systmes numriques et

leur adaptabilit de nombreuses situations. Les informations peuvent tre crites ou

lues. Il y a criture lorsqu'on enregistre des informations en mmoire, lecture

lorsqu'on rcupre des informations prcdemment enregistres.

3.1. 2r.'nis'tion d(une mmoire

Avec une adresse de n bits il est possible de rfrencer au plus 2n cases

mmoire. Chaque case est remplie par un mot de donnes (sa longueur m est toujours

une puissance de 2). Le nombre de fils dadresses dun botier mmoire dfinit donc

le nombre de cases mmoire que comprend le botier. Le nombre de fils de donnes

dfinit la taille des donnes que lon peut sauvegarder dans chaque case mmoire.

En plus du bus dadresses et du bus de donnes, un botier mmoire comprend

une entre de commande qui permet de dfinir le type daction que lon effectue avec

la mmoire (lecture/criture) et une entre de slection qui permet de mettre les

entres/sorties du botier en haute impdance.

On peut donc schmatiser un circuit mmoire par la Figure 6 o lon peut

distinguer :

les entres dadresses

les entres de donnes

les sorties de donnes

les entres de commandes :

- une entre de slection de lecture ou dcriture. (R/W)

- une entre de slection du circuit. (CS)

Figure 6: schma d'une mmoire

Une opration de lecture ou dcriture de la mmoire suit toujours le mme cycle (Figure 7) :

1. slection de ladresse

2. choix de lopration effectuer (R/W)

3. slection de la mmoire (CS = 0)

4. lecture ou criture la donne

Chapitre III : Les mmoires

11

Figure 7: Chronogramme dun cycle de lecture

3.2. C'r'ctristiques d(une mmoire

La capacit : cest le nombre total de bits que contient la mmoire. Elle

sexprime aussi souvent en octet.

Le format des donnes : cest le nombre de bits que lon peut mmoriser par

case mmoire. On dit aussi que cest la largeur du mot mmorisable.

Le temps daccs : cest le temps qui s'coule entre l'instant o a t lance

une opration de lecture/criture en mmoire et l'instant o la premire

information est disponible sur le bus de donnes.

Le temps de cycle : il reprsente l'intervalle minimum qui doit sparer deux

demandes successives de lecture ou d'criture.

Le dbit : cest le nombre maximum d'informations lues ou crites par

seconde.

Volatilit : elle caractrise la permanence des informations dans la mmoire.

L'information stocke est volatile si elle risque d'tre altre par un dfaut

d'alimentation lectrique et non volatile dans le cas contraire.

Les mmoires utilises pour raliser la mmoire principale dun systme

microprocesseur sont des mmoires semi-conducteur. On a vu que dans ce type de

mmoire, on accde directement n'importe quelle information dont on connat

l'adresse et que le temps mis pour obtenir cette information ne dpend pas de

l'adresse. On dira que l'accs une telle mmoire est alatoire ou direct.

A l'inverse, pour accder une information sur bande magntique, il faut

drouler la bande en reprant tous les enregistrements jusqu' ce que l'on trouve celui

que l'on dsire. On dit alors que l'accs l'information est squentiel. Le temps

d'accs est variable selon la position de l'information recherche. L'accs peut encore

tre semi-squentiel : combinaison des accs direct et squentiel.

Pour un disque magntique par exemple l'accs

l'accs au secteur est squentiel.

3.3. Diffrents t3pes de mmoires

3.3.1. Les ROMs :

C'est une mmoire lecture seule (Read Only Memory), lcriture ncessite un

programmateur ou une procdure p

qu'elle contient sont conserves en permanence, mme lors dune coupure

dalimentation. Nous vous proposons la suite les diffrents types de mmoires ROM

(Figure 8)

ROM (Read Only Memory)

Masque de fabrication

- diodes disposes sur un rseau de lignes et de colonnes.

- ou transistors dont sont

PROM fusibles ou FPROM (Programmable Read Only Memory ou Fuse

PROM) Ralise partir de transistors bipolaires dont leurs liaisons entre

l'metteur et la colonne sont effectues

EPROM (Erasable Programmable Read Only Memory)

avantages de la PROM avec un plus, qui est l'effacement des donnes par

l'utilisateur.

Le terme EPROM correspond un ensemble de composants. Abusivement on

utilise ce terme pour les UVPR

$)(>

5$)(>

%8$)(>

Chapitre III : Les mmoires

Pour un disque magntique par exemple l'accs la piste est direct, puis

l'accs au secteur est squentiel.

Diffrents t3pes de mmoires

Les ROMs : Mmoire Morte, la ROM (Read Only Memory)

C'est une mmoire lecture seule (Read Only Memory), lcriture ncessite un

programmateur ou une procdure plus longue que pour les RAMs. Les informations

qu'elle contient sont conserves en permanence, mme lors dune coupure

Nous vous proposons la suite les diffrents types de mmoires ROM

Figure 8: les mmoires ROM

ROM (Read Only Memory)

Masque de fabrication :

diodes disposes sur un rseau de lignes et de colonnes.

ou transistors dont sont effectues des coupures leurs bases.

PROM fusibles ou FPROM (Programmable Read Only Memory ou Fuse

Ralise partir de transistors bipolaires dont leurs liaisons entre

l'metteur et la colonne sont effectues par l'intermdiaire d'un fusible.

EPROM (Erasable Programmable Read Only Memory): Elles

avantages de la PROM avec un plus, qui est l'effacement des donnes par

Le terme EPROM correspond un ensemble de composants. Abusivement on

utilise ce terme pour les UVPROM.

mmoires

mortes

$)(>

%8$)(> 55$)(>

55$)(>

4L,&'

(6$ 4$)(>

12

la piste est direct, puis

Mmoire Morte, la ROM (Read Only Memory)

C'est une mmoire lecture seule (Read Only Memory), lcriture ncessite un

lus longue que pour les RAMs. Les informations

qu'elle contient sont conserves en permanence, mme lors dune coupure

Nous vous proposons la suite les diffrents types de mmoires ROM

effectues des coupures leurs bases.

PROM fusibles ou FPROM (Programmable Read Only Memory ou Fuse

Ralise partir de transistors bipolaires dont leurs liaisons entre

par l'intermdiaire d'un fusible.

Elles possdent les

avantages de la PROM avec un plus, qui est l'effacement des donnes par

Le terme EPROM correspond un ensemble de composants. Abusivement on

)(>

Chapitre III : Les mmoires

13

OTP MEMORY (One Time Programmable MEMORY): programmable une

seule fois laide dun programmateur (Rem : On utilise souvent le terme

PROM

UVPROM (EPROM effaable par une exposition aux ultraviolet U.V.)

Ce type de mmoire est plac dans un botier cramique avec fentre de quartz

effaable aux U.V.

EEPROM ou E2PROM (Erasable Electricaly PROM) : effaable

lectriquement.

Il existe des mmoires EEPROM accs parallle et des mmoires EEPROM

accs srie. Pour celle accs parallle, les donnes entrent et sortent sous

la forme dun octet.

Pour celles accs srie, les donnes entrent et sortent en srie en commenant

par le bit de poids fort des octets. La liaison srie utilise est de type synchrone

(SPI ou I2C). Dans ce cas, ces mmoires sont intressantes par leur faible

encombrement (botier DIP8), puisque ladresse et la donne sont transmis

sous forme srie. Toutefois le temps daccs aux donnes est alors

relativement long.

EPROM FLASH : effaable lectriquement, criture plus rapide que les

EEPROM mais effacement de toute la capacit de la mmoire en un coup.

3.3.2. Les RAMs : Mmoire Vive, la RAM (Random Access Memory)

Les mmoires RAM sont volatiles et accs direct (Accs alatoire en lecture

ou criture). Dans cette catgorie de mmoires on trouve :

Les mmoires RAM statiques (SRAM) dans lesquelles les informations sont

mmorises par une bascule de type D et conserves tant que l'alimentation est

prsente (mmoire volatile), elles sont ralises en technologie MOS ou

bipolaire.

Les mmoires RAM dynamiques (DRAM) qui utilisent un condensateur

comme cellule mmoire (un bit mmoris) de l'information. Cette information

tend se dgrader cause des courants de fuites, ce qui ncessite un

rafrachissement priodique.

C'est l'espace de travail pour les ordinateurs. C'est l que se recopient le

systme d'exploitation et les applications (programmes), stocks sur le disque dur, et

ou sont transforms vos documents avant sauvegarde sur une mmoire de masse.

Pour les systmes micro industriels cest lemplacement des donnes appeles

variables. Ces donnes peuvent correspondre des variables globales ou locales du

programme, ou des donnes de transmission ou de traitement (acquisition, valeurs

de sortie).

Chapitre III : Les mmoires

14

NOVRAM = (Non volatile RAM) : Mmoire de type SRAM associe une

pile de sauvegarde, ou systme de transfert vers une mmoire morte de type FLASH.

Leur cot capacit gale est suprieur aux SRAMs. Elles sont donc limites aux

applications micro contrleurs industriels ou il est indispensable de ne pas perdre les

donnes.

15

4. Etude et programmation dun

microprocesseur !"#"$%

Les premiers pc commercialiss au dbut des annes 1980 utilisaient le 8086,

qui est un microprocesseur 16bits. La gamme de microprocesseurs sui quipe les

micro-ordinateurs de type PC et compatibles sont les 80x86.

Chacun de ces processeurs, Le 80286, 80386, 80486 et Pentium (ou 80586) est

plus puissant que les prcdents : horloge plus rapide, bus de donnes plus large, de

nouvelles instructions sont ajoutes comme le calcul sur les rels et ajout de registres.

Chacun de ces microprocesseurs est compatible avec les modles prcdents.

On parle de compatibilit ascendante car un programme crit sur un 286 fonctionne

sur un 386 mais pas linverse.

Du fait de cette compatibilit, nous allons tudier et programmer le 8086,

utilis dans nos salles de Travaux Pratiques.

!.1. LE +4C2,2CESSE5 $6$%

Il se prsente sous forme d'un botier de 40 broches aliment par une alimentation

unique de 5V. (Figure 9: brochage du 8086)

Il possde un bus multiplex adresse/donne de 20 bits.

Le bus de donne occupe 16 bits ce qui permet d'changer des mots de 2 octets

Le bus d'adresse occupe 20 bits ce qui permet d'adresser 1 Mo (2

20

)

Il est entirement compatible avec le 8088, le jeu d'instruction est identique. La

seule diffrence rside dans la taille du bus de donnes, celui du 8088 fait

seulement 8 bits. Les programmes tourneront donc un peu plus lentement sur ce

dernier puisqu'il doit changer les mots de 16 bits en deux tapes.

Tous les registres sont de 16 bits, mais pour garder la compatibilit avec le

8085/8088, certains registres sont dcoups en deux et on peut accder sparment

la partie haute et la partie basse.

Chapitre IV : Etude et programmation dun microprocesseur (8086)

16

Figure 9: brochage du 8086

Le tableau suivant donne la description des diffrentes broches de 8086 :

CLK

Entre "u s$)n(0 ":5or0o)e ;u$ c("ence 0e fonct$onneent "u

$cro'rocesseur<

RESET Entre "e re$se 8 9ro "u $cro'rocesseur<

READ= Entre "e s>nc5ron$s(t$on (?ec 0( o$re<

TEST@ Entre "e s>nc5ron$s(t$on "u $cro'rocesseur ":un ?neent

eAtr$eur<

2N62B@ Entre "e c5o$A "u o"e "e fonct$onneent "u $cro'rocesseur C

2N C 2o"e $n$u<

2B C 2o"e (A$u<

N2I Entre "e "e(n"e ":$nterru't$on non (s;ue<

INTR Entre "e "e(n"e ":$nterru't$on (s;ue<

INTA@ Sort$e $n"$;ue 0( r'onse 8 une "e(n"e ":$nterru't$on<

HOLD et HLDA S$)n(uA "e 0:(ccDs "$rect o$re '(r 0e c$rcu$t D2A<

S0E<S7

S$)n(uA ":t(t "u F' en o"e STEP G= STEP *'(s 8 '(s,<

A0 <<< A1& S$)n(uA "e !us ":("resse "e 20 !$ts *12o es'(ce ("ress(!0e,<

D0 <<< D15 S$)n(uA "e !us "e "onnes "e 1% !$ts<

RD@ S$)n(0 "e "e(n"e "e 0ecture<

WR@ S$)n(0 "e "e(n"e ":cr$ture<

Chapitre IV : Etude et programmation dun microprocesseur (8086)

17

Tableau 3:description des broches du 8086

4.2. La segmentation de la mmoire

Le 8086 possde 20 bits d'adresse, il peut donc adresser 2

20

octets soit 1 Mo.

L'adresse de la premire case mmoire est 0000 0000 0000 0000 0000 celle de

la dernire casse est 1111 1111 1111 1111 1111 1111. Nous allons reprsenter les

adresses en hexadcimal, et notre 8086 peut donc adresser 1 Mo allant de 00000

FFFFF. Le problme qui se pose est comment reprsenter ces adresses au sein du P

puisque les registres ne font que 16 bits soit 4 digits au maximum en hexadcimal. La

solution adopte par Intel a t la suivante : Puisque avec 16 bits en peut adresser 2

16

octets = 65535 octets = 64 ko, La mmoire totale adressable de 1 Mo est fractionne

en pages de 64 ko appels segments. On utilise alors deux registres pour adresser une

case mmoire donne, Un registre pour adresser le segment qu'on appelle registre

segment et un registre pour adresser l'intrieur du segment qu'on dsignera par

registre d'adressage ou offset. Une adresse se prsente toujours sous la forme

segment: offset

A titre d'exemple, procdons au dcoupage de la mmoire en 16 segments qui

ne se chevauche pas.

Tableau 4: segmentation de la mmoire

Considrons la case mmoire d'adresse 20350, appele adresse absolue ou

adresse linaire. Cette case mmoire se situe dans le segment 2, son adresse relative

ce segment est 350, on peut donc la rfrencer par le couple segment: offset =

20000:350, Se pose maintenant le problme de la reprsentation de cette adresse au

sein du CPU car les registres de 16 bits ne peuvent contenir que 4 digits. S'il n'y a

26IO@ S$)n(0 "e s'(r(t$on ":(ccDs o$re ou 'ort C

26IO@ H 1 C (ccDs o$re<

26IO@ H 0 C (ccDs 'ort ":E6S

DEN Sort$e $n"$;ue ;ue 0:$nfor(t$on ;u$ c$rcu0e "(ns !us AD est une "onne<

DT6R@ Sort$e $n"$;ue 0e sens "e tr(nsfert "es "onnes sur 0( !us "e "onnesC

DT6R@ H 1 C 0e !us "e "onne en sort$e<

DT6R@ H 0 C 0e !us "e "onne en entre<

GHE@ S$)n(0 ":(ccDs "e 0:octet "u 'o$"s fort sur 0( !us *D- 6 D15,<

ALE

Sort$e $n"$;ue ;ue 0:$nfor(t$on ;u$ c$rcu0e "(ns !us AD est une

("resse<

Segment Adresse

dbut

Adresse

fin

Pointeur de

segment

Segment 0 00000 0FFFF 00000

Segment 1 10000 1FFFF 10000

Segment 2 20000 2FFFF 20000

Segment 14 E0000 EFFFF E0000

Segment 15 F0000 FFFFF F0000

Chapitre IV : Etude et programmation dun microprocesseur (8086)

18

aucun problme pour reprsenter 350 dans un registre d'offset, on ne peut pas

reprsenter 20000 dans un registre segment. La solution adopte par Intel est la

suivante :

Dans le registre segment, on crit l'adresse segment sans le chiffre de

faible poids Dans le registre d'adressage (d'offset) on crit l'adresse relative dans

le segment

Pour calculer l'adresse absolue qui sera envoye sur le bus d'adresse de

20 bits, le CPU procde l'addition des deux registres aprs avoir dcal le

registre segment d'un chiffre gauche :

x x x x 0 Segment

+ x x x x Offset

x x x x x Adresse absolue

Dans notre exemple, l'adresse de la case mmoire considre devient

2000:350 soit :

Segment = 2000

Offset = 350

'adresse a!sol"e est calc"le ainsi :

2 0 0 0 0 Segment

+ 0 3 5 0 Offset

2 0 3 5 0 Adresse absolue

Remarque : Les zones rserves aux segments ne sont pas exclusives, elles

peuvent se chevaucher. La seule rgle respecter lors du choix d'un segment est que

le digit de plus faible poids soit nul. Nous pouvons donc commencer un segment tous

les 16 octets.

4.3. Les registres du 8086

Registres gnraux Registres

dadressage

Registres de

segment

Registre de

commande

AX AH AL SP CS IP

BX BH BL BP DS FLAGS

CX CH CL SI SS

DX DH DL DI ES

Chapitre IV : Etude et programmation dun microprocesseur (8086)

19

Tous les registres et le bus interne du 8086 sont structurs en 16 bits. Vu de

l'utilisateur, le 8086 comprend 3 groupes de 4 registres de 16 bits, un registre d'tat de

9 bits et un compteur programme de 16 bits non accessible par l'utilisateur.

!.3.1. Les re.istres .nr'u1

Les registres gnraux participent aux oprations arithmtiques et logiques

ainsi qu' l'adressage. Chaque demi-registre est accessible comme registre de 8 bits, le

8086 peut donc effectuer des oprations 8 bits d'une faon compatible avec le 8080.

AX : Accumulateur : Usage gnral, Obligatoire pour la multiplication

et la division, Ne peut pas servir pour l'adressage

BX : Base : Usage gnral, Adressage, (Par dfaut, son offset est relatif

au segment DS)

CX : Comptage et calcul : Usage gnral, Utilis par certaines

instruction comme compteur de rptition. Ne peut pas servir pour l'adressage

DX : Data : Usage gnral, Dans la multiplication et la division 16 bits,

il sert comme extension au registre AX pour contenir un nombre 32 bits, Ne

peut pas servir pour l'adressage.

!.3.2. Les re.istres d''dress'.e *offset-

Ces registres de 16 bits permettent l'adressage d'un oprande l'intrieur d'un

segment de 64 ko (216 positions mmoires)

SP : Pointeur de Pile : Utilis pour l'accs la pile.

Pointe sur la tte de la pile. Par dfaut, son offset est relatif SS

BP : Pointeur de Base : Adressage comme registre de

base, (Par dfaut, son offset est relatif SS), Usage gnral

SI : Registre d'index (source) : Adressage comme

registre dindex, (Par dfaut, son offset est relatif DS), Certaines

instruction de dplacement de donns l'utilise comme index de

l'oprande source. L'oprande destination tant index par DI, Usage

gnral

DI : Registre d'index (destination) : Adressage comme

registre dindex, (par dfaut, son offset est relatif DS), Certaines

instruction de dplacement de donns l'utilise comme index de

l'oprande destination, l'oprande destination tant index par SI.

!.3.3. Les re.istres de se.ments

Ces registrent sont combin avec les registres doffset pour former les

adresses. Une case mmoire est repre par une adresse de la forme RS:RO. On place

le registre segment au dbut dune zone mmoire de 64Ko, ensuite on fait varier le

registre doffset qui prcise ladresse relative par rapport cette position.

CS : Code Segment : Dfinit le dbut de la mmoire programme. Les

adresses des diffrentes instructions du programme sont relatives CS

DS : Data Segment : Dbut de la mmoire de donnes dans laquelle

sont stockes toutes les donnes traites par le programme

Chapitre IV : Etude et programmation dun microprocesseur (8086)

20

SS : Stack Segment : Dbut de la pile (voir chapitre V)

ES : Extra Segment Dbut d'un segment auxiliaire pour donnes

Une adresse doit avoir la forme [Rs : Ro]

Si le registre segment nest pas spcifi (cas rien), alors le processeur lajoute

par dfaut selon loffset choisit :

Tableau 5: segments par dfaut

!.3.!. Le re.istre d't't *f)'.s-

Tableau 6: registres d'tats

Six bits refltent les rsultats d'une opration arithmtique ou logique et 3

participent au control du processeur.

C : (Carry) indique le dpassement de capacit de 1 sur une opration 8

bits ou 16 bits. Ce flag peut tre utilis par des instructions de saut conditionnel,

des calculs arithmtiques en chane ou dans des oprations de rotation.

P : (Parit) indique que le nombre de 1 est un nombre pair. Ce flag est

utilis avec certains sauts conditionnels.

A : (retenue Arithmtique) indique une retenue sur les 4 bits (digit) de

poids faible. Par exemple quand la somme des 2 digits de poids faible dpasse F

(15)

Z : (Zro) Indique que le rsultat d'une opration arithmtique ou

logique est nul. Il est utilis dans plusieurs instructions de sauts conditionnels.

S : (Signe) reproduit le bit de poids fort d'une quantit signe sur 8 bits

ou sur 16 bits. L'arithmtique signe fonctionne en complment 2. S=0 :

positif, S=1 : ngatif. Ce flag sert lors de sauts conditionnels.

T : (Trap) met le CPU en mode pas pas pour faciliter la recherche des

dfauts d'excution.

I : (Interruption) autorise ou non la reconnaissance des interruptions : I

= 0 alors Interruptions autorises. I = 1 alors Interruptions non autorises

D : (Direction) fixe la direction de l'auto-inc/dcrmentation de SI et

DI lors des instructions de manipulation de chanes. D = 0 alors incrmentation

des index. D = 1 alors dcrmentation des index

O : (Overflow) indique un dpassement de capacit quand on travaille

avec des nombres signs. Comme par exemple si la somme de 2 nombres

positifs donne un nombre ngatif ou inversement. (40h + 40h = 80h et O=1)

Offset utilis Registre segment par dfaut qui sera utilis par le CPU

Valeur

DS

DI

SI

BX

BP SS

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

O I T S Z A P C

Chapitre IV : Etude et programmation dun microprocesseur (8086)

21

!.!. Les modes d('dress'.e

Dans la suite on utilisera les abrviations suivantes :

Tableau 7: les abrviations utilises

La structure la plus gnrale dune instruction est la suivante : INST op1, op2

Lopration est ralise entre les 2 oprandes et le rsultat est toujours

rcupr dans loprande de gauche. Il y a aussi des instructions qui agissent sur un

seul oprande Les oprandes peuvent tre des registres, des constantes ou le contenu

de cases mmoire, on appelle a le mode dadressage :

Adressage registre (R) : L'opration se fait sur un ou 2 registres (INST

R, R ; INST R)

Exemples : INC AX : incrmenter le registre AX

MOV AX, BX : Copier le contenu de BX dans AX

Adressage Immdiat (IM) : Un des oprandes est une constante

(valeur) :

INST R , im

INST taille [adr] , im

Exemples :

MOV AX, 243 : charger le registre AX par le nombre dcimal 243

ADD AX, 243h : additionner le registre AX avec le nombre hexadcimal 243

MOV AX, 0xA243 : Quand le chiffre de gauche du nombre hexadcimal est

une lettre, il est prfrable d'utiliser le prfix 0x pour l'hexadcimal

MOV AL, 'a' : Charger le registre AL par le code ASCII du caractre 'a'

MOV AX, 'a' : Charger le registre AH par 00 et le registre AL par le code

ASCII du caractre 'a'

MOV AX,'ab' : Charger AH par 'a' et AL par 'b'

Adressage direct (DA) : Un des deux oprandes se trouve en mmoire.

Ladresse de la case mmoire ou plus prcisment son Offset est prcis

directement dans linstruction. Ladresse Rseg:Off doit tre place entre [ ], si le

segment nest pas prcis, DS est pris par dfaut

INST instruction

R Registre quelconque

Rseg Registre Segment

Roff Registre doffset

Adr Adresse

[ adr] contenu Mmoire

Off Offset de ladresse

Im donne (constante)

Dep dplacement (constante)

Op Oprande

Os Oprande source

Od oprande destination

Chapitre IV : Etude et programmation dun microprocesseur (8086)

22

INST R , [adr]

INST [adr] , R

INST taille [adr] , im

Exemples :

MOV AX, [243] : Copier le contenu de la mmoire d'adresse DS:243 dans AX

MOV [123], AX : Copier le contenu de AX dan la mmoire d'adresse DS:123

MOV AX, [SS:243] : Copier le contenu de la mmoire SS:243 dans AX

Adressage indirect (IR) : Un des deux oprandes se trouve en mmoire.

Loffset de ladresse nest pas prcis directement dans l'instruction, il se trouve

dans lun des 4 registres doffset BX, BP, SI ou DI et cest le registre qui sera

prcis dans linstruction : [Rseg : Roff].

INST R , [Rseg : Roff]

INST [Rseg : Roff] , R

INST taille [Rseg : Roff] , im

Exemples :

MOV AX, [BX] ; Charger AX par le contenu de la mmoire d'adresse DS:BX

MOV AX, [BP] ; Charger AX par le contenu de la mmoire d'adresse SS:BP

MOV AX, [SI] ; Charger AX par le contenu de la mmoire d'adresse DS:SI

MOV AX, [DI] ; Charger AX par le contenu de la mmoire d'adresse DS:DI

MOV AX, [ES:BP] ; Charger AX par le contenu de la mmoire d'adresse

ES:BP

Ladressage indirect est divis en 3 catgories selon le registre doffset utilis.

On distingue ainsi, ladressage Bas, ladressage index et ladressage bas index,

Adressage Bas (BA) : Loffset se trouve dans lun des deux registres

de base BX ou BP. On peut prciser un dplacement qui sera ajout au contenu

de Roff pour dterminer loffset

INST R , [Rseg : Rb+dep]

INST [Rseg : Rb+dep] , R

INST taille [Rseg : Rb+dep] , im

Exemples :

MOV AX, [BX] : Charger AX par le contenu de la mmoire d'adresse DS:BX

MOV AX, [BX+5] : Charger AX par le contenu de la mmoire d'adresse

DS:BX+5

MOV AX, [BP-200] : Charger AX par le contenu de la mmoire d'adresse

SS:BX-200

MOV AX, [ES:BP] : Charger AX par le contenu de la mmoire d'adresse

ES:BP

Adressage Index (X) : Loffset se trouve dans lun des deux registres

dindex SI ou DI. On peut prciser un dplacement qui sera ajout au contenu

de Ri pour dterminer loffset

Chapitre IV : Etude et programmation dun microprocesseur (8086)

23

INST R , [Rseg : Ri+dep]

INST [Rseg : Ri+dep] , R

INST taille [Rseg : Ri+dep] , im

Exemples :

MOV AX, [SI] ; Charger AX par le contenu de la mmoire d'adresse DS:SI

MOV AX, [SI+500] ; Charger AX par la mmoire d'adresse DS:SI+500

MOV AX, [DI-8] ; Charger AX par la mmoire d'adresse DS:DI-8

MOV AX, [ES:SI+4] ; Charger AX par la mmoire d'adresse ES:SI+4

Adressage Bas Index (BXI) : loffset de ladresse de l'oprande est la

somme d'un registre de base, d'un registre d'index et d'un dplacement

optionnel. Si Rseg n'est pas spcifi, le segment par dfaut du registre de base

est utilis :

INST R , [Rseg : Rb+Ri+dep]

INST [Rseg : Rb+Ri+dep] , R

INST taille [Rseg : Rb+Ri+dep] , im

Exemples :

MOV AX,[BX+SI] ; AX est charg par la mmoire d'adresse DS:BX+SI

MOV AX,[BX+DI+5] ; AX est charg par la mmoire d'adresse DS:BX+DI+5

MOV AX,[BP+SI-8] ; AX est charg par la mmoire d'adresse SS:BP+SI-8

MOV AX,[BP+DI] ; AX est charg par la mmoire d'adresse SS:BP+DI

!.0. T'i))e des c&'n.es '7ec )' mmoire

La mmoire est organise en octets. Quand on fait une instruction entre un

registre et une donne qui se trouve en mmoire, cest le registre qui dtermine la

taille de lopration. Si le registre est un registre simple (8 bits), lopration se fera

avec une seule case mmoire.

MOV [adresse], AL donne

Si le registre est un registre double (2 octets), lopration se fera avec deux

cases mmoires

MOV [adresse], AX donne

Nous remarquons que c'est la partie basse du registre qui est traite en premier,

et ceci dans les deux sens.

adresse AL

adresse AL

AH

Chapitre IV : Etude et programmation dun microprocesseur (8086)

24

Quand on fait une opration entre une constante et une case mmoire, il y a

ambigut, le processeur ne sait pas sil faut considrer la constante sur 8 bits ou sur

16 bits. Il faut utiliser les prfixes BYTE et WORD pour prciser le nombre doctets

crire :

MOV BYTE ptr [adresse],4Ah ; On crit 4A dans la position adresse

MOV WORD ptr [adresse],4Ah ; On crit 004A, donc 4A dans la

position adresse, et 00 dans la position adresse+1 :

4.6. La pile :

4.6.1. Notion de pile

Les piles offrent un nouveau moyen daccder des donnes en mmoire

principale, qui est trs utilis pour stocker temporairement des valeurs. Une pile est

une zone de mmoire et un pointeur qui conserve ladresse du sommet de la pile.

!.%.2. 4nstructions ,5SH et ,2,

Deux nouvelles instructions, PUSH et POP, permettent de manipuler la pile.

PUSH registre empile le contenu du registre sur la pile.

POP registre retire la valeur en haut de la pile et la place dans le registre

spcifi.

Exemple : transfert de AX vers BX en passant par la pile.

PUSH AX ; Pile <- AX

POP BX ; BX <- Pile

(Note : cet exemple nest pas trs utile, il vaut mieux employer MOV AX,

BX.). La pile est souvent utilise pour sauvegarder temporairement le contenu des

registres :

AX et BX contiennent des donnes conserver

PUSH AX

PUSH BX

MOV AX, valeur ; // on utilise AX

ADD AX, BX ; // et BX

MOV truc, BX

POP BX ; rcupre lancien BX

POP AX ; et lancien AX

On voit que la pile peut conserver plusieurs valeurs. La valeur dpile par POP

est la dernire valeur empile ; cest pourquoi on parle ici de pile LIFO (Last In First

Out, Premier Entr Dernier Sorti).

adresse 4A

adresse 4A

00

Chapitre IV : Etude et programmation dun microprocesseur (8086)

25

!.%.3. e.istres SS et S,

La pile est stocke dans un segment spar de la mmoire principale. Le

processeur possde deux registres ddis la gestion de la pile, SS et SP.

Le registre SS (Stack Segment) est un registre segment qui contient ladresse

du segment de pile courant (16 bits de poids fort de ladresse). Il est normalement

initialis au dbut du programme et reste fix par la suite.

Le registre SP (Stack Pointer) contient le dplacement du sommet de la pile

(16 bits de poids faible de son adresse).

16bits

SP-2

Emplacement libre

SP

Figure 10: fonctionnement dune pile

!.8. Les instructions du $6$%

!.8.1. Les instructions de tr'nsfert

MOV Od , Os

Copie l'oprande Source dans l'oprande Destination

MOV R1 , R2 copier un registre dans un autre

MOV R , M copier le contenu dune case mmoire dans un registre

MOV M , R copier un registre dans une case mmoire

MOV R , im copier une constante dans un registre

MOV taille M , im copier une constante dans une case mmoire (taille

= BYTE ou WORD)

PUSH Op

Empiler loprande Op (Op doit tre un oprande 16 bits)

- Dcrmente SP de 2

- Copie Op dans la mmoire ponte par SP

PUSH R16

PUSH word [adr]

POP Op

Dpiler dans loprande Op (Op doit tre un oprande 16 bits)

Adresses

croissantes

POP PUSH

Chapitre IV : Etude et programmation dun microprocesseur (8086)

26

- Copie les deux cases mmoire pointe par SP dans l'oprande Op

- Incrmente SP de 2

POP R16

POP word M

!.8.2. Les instructions Arit&mtiques

Le 8086 permet d'effectuer les Quatre oprations arithmtiques de base,

l'addition, la soustraction, la multiplication et la division. Les oprations peuvent

s'effectuer sur des nombres de 8 bits ou de 16 bits signs ou non signs. Les nombres

signs sont reprsents en complment 2. Des instructions d'ajustement dcimal

permette de faire des calculs en dcimal (BCD).

Addition :

ADD Od , Os Additionne l'oprande source et l'oprande destination avec

rsultat dans l'oprande destination, Od + Os Od

ADD AX,123

ADD AX,BX

ADD [123],AX

ADD BX,[SI]

ADC Od , Os Additionne l'oprande source, l'oprande destination et le

curry avec rsultat dans l'oprande destination :Od + Os + C Od

INC Op Incrmente l'oprande Op Op + 1 Op

Attention, lindicateur C nest pas positionn quand il y a dbordement, C'est

lindicateur Z qui permet de dtecter le dbordement Pour incrmenter une

case mmoire, il faut prciser la taille :

INC byte [ ]

INC word [ ]

Soustraction : SUB Od , Os Soustrait l'oprande source et l'oprande

destination avec rsultat dans l'oprande destination. Od - Os Od

SBB Od , Os Soustrait l'oprande source et le curry de l'oprande

destination avec rsultat dans l'oprande destination. Od - Os - C Od

DEC Op Dcrmente l'oprande Op ; Op - 1 Op

NEG Op Donne le complment 2 de l'oprande Op : remplace Op par

son ngatif. C2(Op) Op

CMP Od , Os Compare (soustrait) les oprandes Os et Od et positionne

les drapeaux en fonction du rsultat. Loprande Od nest pas modifi.

Multiplication : MUL Op instruction un seul oprande. Elle effectue

une multiplication non signe entre l'accumulateur (AL ou AX) et l'oprande

Op. Le rsultat de taille double est stock dans l'accumulateur et son extension

(AH:AL ou DX:AX).

Chapitre IV : Etude et programmation dun microprocesseur (8086)

27

MUL Op8 alors AL x Op8 AX

MUL Op16 alors AX x Op16 DX:AX

L'oprande Op ne peut pas tre une donne, cest soit un registre soit une

position mmoire, dans ce dernier cas, il faut prciser la taille (byte ou word)

MUL BL ; AL x BL AX

MUL CX ; AX x CX DX:AX

MUL byte [BX] ; AL x (octet point par BX) AX

MUL word [BX] ; AX x (word point par BX) DX :AX

IMUL Op (Integer Multiply) Identique MUL except qu'une

multiplication signe est effectue.

Division : DIV Op Effectue la division AX/Op8 ou (DX|AX)/Op16

selon la taille de Op qui doit tre soit un registre soit une mmoire. Dans le

dernier cas il faut prciser la taille de loprande, exemple : DIV byte [adresse]

ou DIV word [adresse].

DIV Op8 ;AX / Op8 , Quotient AL , Reste AH

DIV S16 ;DX:AX / S16 , Quotient AX , Reste DX

S ne peut pas tre une donne (immdiat). Aprs la division L'tat des

indicateurs est indfini. La division par 0 dclenche une erreur

IDIV Op Identique DIV mais effectue une division signe

CBW (Convert Byte to Word) Effectue une extension de AL dans AH.

On crit le contenu de AL dans AX en respectant le signe

Si AL contient un nombre positif, On complte par des 0 pour obtenir la

reprsentation sur 16 bits.

Si AL contient un nombre ngatif, On complte par des 1 pour obtenir la

reprsentation sur 16 bits.

+5 = 0000 0101 alors AX devient 0000 0000 0000 0101

5 = 1111 1011 alors AX devient 1111 1111 1111 1011

CWD (Convert Word to Double Word ) effectue une extension de AX

dans DX en respectant le signe. On crit AX dans le registre 32 bits obtenu en

collant DX et AX

!.8.3. Les instructions )o.iques

NOT Op :Complment 1 de l'oprande Op

AND Od , Os : ET logique

Od ET Os Od

OR Od , Os : OU logique

Chapitre IV : Etude et programmation dun microprocesseur (8086)

28

Od OU Os Od

XOR Od , Os OU exclusif logique

Od OUX Os Od

TEST Od , Os Similaire AND mais ne retourne pas de rsultat dans

Od, seuls les indicateurs sont positionns

!.8.!. Les m'sques )o.iques #

Le 8086 ne possde pas d'instructions permettant d'agir sur un seul bit. Les

masques logiques sont des astuces qui permettent d'utiliser les instructions logiques

vues ci-dessus pour agir sur un bit spcifique d'un octet ou d'un mot.

Forcer un bit 0 : Pour forcer un bit 0 sans modifier les autres bits,

on utilise l'oprateur logique AND et ces proprits :

x AND 0 = 0 (0 = lment absorbant de AND)

x AND 1 = x (1 = lment neutre de AND)

On fait un AND avec une valeur contenant des 0 en face des bits qu'il faut

forcer 0 et des 1 en face des bits qu'il ne faut pas changer.

x x x x x x x X

and 1 1 1 0 1 1 0 1

x x x

0

x x

0

x

Forcer un bit 1 : Pour forcer un bit 1 sans modifier les autres bits,

on utilise l'oprateur logique OR et ces proprits :

x OR 1 = 1 (1 = lment absorbant de OR)

x OR 0 = x (0 = lment neutre de OR)

On fait un OR avec une valeur contenant des 1 en face des bits qu'il faut forcer

1 et des 0 en face des bits qu'il ne faut pas changer

x x x x x x x x

OR 0 0 1 0 0 0 0 0

x x

1

x x x x x

Inverser un bit : Pour inverser la valeur d'un bit sans modifier les autres

bits, on utilise l'oprateur logique XOR et ces proprits :

X XOR 1 = X

Chapitre IV : Etude et programmation dun microprocesseur (8086)

29

X XOR 0 = X (0 = lment neutre de XOR)

Donc, on fait un XOR avec une valeur contenant des 1 en face des bits qu'il

faut inverser et des 0 en face des bits qu'il ne faut pas changer

x x x x x x x x

XOR 0 0 1 0 0 0 0 0

x x

X

x x x x x

!.8.0. Les instructions de dc')'.e

Ces instructions dplacent dun certain nombre de positions les bits dun mot

vers la gauche ou vers la droite. Dans les dcalages, les bits qui sont dplacs sont

remplacs par des zros. Il y a les dcalages logiques (oprations non signes) et les

dcalages arithmtiques (oprations signes).

Dans les instructions de dcalage, l'oprande k peut tre soit une constante

(immdiat) soit le registre CL :

INST AX,1 ; dcaler AX de 1 bit

INST BL,4 ; dcaler BL de 4 bits

INST BX,CL ; dcaler BX de CL bits

On peut aussi dcaler le contenu d'une case mmoire mais il faut prciser la

taille

INST byte [BX],1 ; dcaler une fois le contenu de la case mmoire d'adresse

BX.

SHL R/M,k (SHift Logical Left) dcalage logique gauche de k bits

SHR R/M,k (SHift Logical right ) dcalage logique droite

Chapitre IV : Etude et programmation dun microprocesseur (8086)

30

SAR R/M,k (SHift Arithmetic right ) dcalage arithmtique droite

SAL R/M,k (SHift Arithmtic Left) dcalage arithmtique gauche

Les dcalages arithmtiques permettent de conserver le signe. Ils sont utiliss

pour effectuer des oprations arithmtiques comme des multiplications et des

divisions par 2.

ROL R/M,k (Rotate Left ) Rotation gauche

ROR R/M,k (Rotate Right ) Rotation droite

RCL R/M,k (Rotate Through CF Left ) Rotation gauche travers le

Carry

RCR R/M,k (Rotate Through CF Right) Rotation droite travers le

Carry

!.8.%. 4nstructions '.iss'nt sur )es indic'teurs

CLC (CLear Carry) positionne le drapeau C 0

STC (Set Carry) positionne le drapeau C 1

CMC Complmente le drapeau C

CLD Positionne le Drapeau D 0

Chapitre IV : Etude et programmation dun microprocesseur (8086)

31

STD Positionne le Drapeau D

CLI Positionne le Drapeau I 0

STI Positionne le Drapeau I 1

LAHF : Copier l'octet bas du registre d'tat dans AH

SAHF : Opration inverse de LAHF : Transfert AH dans l'octet bas du

registre d'tat

PUSHF : Empile le registre d'tat,

POPF : Dpile le registre d'tat,

4.7.7. Les instructions de contrle de boucle

LOOP xyz L'instruction loop fonctionne automatiquement avec le

registre CX (compteur). Quant le processeur rencontre une instruction

loop, il dcrmente le registre CX. Si le rsultat n'est pas encore nul, il

reboucle la ligne portant l'tiquette xyz, sinon il continue le

programme la ligne suivante ;

L'tiquette est une chane quelconque qui permet de reprer une ligne. Le

caractre ':' la fin de l'tiquette n'est obligatoire que si l'tiquette est seule sur

la ligne

LOOPZ xyz (Loop While Zero) Dcrmente le registre CX (aucun

flag n'est positionn) on reboucle vers la ligne xyz tant que CX est

diffrent de zro et le flag Z est gal 1. La condition supplmentaire

sur Z, donne la possibilit de quitter une boucle avant que CX ne soit

gal zro.

LOOPNZ xyz Dcrmente le registre CX et reboucle vers la ligne xyz

tant que CX est diffrent de zro et le flag Z est gal 0. Fonctionne de

la mme faon que loopz,

!.8.$. Les instructions de "r'nc&ement

3 types de branchement sont possibles :

Branchements inconditionnels

Branchements conditionnels

Appel de fonction ou dinterruptions

Tous ces transferts provoquent la poursuite de l'excution du programme

partir d'une nouvelle position du code. Les transferts conditionnels se font dans une

marge de -128 +127 octets partir de la position de transfert.

4.7.8.1. Branchements inconditionnels

JMP xyz Provoque un saut sans condition la ligne portant l'tiquette

xyz.

Chapitre IV : Etude et programmation dun microprocesseur (8086)

32

CALL xyz Appel d'une procdure (sous programme) qui commence

la ligne xyz. La position de l'instruction suivant le CALL est empile

pour assurer une poursuite correcte aprs l'excution du sous

programme.

RET Retour de sous programme. L'excution du programme continue

la position rcupre dans la pile.

INT n appel linterruption logicielle n n

4.7.8.2. Branchements conditionnels

Les branchements conditionnels sont conditionns par l'tat des indicateurs

(drapeaux) qui sont eux mme positionns par les instructions prcdentes.

Dans la suite nous allons utiliser la terminologie :

o suprieur ou infrieur pour les nombres non signs

o plus petit ou plus grand pour les nombres signs

o + pour l'oprateur logique OU

JE/JZ xyz (Jump if Equal or Zero ) Aller la ligne xyz si rsultat nul

ou si galit. C'est--dire si Z=1

JNE/JNZ xyz (Jump if Not Equal or Not Zero ) Aller la ligne xyz si

rsultat non nul ou si diffrent. C'est--dire si Z=0

JA xyz (Jump if Above ) aller la ligne xyz si suprieur (non sign).

C'est--dire si C + Z = 0

JAE xyz (Jump if Above or Equal ) aller la ligne xyz si suprieur ou

gal (non sign). C'est--dire si C = 0

JB xyz (Jump if Bellow) Branche si infrieur (non sign). C'est--dire

si C = 1

JBE xyz (Jump if Bellow or Equal ) aller la ligne xyz si infrieur ou

gal (non sign). C'est--dire si C + Z = 1

JC xyz (Jump if CArry ) aller la ligne xyz s'il y a retenu. C'est--dire

si C = 1

JNC xyz (Jump if No CArry) aller la ligne xyz s'il n'y a pas de

retenu. C'est--dire si C = 0

JG xyz (Jump if Grater) aller la ligne xyz si plus grand (sign). C'est-

-dire si (S ^ O) + Z = 1

JGE xyz (Jump if Grater or Equal ) aller la ligne xyz si plus grand ou

gal (sign). C'est--dire si S ^ O = 0

Chapitre IV : Etude et programmation dun microprocesseur (8086)

33

JL xyz (Jump if Less) aller la ligne xyz si plus petit (sign). C'est--

dire si S ^ O = 1

JLE xyz (Jump if Less or Equal) aller la ligne xyz si plus petit ou

gal (sign). C'est--dire si (S ^ O) + Z = 1

JO xyz (Jump if Overflow) aller la ligne xyz si dpassement. C'est--

dire si O = 1

JNO xyz (Jump if No Overflow) aller la ligne xyz s'il n'y a pas de

dpassement O = 0

JP/JPE xyz (Jump if Parity or Parity Even) aller la ligne xyz si parit

paire. C'est- dire si P = 1

JNP/JPO xyz (Jump if No Parity or if Parity Odd) aller la ligne xyz

si parit impaire. C'est--dire si P = 0

JS xyz (Jump if Sign) aller la ligne xyz si signe ngatif. C'est--dire

si S = 1

JNS xyz (Jump if No Sign) aller la ligne xyz si signe positif. C'est--

dire si S= 0

!.$. ,rocdures

!.$.1. Notion de procdure

La notion de procdure en assembleur correspond celle de fonction en

langage C, ou de sous-programme dans dautres langages.

Instruction A Calcul

Instruction B Instruction C

Call calcul

Instruction D RET

Figure 11: fonctionnement d'une procdure

Dans lexemple de la Figure 11: fonctionnement d'une procdure

La procdure est nomme calcul. Aprs linstruction B, le processeur passe

linstruction C de la procdure, puis continue jusqu rencontrer RET et revient

linstruction D.

Chapitre IV : Etude et programmation dun microprocesseur (8086)

34

!.$.2. Dc)'r'tion d(une procdure

Lassembleur possde quelques directives facilitant la dclaration de

procdures. On dclare une procdure dans le segment dinstruction comme suit :

Calcul Proc near ; procdure nomme

calcul

; instructions

RET ; dernire instruction

Calcul ENDP ;fin de la procdure

Le mot clef PROC commence la dfinition dune procdure, near indiquant

quil sagit dune procdure situe dans le mme segment dinstructions que le

programme appelant. Lappel scrit simplement : CALL Calcul

!.9. +t&odes de pro.r'mm'tion

!.9.1. Les t'pes de r')is'tion

Les tapes de ralisation dun programme sont les suivantes:

Dfinir la problmatique, sous forme de schmas, dorganigrammes, de

grafcet etc.

Dterminer des algorithmes : comment faire, par quoi commencer etc.

Rdiger le programme (code source) : utilisation du jeu dinstructions

(mnmoniques) ;

cration de documents explicatifs (documentation).

Tester le programme en rel ;

Corriger les erreurs (bugs) ventuelles : dboguer le programme puis

refaire des tests jusqu`a obtention dun programme fonctionnant de

manire satisfaisante.

!.9.2. L'n.'.e m'c&ine et 'ssem")eur #

Le langage machine est le langage utilisant des codes binaires correspondant

aux instructions ;

Lassembleur est un logiciel de traduction du code source crit en langage

assembleur (mnmoniques) vers le langage machine.

!.9.3. ')is'tion pr'tique d(un pro.r'mme #

On commence tout dabord par la rdaction du code source en assembleur

laide dun diteur (logiciel de traitement de texte ASCII): (exemples edit sous MS-

Chapitre IV : Etude et programmation dun microprocesseur (8086)

35

DOS, notepad (bloc-note) sous Windows), ensuite on procde lassemblage du code

source (traduction des instructions en codes binaires) avec un assembleur :(exemples :

MASM de Microsoft, TASM de Borland, A86 disponible en shareware sur Internet,

etc.) et ce pour obtenir le code objet : code machine excutable par le

microprocesseur.

Par la suite systme dexploitation ou laide du moniteur dune carte de

dveloppement, le code est charg en mmoire centrale et le programme est excut.

Pour la mise au point (dbogage) du programme, on peut utiliser un

programme daide la mise au point (comme DEBUG sous MS-DOS) qui permet

dexcuter pas pas le programme, de visualiser le contenu des registres et de la

mmoire et de poser des points darrt etc.

!.9.!. Structure d(un fic&ier source en 'ssem")eur #

Afin de facilit la clart de notre programme il est prfrable dorganiser le

code source de la manire suivante :

tiquettes instructions commentaires

Etiquette 1 : Mov ax,05h ; ceci est un commentaire

Sous_prog1 Proc near

; sous programme

Sous_prog1 endp

!.9.0. Directi7es pour )('ssem")eur #

Origine du programme en mmoire : ORG offset ; Exemple : org

1000H

Dfinitions de constantes : nom constante EQU valeur ; Exemple :

escape equ 1BH

Rservation de cases mmoires :

nom variable DB valeur initiale

nom variable DW valeur initiale

DB : Define Byte, rservation dun octet ;

DW : Define Word, rservation dun mot (2 octets).

Exemples :

nombre1 db 25

nombre2 dw ? ; pas de valeur initiale

buffer db 100 dup ( ?) ; rservation dune zone mmoire de 100

octets

Chapitre IV : Etude et programmation dun microprocesseur (8086)

36

!.16. Les interruptions

Une interruption est une requte spciale au microprocesseur pour lui indiquer

un vnement particulier ncessitant lattention du microprocesseur.

Il existe trois types dinterruption :

Interruption matrielle : caus par un des composants de lunit

centrale (souris, clavier, imprimante, etc.)

Interruption logicielle : caus par un programme en cours dexcution

Exception : du une erreur dans le programme en cours.

NB : Une interruption peut tre initie par le microprocesseur lui-mme en cas

de problmes (exemple : division par zro, mmoire dfectueuse, etc.)

Une interruption est dite non masque si elle est reconnue par le

microprocesseur ds que le signal lectrique a t dclench. Elle est dite masque

sinon.

!.16.1. Les interruptions m'trie))es *e1ternes-

Une interruption matrielle est un arrt de lexcution dun programme suite

un vnement matriel. Les demandes dinterruptions matrielles sont effectues par

les priphriques Signaux dinterruptions matrielles.

Les priphriques utilisent les signaux dinterruption du microprocesseur

(RESET, NMI, et INTR) pour signaler un vnement.

Le p 8086 contient 3 sources dinterruptions externes :

Reset : rinitialisation du p :

FLAG : 0000h

CS : FFFFh

IP : 0000h

DS : 0000h

ES : 0000h

SS : 0000h

Ladresse de dmarrage est : FFFF0H

NMI : (NO MASKABLE INTERUPT) : Cette interruption interrompe

directement le CPU.

INTR : (INTERUPT REQUASTE) : Cest une interruption autorise si

IF=1 sinon elle est masque

!.16.2. Les interruptions )o.icie))es

Une interruption logicielle est un arrt de lexcution dun programme pour

excuter une routine dinterruption du DOS ou BIOS

Chapitre IV : Etude et programmation dun microprocesseur (8086)

37

Pour le 8086, les interruptions logicielles sont provoques par linstruction

INT suivie du numro dinterruption (exemple : INT 21h : pour les interruptions du

DOS ; INT 14h : pour les interruptions du BIOS) ; Linstruction INTO est quivalente

INT 4 si overflow=1

Le droulement dune interruption logicielle est le suivant :

Le P reoit linstruction INT suivie du numro dinterruption

Le P utilise le numro dinterruption pour trouver le vecteur

dinterruption

Le P met le flag IF=0 (IF est le flag dinterruption), sauvegarde dans

la pile le registre dtat, et les registres CS et IP, et charge le vecteur

dinterruption dans CS:IP

Le P excute la routine dinterruption qui se termine par linstruction