Professional Documents

Culture Documents

Layout 4

Uploaded by

Kesani Venkat Narsimha ReddyOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Layout 4

Uploaded by

Kesani Venkat Narsimha ReddyCopyright:

Available Formats

2-1

2.1 Introduction

In doing layouts for digital circuits, the speed and the area are the two most important issues.

In contrast, in doing layout for analog circuits, everything should be considered simultaneously. In

addition to the speed and the area, other equally critical considerations should be taken into account.

For example, for amplifier design, good matching in devices is necessary to minimize the

offset voltage, and good shielding is required to protect critical nodes from being disturbed. Without

proper layout, the mismatches and the coupled noise would be quite large and would significantly

degrade the performance of the ampliers.

In this chapter, general guidelines in doing layout for analog integrated circuits will be

presented and discussed. Focus will be placed not only on the absolute values of components but also

on their matching and being protected from noise coupling.

2.2 Matching

There are many reasons why mismatches exist in integrated-circuit devices, the major of

which are listed as follows.

Mask production and alignment

Lateral diffusion (Fig. 2.1a)

Over-etching / undercut (Fig. 2.1b)

Boundary conditions (Fig. 2.1b)

Non-uniformity

Accordingly, the following layout guidelines can be made to obtain good matching in terms of

the absolute values of the devices themselves and the ratio between any two devices.

Chapter 2

ANALOG LAYOUT CONSIDERATIONS

CHAPTER 2: ANALOG LAYOUT CONSIDERATIONS 2-2

Build large components out of many identical small units

Consider boundary conditions for all components and use dummy if necessary

Use common-centroid symmetry

Use stacked layout for large devices

In the next few sections, specic layout issues for integrated-circuit devices, namely resistors,

capacitors, and MOS transistors, will be presented.

2.3 Resistor Layout

2.3.1 Structures

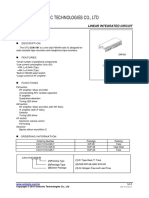

Integrated resistors can be implemented using different materials. Table 2.1 lists typical sheet

resistance, tolerance, and temperature coefficients for the mostly-used materials, namely polysilicon,

diffusion, and well.

Conductors Sheet Resistance Tolerance

Temperature

Coefcient

Polysilicon

20 - 50 /sq (non-silicide)

1 - 5 /sq (silicide)

Absolute: +/- 10 %

Matching: 2 %

500 - 1500 ppm/

o

C

Diffusion

15 - 30 /sq (for n+)

40 - 200 /sq (for p+)

Absolute: +/- 2 - 10 %

Matching: 0.1 - 0.5 %

500 - 1500 ppm/

o

C

Well 1 - 5 K/sq (for n+)

Absolute: +/- 30 %

Matching: +/- 5%

~ 3000 ppm/

o

C

Table 2.1 Properties for different types of resistors

Fig. 2.1 Effects of lateral diffusion (a) and over-etching or undercut (b)

etched layer

diffusion layer

lateral diffusion

over-etching/undercut

SiO

2

protection layer

(a) (b)

CHAPTER 2: ANALOG LAYOUT CONSIDERATIONS 2-3

2.3.2 Absolute Values

For small resistors, straight segments can be used, and the resistance value can be obtained as

(2.1)

(2.2)

where L, W, t, R

sh

, and are the length, width, thickness, sheet resistance, and sheet resistivity of the

segment, respectively.

For resistors with large values, serpentine structures as shown in Fig. 2.2 should be used. In

this case, each corner can be approximated as 0.50 to 0.55 squares, and each contact can be estimated

to contribute 0.14 squares. As an example, the structure in the gure should be approximately counted

as (6 x 4 + 5 + 5 x 2 x 0.55 + 2 x 0.14) = 34.78 squares. Round corners contribute more resistance and

can be estimated more accurately than squared corners.

Typically, the variation in the sheet resistance is very small, and L >> W. From Eq. 2.1, the

error in the absolute resistance value can be obtained as

(2.3)

For a given process, W is fixed, and as a result, the resistance error can be minimized by

maximizing the width W.

R Rsh

L

W

-----

t

---

L

W

----- = =

1

qND

-------------- =

Fig. 2.2 A serpentine structure to achieve a large resistance

4 squares

R

R

-------

L

L

-------

W

W

---------

Rsh

Rsh

----------- +

W

W

--------- =

CHAPTER 2: ANALOG LAYOUT CONSIDERATIONS 2-4

2.3.3 Matching Ratio

To obtain good matching ratio between two resistors, all the techniques mentioned above can

and should be used, including common-centroid, boundary conditions, and shields. With proper

layout, resistors with 0.1% mismatches can be achieved. Figure 2.3 illustrates an example of a layout

for two matched resistors. Note that both common-centroid symmetry and dummy cells are used

there.

2.4 Capacitor Layout

2.4.1 Structures

In integrated circuits, capacitors can be readily obtained using parallel plates from any two

different layers. Table 2.2 lists the typical capacitance per unit area together with their tolerance for

different structures in a 0.8-m MOSIS CMOS process.

Fig. 2.3 An example of a layout for two matched resistors

CHAPTER 2: ANALOG LAYOUT CONSIDERATIONS 2-5

It is important to note that MOS capacitors using the gate oxide thickness can be used to

achieve large capacitance per unit area. However, these capacitors in general are highly dependent on

Structure Type Value Tolerance

Gate Oxide Plate Area (fF/m

2

) 2.15 0.15

Poly to Substrate Over

Field Oxide

Area (fF/m

2

) 0.058 0.004

Fringing per edge (fF/m) 0.043

Metal-1 to Poly-Si

Area (fF/m

2

) 0.055 0.004

Fringing per edge (fF/m) 0.049

Metal-1 to Substrate

Area (fF/m

2

) 0.031 0.001

Fringing per edge (fF/m) 0.044

Metal-2 to Substrate

Area (fF/m

2

) 0.015 0.001

Fringing per edge (fF/m) 0.035

Metal-2 to Poly-Si

Area (fF/m

2

) 0.022 0.001

Fringing per edge (fF/m) 0.040

Metal-2 to Metal-1

Area (fF/m

2

) 0.035 0.002

Fringing per edge (fF/m) 0.046

Metal-3 to Substrate

Area (fF/m

2

) 0.010 0.001

Fringing per edge (fF/m) 0.033

Metal-3 to Poly-Si

Area (fF/m

2

) 0.012 0.001

Fringing per edge (fF/m) 0.034

Metal-3 to Metal-1

Area (fF/m

2

) 0.016 0.001

Fringing per edge (fF/m) 0.039

Metal-3 to Metal-2

Area (fF/m

2

) 0.035 0.002

Fringing per edge (fF/m) 0.049

Table 2.2 Properties of different types of capacitors

CHAPTER 2: ANALOG LAYOUT CONSIDERATIONS 2-6

their bias voltages and appropriate bias should be provided and maintained, which could be quite

complicated and troublesome.

Also note that the fringing capacitance can be quite significant and should be included when

accurate capacitance values are required.

More popular structures with much larger capacitance per unit area can be obtained using the

polysilicon layer as one or both of the capacitor plates. Table 2.3 shows typical capacitance values,

tolerances, temperature and voltage coefcients for several of these structures.

2.4.2 Absolute Values

For a capacitor with parallel plates, the capacitance value is given by

(2.4)

where A, W, L, t

ox

, and

ox

are the plate area, the width, the length, the dielectric thickness, and the

dielectric constant of the capacitor, respectively.

To achieve large capacitance per unit area in order to save the total area, it is common to use

several sandwiched-type capacitors and connect them in parallel, as illustrated in Fig. 2.4. Note that

the total capacitance is the sum of the individual capacitances. A potential problem is that parasitic

capacitance from the poly to the substrate C

ps

inevitably exists and may affect the circuit

performance. As comparison, typical total capacitance per unit area together with the parasitic

capacitance for several structures are shown in Table 2.4.

From Eq. 2.4, the error in the absolute capacitance value can be obtained as

Structure

Capacitance /

Area

Tolerance

Temperature

Coefcient

Voltage

Coefcient

poly - poly

0.34 fF/m

2

(t

ox

= 1000 A)

Absolute: +/- 10 %

Matching: +/- 0.2 - 0.5 %

20 - 30 ppm/

o

C 10 - 100 ppm/

o

C

poly - n+/p+

0.69 fF/m

2

(t

ox

= 500 A)

Absolute: +/- 5 %

Matching: +/- 0.2 %

20 - 30 ppm/

o

C 10 - 200 ppm/

o

C

poly - metal

0.03 fF/m

2

(t

ox

= 1 m)

Absolute: +/- 40 %

Matching: +/- 5%

~ small ~ small

Table 2.3 Properties of capacitors using polysilicon

C

ox

tox

------A CoxWL = =

CHAPTER 2: ANALOG LAYOUT CONSIDERATIONS 2-7

(2.5)

Typically, the error due to over-etching is the same for both sides, i.e. W = L = , and it

follows that

(2.6)

This goes to show that the capacitance error due to the over-etching is proportional to the ratio

of the perimeter to the area of the capacitor.

As a result, the capacitor error is minimized if the dimensions are chosen to minimize the

perimeter while keeping the area the same. This suggests that a squared structure would yield a

minimum error for a given capacitor.

Structure Designed Capacitance Parasitic Capacitance Ratio

M3-M2 31 aF/m

2

24 aF/m

2

0.77

M3-M2-M1 61 aF/m

2

62 aF/m

2

1.02

M3-M2-M1-poly 123 aF/m

2

86 aF/m

2

0.70

Table 2.4 Designed and parasitic capacitance values for sandwiched-type capacitors

Fig. 2.4 Sandwiched-type capacitor to reduce the capacitor area

substrate

C

32

M3

M2

poly

M1

C

32

C

1p

C

ps

C

ps

C

T

x

y

x

y

x y

C

C

-------

L

L

-------

W

W

--------- + =

error

C

C

-------

W L + ( )

A

-----------------------

P

2A

-------

P

A

---- = = =

CHAPTER 2: ANALOG LAYOUT CONSIDERATIONS 2-8

2.4.3 Matching Ratio

Just like resistors or any other devices, in order to obtain two capacitors with a good matching

ratio, all the techniques mentioned above should be used whenever possible, including the use of

common-centroid and dummy devices. Figure 2.5 illustrates such a layout.

For two capacitors with the ratio being an integer, the best matching is achieved if each can be

built using an integral number of identical unit cells.

Moreover, from Eq. 2.6, good matching for two capacitors can be achieved if their ratios of

perimeter to area are designed to be the same, even when they are of different sizes, that is

(2.7)

For the layout of two capacitors with the ratio being a non-integer, consider Fig. 2.6. Given a

squared capacitor C

1

with each side being x

1

, to achieve a matched rectangular capacitor C

2

with a

ratio of C

2

/C

1

= K, the two dimensions x

2

and y

2

of the rectangular capacitor C

2

should satisfy the

following condition

Fig. 2.5 Illustration of two capacitors to be matched with the ratio being an integer

C

1

C

2

C

1

C

2

C

1

C

2

C

1

C

2

C

1

C

2

C

1

C

2

C

1

C

2

C

1

C

2

P1

A1

------

P2

A2

------ =

CHAPTER 2: ANALOG LAYOUT CONSIDERATIONS 2-9

(2.8)

In addition, from Eq. 2.7, for good matching, the ratios of perimeter to area of the two

capacitors should be the same.

(2.9)

As a result,

(2.10)

and

(2.11)

2.5 Transistor Layout

2.5.1 Single Transistor

In addition to all the layout techniques mentioned above, the following guidelines can be used

specically for MOS transistors.

Minimize parasitic series resistance by using as many small contacts as possible

Use multiple small contacts as opposed to a single large contact to reduce the

curvature of the metal surface and thus to reduce the risk of micro-fracture

Fig. 2.6 Illustration of two capacitors to be matched with a non-integer ratio

x

1

x

1

y

2

x

2

C

1

C

2

A

2 P

1

A

1

P

2

K

C2

C1

-----

A2

A1

------

x2y2

x1

2

---------- = = =

K

P2

P1

-----

A2

A1

------

x2 y2 + ( )

2x1

--------------------- = = =

y2 x1 K K K 1 ( ) +

[ ] Kx1 1 1

1

K

---- +

= =

x2

Kx1

2

y2

---------

x1

1 1 1 K +

--------------------------------- = =

CHAPTER 2: ANALOG LAYOUT CONSIDERATIONS 2-10

Use stacked structures to realize large transistors

An example of how a stacked transistor can be laid out is shown in Fig. 2.7.

If a stack is divided in an odd number of ngers, the source is on one side, and the drain is on

the other side of the stack. On the other hand, if the number of ngers is even, either the drain or the

source is on both sides of the stack, and the other one is inside of the stack.

Using stacked transistors, not only is the total area minimized but the diffusion capacitors

from the drain and the source to the substrate are greatly reduced as well. If a stack with an odd

number of fingers n

odd

is used, both the drain-to-substrate and source-to-substrate capacitors are

reduced by a factor of

(2.12)

If an even number of fingers n

even

is used, the reduction factors of the inside diffusion

capacitor and the outside diffusion capacitor are given by

(2.13)

Fig. 2.7 An example of a layout for a stacked transistor

Cdb

Cdb

---------

Csb

Csb

---------

nodd 1 +

2nodd

------------------ = =

Cd out ,

Cd out ,

--------------

neven 2 +

2neven

------------------- - =

CHAPTER 2: ANALOG LAYOUT CONSIDERATIONS 2-11

(2.14)

Another advantage of using stacked transistors is that the polysilicon gate is interdigated and

thus the gate series resistance is reduced. It can be proved that the gate resistance as a function of the

number of ngers can be estimated as,

(2.15)

where R

sh

is the poly sheet resistance, W/L is the device aspect ratio, n is the number of the gate

ngers, and K is 3 or 12 depending on whether the gate ngers are contacting at one end or both ends,

respectively.

2.5.2 Matched Transistors

Using all the layout techniques and guidelines mentioned so far, in particular the

interdigitating technique with a common-centroid symmetry, good matching for two transistors can

be achieved. Figure 2.8 illustrates an example of a layout of a differential pair with common-centroid

symmetry.

2.6 General Guidelines for Noise Minimization

The following are useful guidelines to minimize noise coupling in doing layout for analog and

mixed-signal integrated circuits.

Maximize the separation between the analog and digital bias lines.

Use multiple supply and ground connections and I/O pins when possible. If this is

not possible, the connection should be made as closely to the pad as possible.

Use guard rings for isolation

Use wells for isolation, shielding, and as bypass capacitor for supply voltages

Use metal lines with constant bias between interconnection lines

Use metal plate with constant bias below the connect lines

Fill up unused space with contacts to substrate and wells

Always connect the bottom plate of capacitors to the non-critical nodes because

more noise is coupled to the bottom plate through the substrate.

Cd in ,

Cd in ,

------------

1

2

-- - =

RG

1

Kn

2

---------Rsh

W

L

----- =

CHAPTER 2: ANALOG LAYOUT CONSIDERATIONS 2-12

2.7 Floor Plan

Similar to laying out for devices, laying out for the whole circuit requires careful floorplan

and the same techniques can be applied to minimize mismatches and coupled noise. More

specically, the following guidelines should be observed.

Maximize the spacing between critical analog components and digital components

Minimize the connections to critical nodes

Minimize coupling or crossing between sensitive lines

Use shields whenever possible

Fig. 2.8 An example of a layout for a differential pair with common-centroid symmetry

G

2

G

1

S

12

D

2

D

1

S

12

CHAPTER 2: ANALOG LAYOUT CONSIDERATIONS 2-13

2.8 REFERENCES

D. Johns, and K. Martin, Analog Integrated Circuit Design, New York, Wiley, 1997.

M. Ismail and T. Fiez, Analog VLSI Signal and Information Processing, New York,

Mc-Graw-Hill, 1994.

J. Franca and Y. Tsividis, Design of Analog-Digital VLSI Circuits for Telecommunications

and Signal Processing, New Jersey, Prentice Hall, 2nd ed., 1994.

CHAPTER 2: ANALOG LAYOUT CONSIDERATIONS 2-14

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- SQL TutorialDocument200 pagesSQL Tutorialroamer10100% (1)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Principles of Data Conversion System DesignDocument5 pagesPrinciples of Data Conversion System Designbalodhi100% (1)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- From Creation To CreatorDocument50 pagesFrom Creation To CreatorAmy Walton100% (8)

- Sailor Hc4500 MF HF Control Unit Operating InstructionsDocument28 pagesSailor Hc4500 MF HF Control Unit Operating Instructionsckean_ng100% (1)

- Generator Set Iso8528!5!2005 Operating LimitsDocument1 pageGenerator Set Iso8528!5!2005 Operating Limitsswsw2011No ratings yet

- Urit 3000 Plus InstrumentDocument2 pagesUrit 3000 Plus InstrumentBilogba Alex67% (3)

- Partial Discharge TestingDocument349 pagesPartial Discharge Testinghungphuc2010No ratings yet

- HDFC Credit Card Limit Enhancement FormDocument1 pageHDFC Credit Card Limit Enhancement Formranju93No ratings yet

- Whitepaper - Top 6 Microservices PatternsDocument46 pagesWhitepaper - Top 6 Microservices PatternsTeja KamalNo ratings yet

- Web MethodsDocument1 pageWeb MethodsKesani Venkat Narsimha ReddyNo ratings yet

- MIV Fields Data MappingDocument4 pagesMIV Fields Data MappingKesani Venkat Narsimha ReddyNo ratings yet

- G.O.No.111 M.A.Document5 pagesG.O.No.111 M.A.jagankoneyNo ratings yet

- Introduction To Cmos Vlsi Design: Circuits & LayoutDocument54 pagesIntroduction To Cmos Vlsi Design: Circuits & LayoutEvi SouNo ratings yet

- 3131-IBM Message Broker Training PDFDocument13 pages3131-IBM Message Broker Training PDFKesani Venkat Narsimha ReddyNo ratings yet

- SAP Exchange Infrastructure - WebMethods Integration PDFDocument26 pagesSAP Exchange Infrastructure - WebMethods Integration PDFKesani Venkat Narsimha ReddyNo ratings yet

- Layer7 FirewallsDocument9 pagesLayer7 FirewallsKesani Venkat Narsimha ReddyNo ratings yet

- Integrationpatternsbiztalk PDFDocument420 pagesIntegrationpatternsbiztalk PDFKesani Venkat Narsimha ReddyNo ratings yet

- Set-Up Webmethods Terracotta Clustering PDFDocument13 pagesSet-Up Webmethods Terracotta Clustering PDFKesani Venkat Narsimha ReddyNo ratings yet

- Memory Flash-Dram PDFDocument18 pagesMemory Flash-Dram PDFKesani Venkat Narsimha ReddyNo ratings yet

- Choosing The Right API Management Solution For The Enterprise User PDFDocument9 pagesChoosing The Right API Management Solution For The Enterprise User PDFKesani Venkat Narsimha ReddyNo ratings yet

- 503 Data Power Virtual ApplianceDocument15 pages503 Data Power Virtual ApplianceKesani Venkat Narsimha ReddyNo ratings yet

- Ketu StoramDocument3 pagesKetu StoramKesani Venkat Narsimha ReddyNo ratings yet

- VPN Installation & Configuration GuideDocument4 pagesVPN Installation & Configuration GuideKesani Venkat Narsimha ReddyNo ratings yet

- Cadence Layout TipsDocument4 pagesCadence Layout TipsBhargav CoolNo ratings yet

- SQL Server 2012 Database Administration with AlwaysOn & Clustering TechniquesDocument6 pagesSQL Server 2012 Database Administration with AlwaysOn & Clustering TechniquesKesani Venkat Narsimha ReddyNo ratings yet

- DRCDocument16 pagesDRCdharma_panga8217No ratings yet

- Virtuoso LayoutDocument19 pagesVirtuoso LayoutpkashyNo ratings yet

- Web ArchitecturesDocument30 pagesWeb Architectureskakalotk15No ratings yet

- Programming 1SQL Server 2012 PDFDocument3 pagesProgramming 1SQL Server 2012 PDFKesani Venkat Narsimha ReddyNo ratings yet

- Lecture 3 Transmission Line Junctions Time Harmonic ExitationDocument23 pagesLecture 3 Transmission Line Junctions Time Harmonic Exitationvaldesc_tolNo ratings yet

- Lecture 4 Transmission Lines With Time Harmonic ExitationDocument26 pagesLecture 4 Transmission Lines With Time Harmonic Exitationvaldesc_tolNo ratings yet

- Lecture 2 Transmission Line DiscontinuitiesDocument22 pagesLecture 2 Transmission Line Discontinuitiesvaldesc_tolNo ratings yet

- Unix Course Material - Tata ElxsiDocument112 pagesUnix Course Material - Tata ElxsiKesani Venkat Narsimha ReddyNo ratings yet

- Lecture 1 Transmission LinesDocument18 pagesLecture 1 Transmission Linesvaldesc_tolNo ratings yet

- Unix CommandsDocument1 pageUnix CommandsKesani Venkat Narsimha ReddyNo ratings yet

- Digital Clamp Meter Kusam Meco 2700Document1 pageDigital Clamp Meter Kusam Meco 2700industrialindiaNo ratings yet

- MA5603T Product DescriptionDocument68 pagesMA5603T Product DescriptionHibiki KwoaHuiNo ratings yet

- MCQS ON CE - Fundamentals of Communication EngineeringDocument5 pagesMCQS ON CE - Fundamentals of Communication EngineeringsasirekhaNo ratings yet

- Co Unit 6Document30 pagesCo Unit 6GuruKPONo ratings yet

- EcsyllDocument121 pagesEcsyllDaisyQueenNo ratings yet

- 1485-td001 - En-P DeviceNet Media System Tech Data 1408Document40 pages1485-td001 - En-P DeviceNet Media System Tech Data 1408joseNo ratings yet

- MS-1756 Disassembly GuideDocument27 pagesMS-1756 Disassembly GuideCarlos CuboNo ratings yet

- Guide to Using the Satmotion Pocket App for PCDocument25 pagesGuide to Using the Satmotion Pocket App for PCHans Michael Estay JaraNo ratings yet

- Alpha Numeric Code For Resistors: 0603, 1% Resistors and Thin Film ResistorsDocument1 pageAlpha Numeric Code For Resistors: 0603, 1% Resistors and Thin Film ResistorspicimiciNo ratings yet

- High Speed Adder Used in DSPDocument17 pagesHigh Speed Adder Used in DSPPrabhu KiranNo ratings yet

- Mixing Console: Owner's ManualDocument26 pagesMixing Console: Owner's ManualTiago Flavia CavalcanteNo ratings yet

- User Manual: EnglishDocument17 pagesUser Manual: EnglishingcalderonNo ratings yet

- Asus Notebook Certificate Repair Training Engineer (CHER) Level 2-1 PDFDocument44 pagesAsus Notebook Certificate Repair Training Engineer (CHER) Level 2-1 PDFGerminii100% (1)

- Jiuzhou DTS6600: A HDTV PVR For All Walks of LifeDocument6 pagesJiuzhou DTS6600: A HDTV PVR For All Walks of LifeAlexander WieseNo ratings yet

- Memory Map and Address DecodingDocument9 pagesMemory Map and Address DecodingGhozi AlNo ratings yet

- B 450 NHDocument98 pagesB 450 NHRaul ContrerasNo ratings yet

- Unisonic Technologies Co., LTD: FM/AM RadioDocument8 pagesUnisonic Technologies Co., LTD: FM/AM RadioCyber XNo ratings yet

- EncoderDocument3 pagesEncoderRicardo Reguera AlvarezNo ratings yet

- T5L_DGUSII Application Development GuideDocument219 pagesT5L_DGUSII Application Development GuideZillaIllozNo ratings yet

- Meg X570 AceDocument1 pageMeg X570 AceMark Gabriel NoblezaNo ratings yet

- Standard Control Unit: Features and BenefitsDocument2 pagesStandard Control Unit: Features and BenefitspeterNo ratings yet

- Models - Acdc.inductor in CircuitDocument14 pagesModels - Acdc.inductor in CircuitneomindxNo ratings yet

- CDI (Capacitive Discharge Ignition) : Unit-IIDocument12 pagesCDI (Capacitive Discharge Ignition) : Unit-IIVARUN BABUNELSONNo ratings yet

- Marantz PM-15S1K1G Service ManualDocument51 pagesMarantz PM-15S1K1G Service ManualBon BencavNo ratings yet

- Optical Computers: Presented by Adarsh R. 1AY06EC104Document16 pagesOptical Computers: Presented by Adarsh R. 1AY06EC104Sonia SinghNo ratings yet