Professional Documents

Culture Documents

Review On Different Types of Router Architecture and Flow Control

Uploaded by

seventhsensegroup0 ratings0% found this document useful (0 votes)

46 views4 pagesNoC (Network on chip) is a new technology for

designing of communication structure in SoC design.

Where large number of IP blocks communicates with each

other. Router is the backbone of NoC design which

handles the communication and connecting with

neighbors. Designing of router and its characteristics is

directly impact on the performance of NoC. Size of the

new era digital system design are shrieked and the system

becomes more complex day by day. Before to design any

digital system we think two more important factors are

power and performance. Only the communication portion

in any system consume 50% power of the total power used

by the system. Here we show the different types of router

architecture which can improve the system performance.

Original Title

Review On Different Types Of Router Architecture And Flow Control

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentNoC (Network on chip) is a new technology for

designing of communication structure in SoC design.

Where large number of IP blocks communicates with each

other. Router is the backbone of NoC design which

handles the communication and connecting with

neighbors. Designing of router and its characteristics is

directly impact on the performance of NoC. Size of the

new era digital system design are shrieked and the system

becomes more complex day by day. Before to design any

digital system we think two more important factors are

power and performance. Only the communication portion

in any system consume 50% power of the total power used

by the system. Here we show the different types of router

architecture which can improve the system performance.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

46 views4 pagesReview On Different Types of Router Architecture and Flow Control

Uploaded by

seventhsensegroupNoC (Network on chip) is a new technology for

designing of communication structure in SoC design.

Where large number of IP blocks communicates with each

other. Router is the backbone of NoC design which

handles the communication and connecting with

neighbors. Designing of router and its characteristics is

directly impact on the performance of NoC. Size of the

new era digital system design are shrieked and the system

becomes more complex day by day. Before to design any

digital system we think two more important factors are

power and performance. Only the communication portion

in any system consume 50% power of the total power used

by the system. Here we show the different types of router

architecture which can improve the system performance.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 4

International Journal of Engineering Trends and Technology (IJETT) Volume 4 Issue 10 - Oct 2013

ISSN: 2231-5381 http://www.ijettjournal.org Page 4610

Review On Different Types Of Router

Architecture And Flow Control

Omprakash Ghorse

1

, Nitin Meena

2

, Shweta Singh

3

1

M.Tech Scholar, Electronics Department, IES College of Technology, Bhopal, RGPV Bhopal, India

2

Asst. prof. Electronics Department, IES College of Technology, Bhopal, RGPV Bhopal, India

3

Associate Prof. Electronics Department, IES College of Technology, Bhopal, RGPV Bhopal, India

Abstract NoC (Network on chip) is a new technology for

designing of communication structure in SoC design.

Where large number of IP blocks communicates with each

other. Router is the backbone of NoC design which

handles the communication and connecting with

neighbors. Designing of router and its characteristics is

directly impact on the performance of NoC. Size of the

new era digital system design are shrieked and the system

becomes more complex day by day. Before to design any

digital system we think two more important factors are

power and performance. Only the communication portion

in any system consume 50% power of the total power used

by the system. Here we show the different types of router

architecture which can improve the system performance.

Keywords Network on chip, Flow control of flit,

pipelining;

I. INTRODUCTION

Network-On-Chip (NoC) gives a new design to the

System-On-Chip (SoC) designing. We can design a high

density and complex VLSI technology on a single chip with

the SoC.

As the technology improves day by day SoC becomes

more heterogeneous IP (Intelactual property) blocks, and they

require high performance and flexibility which is becomes

more critical in SoC. The traditional bus structure which is

used in SoC design is replaced by the NoC which gives

several advantages over structure, performances and power.

NoC is consist of three main component switch which is

also called as router, network interface (NI) and link. The

main component of NoC is router whose main function is to

give the route to the packet fromits source to its destination.

NI is in between routers and IP blocks which is responsible

for packetizing and depacketizing of the message. Links are

used for communication between neighboring routers. Route

of the packet is determine by the router according to the

routing algorithm. Routing of packets is an important aspect in

NoC. The network throughput and latency is directly depends

upon the router and routing algorithm.

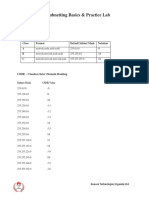

II. WORMHOLE SWITCHING ROUTER

ARCHITECTURE

The performance and implementation of wormhole

switching for relatively less traffic workload, makes it the

preferred switching technique as compare to store and forward

and virtual cut through switching. In this technique the

routing decision is made on reception of the header flit. The

data flits simply follow the header flit.

The router implemented using by a wormhole is Generic

NoC router . It has five inputs and output ports, each of one is

for local processing element (PE) and four for the neighboring

routers communication. Each router also has five components:

Routing Computation (RC) Unit, Virtual Channel Allocator

(VA), Switch Allocator (SA), flit Buffers (BUF), and

Crossbar Switch.

In a wormhole routing a message (packet) broken into a

multiple flits (flow control digit) for transmission and flow

control. The header flit containing all the routing information,

governs the route and the remaining data flits follow them in a

pipelined fashion. If the header flit is blocked, data flits are

also blocked. Wormhole switching makes the end-to-end

delay insensitive to the packet destination due to the

pipelining of flits, and routers require only small amount of

buffer space.

In a wormhole router, the switch arbiter stores priorities

between different requestors for fair arbitration. These

priorities are dependent upon the outcome of each arbitration.

In a wormhole router, a packet proceeds through the

states of routing, switch arbitration and switch traversal, as

traced in the flowchart.

International Journal of Engineering Trends and Technology (IJETT) Volume 4 Issue 10 - Oct 2013

ISSN: 2231-5381 http://www.ijettjournal.org Page 4611

Fig. 1 Flow of a flit through routing, switch arbitration and switch traversal in

a wormhole router

Fig. 2 The atomic module of a wormhole router, and the dependencies

between themdepicted with arrows

At very high work load traffic, wormhole switching

implementation may be suffer fromdeadlocks and highly

unpredictable latencies.

Wormhole router architecture increase latency, low

complexity and high buffer utilization, but less efficiency.

III. VIRTUAL CHANNEL ROUTER

ARCHITECTURE

When a physical channel is divided in to a multiple

number of logical channels. These logical channels are called

as virtual channel(VC). The concept of virtual channels is

used by Dally and Seitz to create a deadlock free

deterministic routing. A virtual channel has its own queue, but

it shares the bandwidth of the physical channel in a time

multiplexed fashion.

Power efficiency is one of the most important issue in

early systemdesign which is directly impact on the system

performance. For current process technologies, dynamic

power is the primary power source consumed in CMOS

circuits.

International Journal of Engineering Trends and Technology (IJETT) Volume 4 Issue 10 - Oct 2013

ISSN: 2231-5381 http://www.ijettjournal.org Page 4612

Fig. 3 The flow of flits through the states of routing, virtual-channel

allocation, switch allocation and switch traversal in a virtual-channel router is

depicted

Fig. 4 Atomic modules of a virtual-channel router, with dependencies shown

as arrows between them.

Hence, Figure shows the flow of a flit in a virtual-channel

router through the routing computation logic, the virtual-

channel allocator, the switch allocator, and the crossbar switch

module. It also shows the dependencies between these

modules. A flit needs to know which virtual channels to

request for before it can move on to virtual-channel allocation,

and it obtains this information fromthe routing logic, thus the

dependency of virtual-channel allocation on routing logic.

Thereafter, after securing a virtual channel, it arbitrates for a

physical channel through the switch allocator. Naturally, the

flit needs to win the switch allocation before it can traverse it.

The switch arbiter stores priorities between different

requestors for fair arbitration. These priorities are dependent

upon the outcome of each arbitration.

Although the VCFC (virtual channel flow control) is able

to increase the network throughput while reducing the

transmission delay. The use of VCFC decouples the buffers

fromthe physical communication links and routers. As such,

when a certain VC is congested, the packets in other VCs can

still progress through some links in the network and so the

network throughput can be significantly improved.

Virtual-channel flow control exploits an array of buffers

at each input port. By allocating different packets to each of

these buffers, flits frommultiple packets may be sent in an

interleaved manner over a single physical channel. This

improves both throughput and latency by allowing blocked

packets to be bypassed.

The basic steps followed by a virtual-channel router are

shown below:

A. Routing. When the first flit of a new packet arrives at

any input port of the router. First the routing field is

examined and a set of valid output virtual-channels on

which the packet can be routed is generated. The number

of output VCs generated by the routing logic will depends

on the routing function.

B. Virtual Channel Allocation. After the routing

computation packet is to made an attempt to allocate an

unused VC. A request which is made for one of the

virtual-channels returned by the routing function.

Allocation involves arbitrating between all those packets

requesting the same output VC.

C. Switch Allocation. Each packet maintains state

indicating the availability of buffer space at their assigned

output VC. When flits are waiting to be sent, and buffer

space is available, an input VC will request access to the

necessary output channel via the routers crossbar. On

each cycle the switch allocation logic matches these

requests to output ports, generating the required crossbar

control signals.

D. Crossbar Traversal. Flits that have been granted passage

on the crossbar are passed to the appropriate output

channel and flit is forwarding to the next hop.

IV. SPECULATIVE VIRTUAL CHANNEL ROUTER

In a VC router, a head flit has to ensure that it has first

reserved an output virtual channel for the packet before it can

request for its own passage through the crossbar and leave for

the next hop. Therefore a dependency exists between virtual-

channel allocation and switch allocation. This serialization

process of arbitration of a virtual channel and the switch

allocation significantly increases the latency of a virtual-

channel router.

A speculative virtual-channel router take away this

dependency. In this we assumes a flit will succeed in its

virtual-channel allocation, and proceeds to request for

crossbar switch passage in parallel. If the flit is really allowed

an output virtual channel, and it won the switch arbitration too

it can immediately traverse the crossbar and leave for the next

hop. if the speculation turns out to be incorrect, the switch

passage is simply wasted. This greatly shortens the critical

path of a virtual-channel router, potentially reduces the router

pipe line. A shorter router pipeline results in reduces network

latency and higher throughput due to quicker buffer

turnaround.

To avoid any negative impact on throughput, a

speculative virtual-channel router should be conservative,

prioritizing non-speculative requests over speculative ones.

Thus, speculative switch request will never be granted if there

are other non-speculative requests, and crossbar switch slots

will never be wasted if there are non-speculative flits waiting

to use it.

In a speculative virtual channel router, the switch

allocator speculatively assumes that a packet will succeed in

obtaining a free output virtual channel from the virtual-

channel allocator, and thus, proceed to request for the desired

output port before it has secured an output virtual channel.

The virtual-channel allocation and speculative switch

allocation states thus proceed in Parallel, the speculation is

conservative i.e., it will never reduce router performance. This

speculative architecture reduces a virtual-channel routers

pipeline as compare to the wormhole router, effectively

reducing the zero-load latency of a virtual-channel network to

that of a wormhole network.

International Journal of Engineering Trends and Technology (IJETT) Volume 4 Issue 10 - Oct 2013

ISSN: 2231-5381 http://www.ijettjournal.org Page 4613

Fig. 5 Atomic modules and dependencies of a speculative virtual-channel

router. The dependency between virtual-channel allocation and switch

allocation is removed with speculation

Fig. 6 shows Flow of a flit through a speculativevirtual-channel router.

V. CONCLUSION

As we see that there are many types of router architecture

in NoC are used. First we see that the wormhole architecture

this is simple in implementation but it is suffers from

deadlocks when the network is in heavy workload traffic so

that latency is increases which degrade the system

performance. It also has a low efficiency.

In VC & speculative architecture uses three pipeline

stages where as in wormhole router uses four pipeline stages

to transfer a flit from one hop to the next hop. Reducing

pipelining increases the network throughput and reduces the

latencies.

In addition to reducing the latency of a conventional

virtual-channel router, a speculative virtual-channel router

also increases network throughput, with its faster recycling of

buffers.

ACKNOWLEDGEMENT

I amstudy of many papers which is on network on chip

are published by many authors. I amthankful to all that give

me the more knowledge about NoC router.

REFERENCES

[1] Li shiuan peh flow control and micro architectureral mechanisumfor

extnding the performance of interconnection network in 2001.

[2] L.Rooban, S.DhananjeyanDesign of Router Architecture Based on

Wormhole Switching Mode for NoC International J ournal of Scientific

&Engineering Research Volume 3, Issue 3, March-2012

[3] N. Kavaldjiev, G.J.M. Smit, P.G. Jansen A Virtual Channel Router for

Onchip Networks Proceedings, IEEE International SOC Conference, 1215

September 2004, pages: 289293.

[5] Robert Mullins, Andrew West and Simon Moore Low-Latency Virtual-

Channel Routers for On-Chip Networks Computer Laboratory, University of

Cambridge

[6] Ville Rantala Teijo Lehtonen Juha Plosila Network on Chip Routing

Algorithms TUCS Technical Report No 779, August 2006 page: 09.

[7] Arnab Banerjee, Robert Mullins and Simon Moore A Power and

Energy Exploration of Network-on-Chip Architectures IEEE 2007

[8] Mostafa S. Sayed, A. Shalaby, M. El-Sayed Ragab, Victor Goulart,

Congestion Mitigation Using Flexible Router Architecturefor Network-on-

Chip2012 IEEE.

[9] Son Truong Nguyen Shigeru Oyanagi The Design of On-the-fly Virtual

Channel Allocation for Low Cost High Performance On-Chip Routers2010

IEEE.

[10]. Nicopoulos et al., ViChaR: A Dynamic Virtual Channel Regulator

for Network-on-Chip Routers, in Proc. of the 39th Intl Symp. on

Microarchitecture, 2006.

[10] Daniel U. Becker, WilliamJ . Dally Allocator Implementations for

Network-on-Chip Routers2009 IEEE.

[11] Ioannis Nousias, Tughrul Arslan Wormhole Routing with Virtual

Channels using Adaptive Rate Control for Network-on-Chip (NoC)2006

IEEE.

You might also like

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Music GcseDocument45 pagesMusic GcseAimee DohertyNo ratings yet

- NEC Article 250Document42 pagesNEC Article 250unknown_3100% (1)

- CobolDocument224 pagesCobolrahulravi007No ratings yet

- AutoCAD Mechanical 2015 Overview Brochure - A4Document4 pagesAutoCAD Mechanical 2015 Overview Brochure - A4Raul ReynosoNo ratings yet

- Non-Linear Static Analysis of Multi-Storied BuildingDocument5 pagesNon-Linear Static Analysis of Multi-Storied Buildingseventhsensegroup100% (1)

- Operational Guidelines For VlsfoDocument2 pagesOperational Guidelines For VlsfoИгорьNo ratings yet

- Optimal Search Results Over Cloud With A Novel Ranking ApproachDocument5 pagesOptimal Search Results Over Cloud With A Novel Ranking ApproachseventhsensegroupNo ratings yet

- The Utilization of Underbalanced Drilling Technology May Minimize Tight Gas Reservoir Formation Damage: A Review StudyDocument3 pagesThe Utilization of Underbalanced Drilling Technology May Minimize Tight Gas Reservoir Formation Damage: A Review StudyseventhsensegroupNo ratings yet

- Comparison of The Effects of Monochloramine and Glutaraldehyde (Biocides) Against Biofilm Microorganisms in Produced WaterDocument8 pagesComparison of The Effects of Monochloramine and Glutaraldehyde (Biocides) Against Biofilm Microorganisms in Produced WaterseventhsensegroupNo ratings yet

- Experimental Investigation On Performance, Combustion Characteristics of Diesel Engine by Using Cotton Seed OilDocument7 pagesExperimental Investigation On Performance, Combustion Characteristics of Diesel Engine by Using Cotton Seed OilseventhsensegroupNo ratings yet

- High Speed Architecture Design of Viterbi Decoder Using Verilog HDLDocument7 pagesHigh Speed Architecture Design of Viterbi Decoder Using Verilog HDLseventhsensegroupNo ratings yet

- Application of Sparse Matrix Converter For Microturbine-Permanent Magnet Synchronous Generator Output Voltage Quality EnhancementDocument8 pagesApplication of Sparse Matrix Converter For Microturbine-Permanent Magnet Synchronous Generator Output Voltage Quality EnhancementseventhsensegroupNo ratings yet

- An Efficient Model of Detection and Filtering Technique Over Malicious and Spam E-MailsDocument4 pagesAn Efficient Model of Detection and Filtering Technique Over Malicious and Spam E-MailsseventhsensegroupNo ratings yet

- Fabrication of High Speed Indication and Automatic Pneumatic Braking SystemDocument7 pagesFabrication of High Speed Indication and Automatic Pneumatic Braking Systemseventhsensegroup0% (1)

- Extended Kalman Filter Based State Estimation of Wind TurbineDocument5 pagesExtended Kalman Filter Based State Estimation of Wind TurbineseventhsensegroupNo ratings yet

- A Multi-Level Storage Tank Gauging and Monitoring System Using A Nanosecond PulseDocument8 pagesA Multi-Level Storage Tank Gauging and Monitoring System Using A Nanosecond PulseseventhsensegroupNo ratings yet

- Color Constancy For Light SourcesDocument6 pagesColor Constancy For Light SourcesseventhsensegroupNo ratings yet

- An Efficient and Empirical Model of Distributed ClusteringDocument5 pagesAn Efficient and Empirical Model of Distributed ClusteringseventhsensegroupNo ratings yet

- Comparison of The Regression Equations in Different Places Using Total StationDocument4 pagesComparison of The Regression Equations in Different Places Using Total StationseventhsensegroupNo ratings yet

- Design, Development and Performance Evaluation of Solar Dryer With Mirror Booster For Red Chilli (Capsicum Annum)Document7 pagesDesign, Development and Performance Evaluation of Solar Dryer With Mirror Booster For Red Chilli (Capsicum Annum)seventhsensegroupNo ratings yet

- Implementation of Single Stage Three Level Power Factor Correction AC-DC Converter With Phase Shift ModulationDocument6 pagesImplementation of Single Stage Three Level Power Factor Correction AC-DC Converter With Phase Shift ModulationseventhsensegroupNo ratings yet

- Ijett V5N1P103Document4 pagesIjett V5N1P103Yosy NanaNo ratings yet

- Design and Implementation of Height Adjustable Sine (Has) Window-Based Fir Filter For Removing Powerline Noise in ECG SignalDocument5 pagesDesign and Implementation of Height Adjustable Sine (Has) Window-Based Fir Filter For Removing Powerline Noise in ECG SignalseventhsensegroupNo ratings yet

- An Efficient Encrypted Data Searching Over Out Sourced DataDocument5 pagesAn Efficient Encrypted Data Searching Over Out Sourced DataseventhsensegroupNo ratings yet

- Separation Of, , & Activities in EEG To Measure The Depth of Sleep and Mental StatusDocument6 pagesSeparation Of, , & Activities in EEG To Measure The Depth of Sleep and Mental StatusseventhsensegroupNo ratings yet

- FPGA Based Design and Implementation of Image Edge Detection Using Xilinx System GeneratorDocument4 pagesFPGA Based Design and Implementation of Image Edge Detection Using Xilinx System GeneratorseventhsensegroupNo ratings yet

- An Efficient Expert System For Diabetes by Naïve Bayesian ClassifierDocument6 pagesAn Efficient Expert System For Diabetes by Naïve Bayesian ClassifierseventhsensegroupNo ratings yet

- Study On Fly Ash Based Geo-Polymer Concrete Using AdmixturesDocument4 pagesStudy On Fly Ash Based Geo-Polymer Concrete Using AdmixturesseventhsensegroupNo ratings yet

- Key Drivers For Building Quality in Design PhaseDocument6 pagesKey Drivers For Building Quality in Design PhaseseventhsensegroupNo ratings yet

- Ijett V4i10p158Document6 pagesIjett V4i10p158pradeepjoshi007No ratings yet

- Free Vibration Characteristics of Edge Cracked Functionally Graded Beams by Using Finite Element MethodDocument8 pagesFree Vibration Characteristics of Edge Cracked Functionally Graded Beams by Using Finite Element MethodseventhsensegroupNo ratings yet

- A Comparative Study of Impulse Noise Reduction in Digital Images For Classical and Fuzzy FiltersDocument6 pagesA Comparative Study of Impulse Noise Reduction in Digital Images For Classical and Fuzzy FiltersseventhsensegroupNo ratings yet

- Performance and Emissions Characteristics of Diesel Engine Fuelled With Rice Bran OilDocument5 pagesPerformance and Emissions Characteristics of Diesel Engine Fuelled With Rice Bran OilseventhsensegroupNo ratings yet

- A Review On Energy Efficient Secure Routing For Data Aggregation in Wireless Sensor NetworksDocument5 pagesA Review On Energy Efficient Secure Routing For Data Aggregation in Wireless Sensor NetworksseventhsensegroupNo ratings yet

- PF-CIS-Fall 2022 LABDocument4 pagesPF-CIS-Fall 2022 LABMuhammad FaisalNo ratings yet

- PTP - Level MethodsDocument23 pagesPTP - Level Methodssasikiran mNo ratings yet

- GenEd Mathematics LLL PDFDocument32 pagesGenEd Mathematics LLL PDFArmely NiedoNo ratings yet

- Impedance Measurement Handbook: 1st EditionDocument36 pagesImpedance Measurement Handbook: 1st EditionAlex IslasNo ratings yet

- FTP FUNCTION MODULE in ABAPDocument8 pagesFTP FUNCTION MODULE in ABAPAdriano PermanaNo ratings yet

- Steam Drive Correlation and Prediction PDFDocument10 pagesSteam Drive Correlation and Prediction PDFEmre CengizNo ratings yet

- HowTo Work With CR 90Document87 pagesHowTo Work With CR 90WagBezerraNo ratings yet

- WebControls - TabStripDocument38 pagesWebControls - TabStripProkopis PrNo ratings yet

- Windows Mbox Viewer User Manual 1.0.3.4Document33 pagesWindows Mbox Viewer User Manual 1.0.3.4Billy NoelNo ratings yet

- Astm A6 A6m-08Document62 pagesAstm A6 A6m-08Vũ Nhân HòaNo ratings yet

- Logic CHPT71Document27 pagesLogic CHPT71Eronjosh FontanozaNo ratings yet

- Lecture 1: Encoding Language: LING 1330/2330: Introduction To Computational Linguistics Na-Rae HanDocument18 pagesLecture 1: Encoding Language: LING 1330/2330: Introduction To Computational Linguistics Na-Rae HanLaura AmwayiNo ratings yet

- Wsat200 RamsaDocument12 pagesWsat200 RamsaAndy ColeNo ratings yet

- CI SetDocument18 pagesCI Setতন্ময় ঢালি Tanmay DhaliNo ratings yet

- Home Automation Iot Bca Up (2ND SEMINAR PPT) RTDocument30 pagesHome Automation Iot Bca Up (2ND SEMINAR PPT) RTTejaswiniNo ratings yet

- Cross Belt Magnetic Separator (CBMS)Document2 pagesCross Belt Magnetic Separator (CBMS)mkbhat17kNo ratings yet

- dp0 PDFDocument4 pagesdp0 PDFSimonNo ratings yet

- Hot Rolled Sheet Pile SHZ Catalogue PDFDocument2 pagesHot Rolled Sheet Pile SHZ Catalogue PDFkiet eelNo ratings yet

- OracleDocument23 pagesOracleriza arifNo ratings yet

- SubNetting Practice LabDocument3 pagesSubNetting Practice LabOdoch HerbertNo ratings yet

- LC IN SCIENCE and MathDocument14 pagesLC IN SCIENCE and MathCharity Anne Camille PenalozaNo ratings yet

- Electrocraft EAD BLDC CatalogDocument16 pagesElectrocraft EAD BLDC CatalogElectromateNo ratings yet

- Inferential Statistics: Estimation and Confidence IntervalsDocument19 pagesInferential Statistics: Estimation and Confidence IntervalsHasan HubailNo ratings yet

- 1.11 CHEM FINAL Chapter 11 Sulfuric AcidDocument21 pages1.11 CHEM FINAL Chapter 11 Sulfuric AcidSudhanshuNo ratings yet

- Toyo ML210 thread cutting gear assembly drawingsDocument12 pagesToyo ML210 thread cutting gear assembly drawingsiril anwarNo ratings yet