Professional Documents

Culture Documents

Final Manual Ec-1

Uploaded by

BoobalanRamasamyCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Final Manual Ec-1

Uploaded by

BoobalanRamasamyCopyright:

Available Formats

EX NO:1 FIXED BIAS AMPLIFIER CIRCUITS USING BJT

PRELAB

1. What is the another name for fixed bias circuit?

2. What is the value of stability factor in fixed bias?

3. Draw the circuit of fixed bias.

4. What are the advantages of fixed bias?

5. Define iasing

1

INLAB

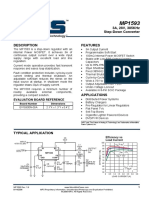

CIRCUIT DIAGRAM: FIXED BIAS AMPLIFIER

SYMBOL

2

C

E

B

BC107

7

EX .NO : 1

FIXED BIAS AMPLIFIER CIRCUITS USING BJT

1. Wave forms at in!ut and out!ut without bias.

2. Determination of bias resistance to locate " # !oint at center of load line.

3. $easurement of h%& and gain.

4. 'alculation of h ie()* + , dc and gain assuming h%&(hfe.

5. -lot of fre.uency res!onse.

AIM :

*o study and !lot the fre.uency res!onse of '& am!lifier with fixed bias.

APPARATUS REQUIRED :

/0.12 &.ui!ment +'om!onent *y!e+3ange "uantity

1

'32 4534$67 1

2

3egulated -ower /u!!ly 845349) 1

3

/ignal :enerator 8453 9$67 1

4

*ransistor ' 14; 1

5

3esistors 5<5=>? 2.2=>?1=> &ach 1

<

'a!acitors 2.2 @%?4; @% 2?1

;

read oard 5 1

A 'onnecting wires?!robes 5 Bs !er re.uired

THEORY :

*he su!!ly )ce has fixed vale and the resistance 3 8 144 C ohm 9 is selected. ,* is also

fixed. 6ence the circuit is called as fixed. 6ence the su!!ly voltage )ce !rovides the voltage

dro! across 3' can never be move than )'' + 3' value o!erating !oint will be on the

restoration region of the characteristic curve.

3

MODEL GRAPH :

TABULATION :

),1 ( )

S.No Freque!" #H$% Ou&'u& (o)&*+e #,o% - ( G*- #.B%

CALCULATION :

4

)'' ( , 3 D )& E , ( F)'' 5 )& G + 3

)'' ( ,' 3' D )'& E ,' ( )'' + 3' E ,'" (H ,E

B1DW,D*6 (%25%1

PROCEDURE :

1. 'onnect the circuit as !er the circuit diagram.

2. -ut in!ut voltage as at a constant voltage being signal generator.

3. =ee!ing the in!ut voltage constant? vary the fre.uency from 1 6I to 1 $6I

corres!onding out!ut voltage is noted

4. -lot the fre.uency res!onse by varying the in!ut fre.uency and note down the out!ut

voltage.

5. 'alculate the gain from the formula :ain(24 log F)out + )in Gd.

<. -lot the following characteristics and obtain bandwidth.

andwidth(%25%1.

.

5

POST LAB

1. Draw the out!ut transfer characteristic curve.

2. What is the value for " !oint ?

3. What are the a!!lications of fixed bias circuit?

4. What do you mean by load line?

5. Difference between %ixed ias circuit and )oltage divider bias circuit.

RESULT:

%re.uency res!onse of common emitter am!lifier with fixed bias gra!h was drawn and

determined.

andwidth ( 6I.

6

&J 12K2 BJT COMMON EMITTER AMPLIFIER USING ,OLTAGE DI,IDER

BIAS

PRELAB

1./0*& -1 2e*& 3" 1e)4 3-*15

6./0*& -1 &0e (*)ue o4 1&*3-)-&" 4*!&or - 1e)4 3-*15

7.Dr*8 &0e -'u& !0*r*!&er-1&-!1 o4 CE *2')-4-er.

9.Dr*8 &0e !-r!u-& o4 (o)&*+e .-(-.er 3-*1.

:. 80" -& -1 !*))e. *1 1e)4 3-*15

7

INLAB

&J 12K2 BJT COMMON EMITTER AMPLIFIER USING ,OLTAGE DI,IDER BIAS

C-r!u-& D-*+r*2

8

EX .NO : 6

BJT COMMON EMITTER AMPLIFIER USING ,OLTAGE DI,IDER BIAS

1. $easurement of gain.

2. -lot he fre.uency res!onse LDetermination of gain bandwidth -roduct.

AIM:

*o study the M* voltage divider bias circuit.

APPARATUS REQUIRED:

/0.12 &.ui!ment +'om!onent *y!e+3ange "uantity

1 '32 4534$67 1

2 3egulated -ower /u!!ly 845349) 1

3 /ignal :enerator 8453 9$67 1

4 *ransistor ' 14; 1

5 3esistors N4=>?14=>?2.2=>?5=> 1?2?1?1

< 'a!acitors 14@% 2

; read oard 5 1

A. 'onnecting wires?!robes 5 Bs !er re.uired

THEORY :

*he design of a transistor am!lifier re.uires Cnowledge of both the dc and the ac

res!onse of the system. iasing means the a!!lication of dc voltages to establish a fixed level of

current and voltage. %or transistor am!lifiers the bias voltage and the resulting dc current

establish an o!erating !oint on the characteristics that define the region that will be em!loyed for

am!lification of the ,n!ut )oltage. )oltage divider bias is the most stable bias circuit. )oltage

divider bias circuits are normally designed to have the voltage divider current very much larger

than the transistor base current. ,n this circumstance? base voltage is largely unaffected by base

current? so base voltage can be assumed to remain constant.

9

MODEL GRAPH

TABULATION

),1 ( )

S.No Freque!" #H$% Ou&'u& (o)&*+e #,o% - ( G*- #.B%

10

PROCEDURE:

1. 'onnect the circuit as !er the circuit diagram.

2. -ut in!ut voltage as at a constant voltage being signal generator.

3 =ee!ing the in!ut voltage constant? vary the fre.uency from 1 6I to 1 $6I

corres!onding out!ut voltage is noted.

4 -lot the fre.uency res!onse by varying the in!ut fre.uency and note down the out!ut

voltage.

11

POST LAB

1./0*& -1 &0e u1e o4 1e)4 3-*1 !-r!u-&5

6./0*& *re &0e *'')-!*&-o1 o4 CE *2')-4-er5

7./0*& -1 &0e !urre& *2')-4-!*&-o 4*!&or o4 CE *2')-4-er5

9. /0" -& -1 *2e. *1 (o)&*+e .-(-.er 3-*15

:. D-44ere&-*&e ,o)&*+e .-(-.er 3-*1 *. 4-;e. 3-*1.

RESULT:

*he 'ommon &mitter voltage divider bias circuit was designedE im!lemented and out!ut

values are tabulated and fre.uency res!onse is calculated as.

andwidth ( 6I.

12

&J 12K3 BJT CC AMPLIFIER

PRELAB

1.What is meant by '' am!lifier?

2.Draw the circuit of '' am!lifier.

3.Draw the out!ut characteristics of '' am!lifier.

4.What are advantages of '' am!lifier?

5. What is the other name for '' am!lifier?

13

&J 12K3 BJT COMMON COLLECTOR AMPLIFIER INLAB

14

EX .NO : 7

BJT COMMON COLLECTOR AMPLIFIER USING ,OLTAGE

DI,IDER BIAS

1. $easurement of gain.

2. -lot the fre.uency res!onse LDetermination of :ain andwidth -roduct.

AIM:

*o 'onstruct the 'ommon 'ollector Bm!lifier using the )oltage divider bias and !lot the

fre.uency res!onse and bandwidth.

APPARATUS REQUIRED:

/0.12 &.ui!ment +'om!onent *y!e+3ange "uantity

1 '32 4534$67 1

2 3egulated -ower /u!!ly 845349) 1

3 /ignal :enerator 8453 9$67 1

4 *ransistor ' 14; 1

5 3esistors

4;4O?144 O?1= O?1.5=

O &ach 1

< 'a!acitors 14 @% 2

; read oard 5 1

A 'onnecting wires? !robes 5 Bs !er re.uired

15

MODEL GRAPH:

TABULATION< FREQUENCY RESPONSE PLOT : ,- = 2,

S.No

Freque!" #H$% Ou&'u& ,o)&*+e ,o#,% G*-=6> )o+#,o?,-% .B

16

PROCEDURE:

1. 'onnect the circuit as !er the circuit diagram.

2. -ut in!ut voltage as at a constant voltage being signal generator.

3. =ee!ing the in!ut voltage constant? vary the fre.uency from 1 6I to 1 $6I

corres!onding out!ut voltage is noted.

4. -lot the fre.uency res!onse by varying the in!ut fre.uency and note down the out!ut

voltage.

17

POSTLAB

1./0*& -1 &0e !urre& *2')-4-!*&-o 4*!&or o4 CC *2')-4-er5

6./0*& -1 &0e (*)ue 4or Q 'o-& 5

7./0*& *re &0e *'')-!*&-o1 o4 CE *2')-4-er5

9./0*& -1 &0e .-44ere!e 3e&8ee CC *. CE *2')-4-er5

:. G-(e 1o2e .-1*.(*&*+e1 o4 CC *2')-4-er.

RESULT:

*he 'ommon 'ollector circuit using voltage divider bias circuit was constructed and

fre.uency res!onse was calculated as .

andwidth(

18

&J 12K4 DARLINGTON AMPLIFIER USING BJT

PRELAB

1.What is meant by darlington am!lifier?

2.Draw the circuit of darlington am!lifier.

3.Define darlington transistor.

4. What will be current gain and voltage gain if we use darlington transistor?

5. 6ow two transistors are cou!led to form dalington !air?

&J 12K4 DARLINGTON AMPLIFIER USING BJT

19

CIRCUIT DIAGRAM @ DARLINGTON AMPLIFIER USING BJT

INLAB

20

EX .NO : 9

DARLINGTON AMPLIFIER USING BJT

1. $easurement of gain and in!ut im!edance.

2. 'om!arison with calculated values.

3. -lot the fre.uency res!onse LDetermination of :ain andwidth -roduct.

AIM:

*o construct the Darlington !air am!lifier and to !lot the fre.uency res!onse.

APPARATUS REQUIRED:

S. No Co2'oe&1 S'e!-4-!*&-o1 Qu*&-&"

1 *ransistor '54; 2

2 3esistor

3.3

3N4

1$

&ach 1

3 'a!acitor 14@f 2

4 3egulated -ower /u!!ly 84534)9 1

5 '32 55 1

< read board 55 1

; Wires 55

Bs

re.uired

A %unction :enerator 5 1

N -robe 5 2

THEORY:

When the collectorPs of two M*Ps are tied together and the emitter of one is direct

cou!led to the base of the other? the configuration is called Darlington !air.

,n some a!!lications of am!lifier circuits very high in!ut im!edance is re.uired to achieve

this Darlington !air is used. *his combination is used in am!lifier circuits.

21

MODEL GRAPH:

TABULATION< FREQUENCY RESPONSE PLOT :

,- = 2,

S.No

Freque!" #H$% Ou&'u& ,o)&*+e ,o#,% G*-=6> )o+#,o?,-% .B

22

PROCEDURE:

1. 'onnections are given as !er the circuit diagram.

2. :ive the 12 ) 8)cc9 -ower su!!ly to the circuit.

3. )ary the fre.uency of the function generator and note down the corres!onding am!litude.

4. 1ote the readings of voltage and fre.uency in the table and draw the gra!h.

POSTLAB

23

1.What is the use of darlington am!lifier?

2.What are advantages of darlington am!lifier?

3.'omment in in!ut and out!ut im!edance of darlington transistor.

4. What is the disadvantage of using Darlington !air?

5.:ive your inference on gain in darlington !air.

RESULT:

*hus the Darlington !air was constructed and the fre.uency res!onses were

calculated.

EX NO:: SOURCE FOLLO/ER

24

PRELAB

1.What is meant by source follower?

2.What is the another name for source follower?

3.Draw the circuit of source follower.

4.Why it is called as source follower?

5.Draw the fre.uency res!onse curve of /ource follower.

EX NO:: SOURCE FOLLO/ER

25

INLAB

CIRCUIT DIAGRAM @ SOURCE FOLLO/ER /ITH BOOTSTRAPPED GATE RESISTANCE

26

EX .NO : :

SOURCE FOLLO/ER /ITH BOOTSTRAPPED GATE RESISTANCE

1. $easurement of :ain? ,+- resistance? 2+- resistance with and without ootstra!!ing

2. 'om!arison with calculated values.

AIM:

*o construct and test a source follower with gate resistance and to !lot the fre.uency

res!onse.

APPARATUS REQUIRED:

S. No Co2'oe&1 S'e!-4-!*&-o1 Qu*&-&"

1 M%&* %W 14 1

2 3esistor

14$

1$?4$?2$

1?1?2?1

3 'a!acitor 14@%?33 @% 2?1

4 3egulated -ower /u!!ly 84534)9 1

5 '32 5 1

< read board 55 1

; Wires 55

Bs

re.uired

A %unction :enerator 5 1

N -robe 5 2

THEORY:

*he field effect transistor is a three terminal device uni!olar in nature in which a current is

controlled by an electric field. B field effect transistor has advantages over uni!olar transistors?

1. &xtremely high in!ut resistance

2. 0ess noisy.

3. etter thermal stability.

,t has only one disadvantage that it has a relatively small gain? bandwidth !roduct. 6owever this

drawbacC is removed considerably by using advanced manufactured technology. ecause of the

above advantages the field effect transistors has become more !o!ular.

27

MODEL GRAPH:

SYMBOL

D

G

S

S.No Freque!" #H$% Ou&'u& ,o)&*+e ,o#,% G*-=6> )o+#,o?,-% .B

28

3 dB

Frequency in Hz

Gain

(dB)

F

1

F

2

CALCULATION :

1. :ain (24 log 8 )o + )in 9 in d

2. and Width (f25f1

PROCEDURE:

1. *he connections are given as !er the circuit diagram

2. /et )in (54m) using the signal generator.

3. )arying the fre.uency in the function generator and note down the out!ut voltage.

4. *he readings are taCen until the rece!tion of out!ut voltage occurs after constant values

5. :ain in decibels is calculated

<. 3eadings are !lotted in gra!h.

29

POST LAB

1. Write down the in!ut characteristics of source follower?

2. Write down the out!ut characteristics of source follower?

3. What are the uses of source follower?

4. What are the a!!lications of source follower?

5. Why is the name so called as source follower?

RESULT :

*he '/ am!lifier circuit was constructed and its fre.uency res!onse curve was drawn.

and Width( 67.

EX NO:A DIFFERENTIAL AMPLIFIER USING BJT

30

PRELAB

1.What is meant by differential am!lifier?

2.What are the two modes in the differential am!lifier?

3.Draw the circuit of differential am!lifier?

4.What are the advantages of differential am!lifier?

5. what do you meant by '$33?

EX NO:A DIFFERENTIAL AMPLIFIER USING BJT

31

CIRCUIT DIAGRAM

DIFFERENTIAL MODE GAIN

COMMON MODE GAIN

4

4

' 1 4 ;

" 1

' 1 4 ;

" 2

3 1

2 . 2 C

3 2

2 . 2 C

3 2

3 . 3 C

5 1 2 )

S I G N A L

G E N E R A T O R

V i n = 1 V

V c c = 1 2 v

V o

EX.NO: A

DIFFERENTIAL AMPLIFIER USING BJT

32

AIM:

*o find differential mode gain? common mode gain and '$33

APPRATUS REQUIRED

/.1o 'om!onents 3ange "uantity

1 3-/ 845349) 1

2 *ransistor '14; 2

3 3esistor 3.3=>?2.2=>?1.5=> 1?2?1

4 Dual mode !ower

su!!ly

845349) 1

5 '32 5555 1

< Bmmeter 8451449 mB 1

; /ignal generator 453$67 1

A read board 5555 1

N. 'onnecting wires

L!robes

5 Bs !er

re.uired

THEORY

*he function of differential am!lifier is to am!lify the difference between two signals. *he

need foe differential am!lifier arises in many !hysical measurements where res!onse from dc to

$67 is re.uired. ,t is also basic stage of an differential in!ut.

B linear active device with two in!ut signal v1? v2 and one out!ut signal v4? each

measured with res!ect to ground. ,n an ideal differential am!lifier the out!ut v4 is given by

)4(Bd 8)15)29

Bd()4+)15)2

Where Bd is the gain of the differential am!lifier. a !ractical differential am!lifier not only

de!ends on the differential /ignal )d of the two signal but also de!ends on the level called the

common mode signal ac where

)4(Bc 8v1Dv2+29

'$33 of differential am!lifier is calculated as

'$33( Bd+Bc

FORMULA

'ommon $ode :ain Bc ( )4+ 8)1D)2+29

Differential $ode :ain Bd ( )4 + 8)15)29

'$33 ( Bd+Bc

Differential mode gain

33

'ommon mode gain

PROCEDURE:

'onnection are given as !er the circuit diagram

/et the in!ut signal using a signal generator

'onnect the in!ut signal to the circuit after giving a dc su!!ly of 12v to collector terminal

and 512v to emitter terminal

2ut!ut voltage v41 and v42 are measured from '32

$easure the collector current of individual transistor using ammeter

Differential mode gain and common mode gain can be calculated from which '$33 can

be found

34

/.1o ,n!ut )oltage 2ut!ut )oltage Differential

gain8Bd9 )1 )2 )o1 )22

/.1o ,n!ut )oltage 2ut!ut )oltage common

mode

gain8Bc9

)1 )2 )o1 )22

POSTLAB

1.What is meant by common mode reQection ratio?

2.What are the a!!lications of differential am!lifier?

3.What is meant by common mode gain?

4.What is differential mode gain?

5. Write down the relation of gain relating to '$33 with differential of am!lifier

35

RESULT:

*hus the differential mode gain? common mode gain and '$33 of differential am!lifier

were determined

EX NO:B CLASS @ A PO/ER AMPLIFIER

PRELAB

1. What is meant by class a !ower am!lifier?

2. Draw the out!ut characteristics of class a !ower am!lifier.

3. Write the !ower out!ut e.uation for class a !ower am!lifier?

4. Draw the circuit of class a !ower am!lifier.

5. What is the efficiency of 'lass B -ower am!lifier?

36

EX NO:B CLASS @ A PO/ER AMPLIFIER

INLAB

CIRCUIT DIAGRAM

37

E;.No. B

CLASS @ A PO/ER AMPLIFIER

819 2bservation of out!ut waveform 829 $easurement of max !ower out!ut

839 Determination of efficiency 849'om!arison with calculated values

AIM

*o design the 'lass B !ower am!lifier and find the fre.uency res!onse.

APPARATUS REQUIRED

/0.12 &.ui!ment +'om!onent *y!e+3ange "uantity

1 '32 4534$67 1

2 3egulated -ower /u!!ly 845349) 1

3 /ignal :enerator 8453 9$67 1

4 *ransistor '14; 1

5 3esistors <A=>?1=>?144>?4;4>?<A4> &ach 1

< 'a!acitors 14@% 3

; read oard 5 1

A. 'onnecting wires L!robes 5 Bs !er re.uired

THEORY:

-ower am!lifiers !rovide sufficient !ower to an out!ut load to drive !ower devices?

ty!ically a few watts to tens off watts. *he main feature of !ower am!lifier is the circuitPs

efficiency? the maximum amount of !ower that the circuit is ca!able of handling? the im!edance

matching to the out!ut device. ,n a 'lass B !ower am!lifier? the out!ut signal varies for a full 3<4

4

of the cycle. *his circuit re.uires the " !oint to be biased at a level such that at least half the

38

signal swing of the out!ut may vary u! and down? the extreme values not being limited by the

su!!ly voltage levels? high as well as low.

MODEL GRAPH

TABULATION

/.1o %re.uency in 67 2ut!ut in volts :ain :ain in d ( 24

log 8)4+)i9

39

PROCEDURE:

1. :ive the connections as shown in the circuit diagram.

2. =ee! the in!ut voltage constant.

3. 1ote the value of 30 that give maximum undistorted !ower to load 30 for !articular

fre.uency.

4. -lot the fre.uency res!onse by varying the in!ut fre.uency L noting down the out!ut

voltage for 30 maximum.

40

POSTLAB

1.Write the efficiency of class a !ower am!lifier?

2.what is the use of class a !ower am!lifier?

3.What is the advantage of class a !ower am!lifier?

4. what is the a!!lications of 'lass B am!lifier?

5. why 'lass B am!lifier is called as -ower am!lifier?

41

RESULT

*hee 'lass B !ower am!lifier circuit were constructed and the fre.uency res!onses

were tabulated and !lotted on the gra!h

EX NO:C CLASS B COMPLEMENTARY SYMMETRY PO/ER AMPLIFIER

PRELAB

1. What is meant by class !ower am!lifier?

2. Draw the out!ut characteristics of class !ower am!lifier.

3. Write the !ower out!ut e.uation for class !ower am!lifier?

4. Draw the circuit of class !ower am!lifier.

5. What is the efficiency of 'lass -ower am!lifier?

42

EX NO:C CLASS B COMPLEMENTARY SYMMETRY PO/ER AMPLIFIER

INLAB

CLASS B AMPLIFIER /ITH DISTORTION

CLASS B AMPLIFIER /ITHOUT DISTORTION

43

EX.NO : C

CLASS B COMPLEMENTARY SYMMETRY PO/ER AMPLIFIER

1. 2bservation of the out!ut waveform with crossover Distortion.

2. $odification of the circuit to avoid crossover distortion.

3. $easurement of maximum !ower out!ut.

4. Determination of efficiency.

5. 'om!arison with calculated values.

AIM:

*o construct and study the !erformance of a class com!lementary symmetry !ower

am!lifier? and study the !erformance the above.

APPARATUS REQUIRED K

S.No Co2'oe&1 Requ-re. S'e!-4-!*&-o1

Qu*&-&"

1. 3egulated -ower /u!!ly 845349 v

1

2. B%2 55 1

3. '32 55

1

4. read oard 55

1

5. *ransistor /0144? /=144 1

<. 'a!acitor 1@f

3

44

;. 3esistor 5<C ohm ? 1C ohm? 2C ohm.

2?1?1

A. Diode 11 444; 2

N. 'onnecting wires

THEORY K

*he am!lifier that delivers more !ower to the load is called !ower am!lifier. *he in!ut

signal for a !ower am!lifier is large. 6ence they are Cnown as large signal am!lifier. *hey

deliver large amount of !ower to load. ,n !ower am!lifier? only current am!lification taCes !lace.

*ransistors used in !ower am!lifier circuits must have large !ower dissi!ation rating.

,n class mode of o!eration the o!erating !oint is almost near the cut off !oint. *his

im!lies that collector current flows only for the half cycle 81A4 degree9 of the in!ut B' cycle. ,n

class o!eration transistor is so adQusted that 7ero signal collector current is 7ero? 8i.e. no biasing

is needed at all9. During !ositive half cycle of the in!ut signal the in!ut circuit is forward biased

and hence collector current flows. During negative half cycle of the in!ut signal in!ut circuit is

reverse biased L no collector current flows.

MODEL GRAPH

Ou&'u& 8*(e4or2 8-&0ou& .-o.e

Ou&'u& 8*(e4or2 8-&0 .-o.e

45

PROCEDURE:

1. :ive the connections as shown in the circuit diagram.

2. =ee! the in!ut voltage constant.

3. 1ote the value of 30 that give maximum undistorted !ower to load 30 for !articular

fre.uency.

4. -lot the fre.uency res!onse by varying the in!ut fre.uency L noting down the out!ut

voltage for 30 maximum.

46

POST LAB

1. Write the efficiency of class !ower am!lifier?

2. What is the use of class !ower am!lifier?

3. What is the advantage of class !ower am!lifier?

4. What is the a!!lications of 'lass am!lifier?

5. Why 'lass am!lifier is called as -ower am!lifier?

47

RESULT:

*he !erformance of 'lass 'om!lementary /ymmetry -ower Bm!lifier is studied with

and without cross over distortion. *he !erformance gra!h is !lotted.

$aximum -ower 2ut!ut - 8out9 (

&fficiency R (

EX NO:D HALF /A,E RECTIFIER

PRELAB

1.What is meant by half wave rectifier?

2.What is the value of ri!!le factor?

3.What is the value of !eaC factor?

4.Draw the circuit of half wave rectifier?

5. Draw the waveform of 6W3.

48

EX NO:D HALF /A,E RECTIFIER

INLAB

C-r!u-& D-*+r*2

HALF /A,E /ITH FILTER

/ITHOUT FILTER

49

E;: No: D

IMPLEMENTATION OF HALF /A,E /ITH SIMPLE CAPACITOR FILTER

8i9 $easurement of D' voltage under load and ri!!le factor? 'om!arison with

calculated values..

8ii9 $easurement of load regulation characteristics 8)out )s ,out 9.

AIM:

*o design and construct the half wave rectifiers circuit with a without filter and test their

characteristics by measuring the following !arameters.

APPARATUS REQUIREDK

/.12 B!!aratus

1ame

3ange+*y!e "uantity

1. *ransformer 234+8N545N9v 1

2. -1 diode ,1444; 1

3. 3esistors 5<4=O 1

4. 'a!acitors 22@%.144@%?4;4@% 1

5. '32 L!robe 5 1

<. 'onnecting wires 5 Bs !er re.uired

THEORY:

B rectifier is basically used to convert the ac com!onents into dc com!onents. 6ere ac

voltage due to rectifier is a!!lied at the in!ut and the voltage across the secondary forms the

in!ut voltage to the rectifier diode. During the !ositive half cycle the ac voltage is rectified as the

diode is forward biased. ut during the negative half cycle? the diode is reverse biased and hence

50

it does not conduct and hence an un rectified dc signal is obtained. /o here the !ositive half cycle

of the ac com!onent is rectified and negative half cycle remains un rectified.

&.uating the relations of !arameters and com!onents valuesK

With %ilterK

3$/ )alue of ri!!le voltage )r8rms9 ( )r+2S3

Dc voltage )dc ( )m85)r+29

*heoretical ri!!le factor r ( 1+82S3D30'9

$easured ri!!le factor ( r ( )r8rms9+ )dc

Where ?

)m ( $aximum secondary voltage

)r ( 3i!!le voltage8!eaC to !eaC9

TABULATIONSK

Without filterK

)m (

)dc ( )m+T

)rms ( )m+S2

3i!!le factor r ( F8)rms+)dc9U251GU81+29

With %ilterK

'

8@%9

)r

8)9

)m

8)9

)rms

8)9

)dc

8)9

*heoretical

3i!!le factor

-ractical

3i!!le factor

MODEL GRAPH

51

PROCEDUREK

Without filterK

1. 'onnect the com!onent to the secondary terminal of the transformer.

2. 'onnect '32 across the load.

3. =ee! the '32 switch in the ground mode and then adQust the hori7ontal line to the

central line.

4. /witch '32 to D' mode and observe the waveform. 1ote down the am!litude )m and

time !eriod from the screen.

5. 'alculate )dc by using the formula )dc ( )m+T.

<. 'alculate ri!!le factor r ( F8)rms+)dc9U251GU81+29.

;. 'alculate )rms ( )m+S2.

With %ilterK

1. 'onnect ca!acitors of values 22@%?144@% and 4;4@% .

2. 3e!eat the ste!s and calculate the ri!!le voltage and dc voltage.

3. 'alculate the ri!!le factor from the above readings.

52

POST LAB

1.What is the advantage of half wave rectifier?

2.Where half wave rectifier used?

3.0ist some disadvantages of half wave rectifier?

4.What are the a!!lications of 6W3?

5. What do you meant by ri!!le factor?

53

RESULTK

*hus the 6alf Wave 3ectifier With and Without %ilter is 'onstructed and *abulated

3i!!le factor without filterK

$easured )alueK

*heoretical valueK

3i!!le factor with filterK

$easured )alueK

*heoretical valueK

EX NO:1> Fu)) /*(e Re!&-4-er:

PRELAB

1.What is meant by full wave rectifier?

2.What is the value of ri!!le factor?

3.What is the value of !eaC factor?

4.Draw the circuit of full wave rectifier.

5. Draw the in!ut and out!ut waveforms.

54

EX NO:1> Fu)) /*(e Re!&-4-er:

INLAB

'ircuit Diagram

FULL /A,E RECTIFIER /ITHOUT FILTER

55

FULL /A,E RECTIFIER /ITH FILTER

E;: No: 1>

IMPLEMENTATION OF FULL /A,E /ITH SIMPLE CAPACITOR FILTER

8i9 $easurement of D' voltage under load and ri!!le factor? 'om!arison with

calculated values..

8ii9 $easurement of load regulation characteristics 8)out )s ,out 9.

AIM:

*o design and construct the full wave rectifiers circuit with a without filter and test their

characteristics by measuring the following !arameters.

APPARATUS REQUIRED:

S.NO A''*r*&u1 /'e!-4-!*&-o1

Qu*&-&"

1 *ransformer 8<545<9 ) 1

2 Bmmeter 8452449 mB 1

3 )oltmeter 845249 ) 1

4 -1 Munction diode 11 444; 2

5 3esistor 4;4 ohm 1

< 'a!acitor 144 uf 1

; Decade 3esistance ox 555 1

A '32 5555 1

N read oard 5555 1

14 'onnecting wires L!robes 5555 Bs !er

re.uired

56

THEORY:

,n full wave rectification? current flows through the load in the same direction for

both cycles of in!ut B' voltage? this can be achieved with two diodes worCing alternatively. %or

the !ositive half cycle of in!ut the other diode so? current being always in same directions through

the load therefore? a full wave rectifier utili7e both half cycles of in!ut B' voltage to !roduce the

D' out!ut. *he following two circuits are commonly used for full wave rectification? 8i9 'enter #

ta! full wave rectifier. 8ii9 %ull wave bridge rectifier.

TABULATION K

'

8@%9

)r

8)9

)m

8)9

)rms

8)9

)dc

8)9

*heoretical

3i!!le factor

-ractical

3i!!le factor

FORMULA K

W,*62V* %,0*&3K

)rms ( )!! + 2 2

3i!!le %actor ( 8 )rms + )dc9

2

#1

-ercentage of 3egulation ( )10 5 )%0 + )%0 x 144

W,*6 %,0*&3K

)rms ( )!! + 2<

57

3i!!le factor r ( 8 )rms + )dc 9

-ercentage of 3egulation. ( )10 5 )%0 + )%0 x 144

)10 ( 1o load dc voltageE )%0 ( %ull load dc voltage.

MODEL GRAPH K

)o 8)olts9

INPUT SIGNAL

T#21%

/ITHOUT FILTER

T#21%

/ITH FILTER

T#21%

,DC #,o)&%

58

/-&0 4-)&er

/-&0 ou& 4-)&er

IDC #2A %

PROCEDURE K

1. $aCe the connections as shown in fig.

2. )ary the D3 in small ste!s? measure and record the corres!onding current ,dc and

voltage )dc readings.

3. -lot the gra!h by taCing ,dc along J5 axis and )dc along W # axis.

4. /tudy the in!ut and out!ut waveforms for the above connections using '32.

5. $easure the no load and full load voltage.

<. 'alculate the ri!!le factor and !ercentage of regulation.

;. $aCe the connections as shown in fig.

A. 3e!eat the ste!s 2 to <.

59

POSTLAB

1.What are the advantage of full wave rectifier?

2.What is the value of form factor?

3.6ow much diodes used in the full wave rectifier?

4.What is the use of center ta!!ed transformer?

5. What is the efficiency of %W3?

60

RESULT K

*hus the full wave rectifier with and without filter is constructed and tested.

1. 3i!!le factor with filter (

2. 3i!!le factor without filter (

3. -ercentage regulation with filter (

4. -ercentage regulation without filter (

EX NO:11 DOUBLE STAGE RC COUPLED AMPLIFIER

PRELAB

1. /0*& .o "ou 2e*& 3" .ou3)e 1&*+e RC !ou')e. *2')-4-er5

6. /0*& -1 &0e *.(*&*+e o4 &8o 1&*+e1 o4 !ou')-+5

7. /0*& *re &0e '*r*2e&er1 +e&1 !0*+e. - .ou3)e 1&*+e RC !ou')e.

*2')-4-er5

9. Dr*8 &0e !-r!u-& .-*+r*2 o4 RC !ou')e. *2')-4-er

:. Dr*8 &0e ou&'u& !0*r*!&er-1&-!1 o4 RC !ou')e. *2')-4-er.

61

EX NO:11 DOUBLE STAGE RC COUPLED AMPLIFIER

INLAB

C-r!u-& D-*+r*2

62

E;. No: 11

DOUBLE STAGE RC COUPLED AMPLIFIER

AIM

*o construct and test a double staged 3' cou!led am!lifier and to !lot the fre.uency

res!onse.

APPARATUS REQUIRED

S. No Co2'oe&1 S'e!-4-!*&-o1 Qu*&-&"

1 *ransistor ' 14; 2

2 3esistor 1 = &ach 2

63

2.4 =

3.2 =

<44>

3 'a!acitor 14 @ % 5

4 Dual -ower /u!!ly 84534)9 1

5 '32 55 1

< read board 55 1

; Wires 55

Bs

re.uired

A %unction :enerator 55 1

N -robe 555 2

THEORY

*he transistors used in this circuit are identical to each other. Bnd a common !ower

su!!ly is used. 3esistors are used to !rovide biasing voltages. *he cou!ling ca!acitors are used

to cou!le the out!ut of the one stage out!ut to next stage of the am!lifier. *he by!ass ca!acitor

!revents the loss in am!lification. *he out!ut of first stage is cou!led to the in!ut of the second

stage via cou!ling ca!acitor 'c which also serves as the blocCing ca!acitor to Cee! the D'

com!onent of the out!ut of first stage from reaching the in!ut of the second stage and to !ass B'

com!onent

MODEL GRAPH

64

TABULATION

,n!ut )oltage ( ).

/.1o %re.uency in 67 2ut!ut in volts :ain

:ain in d ( 24 log

)4+)i9

PROCEDURE

1. *he connections are given as !er the circuit diagram

65

2. 1ote down the in!ut voltage

3. )arying the fre.uency in the function generator and note down the out!ut voltage.

4. *he readings are taCen until the rece!tion of out!ut voltage occurs after constant values

5. :ain in decibels is calculated

<. 3eadings are !lotted in gra!h.

-2/* 0B

66

1. What are the drawbacCs of two stages of cou!ling?

2. What is the gain of 3' cou!led am!lifier?

3. What is the maximum bandwidth of 3' cou!led am!lifier?

4. Difference between 3' and 0' cou!led am!lifiers.

5. What do you infer from the out!ut of 3' cou!led am!lifier?

RESULT

*hus the double stage 3' cou!led am!lifier was constructed and fre.uency res!onses

were !lotted.

67

You might also like

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Manual Frecuenciometro Xplorer PDFDocument28 pagesManual Frecuenciometro Xplorer PDFHector GarciaNo ratings yet

- YAESU FT 8900R Service ManualDocument58 pagesYAESU FT 8900R Service ManualKuh TohNo ratings yet

- x3500 m5 x3550 m5 x3650 m5 Data Center Plan v1.0.4Document130 pagesx3500 m5 x3550 m5 x3650 m5 Data Center Plan v1.0.4joko purwNo ratings yet

- EDCDocument232 pagesEDClakshmipo67% (3)

- ASCDocument5 pagesASCmintoissacNo ratings yet

- Unit II - Signal Conditioning - MasterDocument33 pagesUnit II - Signal Conditioning - MasterSunitha SasiNo ratings yet

- 1U Switching Power Supplies: InstallationDocument2 pages1U Switching Power Supplies: Installationroben parsieNo ratings yet

- Scintilator ST450manualDocument13 pagesScintilator ST450manualtxe_scientistNo ratings yet

- Measurements & Instrumentation (ELE 306) RCSDocument2 pagesMeasurements & Instrumentation (ELE 306) RCSJithinNo ratings yet

- Introduction To Instrumentation Work SheetDocument4 pagesIntroduction To Instrumentation Work Sheetmeleseashenafi736No ratings yet

- Finisar Amplifier Ultraspan 1ru Raman Product BriefDocument2 pagesFinisar Amplifier Ultraspan 1ru Raman Product BriefMohamed AliNo ratings yet

- S 0859Document16 pagesS 0859bertan dağıstanlıNo ratings yet

- LM386-Aplicacion General NationalDocument10 pagesLM386-Aplicacion General NationalfcabreraibanezNo ratings yet

- Reviewer ExcelDocument4 pagesReviewer ExcelJC Tolentino67% (3)

- Chapter10 Integer-N Frequency SynthesizersDocument82 pagesChapter10 Integer-N Frequency SynthesizersNikunj ShahNo ratings yet

- 3A, 28V, 385Khz Step-Down Converter: The Future of Analog Ic TechnologyDocument11 pages3A, 28V, 385Khz Step-Down Converter: The Future of Analog Ic TechnologyerdaNo ratings yet

- CD-20 Sample Probe Controller User Manual: Clif Mock™Document16 pagesCD-20 Sample Probe Controller User Manual: Clif Mock™Gibran TorresNo ratings yet

- Autodialler PTU 8028 V2 and PTU 8028 D06 Installation ManualDocument19 pagesAutodialler PTU 8028 V2 and PTU 8028 D06 Installation ManualderbalijalelNo ratings yet

- Premier 816 Installation Manual - Iss 06Document83 pagesPremier 816 Installation Manual - Iss 06Esa Valtteri Vehviläinen50% (2)

- Opa 227 UADocument28 pagesOpa 227 UAraywizyNo ratings yet

- TIG 250EX Operator ManualDocument31 pagesTIG 250EX Operator Manualazharjaved2000100% (2)

- Experiment 4Document9 pagesExperiment 4mohammed_524176180No ratings yet

- Features Description: LTC3851 Synchronous Step-Down Switching Regulator ControllerDocument28 pagesFeatures Description: LTC3851 Synchronous Step-Down Switching Regulator ControllerDjems DjemsNo ratings yet

- Combinepdf 1Document34 pagesCombinepdf 1Nikola TušekNo ratings yet

- Monark Manual EnglishDocument49 pagesMonark Manual EnglishEzra Savadious100% (1)

- Current Research Paper: January 2013Document12 pagesCurrent Research Paper: January 2013other appsNo ratings yet

- Battery EliminatorDocument27 pagesBattery EliminatorVaibhav Soni67% (6)

- MA-3600VZ: Macro-Tech SeriesDocument2 pagesMA-3600VZ: Macro-Tech SeriesKevin MaduranNo ratings yet

- Uttarakhand TTA 2013 NotificationDocument13 pagesUttarakhand TTA 2013 NotificationReviewKeys.comNo ratings yet