Professional Documents

Culture Documents

SRAM Variability Measurements Description Project Objectives and

Uploaded by

api-19668941Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

SRAM Variability Measurements Description Project Objectives and

Uploaded by

api-19668941Copyright:

Available Formats

SRAM Variability Measurements

Faculty Investigator: Borivoje Nikolić, University of California, Berkeley

IBM Technical Contact: Kevin Nowka, IBM Austin Research Laboratory

Description

SRAM arrays occupy a large fraction of the chip area in many of today’s digital designs. As memory will continue to

consume a large fraction of many future designs, scaling of memory density must continue to track the scaling trends of

logic. Increased transistor leakage and parameter variations present challenges for scaling of conventional six-

transistor (6-T) SRAM cells. Statistical dopant fluctuations, variations in oxide thickness, and line-edge roughness

increase the spread in transistor threshold voltage and thus the on- and off- currents as the MOSFET is scaled down in

the nanoscale regime.

The functionality and density of a memory array are its most important properties. Functionality is guaranteed for large

memory arrays by providing sufficiently large design margins (to be able to be read without changing the state, to hold

the state, to be writable and to function in specified time), which are determined by device sizing (channel widths and

lengths), the supply voltage and, marginally, by the selection of transistor threshold voltages. Although upsizing the

transistors increases the noise margins, it increases the cell area and thus lowers the density. Since the control of

process variables does not track the scaling of minimum features, design margins would need to be increased to achieve

large functional memory arrays. This trend reverses the advantages of technology scaling, and has been perceived as a

major roadblock.

We plan to experimentally investigate the impact of the SRAM cell design and bitline column design on stability of the

memory. A test structure will be built that measures the distribution of the key design margins within the array. Various

arrays will be tested that differ in layouts and sizes of the memory cells as well as in different bitline organizations.

The key challenge in this project is to develop a test structure and an on-chip measurement circuitry that allows for

direct or indirect observation of noise margins within individual cells or groups of cells. Our approach relies on precise

on-chip current measurements with on-chip analog-to-digital conversion of measured values. This measurement will

involve obtaining:

1. Read currents vs. bitline leakage scatter plots for the cells in the array,

2. Estimation of the static noise margins in the cells

3. Estimation of the hold margins.

Read current, which is below 100uA in modern CMOS memories, can be accurately measured, e.g. using a single-slope

or a dual-slope analog-to-digital converter (ADC) that would be integrating the read current over the specified period of

time. In our previous projects we have demonstrated to be able to measure currents with 1-10nA accuracy. Measuring

the bitline leakage currents for short bitlines is significantly more challenging (currents are sub-1nA), requiring a

refinement in the measurement circuitry and the use of a dual-slope ADC. By writing various data into the cells and

then accessing them, a map of read and leakage currents can be obtained. Since the variations in the leakage currents

are larger than in read currents, because of their exponential dependence on the technology parameters, even low-

resolution measurements should provide interesting data when correlated with read currents.

Distribution of the SNMs in the array can be measured by dissecting the SRAM cells in halves and using a high-

resolution ADC. Alternatively, a distribution of SNM can be estimated by measuring the currents vs. voltages in the

cell storage nodes (these are known as ‘N-curves’ in IBM).

Finally, by lowering the wordline voltages during cell access either read/write access fails, another distribution in the

array can be achieved. Supply voltage can also be lowered and raised until the cell fails. The plot of minimum

voltages at which the hold margin is not compromised is yet another indication of variability.

Project objectives and goals

Objective of this research is to provide a methodology for on-chip measurements of variability in SRAM, as well as to

experimentally quantify the impact of the cell sizing and layout on a tradeoff between the density and stability. This

goal would be achieved through a theoretical study of variations in the memory and building of a test chip in 90nm or

65nm CMOS technology that evaluates the proposed ideas. Ultimately, the data collected through these experiments

will be used to design robust dense memory arrays. The measurement circuitry can be used for other precise on-chip

current and voltage measurements.

Long-term impact

Deceleration in memory scaling has been perceived as one of the major roadblocks to future technology scaling. The

measurement results from this project can be used to extend the scaling of static memory and CMOS technology in

general.

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Ultralow-Power SRAM TechnologyDocument14 pagesUltralow-Power SRAM Technologyapi-19668941No ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- X-Calibration-A Technique For Combating Excessive Bitline Leakage Current in Nanometer SRAM DesignsDocument8 pagesX-Calibration-A Technique For Combating Excessive Bitline Leakage Current in Nanometer SRAM Designsapi-19668941No ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- WARM SRAM - A Novel Scheme To Reduce Static Leakage Energy in SRAMDocument8 pagesWARM SRAM - A Novel Scheme To Reduce Static Leakage Energy in SRAMapi-19668941No ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Characterization of Low Voltage SRAM Response To Gamma RadiationDocument6 pagesCharacterization of Low Voltage SRAM Response To Gamma Radiationapi-19668941No ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Tomorrows High-Quality SoCs Require High-Quality Embedded Memories TodayDocument1 pageTomorrows High-Quality SoCs Require High-Quality Embedded Memories Todayapi-19668941No ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Ultra-Low Power 90nm 6T SRAM Cell For Wireless Sensor Network ApplicationsDocument4 pagesUltra-Low Power 90nm 6T SRAM Cell For Wireless Sensor Network Applicationsapi-19668941No ratings yet

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Term PaperDocument2 pagesTerm Paperapi-19668941No ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- SRAM Circuit With Expanded Operating Margin and Reduced Stand-By Leakage Current Using Thin-BOX FD-SOI TransistorsDocument7 pagesSRAM Circuit With Expanded Operating Margin and Reduced Stand-By Leakage Current Using Thin-BOX FD-SOI Transistorsapi-19668941No ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- News June07Document8 pagesNews June07api-19668941No ratings yet

- Statistically-Aware SRAM Memory Array DesignDocument17 pagesStatistically-Aware SRAM Memory Array Designapi-19668941No ratings yet

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- SRAM TechnologyDocument17 pagesSRAM Technologyapi-19668941No ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- SRAM Leakage Suppression by Minimizing Standby Supply VoltageDocument19 pagesSRAM Leakage Suppression by Minimizing Standby Supply Voltageapi-19668941No ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Static Energy Reduction Techniques For Microprocessor CachesDocument9 pagesStatic Energy Reduction Techniques For Microprocessor Cachesapi-19668941No ratings yet

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Statistical Data Stability and Leakage Evaluation of FinFET SRAM Cells With Dynamic Threshold Voltage Tuning Under Process Parameter FluctuationsDocument6 pagesStatistical Data Stability and Leakage Evaluation of FinFET SRAM Cells With Dynamic Threshold Voltage Tuning Under Process Parameter Fluctuationsapi-19668941No ratings yet

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- SRAM Leakage Suppression by Minimizing Standby Supply VoltageDocument6 pagesSRAM Leakage Suppression by Minimizing Standby Supply Voltageapi-19668941No ratings yet

- Review and Future Prospects of Low-Voltage RAM CircuitsDocument24 pagesReview and Future Prospects of Low-Voltage RAM Circuitsapi-19668941No ratings yet

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Seu - Sram As A Process MonitorDocument6 pagesSeu - Sram As A Process Monitorapi-19668941No ratings yet

- Power Supply Current Detectability of SRAM DefectsDocument7 pagesPower Supply Current Detectability of SRAM Defectsapi-19668941No ratings yet

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- #Reducing The Sub-Threshold and Gate-Tunneling Leakage of SRAMDocument6 pages#Reducing The Sub-Threshold and Gate-Tunneling Leakage of SRAMapi-19668941No ratings yet

- Memories I: Dr. T.Y. Chang Nthu Ee 2007.11.20 - 22 - 27Document38 pagesMemories I: Dr. T.Y. Chang Nthu Ee 2007.11.20 - 22 - 27api-19668941No ratings yet

- Optimum Supply Voltages For Minimization of Leakage Currents in SRAM in Stand-By ModeDocument5 pagesOptimum Supply Voltages For Minimization of Leakage Currents in SRAM in Stand-By Modeapi-19668941No ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Radiation Effects Challenges in 90nm Commercial-Density SRAMsDocument20 pagesRadiation Effects Challenges in 90nm Commercial-Density SRAMsapi-19668941No ratings yet

- Memory Design For Electrically Addressed Spatial Light ModulatorsDocument31 pagesMemory Design For Electrically Addressed Spatial Light Modulatorsapi-19668941No ratings yet

- Low-Leakage Asymmetric-Cell SRAMDocument15 pagesLow-Leakage Asymmetric-Cell SRAMapi-19668941No ratings yet

- Low Power Static RAM ArchitecturesDocument7 pagesLow Power Static RAM Architecturesapi-19668941No ratings yet

- Low-Power High-Performance and Dynamically Configured Multi-Port Cache Memory ArchitectureDocument6 pagesLow-Power High-Performance and Dynamically Configured Multi-Port Cache Memory Architectureapi-19668941No ratings yet

- Low-Leakage SRAM Design With Dual VT TransistorsDocument6 pagesLow-Leakage SRAM Design With Dual VT Transistorsapi-19668941No ratings yet

- Low-Leakage Asymmetric-Cell SRAM1Document4 pagesLow-Leakage Asymmetric-Cell SRAM1api-19668941No ratings yet

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Low Power Static RAM ArchitecturesDocument7 pagesLow Power Static RAM Architecturesapi-19668941No ratings yet

- BJT Load LineDocument5 pagesBJT Load LineSunilAjmeeraNo ratings yet

- Bogen MT60A & MT125B Booster AmplifiersDocument6 pagesBogen MT60A & MT125B Booster AmplifiersNeal BarrettNo ratings yet

- Low-Power and Fast Full Adder by Exploring New and Gates: XOR XnorDocument13 pagesLow-Power and Fast Full Adder by Exploring New and Gates: XOR XnorvishwasNo ratings yet

- M. SC Physics I and II Sem Practical ListDocument2 pagesM. SC Physics I and II Sem Practical Listycgoswami17% (6)

- Double Balanced Mic Amp Notes PDFDocument42 pagesDouble Balanced Mic Amp Notes PDFTiwi KeromoNo ratings yet

- ExperimentDocument3 pagesExperimentWacko AsahanNo ratings yet

- HTS Code Chapter 85Document87 pagesHTS Code Chapter 85Hoang Trung NguyenNo ratings yet

- FUNDAMENTALS of CMOS VLSI 5th SEM ECE PDFDocument190 pagesFUNDAMENTALS of CMOS VLSI 5th SEM ECE PDFVarunKaradesaiNo ratings yet

- BJT IntroductionDocument4 pagesBJT IntroductionMr KNo ratings yet

- TH 9800 ModsDocument4 pagesTH 9800 ModsBenjamin DoverNo ratings yet

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Ankita Hembram Class:IX-'B' Roll No.:3 Subject: Computer (The History, Applications and Generations of Computer)Document14 pagesAnkita Hembram Class:IX-'B' Roll No.:3 Subject: Computer (The History, Applications and Generations of Computer)Isha GoswamiNo ratings yet

- Experiment No: 1 Date: / / 20Document20 pagesExperiment No: 1 Date: / / 20programmerNo ratings yet

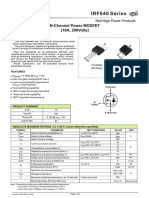

- IRF640 Series: N-Channel Power MOSFET (18A, 200volts) DescriptionDocument7 pagesIRF640 Series: N-Channel Power MOSFET (18A, 200volts) DescriptionAlam Macedo OlveraNo ratings yet

- Transparent ElectronicsDocument14 pagesTransparent ElectronicsgopiraamNo ratings yet

- Electronics Devices - CircuitsDocument355 pagesElectronics Devices - CircuitsEman AlbinoNo ratings yet

- Kang 1Document58 pagesKang 1123vidyaNo ratings yet

- BOM-speeduino v0.4.3 Compatible PCB For m40 Rev1.0Document1 pageBOM-speeduino v0.4.3 Compatible PCB For m40 Rev1.0Randol Rafael Reyes Rodriguez50% (2)

- Manual BJTDocument5 pagesManual BJTSubhadip MaityNo ratings yet

- CH 02 MOS Transistor TheoryDocument20 pagesCH 02 MOS Transistor Theorymuneeb.abrarNo ratings yet

- ECE221 MOSFETs-I SRMAP PDFDocument30 pagesECE221 MOSFETs-I SRMAP PDFRajeshNo ratings yet

- I. Passive ComponentsDocument7 pagesI. Passive Componentsdare beastNo ratings yet

- Wooley 1971Document10 pagesWooley 1971andre oliveiraNo ratings yet

- 9789353502355Document2 pages9789353502355Naveen B MNo ratings yet

- TXSR-805 - S-En1-921-OnkDocument243 pagesTXSR-805 - S-En1-921-Onkmc02701No ratings yet

- Assignment 3Document7 pagesAssignment 3nwaytk520No ratings yet

- BC556 THRU BC559: Small Signal Transistors (PNP)Document7 pagesBC556 THRU BC559: Small Signal Transistors (PNP)Martin Solano MamianNo ratings yet

- TV Radar PJDocument55 pagesTV Radar PJShiv Narayan AhirwarNo ratings yet

- American International University-Bangladesh (AIUB) Faculty of Engineering (EEE)Document5 pagesAmerican International University-Bangladesh (AIUB) Faculty of Engineering (EEE)Ahmed Bin MustafaNo ratings yet

- zn409 DatasheetDocument6 pageszn409 Datasheetian_newNo ratings yet

- EC6304-Electronic Circuits-I PDFDocument11 pagesEC6304-Electronic Circuits-I PDFShinu PaulNo ratings yet