Professional Documents

Culture Documents

Synchronous Buck Nexfet™ Power Block: Features Description

Uploaded by

Walter Apaza TiconaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Synchronous Buck Nexfet™ Power Block: Features Description

Uploaded by

Walter Apaza TiconaCopyright:

Available Formats

Output Current (A)

E

f

f

i

c

i

e

n

c

y

(

%

)

P

o

w

e

r

L

o

s

s

(

W

)

0 5 10 15 20

50 0

60 1

70 2

80 3

90 4

100 5

G029

V

GS

= 5V

V

IN

= 12V

V

OUT

= 1.3V

f

SW

= 500kHz

L

OUT

= 1H

T

A

= 25C

Efficiency

Power Loss

G

1R

D

1

S

2

D /S

2 1

G

1

G

2

S0474-04

ENABLE

ENABLE

PWM

GND

BST

DRVH

LL

DRVL

CSD86330Q3D Driver IC

V

DD

V

I

V

O

V

DD

Control

FET

Sync

FET

PWM

P0116-01

1

2

3 V

SW

V

SW

V

SW

4 B

G 5 T

GR

6 T

G

P

GND

(Pin 9)

7 V

IN

8 V

IN

C S D 8 6 3 3 0 Q 3 D

www.ti.com SLPS264C OCTOBER 2010 REVISED OCTOBER 2011

S y n ch r on ou s B u ck N e x F E T P owe r B l ock

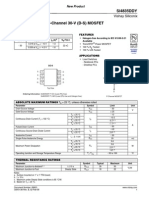

1F E AT URE S D E S C RIP T ION

The CSD86330Q3D NexFET power block is an

2 Hal f-B r idge P owe r B l ock

optimized design for synchronous buck applications

90 % S y s te m E fficie n cy at 15A

offering high current, high efficiency, and high

Up T o 20 A Ope r ation

frequency capability in a small 3.3-mm 3.3-mm

outline. Optimized for 5V gate drive applications, this

High F r e qu e n cy Ope r ation (Up T o 1.5MHz)

product offers a flexible solution capable of offering a

High D e n s ity S ON 3 .3 -mm 3 .3 -mm

high density power supply when paired with any 5V

F ootpr in t

gate drive froman external controller/driver.

Optimize d for 5V Gate D r ive

T E XT AD D E D F OR S P AC IN G

Low S witch in g Los s e s

T op Vie w

Ul tr a Low In du ctan ce P ack age

RoHS C ompl ian t

Hal oge n F r e e

P b-F r e e T e r min al P l atin g

AP P LIC AT ION S

S y n ch r on ou s B u ck C on ve r te r s

High F r e qu e n cy Appl ication s

T E XT AD D E D F OR S P AC IN G

ORD E RIN G IN F ORMAT ION

High C u r r e n t, Low D u ty C y cl e Appl ication s

D e vice P ack age Me dia Q ty S h ip

Mu l tiph as e S y n ch r on ou s B u ck C on ve r te r s

SON 3.3-mm3.3- 13-Inch Tape and

CSD86330Q3D 2500

P OL D C -D C C on ve r te r s mmPlastic Package Reel Reel

IMVP , VRM, an d VRD Appl ication s

TEXT ADDED FOR SPACING

TEXT ADDED FOR SPACING

TEXT ADDED FOR SPACING

T YP IC AL P OWE R B LOC K E F F IC IE N C Y

T YP IC AL C IRC UIT an d P OWE R LOS S

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2NexFET is a trademark of Texas Instruments.

PRODUCTION DATA information is current as of publication date.

Copyright 20102011, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

C S D 8 6 3 3 0 Q 3 D

SLPS264C OCTOBER 2010 REVISED OCTOBER 2011 www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

AB S OLUT E MAXIMUM RAT IN GS

T

A

=25C (unless otherwise noted)

(1)

P ar ame te r C on dition s VALUE UN IT

V

IN

to P

GND

0.8 to 25 V

Voltage range T

G

to T

GR

8 to 10 V

B

G

to P

GND

8 to 10 V

Pulsed Current Rating, I

DM

60 A

Power Dissipation, P

D

6 W

Sync FET, I

D

=65A, L =0.1mH 211

Avalanche Energy E

AS

mJ

Control FET, I

D

=42A, L =0.1mH 88

Operating J unction and Storage Temperature Range, T

J

, T

STG

55 to 150 C

(1) Stresses beyond those listed under Absolute MaximumRatings may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated is not implied. Exposure to absolute-

maximum-rated conditions for extended periods may affect device reliability.

RE C OMME N D E D OP E RAT IN G C ON D IT ION S

T

A

=25 (unless otherwise noted)

P ar ame te r C on dition s MIN MAX UN IT

Gate Drive Voltage, V

GS

4.5 8 V

Input Supply Voltage, V

IN

22 V

Switching Frequency, f

SW

C

BST

=0.1F (min) 200 1500 kHz

Operating Current 20 A

Operating Temperature, T

J

125 C

P OWE R B LOC K P E RF ORMAN C E

T

A

=25 (unless otherwise noted)

P ar ame te r C on dition s MIN T YP MAX UN IT

V

IN

=12V, V

GS

=5V,

V

OUT

=1.3V, I

OUT

=15A ,

Power Loss, P

LOSS

(1)

1.9 W

f

SW

=500kHz,

L

OUT

=1H, T

J

=25C

T

G

to T

GR

=0V

V

IN

Quiescent Current, I

QVIN

10 A

B

G

to P

GND

=0V

(1) Measurement made with six 10-F (TDK C3216X5R1C106KT or equivalent) ceramic capacitors placed across V

IN

to P

GND

pins and

using a high current 5V driver IC.

T HE RMAL IN F ORMAT ION

T

A

=25C (unless otherwise stated)

T HE RMAL ME T RIC MIN T YP MAX UN IT

J unction to ambient thermal resistance (Min Cu)

(1)

135

R

J A

J unction to ambient thermal resistance (Max Cu)

(1)(2)

73

C/W

J unction to case thermal resistance (Top of package)

(1)

29

R

J C

J unction to case thermal resistance (P

GND

Pin)

(1)

2.5

(1) R

J C

is determined with the device mounted on a 1-inch

2

(6.45-cm

2

), 2 oz. (0.071-mmthick) Cu pad on a 1.5-inch 1.5-inch

(3.81-cm3.81-cm), 0.06-inch (1.52-mm) thick FR4 board. R

J C

is specified by design while R

J A

is determined by the users board

design.

(2) Device mounted on FR4 material with 1-inch

2

(6.45-cm

2

) Cu.

2 Submit Documentation Feedback Copyright 20102011, Texas Instruments Incorporated

HD

HG

LG

LD

M0205-01

8

6

3

3

0

Q

3

D

3

3

x

3

3

M

I

N

R

e

v

0

.

.

LS

HS

HD

HG

LG

LD

M0206-01

8

6

3

3

0

Q

3

D

3

3

x

3

3

M

I

N

R

e

v

0

.

.

LS

HS

C S D 8 6 3 3 0 Q 3 D

www.ti.com SLPS264C OCTOBER 2010 REVISED OCTOBER 2011

E LE C T RIC AL C HARAC T E RIS T IC S

T

A

=25C (unless otherwise stated)

Q 1 C on tr ol F E T Q 2 S y n c F E T

P ARAME T E R T E S T C ON D IT ION S

MIN T YP MAX MIN T YP MAX UN IT

S tatic C h ar acte r is tics

BV

DSS

Drain to Source Voltage V

GS

=0V, I

DS

=250A 25 25 V

Drain to Source Leakage

I

DSS

V

GS

=0V, V

DS

=20V 1 1 A

Current

Gate to Source Leakage

I

GSS

V

DS

=0V, V

GS

=+10 / 8 100 100 nA

Current

Gate to Source Threshold

V

GS(th)

V

DS

=V

GS

, I

DS

=250A 0.9 1.4 2.1 0.9 1.1 1.6 V

Voltage

V

IN

=12V, V

GS

=5V,

V

OUT

=1.3V, I

OUT

=15A,

Z

DS(on)

Effective AC On-Impedance 8.8 3.3 m

f

SW

=500kHz,

L

OUT

=1H

g

fs

Transconductance V

DS

=15V, I

DS

=14A 52 82 S

D y n amic C h ar acte r is tics

C

ISS

Input Capacitance

(1)

710 920 1280 1660 pF

C

OSS

Output Capacitance

(1)

V

GS

=0V, V

DS

=12.5V, 350 455 680 880 pF

f =1MHz

Reverse Transfer

C

RSS

18 23 38 49 pF

Capacitance

(1)

R

G

Series Gate Resistance

(1)

1.5 3.0 1.2 2.4

Q

g

Gate Charge Total (4.5V)

(1)

4.8 6.2 9.2 12 nC

Q

gd

Gate Charge - Gate to Drain 0.9 1.6 nC

V

DS

=12.5V,

Gate Charge - Gate to

I

DS

=14A

Q

gs

1.6 2.1 nC

Source

Q

g(th)

Gate Charge at Vth 0.9 1.2 nC

Q

OSS

Output Charge V

DS

=15.5V, V

GS

=0V 7.2 13.6 nC

t

d(on)

Turn On Delay Time 4.9 5.3 ns

t

r

Rise Time 7.5 6.3 ns

V

DS

=12.5V, V

GS

=4.5V,

I

DS

=14A, R

G

=2

t

d(off)

Turn Off Delay Time 8.5 15.8 ns

t

f

Fall Time 1.9 4.2 ns

D iode C h ar acte r is tics

V

SD

Diode Forward Voltage I

DS

=14A, V

GS

=0V 0.85 1 0.8 1 V

Q

rr

Reverse Recovery Charge 3.9 7.3 nC

V

dd

=15.5V, I

F

=14A,

di/dt =300A/s

t

rr

Reverse Recovery Time 13.9 19 ns

(1) Specified by design

Max R

J A

=76C/W Max R

J A

=140C/W

when mounted on when mounted on

1 inch

2

(6.45 cm

2

) of 2- minimumpad area of

oz. (0.071-mmthick) 2-oz. (0.071-mmthick)

Cu. Cu.

Copyright 20102011, Texas Instruments Incorporated Submit Documentation Feedback 3

Board Temperature (C)

O

u

t

p

u

t

C

u

r

r

e

n

t

(

A

)

0 20 40 60 80 100 120 140

0

5

10

15

20

25

G005

Ambient Temperature (C)

O

u

t

p

u

t

C

u

r

r

e

n

t

(

A

)

0 10 20 30 40 50 60 70 80 90

0

5

10

15

20

25

G003

400LFM

200LFM

100LFM

Nat Conv

Ambient Temperature (C)

O

u

t

p

u

t

C

u

r

r

e

n

t

(

A

)

0 10 20 30 40 50 60 70 80 90

0

5

10

15

20

25

G004

400LFM

200LFM

100LFM

Nat Conv

Output Current (A)

P

o

w

e

r

L

o

s

s

(

W

)

0 2 4 6 8 10 12 14 16 18 20

0

0.5

1

1.5

2

2.5

3

3.5

4

G001

Junction Temperature ( C)

P

o

w

e

r

L

o

s

s

,

N

o

r

m

a

l

i

z

e

d

-50 -25 0 25 50 75 100 125 150

0.5

0.6

0.7

0.8

0.9

1

1.1

1.2

G002

C S D 8 6 3 3 0 Q 3 D

SLPS264C OCTOBER 2010 REVISED OCTOBER 2011 www.ti.com

T YP IC AL P OWE R B LOC K D E VIC E C HARAC T E RIS T IC S

Test Conditions: V

IN

=12V, V

DD

=5V, f

SW

=500kHz, V

OUT

=1.2V, L

OUT

=1.0H, I

OUT

=20A, T

J

=125C, unless stated

otherwise.

F igu r e 1. P owe r Los s vs Ou tpu t C u r r e n t F igu r e 2. P owe r Los s vs T e mpe r atu r e

F igu r e 3 . S afe Ope r atin g Ar e a P C B Ve r tical Mou n t

(1)

F igu r e 4. S afe Ope r atin g Ar e a P C B Hor izon tal Mou n t

(1)

F igu r e 5. T y pical S afe Ope r atin g Ar e a

(1)

(1) The Typical Power Block System Characteristic curves are based on measurements made on a PCB design with

dimensions of 4.0(W) 3.5(L) 0.062(H) and 6 copper layers of 1 oz. copper thickness. See Application Section

for detailed explanation.

4 Submit Documentation Feedback Copyright 20102011, Texas Instruments Incorporated

Output Voltage (V)

P

o

w

e

r

L

o

s

s

,

N

o

r

m

a

l

i

z

e

d

0.6 1.2 1.8 2.4 3 3.6 4.2 4.8 5.4

0.6

0.7

0.8

0.9

1

1.1

1.2

1.3

1.4

1.5

1.6

-10.5

-7.9

-5.2

-2.6

0

2.6

5.2

7.9

10.5

13.1

15.7

G008

S

O

A

T

e

m

p

e

r

a

t

u

r

e

A

d

j

(

C

)

Output Inductance (H)

P

o

w

e

r

L

o

s

s

,

N

o

r

m

a

l

i

z

e

d

0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 0.8 0.9 1 1.1

0.6

0.7

0.8

0.9

1

1.1

1.2

1.3

1.4

1.5

1.6

-10.5

-7.9

-5.2

-2.6

0

2.6

5.2

7.9

10.5

13.1

15.7

G009

S

O

A

T

e

m

p

e

r

a

t

u

r

e

A

d

j

(

C

)

Switching Frequency (kHz)

P

o

w

e

r

L

o

s

s

,

N

o

r

m

a

l

i

z

e

d

200 400 600 800 1000 1200 1400 1600

0.6

0.7

0.8

0.9

1

1.1

1.2

1.3

1.4

1.5

1.6

-10.5

-7.9

-5.2

-2.6

0

2.6

5.2

7.9

10.5

13.1

15.7

G006

S

O

A

T

e

m

p

e

r

a

t

u

r

e

A

d

j

(

C

)

Input Voltage (V)

P

o

w

e

r

L

o

s

s

,

N

o

r

m

a

l

i

z

e

d

3 6 9 12 15 18 21 24

0.6

0.7

0.8

0.9

1

1.1

1.2

1.3

1.4

1.5

1.6

-10.5

-7.8

-5.2

-2.6

0

2.6

5.2

7.8

10.5

13.1

15.7

G007

S

O

A

T

e

m

p

e

r

a

t

u

r

e

A

d

j

(

C

)

C S D 8 6 3 3 0 Q 3 D

www.ti.com SLPS264C OCTOBER 2010 REVISED OCTOBER 2011

T YP IC AL P OWE R B LOC K D E VIC E C HARAC T E RIS T IC S (con tin u e d)

Test Conditions: V

IN

=12V, V

DD

=5V, f

SW

=500kHz, V

OUT

=1.2V, L

OUT

=1.0H, I

OUT

=20A, T

J

=125C, unless stated

otherwise.

T E XT AD D E D F OR S P AC IN G T E XT AD D E D F OR S P AC IN G

F igu r e 6 . N or mal ize d P owe r Los s vs S witch in g F r e qu e n cy F igu r e 7. N or mal ize d P owe r Los s vs In pu t Vol tage

T E XT AD D E D F OR S P AC IN G T E XT AD D E D F OR S P AC IN G

F igu r e 8 . N or mal ize d P owe r Los s vs . Ou tpu t Vol tage F igu r e 9. N or mal ize d P owe r Los s vs . Ou tpu t In du ctan ce

Copyright 20102011, Texas Instruments Incorporated Submit Documentation Feedback 5

Q

g

- Gate Charge - nC

V

G

S

-

G

a

t

e

-

t

o

-

S

o

u

r

c

e

V

o

l

t

a

g

e

-

V

0 2 4 6 8

0

1

2

3

4

5

6

7

8

G014

I

D

= 14A

V

DS

= 12.5V

Q

g

- Gate Charge - nC

V

G

S

-

G

a

t

e

-

t

o

-

S

o

u

r

c

e

V

o

l

t

a

g

e

-

V

0 3 6 9 12 15

0

1

2

3

4

5

6

7

8

G015

I

D

= 14A

V

DS

= 12.5V

V

GS

- Gate-to-Source Voltage - V

I

D

S

-

D

r

a

i

n

-

t

o

-

S

o

u

r

c

e

C

u

r

r

e

n

t

-

A

1 1.5 2 2.5 3 3.5

0.001

0.01

0.1

1

10

100

T

C

= -55C

T

C

= 25C

T

C

= 125C

G012

V

DS

= 5V

V

GS

- Gate-to-Source Voltage - V

I

D

S

-

D

r

a

i

n

-

t

o

-

S

o

u

r

c

e

C

u

r

r

e

n

t

-

A

0.5 0.75 1 1.25 1.5 1.75 2 2.25 2.5

0.001

0.01

0.1

1

10

100

T

C

= -55C

T

C

= 25C

T

C

= 125C

G013

V

DS

= 5V

V

DS

- Drain-to-Source Voltage - V

I

D

S

-

D

r

a

i

n

-

t

o

-

S

o

u

r

c

e

C

u

r

r

e

n

t

-

A

0 0.2 0.4 0.6 0.8 1

0

10

20

30

40

50

60

V

GS

= 4.5V

V

GS

= 6V

V

GS

= 8V

G010

V

DS

- Drain-to-Source Voltage - V

I

D

S

-

D

r

a

i

n

-

t

o

-

S

o

u

r

c

e

C

u

r

r

e

n

t

-

A

0 0.05 0.1 0.15 0.2 0.25 0.3

0

10

20

30

40

50

60

V

GS

= 4.5V

V

GS

= 6V

V

GS

= 8V

G011

C S D 8 6 3 3 0 Q 3 D

SLPS264C OCTOBER 2010 REVISED OCTOBER 2011 www.ti.com

T YP IC AL P OWE R B LOC K MOS F E T C HARAC T E RIS T IC S

T

A

=25C, unless stated otherwise.

T E XT AD D E D F OR S P AC IN G T E XT AD D E D F OR S P AC IN G

F igu r e 10 . C on tr ol MOS F E T S atu r ation F igu r e 11. S y n c MOS F E T S atu r ation

T E XT AD D E D F OR S P AC IN G T E XT AD D E D F OR S P AC IN G

F igu r e 12. C on tr ol MOS F E T T r an s fe r F igu r e 13 . S y n c MOS F E T T r an s fe r

T E XT AD D E D F OR S P AC IN G T E XT AD D E D F OR S P AC IN G

F igu r e 14. C on tr ol MOS F E T Gate C h ar ge F igu r e 15. S y n c MOS F E T Gate C h ar ge

6 Submit Documentation Feedback Copyright 20102011, Texas Instruments Incorporated

V

GS

- Gate-to-Source Voltage - V

R

D

S

(

o

n

)

-

O

n

-

S

t

a

t

e

R

e

s

i

s

t

a

n

c

e

-

m

0 1 2 3 4 5 6 7 8 9 10

0

5

10

15

20

25

T

C

= 25C

T

C

= 125C

G020

I

D

= 14A

V

GS

- Gate-to-Source Voltage - V

R

D

S

(

o

n

)

-

O

n

-

S

t

a

t

e

R

e

s

i

s

t

a

n

c

e

-

m

0 1 2 3 4 5 6 7 8 9 10

0

2

4

6

8

10

12

14

16

T

C

= 25C

T

C

= 125C

G021

I

D

= 14A

T

C

- Case Temperature - C

V

G

S

(

t

h

)

-

T

h

r

e

s

h

o

l

d

V

o

l

t

a

g

e

-

V

-75 -25 25 75 125 175

0

0.2

0.4

0.6

0.8

1

1.2

1.4

1.6

1.8

G018

I

D

= 250A

T

C

- Case Temperature - C

V

G

S

(

t

h

)

-

T

h

r

e

s

h

o

l

d

V

o

l

t

a

g

e

-

V

-75 -25 25 75 125 175

0

0.2

0.4

0.6

0.8

1

1.2

1.4

1.6

1.8

G019

I

D

= 250A

V

DS

- Drain-to-Source Voltage - V

C

-

C

a

p

a

c

i

t

a

n

c

e

-

n

F

0 5 10 15 20 25

0.001

0.01

0.1

1

10

C

iss

= C

gd

+ C

gs

C

oss

= C

ds

+ C

gd

C

rss

= C

gd

G016

f = 1MHz

V

GS

= 0V

V

DS

- Drain-to-Source Voltage - V

C

-

C

a

p

a

c

i

t

a

n

c

e

-

n

F

0 5 10 15 20 25

0.01

0.1

1

10

C

iss

= C

gd

+ C

gs

C

oss

= C

ds

+ C

gd

C

rss

= C

gd

G017

f = 1MHz

V

GS

= 0V

C S D 8 6 3 3 0 Q 3 D

www.ti.com SLPS264C OCTOBER 2010 REVISED OCTOBER 2011

T YP IC AL P OWE R B LOC K MOS F E T C HARAC T E RIS T IC S (con tin u e d)

T

A

=25C, unless stated otherwise.

T E XT AD D E D F OR S P AC IN G T E XT AD D E D F OR S P AC IN G

F igu r e 16 . C on tr ol MOS F E T C apacitan ce F igu r e 17. S y n c MOS F E T C apacitan ce

T E XT AD D E D F OR S P AC IN G T E XT AD D E D F OR S P AC IN G

F igu r e 18 . C on tr ol MOS F E T V

GS (th )

F igu r e 19. S y n c MOS F E T V

GS (th )

T E XT AD D E D F OR S P AC IN G T E XT AD D E D F OR S P AC IN G

F igu r e 20 . C on tr ol MOS F E T R

D S (on )

vs V

GS

F igu r e 21. S y n c MOS F E T R

D S (on )

vs V

GS

Copyright 20102011, Texas Instruments Incorporated Submit Documentation Feedback 7

t

(AV)

- Time in Avalanche - ms

I

(

A

V

)

-

P

e

a

k

A

v

a

l

a

n

c

h

e

C

u

r

r

e

n

t

-

A

0.01 0.1 1 10

1

10

100

T

C

= 25C

T

C

= 125C

G026

I

(AV)

= t

(AV)

(0.021 L)

t

(AV)

- Time in Avalanche - ms

I

(

A

V

)

-

P

e

a

k

A

v

a

l

a

n

c

h

e

C

u

r

r

e

n

t

-

A

0.01 0.1 1 10

1

10

100

T

C

= 25C

T

C

= 125C

G027

I

(AV)

= t

(AV)

(0.021 L)

V

SD

- Source-to-Drain Voltage - V

I

S

D

-

S

o

u

r

c

e

-

t

o

-

D

r

a

i

n

C

u

r

r

e

n

t

-

A

0 0.2 0.4 0.6 0.8 1 1.2

0.0001

0.001

0.01

0.1

1

10

100

T

C

= 25C

T

C

= 125C

G024

V

SD

- Source-to-Drain Voltage - V

I

S

D

-

S

o

u

r

c

e

-

t

o

-

D

r

a

i

n

C

u

r

r

e

n

t

-

A

0 0.2 0.4 0.6 0.8 1 1.2

0.0001

0.001

0.01

0.1

1

10

100

T

C

= 25C

T

C

= 125C

G025

T

C

- Case Temperature - C

N

o

r

m

a

l

i

z

e

d

O

n

-

S

t

a

t

e

R

e

s

i

s

t

a

n

c

e

-75 -25 25 75 125 175

0

0.2

0.4

0.6

0.8

1

1.2

1.4

1.6

G022

I

D

= 14A

V

GS

= 8V

T

C

- Case Temperature - C

N

o

r

m

a

l

i

z

e

d

O

n

-

S

t

a

t

e

R

e

s

i

s

t

a

n

c

e

-75 -25 25 75 125 175

0

0.2

0.4

0.6

0.8

1

1.2

1.4

1.6

G023

I

D

= 14A

V

GS

= 8V

C S D 8 6 3 3 0 Q 3 D

SLPS264C OCTOBER 2010 REVISED OCTOBER 2011 www.ti.com

T YP IC AL P OWE R B LOC K MOS F E T C HARAC T E RIS T IC S (con tin u e d)

T

A

=25C, unless stated otherwise.

T E XT AD D E D F OR S P AC IN G T E XT AD D E D F OR S P AC IN G

F igu r e 22. C on tr ol MOS F E T N or mal ize d R

D S (on )

F igu r e 23 . S y n c MOS F E T N or mal ize d R

D S (on )

T E XT AD D E D F OR S P AC IN G T E XT AD D E D F OR S P AC IN G

F igu r e 24. C on tr ol MOS F E T B ody D iode F igu r e 25. S y n c MOS F E T B ody D iode

T E XT AD D E D F OR S P AC IN G T E XT AD D E D F OR S P AC IN G

F igu r e 26 . C on tr ol MOS F E T Un cl ampe d In du ctive S witch in g F igu r e 27. S y n c MOS F E T Un cl ampe d In du ctive S witch in g

8 Submit Documentation Feedback Copyright 20102011, Texas Instruments Incorporated

C S D 8 6 3 3 0 Q 3 D

www.ti.com SLPS264C OCTOBER 2010 REVISED OCTOBER 2011

AP P LIC AT ION IN F ORMAT ION

E qu ival e n t S y s te m P e r for man ce

Many of todays high performance computing systems require low power consumption in an effort to reduce

system operating temperatures and improve overall system efficiency. This has created a major emphasis on

improving the conversion efficiency of todays Synchronous Buck Topology. In particular, there has been an

emphasis in improving the performance of the critical Power Semiconductor in the Power Stage of this

Application (see Figure 28). As such, optimization of the power semiconductors in these applications, needs to

go beyond simply reducing R

DS(ON)

.

F igu r e 28 .

The CSD86330Q3D is part of TIs Power Block product family which is a highly optimized product for use in a

synchronous buck topology requiring high current, high efficiency, and high frequency. It incorporates TIs latest

generation silicon which has been optimized for switching performance, as well as minimizing losses associated

with Q

GD

, Q

GS

, and Q

RR

. Furthermore, TIs patented packaging technology has minimized losses by nearly

eliminating parasitic elements between the Control FET and Sync FET connections (see Figure 29). A key

challenge solved by TIs patented packaging technology is the system level impact of Common Source

Inductance (CSI). CSI greatly impedes the switching characteristics of any MOSFET which in turn increases

switching losses and reduces systemefficiency. As a result, the effects of CSI need to be considered during the

MOSFET selection process. In addition, standard MOSFET switching loss equations used to predict system

efficiency need to be modified in order to account for the effects of CSI. Further details behind the effects of CSI

and modification of switching loss equations are outlined in TIs Application Note SLPA009.

F igu r e 29.

Copyright 20102011, Texas Instruments Incorporated Submit Documentation Feedback 9

78

80

82

84

86

88

90

92

94

96

2 4 6 8 10 12 14 16 18 20 22

Output Current (A)

E

f

f

i

c

i

e

n

c

y

(

%

)

PowerBlock HS/LS R

DS(ON)

= 8.8m/4.6m

Discrete HS/LS R

DS(ON)

= 8.8m/4.6m

Discrete HS/LS R

DS(ON)

= 8.8m/3.3m

V

GS

= 5V

V

IN

= 12V

V

OUT

= 1.3V

L

OUT

= 1H

f

SW

= 500kHz

T

A

= 25C

0

0.5

1

1.5

2

2.5

3

3.5

4

4.5

0 2 4 6 8 10 12 14 16 18 20 22

Output Current (A)

P

o

w

e

r

L

o

s

s

(

W

)

PowerBlock HS/LS R

DS(ON)

= 8.8m/4.6m

Discrete HS/LS R

DS(ON)

= 8.8m/4.6m

Discrete HS/LS R

DS(ON)

= 8.8m/3.3m

V

GS

= 5V

V

IN

= 12V

V

OUT

= 1.3V

L

OUT

= 1H

f

SW

= 500kHz

T

A

= 25C

C S D 8 6 3 3 0 Q 3 D

SLPS264C OCTOBER 2010 REVISED OCTOBER 2011 www.ti.com

The combination of TIs latest generation silicon and optimized packaging technology has created a

benchmarking solution that outperforms industry standard MOSFET chipsets of similar R

DS(ON)

and MOSFET

chipsets with lower R

DS(ON)

. and compare the efficiency and power loss performance of the CSD86330Q3D

versus industry standard MOSFET chipsets commonly used in this type of application. This comparison purely

focuses on the efficiency and generated loss of the power semiconductors only. The performance of

CSD86330Q3D clearly highlights the importance of considering the Effective AC On-Impedance (Z

DS(ON)

) during

the MOSFET selection process of any new design. Simply normalizing to traditional MOSFET R

DS(ON)

specifications is not an indicator of the actual in-circuit performance when using TIs Power Block technology.

TEXT ADDED FOR SPACING

F igu r e 3 0 . F igu r e 3 1.

The chart below compares the traditional DC measured R

DS(ON)

of CSD86330Q3D versus its Z

DS(ON)

. This

comparison takes into account the improved efficiency associated with TIs patented packaging technology. As

such, when comparing TIs Power Block products to individually packaged discrete MOSFETs or dual MOSFETs

in a standard package, the in-circuit switching performance of the solution must be considered. In this example,

individually packaged discrete MOSFETs or dual MOSFETs in a standard package would need to have DC

measured R

DS(ON)

values that are equivalent to CSD86330Q3Ds Z

DS(ON)

value in order to have the same

efficiency performance at full load. Mid to light-load efficiency will still be lower with individually packaged discrete

MOSFETs or dual MOSFETs in a standard package.

C ompar is on of R

D S (ON )

vs . Z

D S (ON )

HS LS

P ar ame te r

T y p Max T y p Max

Effective AC On-Impedance Z

DS(ON)

(V

GS

=5V) 8.8 - 3.3 -

DC Measured R

DS(ON)

(V

GS

=4.5V) 8.8 11.5 4.6 6

10 Submit Documentation Feedback Copyright 20102011, Texas Instruments Incorporated

PWM

ENABLE

PWM

GND

BST

DRVH

LL

DRVL

CSD86330Q3D Driver IC

V

DD

Gate Drive

Current (I )

DD

Input Current (I )

IN

Input Voltage (V )

IN

Output Current (I )

OUT

T

GR

V

IN

P

GND

V

I

V

O

V

SW

T

G

B

G

Gate Drive

Voltage (V )

DD

V

DD

A

V

V

V

Control

FET

Sync

FET

Averaging

Circuit

Averaged Switched

Node Voltage

(V

SW_AVG

)

A

S0475-04

A

C S D 8 6 3 3 0 Q 3 D

www.ti.com SLPS264C OCTOBER 2010 REVISED OCTOBER 2011

The CSD86330Q3D NexFET power block is an optimized design for synchronous buck applications using 5V

gate drive. The Control FET and Sync FET silicon are parametrically tuned to yield the lowest power loss and

highest systemefficiency. As a result, a newrating method is needed which is tailored towards a more systems

centric environment. System level performance curves such as Power Loss, Safe Operating Area, and

normalized graphs allowengineers to predict the product performance in the actual application.

P owe r Los s C u r ve s

MOSFET centric parameters such as R

DS(ON)

and Q

gd

are needed to estimate the loss generated by the devices.

In an effort to simplify the design process for engineers, Texas Instruments has provided measured power loss

performance curves. Figure 1 plots the power loss of the CSD86330Q3D as a function of load current. This curve

is measured by configuring and running the CSD86330Q3D as it would be in the final application (see

Figure 32).The measured power loss is the CSD86330Q3D loss and consists of both input conversion loss and

gate drive loss. Equation 1 is used to generate the power loss curve.

(V

IN

I

IN

) +(V

DD

I

DD

) (V

SW_AVG

I

OUT

) =Power Loss (1)

The power loss curve in Figure 1 is measured at the maximum recommended junction temperatures of 125C

under isothermal test conditions.

S afe Ope r atin g C u r ve s (S OA)

The SOA curves in the CSD86330Q3D data sheet provides guidance on the temperature boundaries within an

operating systemby incorporating the thermal resistance and systempower loss. Figure 3 to Figure 5 outline the

temperature and airflow conditions required for a given load current. The area under the curve dictates the safe

operating area. All the curves are based on measurements made on a PCB design with dimensions of 4 (W)

3.5(L) 0.062(T) and 6 copper layers of 1 oz. copper thickness.

N or mal ize d C u r ve s

The normalized curves in the CSD86330Q3D data sheet provides guidance on the Power Loss and SOA

adjustments based on their application specific needs. These curves show how the power loss and SOA

boundaries will adjust for a given set of systems conditions. The primary Y-axis is the normalized change in

power loss and the secondary Y-axis is the change is systemtemperature required in order to comply with the

SOA curve. The change in power loss is a multiplier for the Power Loss curve and the change in temperature is

subtracted fromthe SOA curve.

F igu r e 3 2. T y pical Appl ication

Copyright 20102011, Texas Instruments Incorporated Submit Documentation Feedback 11

Board Temperature ( C)

0 20 40 60 80 100 120 140

0

5

10

15

20

25

G028

V = 5V

GS

V = 12V

V = 1.3V

f = 500kHz

L = 1 H

IN

OUT

SW

OUT

m

O

u

t

p

u

t

C

u

r

r

e

n

t

(

A

)

1

2

3

C S D 8 6 3 3 0 Q 3 D

SLPS264C OCTOBER 2010 REVISED OCTOBER 2011 www.ti.com

C al cu l atin g P owe r Los s an d S OA

The user can estimate product loss and SOA boundaries by arithmetic means (see Design Example). Though

the Power Loss and SOA curves in this data sheet are taken for a specific set of test conditions, the following

procedure will outline the steps the user should take to predict product performance for any set of system

conditions.

D e s ign E x ampl e

Operating Conditions:

Output Current =15A

Input Voltage =12V

Output Voltage =1.2V

Switching Frequency =1000kHz

Inductor =0.4H

C al cu l atin g P owe r Los s

Power Loss at 15A =2.2W (Figure 1)

Normalized Power Loss for input voltage 1.0 (Figure 7)

Normalized Power Loss for output voltage 0.98 (Figure 8)

Normalized Power Loss for switching frequency 1.17 (Figure 6)

Normalized Power Loss for output inductor 1.06 (Figure 9)

F in al cal cu l ate d P owe r Los s = 2.2W 1.0 0 .98 1.17 1.0 6 2.6 7W

C al cu l atin g S OA Adju s tme n ts

SOA adjustment for input voltage 0C (Figure 7)

SOA adjustment for output voltage 0.29C (Figure 8)

SOA adjustment for switching frequency 4.1C (Figure 6)

SOA adjustment for output inductor 1.5C (Figure 9)

F in al cal cu l ate d S OA adju s tme n t = 0 + (0 .29) + 4.1 + 1.5 5.3 C

In the design example above, the estimated power loss of the CSD86330Q3D would increase to 2.67W. In

addition, the maximumallowable board and/or ambient temperature would have to decrease by 5.3C. Figure 33

graphically shows howthe SOA curve would be adjusted accordingly.

1. Start by drawing a horizontal line fromthe application current to the SOA curve.

2. Drawa vertical line fromthe SOA curve intercept down to the board/ambient temperature.

3. Adjust the SOA board/ambient temperature by subtracting the temperature adjustment value.

In the design example, the SOA temperature adjustment yields a reduction in allowable board/ambient

temperature of 5.3C. In the event the adjustment value is a negative number, subtracting the negative number

would yield an increase in allowable board/ambient temperature.

F igu r e 3 3 . P owe r B l ock S OA

12 Submit Documentation Feedback Copyright 20102011, Texas Instruments Incorporated

C S D 8 6 3 3 0 Q 3 D

www.ti.com SLPS264C OCTOBER 2010 REVISED OCTOBER 2011

RE C OMME N D E D P C B D E S IGN OVE RVIE W

There are two key system-level parameters that can be addressed with a proper PCB design: Electrical and

Thermal performance. Properly optimizing the PCB layout will yield maximumperformance in both areas. A brief

description on howto address each parameter is provided.

E l e ctr ical P e r for man ce

The Power Block has the ability to switch voltages at rates greater than 10kV/s. Special care must be then

taken with the PCB layout design and placement of the input capacitors, Driver IC, and output inductor.

The placement of the input capacitors relative to the Power Blocks VIN and PGND pins should have the

highest priority during the component placement routine. It is critical to minimize these node lengths. As such,

ceramic input capacitors need to be placed as close as possible to the VIN and PGND pins (see Figure 34).

The example in Figure 34 uses 6 10-F ceramic capacitors (TDK Part #C3216X5R1C106KT or equivalent).

Notice there are ceramic capacitors on both sides of the board with an appropriate amount of vias

interconnecting both layers. In terms of priority of placement next to the Power Block, C5, C7, C19, and C8

should followin order.

The Driver IC should be placed relatively close to the Power Block Gate pins. T

G

and B

G

should connect to

the outputs of the Driver IC. The T

GR

pin serves as the return path of the high-side gate drive circuitry and

should be connected to the Phase pin of the IC (sometimes called LX, LL, SW, PH, etc.). The bootstrap

capacitor for the Driver IC will also connect to this pin.

The switching node of the output inductor should be placed relatively close to the Power Block VSW pins.

Minimizing the node length between these two components will reduce the PCB conduction losses and

actually reduce the switching noise level.

In the event the switch node waveform exhibits ringing that reaches undesirable levels, the use of a Boost

Resistor or RC snubber can be an effective way to reduce the peak ring level. The recommended Boost

Resistor value will range between 1 to 4.7 depending on the output characteristics of Driver IC used in

conjunction with the Power Block. The RC snubber values can range from0.5 to 2.2 for the R and 330pF

to 2200pF for the C. Refer to TI App Note SLUP100 for more details on howto properly tune the RC snubber

values. The RC snubber should be placed as close as possible to the Vswnode and PGND see Figure 34

(1)

(1) Keong W. Kam, David Pommerenke, EMI Analysis Methods for Synchronous Buck Converter EMI Root Cause Analysis, University of

Missouri Rolla

Copyright 20102011, Texas Instruments Incorporated Submit Documentation Feedback 13

C S D 8 6 3 3 0 Q 3 D

SLPS264C OCTOBER 2010 REVISED OCTOBER 2011 www.ti.com

T h e r mal P e r for man ce

The Power Block has the ability to utilize the GND planes as the primary thermal path. As such, the use of

thermal vias is an effective way to pull away heat fromthe device and into the systemboard. Concerns of solder

voids and manufacturability problems can be addressed by the use of three basic tactics to minimize the amount

of solder attach that will wick down the via barrel:

Intentionally space out the vias fromeach other to avoid a cluster of holes in a given area.

Use the smallest drill size allowed in your design. The example in Figure 34 uses vias with a 10 mil drill hole

and a 16 mil capture pad.

Tent the opposite side of the via with solder-mask.

In the end, the number and drill size of the thermal vias should align with the end users PCB design rules and

manufacturing capabilities.

F igu r e 3 4. Re comme n de d P C B Lay ou t (T op D own )

14 Submit Documentation Feedback Copyright 20102011, Texas Instruments Incorporated

M0192-01

E1

E

q

5

6

7

8

1

2

3

4

L

d1

d2 K

b

d3

L

e

A

E2

D2

Top View

Bottom View

Side View

5

9

6

7

8

1

2

3

4

q

c1

D1

d

c

Exposed tie clips may vary

Pinout

Position Designation

Pin 1 V

IN

Pin 2 V

IN

Pin 3 T

G

Pin 4 T

GR

Pin 5 B

G

Pin 6 V

SW

Pin 7 V

SW

Pin 8 V

SW

Pin 9 P

GND

C S D 8 6 3 3 0 Q 3 D

www.ti.com SLPS264C OCTOBER 2010 REVISED OCTOBER 2011

ME C HAN IC AL D AT A

Q 3 D P ack age D ime n s ion s

MILLIME T E RS IN C HE S

D IM

MIN MAX MIN MAX

A 1.40 1.5 0.055 0.059

b 0.280 0.400 0.011 0.016

c 0.150 0.250 0.006 0.010

c1 0.150 0.250 0.006 0.010

d 0.940 1.040 0.037 0.041

d1 0.160 0.260 0.006 0.010

d2 0.150 0.250 0.006 0.010

d3 0.250 0.350 0.010 0.014

D1 3.200 3.400 0.126 0.134

D2 2.650 2.750 0.104 0.108

E 3.200 3.400 0.126 0.134

E1 3.200 3.400 0.126 0.134

E2 1.750 1.850 0.069 0.073

e 0.650 TYP 0.026 TYP

L 0.400 0.500 0.016 0.020

0.00

K 0.300 TYP 0.012 TYP

Copyright 20102011, Texas Instruments Incorporated Submit Documentation Feedback 15

0.300 (0.012)

0.300 (0.012)

0.300

(0.012)

1

4

5

8

M0207-01

0.340

(0.013)

0.333

(0.013)

0.100

(0.004)

3.500 (0.138)

0.160 (0.005)

0.200 (0.008) 0.550 (0.022)

2.290

(0.090)

0.350 (0.014)

0.850 (0.033)

0.990

(0.039)

0.200

(0.008)

0.350 (0.014)

0.210

(0.008)

1

4

5

8

M0193-01

0.440

(0.017)

0.210

(0.008)

1.900 (0.075)

0.300 (0.012)

0.650 (0.026) 0.650 (0.026)

3.600 (0.142)

2.800

(0.110)

0.650

(0.026)

1.090

(0.043)

2.390

(0.094)

C S D 8 6 3 3 0 Q 3 D

SLPS264C OCTOBER 2010 REVISED OCTOBER 2011 www.ti.com

Lan d P atte r n Re comme n dation

NOTE: Dimensions are in mm(inches).

S te n cil Re comme n dation

NOTE: Dimensions are in mm(inches).

For recommended circuit layout for PCB designs, see application note SLPA005 Reducing Ringing Through

PCB Layout Techniques.

16 Submit Documentation Feedback Copyright 20102011, Texas Instruments Incorporated

4.00 0.10 (See Note 1) 2.00 0.05

3

.

6

0

3.60

1

.

3

0

1

.

7

5

0

.

1

0

M0144-01

8.00 0.10

1

2

.

0

0

+

0

.

3

0

0

.

1

0

5

.

5

0

0

.

0

5

1.50

+0.10

0.00

C S D 8 6 3 3 0 Q 3 D

www.ti.com SLPS264C OCTOBER 2010 REVISED OCTOBER 2011

Q 3 D T ape an d Re e l In for mation

NOTES: 1. 10-sprocket hole-pitch cumulative tolerance 0.2

2. Camber not to exceed 1mmin 100mm, noncumulative over 250mm

3. Material: black static-dissipative polystyrene

4. All dimensions are in mm, unless otherwise specified.

5. Thickness: 0.30 0.05mm

6. MSL1 260C (IR and convection) PbF reflowcompatible

Spacer

RE VIS ION HIS T ORY

C h an ge s fr om Or igin al (Octobe r 20 10 ) to Re vis ion A P age

Changed I

OUT

Conditions From: 20A To: 15A, and the TYP value From: 2.9W To: 1.9W ................................................... 2

C h an ge s fr om Re vis ion A (D e ce mbe r 20 10 ) to Re vis ion B P age

Change R

DS(on)

to Z

DS(on)

....................................................................................................................................................... 3

Add Equivalent SystemPerformance section ....................................................................................................................... 9

Added Electrical Performance bullet ................................................................................................................................... 13

C h an ge s fr om Re vis ion C (S e pte mbe r 20 11) to Re vis ion C P age

Changed "DIM a" Millimeter Max value From: 1.55 To: 1.5 and Inches Max value From: 0.061 To: 0.059 ...................... 15

Copyright 20102011, Texas Instruments Incorporated Submit Documentation Feedback 17

TAPE AND REEL INFORMATION

*All dimensions are nominal

Device Package

Type

Package

Drawing

Pins SPQ Reel

Diameter

(mm)

Reel

Width

W1 (mm)

A0

(mm)

B0

(mm)

K0

(mm)

P1

(mm)

W

(mm)

Pin1

Quadrant

CSD86330Q3D LSON-

CLIP

DQZ 8 2500 330.0 12.4 3.55 3.55 1.7 8.0 12.0 Q1

PACKAGE MATERIALS INFORMATION

www.ti.com 15-Apr-2014

Pack Materials-Page 1

*All dimensions are nominal

Device Package Type Package Drawing Pins SPQ Length (mm) Width (mm) Height (mm)

CSD86330Q3D LSON-CLIP DQZ 8 2500 367.0 367.0 35.0

PACKAGE MATERIALS INFORMATION

www.ti.com 15-Apr-2014

Pack Materials-Page 2

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other

changes to its semiconductor products and services per J ESD46, latest issue, and to discontinue any product or service per J ESD48, latest

issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and

complete. All semiconductor products (also referred to herein as components) are sold subject to TIs terms and conditions of sale

supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TIs terms

and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary

to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily

performed.

TI assumes no liability for applications assistance or the design of Buyers products. Buyers are responsible for their products and

applications using TI components. To minimize the risks associated with Buyers products and applications, Buyers should provide

adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or

other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information

published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or

endorsement thereof. Use of such information may require a license froma third party under the patents or other intellectual property of the

third party, or a license fromTI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration

and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered

documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different fromor beyond the parameters stated by TI for that component or service

voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice.

TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements

concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support

that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which

anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause

harmand take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use

of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TIs goal is to

help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and

requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties

have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or enhanced plasticare designed and intended for use in

military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components

which have not been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and

regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of

non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive

Amplifiers amplifier.ti.com Communications and Telecom www.ti.com/communications

Data Converters dataconverter.ti.com Computers and Peripherals www.ti.com/computers

DLPProducts www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP dsp.ti.com Energy and Lighting www.ti.com/energy

Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial

Interface interface.ti.com Medical www.ti.com/medical

Logic logic.ti.com Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

RFID www.ti-rfid.com

OMAP Applications Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity www.ti.com/wirelessconnectivity

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright 2014, Texas Instruments Incorporated

You might also like

- Irl 3803Document9 pagesIrl 3803Prashath KugalaNo ratings yet

- 5A, 28V Input, Step Down Swift™ DC/DC Converter With Eco-Mode™Document27 pages5A, 28V Input, Step Down Swift™ DC/DC Converter With Eco-Mode™thunderer2014No ratings yet

- Irf 4905Document9 pagesIrf 4905Andre Vitor DobrychtopNo ratings yet

- Dual P-Channel Nexfet™ Power Mosfet: FeaturesDocument9 pagesDual P-Channel Nexfet™ Power Mosfet: Featurescipri_73No ratings yet

- U9024NDocument10 pagesU9024Nitm12No ratings yet

- 5305SDocument10 pages5305SHugo Camacho RamirezNo ratings yet

- Si4835DDY: Vishay SiliconixDocument10 pagesSi4835DDY: Vishay SiliconixRoberto Celedón AguileraNo ratings yet

- Datasheet 2SK3797 Mosfet Fuente Proyector Viewsonic PJD5123Document6 pagesDatasheet 2SK3797 Mosfet Fuente Proyector Viewsonic PJD5123Rubén Nicanor Sandoval BascuñanNo ratings yet

- IRF9540NDocument8 pagesIRF9540Nhardik_patel182000No ratings yet

- Irf 540 NsDocument11 pagesIrf 540 NsLucas PascualNo ratings yet

- Irfz 24 NDocument9 pagesIrfz 24 Njmbernal7487886No ratings yet

- Qfet Qfet Qfet Qfet: FQP90N08Document8 pagesQfet Qfet Qfet Qfet: FQP90N08Hãy Cố LênNo ratings yet

- Irfi 3205 Power MosfetDocument9 pagesIrfi 3205 Power MosfetAndy WilsonNo ratings yet

- Irfp 140 NDocument9 pagesIrfp 140 NCodinasound CaNo ratings yet

- TLC 5925Document27 pagesTLC 5925zektorNo ratings yet

- IRL540NDocument8 pagesIRL540Nmestek123No ratings yet

- Obsolete Product(s) - Obsolete Product(s)Document10 pagesObsolete Product(s) - Obsolete Product(s)patopickNo ratings yet

- SFR/U9120: Advanced Power MOSFETDocument7 pagesSFR/U9120: Advanced Power MOSFETJavier BendekNo ratings yet

- Coolmos Power Transistor: Features Product SummaryDocument10 pagesCoolmos Power Transistor: Features Product SummaryJosé Miguel Barbosa HernándezNo ratings yet

- TK12A50DDocument6 pagesTK12A50DRaskipusNo ratings yet

- Bias Power Supply For TV and Monitor TFT LCD Panels: FeaturesDocument30 pagesBias Power Supply For TV and Monitor TFT LCD Panels: Featureseduinggv1829No ratings yet

- Irfz 34 NLDocument10 pagesIrfz 34 NLguerrero_27No ratings yet

- Switching Regulator Applications: Absolute Maximum RatingsDocument6 pagesSwitching Regulator Applications: Absolute Maximum RatingsSyed Azhar HussainNo ratings yet

- Datasheet Irlr2905Document10 pagesDatasheet Irlr2905Alberto BritosNo ratings yet

- Mosfet 10NM60NDocument19 pagesMosfet 10NM60NRicardo Misael Torres0% (1)

- Irf7314 Dual P MosfetDocument7 pagesIrf7314 Dual P Mosfetviper22aNo ratings yet

- Low-Noise Fast-Transient-Response 1.5-A Low-Dropout Voltage RegulatorsDocument28 pagesLow-Noise Fast-Transient-Response 1.5-A Low-Dropout Voltage RegulatorssinnlosNo ratings yet

- Irfr 5305Document11 pagesIrfr 5305LucaDirafNo ratings yet

- Upa 1741 (Montel)Document7 pagesUpa 1741 (Montel)Hakemann Hakemann HakemannNo ratings yet

- P-Channel Logic Level Enhancement MOSFETDocument5 pagesP-Channel Logic Level Enhancement MOSFETsilasmateusNo ratings yet

- Apm 4546Document13 pagesApm 4546Walter FabianNo ratings yet

- 15n03gh PDFDocument6 pages15n03gh PDFdragon-red0816No ratings yet

- FQP13N50C / FQPF13N50C: N-Channel QFET MosfetDocument10 pagesFQP13N50C / FQPF13N50C: N-Channel QFET MosfetFidel ArroyoNo ratings yet

- Switching Regulator Applications, DC-DC Converter and Motor Drive ApplicationsDocument6 pagesSwitching Regulator Applications, DC-DC Converter and Motor Drive ApplicationsharanahalliNo ratings yet

- Complete DDR2, DDR3, DDR3L, and LPDDR3 Memory Power Solution Synchronous Buck Controller, 2-A LDO, With Buffered ReferenceDocument30 pagesComplete DDR2, DDR3, DDR3L, and LPDDR3 Memory Power Solution Synchronous Buck Controller, 2-A LDO, With Buffered Referencesalahudeen03No ratings yet

- Datasheet IRFB11N50ADocument8 pagesDatasheet IRFB11N50AMartín SayagoNo ratings yet

- 2SK3667Q DatasheetzDocument6 pages2SK3667Q DatasheetzИегҵ ГемасснеNo ratings yet

- Data SheetDocument35 pagesData SheetvvvssssvvvNo ratings yet

- STP6NA80 Stp6Na80Fi: N - Channel Enhancement Mode Fast Power Mos TransistorDocument11 pagesSTP6NA80 Stp6Na80Fi: N - Channel Enhancement Mode Fast Power Mos Transistorz01loNo ratings yet

- Advanced Power Electronics Corp.: AP15N03H/JDocument6 pagesAdvanced Power Electronics Corp.: AP15N03H/JShezan ShaniNo ratings yet

- Ap09n70p A MosfetDocument9 pagesAp09n70p A MosfetRomar BulaonNo ratings yet

- Tps 54628Document22 pagesTps 54628fet_50No ratings yet

- P6NA60FIDocument11 pagesP6NA60FIvigalNo ratings yet

- Irl 530 NDocument9 pagesIrl 530 NEric Lenin Marin MoncadaNo ratings yet

- K 3918Document8 pagesK 3918Anderson DuarteNo ratings yet

- General Description Product Summary: 30V Dual P-Channel MOSFETDocument5 pagesGeneral Description Product Summary: 30V Dual P-Channel MOSFETshibilvNo ratings yet

- Irfbc30As/L: Smps MosfetDocument10 pagesIrfbc30As/L: Smps MosfetAlexandru Daniel BuleuNo ratings yet

- Smps Mosfet: ApplicationsDocument9 pagesSmps Mosfet: ApplicationsMiloud ChouguiNo ratings yet

- 13 NM 60 NDocument21 pages13 NM 60 Nmarquitos550bNo ratings yet

- FQP5N60C / FQPF5N60C: N-Channel QFET MosfetDocument10 pagesFQP5N60C / FQPF5N60C: N-Channel QFET Mosfethfog2000181No ratings yet

- Irf 9 Z 24 NDocument9 pagesIrf 9 Z 24 NGiovanni Carrillo VillegasNo ratings yet

- Obsolete Product(s) - Obsolete Product(s) : STD70N02L STD70N02L-1Document17 pagesObsolete Product(s) - Obsolete Product(s) : STD70N02L STD70N02L-1Venkatesh SubramanyaNo ratings yet

- Lifetec LCD Monitor TransistorDocument9 pagesLifetec LCD Monitor TransistornegrusrlNo ratings yet

- Coolmos Power Transistor: Please Note The New Package Dimensions Arccording To PCN 2009-134-ADocument11 pagesCoolmos Power Transistor: Please Note The New Package Dimensions Arccording To PCN 2009-134-AHùng NguyenNo ratings yet

- Advanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching P-Channel Fully Avalanche RatedDocument9 pagesAdvanced Process Technology Dynamic DV/DT Rating 175°C Operating Temperature Fast Switching P-Channel Fully Avalanche RatedPedro Cu AguirreNo ratings yet

- IRF7329Document9 pagesIRF7329Михаил СеменовNo ratings yet

- MF10-N Universal Monolithic Dual Switched Capacitor Filter: Features DescriptionDocument35 pagesMF10-N Universal Monolithic Dual Switched Capacitor Filter: Features DescriptionAlbeiro Yr TrancerNo ratings yet

- Irfp 064 VDocument9 pagesIrfp 064 VPerrote PerroNo ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsNo ratings yet

- Power Factor CorrectionDocument43 pagesPower Factor Correctionravirnjn88No ratings yet

- DC-DC Converter Fundamentals and DesignDocument42 pagesDC-DC Converter Fundamentals and DesignSupriya Rakshit0% (1)

- Simulating Buck and Boost Converters in PSPICEDocument9 pagesSimulating Buck and Boost Converters in PSPICEmohanrajgupta19100% (1)

- Data Ir2153Document6 pagesData Ir2153mdkadryNo ratings yet

- Cascade Controller For DCDC Buck ConvertorDocument6 pagesCascade Controller For DCDC Buck ConvertorCristóbal Eduardo Carreño MosqueiraNo ratings yet

- Rys 8833Document12 pagesRys 8833Kherbiche YounesNo ratings yet

- Midterm Exam - SolutionDocument6 pagesMidterm Exam - SolutionSerge Mandhev SwamotzNo ratings yet

- Tutorial CascadeDocument44 pagesTutorial CascadeLeonardo Rojas HNo ratings yet

- Single Synchronous Buck PWM DC-DC ControllerDocument16 pagesSingle Synchronous Buck PWM DC-DC Controllerbachet56No ratings yet

- Inclusion of Switching Loss in The Averaged Equivalent Circuit ModelDocument18 pagesInclusion of Switching Loss in The Averaged Equivalent Circuit ModelUlisesNo ratings yet

- LC 043Document52 pagesLC 043chanxi9No ratings yet

- Optimizing With eGaN FETsDocument6 pagesOptimizing With eGaN FETskhsniperNo ratings yet

- LM 2576Document37 pagesLM 2576Ssj KakarottNo ratings yet

- Application of Hysteretic Current-Mode Control Technology For Electrostatic PrecipitatorDocument5 pagesApplication of Hysteretic Current-Mode Control Technology For Electrostatic PrecipitatorsharathNo ratings yet

- Spreadsheet for MC33063 step-up converter designDocument9 pagesSpreadsheet for MC33063 step-up converter designAlonso CoradoNo ratings yet

- Power Converter II Lab Waveforms and ExperimentsDocument53 pagesPower Converter II Lab Waveforms and ExperimentsK Kiran VishnuNo ratings yet

- SDQSFDocument103 pagesSDQSFHuy Khôi HàNo ratings yet

- LM2575 D PDFDocument28 pagesLM2575 D PDFadfumegaNo ratings yet

- CAP.4. Conv. DC-DC Cu IzolareDocument9 pagesCAP.4. Conv. DC-DC Cu IzolareCondracheClaudiaNo ratings yet

- DRV832x 6 To 60-V Three-Phase Smart Gate Driver: 1 Features 3 DescriptionDocument92 pagesDRV832x 6 To 60-V Three-Phase Smart Gate Driver: 1 Features 3 DescriptionĐặng Minh ĐứcNo ratings yet

- Understanding Modern Power MOSFETsDocument36 pagesUnderstanding Modern Power MOSFETsZhao XuNo ratings yet

- DC-DC Converter Design and OperationDocument59 pagesDC-DC Converter Design and OperationHarshal SpNo ratings yet

- Project Report On "Efficient Solar Charging With Battery Protection"Document40 pagesProject Report On "Efficient Solar Charging With Battery Protection"PRAKASH CHOUDHARYNo ratings yet

- Tps 65171Document46 pagesTps 65171deo57ar100% (2)

- AOZ1021AIDocument15 pagesAOZ1021AIJohnny La Mesa100% (1)

- Discrete Time Control of A Push-Pull Power Converter - JBO - TFMDocument114 pagesDiscrete Time Control of A Push-Pull Power Converter - JBO - TFMprajwalNo ratings yet

- FUJI Power Supply Control IC: Application NoteDocument21 pagesFUJI Power Supply Control IC: Application NoteЕрбол ЖакуповNo ratings yet

- AC DC ConverterDocument21 pagesAC DC ConverterHải Nguyễn CôngNo ratings yet

- Controlling Switch Node Ringing in DC DC ConvertersDocument14 pagesControlling Switch Node Ringing in DC DC ConvertersMohammad Hefdi UnoNo ratings yet