Professional Documents

Culture Documents

MPMC Memory

Uploaded by

swaroop1122Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

MPMC Memory

Uploaded by

swaroop1122Copyright:

Available Formats

MPMC

1

1. Access time is faster for

(A)ROM

(B) SRAM

( C) DRAM

(D)EPROM

Ans-B

2. In 8255 , under the I/O mode of operation we have how many modes ?

(A) 3

(B)2

(C) 4

(D)1

Ans-B

3. Under which mode of 8255 , it will have following features ?

1) a 5 bit control port is available

2) 3 I/O lines are available at port C.

(A) mode 2

(B) mode 0

(C)mode1

(D) mode 3

Ans-A

4. For the most static RAM the write pulse width should be at least

(A) 10 ns

(B) 60 ns

(C) 300ns

(D) 80 ns

Ans-B

5. BURST refresh in DRAM is also called as

(A)connected refresh

(B)distributed refresh

(C)hidden refresh

(D)none

Ans-A

6. For most static RAM the maximum access time is about

(A)1ns

(B)10ns

(C)0100ns

(D)1000ns

Ans-C

MPMC

2

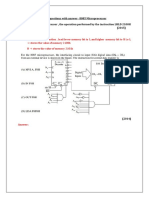

7. After an arithmetic operation, the flag register of 8085 _P has the following contents

The contents of accumulator after operation may be

A) 75 (B) 6C C) DB (D) B6

8. In an 8085 microprocessor, the instruction CMP Bhas been executedwhile the contents of

accumulator is less than that of register B. As a result carry flag andzero flag will be

respectively

(A) set, reset (B) reset, set C) reset, reset (D) set, set

9. Consider the following 8085 instruction

MVI A, A9H

MVI B, 57H

ADD B

ORA A

The flag status (S, Z, CY) after the instruction

ORA A is executed, is

(A) (0, 1, 1) (B) (0, 1, 0) (C) (1, 0, 0) (D) (1, 0, 1)

10. Consider the following set of 8085 instructions

MVI A, 8EH

ADI 73H

J C DSPLY

OUT PORT1

HLT

DSPLY : XRA A

OUT PORT1

HLT

The output at PORT1 is

(A) 00 (B) FEH C) 01H (D) 11H

11. Consider the following 8085 assembly program

MVI A, DATA1

MOV B, A

SUI 51H

J C DLT

MOV A, B

SUI 82H

J C DSPLY

DLT : XRA A

OUT PORT1

HLT

DSPLY : MOV A, B

OUT PORT2

HLT

MPMC

3

This program will display

(A) the bytes from 51H to 82H at PORT2

(B) 00H AT PORT1

(C) all byte at PORT1

(D) the bytes from 52H to 81H at PORT 2

12. It is desired to mask is the high order bits(D D) 7 4 _ of

the data bytes in register C. Consider the following set

of instruction

(a) MOV A, C

ANI F0H

MOV C, A

HLT

(b) MOV A, C

MVI B, F0H

ANA B

MOV C, A

HLT

(c) MOV A, C

MVI B, 0FH

ANA B

MOV C, A

HLT

(d) MOV A, C

ANI 0FH

MOV C, A

HLT

The instruction set, which execute the desired

operation are

(A) a and b (B) c and d

(C) only a (D) only d

13. Consider the following 8085 assembly program :

MVI B, 89H

MOV A, B

MOV C, A

MVI D, 37H

OUT PORT1

HLT

The output at PORT1 is

(A) 89 (B) 37

(C) 00 (D) None of the above

MPMC

4

14. Consider the sequence of 8085 instruction given

below

LXI H, 9258H

MOV A, M

CMA

MOV M, A

By this sequence of instruction the contents of

memory location

(A) 9258H are moved to the accumulator

(B) 9258H are compared with the contents of the accumulator

(C) 8529H are complemented and stored at location

529H

(D) 5829H are complemented and stored at location

85892H

15. Consider the sequence of 8085 instruction

MVI A, 5EH

ADI A2H

MOV C, A

HLT

The initial contents of resistor and flag are as

follows

A C S Z CY

__ __ 0 0 0

After execution of the instructions the contents of

register and flags are

A C S Z CY

(A) 10H 10H 0 0 1

(B) 10H 10H 1 0 0

(C) 00H 00H 1 1 0

(D) 00H 00H 0 1 1

16. It is desired to multiply the number 0AH by 0BH

and store the result in the accumulator. The numbers

are available in register B and C respectively. A part of

the 8085 program for this purpose is given below :

MVI A, 00H

LOOP : ---------------

---------------

---------------

---------------

---------------

HLT

END

The sequence of instruction to complete the

program would be

(A) J NZ LOOP

ADD B

DCR C

MPMC

5

(B) ADD B

J NZ LOOP

DCR C

(C) DCR C

J NZ LOOP

ADD B

(D) ADD B

DCR C

J NZ LOOP

17. Consider the following assembly language program:

MVI B, 87H

MOV A, B

START : J MP NEXT

MVI B, 00H

XRA B

OUT PORT1

HLT

NEXT : XRA B

J P START1

OUT PORT2

HLT

The execution of the above program in an 8085

will result in

(A) an output of 87H at PORT1

(B) an output of 87H at PORT2

(C) infinite looping of the program execution with

accumulator data remaining at 00H

(D) infinite looping of the program execution with

accumulator data alternating between 00H and 87H.

18. Consider the following 8085 program

MVI A, DATA1

ORA A,

J M DSPLY

OUT PORT1

CMA

DSPLY : ADI 01H

OUT PORT1

HLT

If DATA1 =A7H, the output at PORT1 is

(A) 47H (B) 58H

(C) 00 (D) None of the above

Statement for Q.1920:

Consider the following program of 8085 assembly

MPMC

6

language:

LXI H 4A02H

LDA 4A00H

MOV B, A

LDA 4A01H

CMP B

J Z FNSH

J C GRT

MOV M, A

J MP FNSH

MOV M, B

FNSH : HLT

19. If the contents of memory location 4A00H, 4A01H

and 4A02H, are respectively A7H, 98H and 47H, then

after the execution of program contents of memory

location 4A02H will be respectively

(A) A7H (B) 98H

(C) 47H (D) None of the above

Ans-A

20. The memory requirement for this program is

(A) 20 Byte (B) 21 Byte

(C) 23 Byte (D) 18 Byte

Ans-C

21. The instruction, that does not clear the accumulator

of 8085, is

(A) XRA A (B) ANI 00H

(C) MVI A, 00H (D) None of the above

Ans-D

22. The contents of some memory location of an 8085 _P

based system are shown

Address Hex. Contents (Hex.)

3000 02

3001 30

3002 00

3003 30

Fig. P4.6.17

The program is as follows

LHLD 3000H

MOV E, M

INX H

MOV D, M

LDAX D

MOV L, A

MPMC

7

INX D

LDAX D

MOV H, A

The contents if HL pair after the execution of the

program will be

(A) 0030 H (B) 3000 H

(C) 3002 H(D) 0230H

Ans-C

23. Consider the following loop

XRA A

LXI B, 0007H

LOOP : DCX B

J NZ LOOP

This loop will be executed

(A) 1 times (B) 8 times

(C) 7 times (D) infinite times

Ans-A

24. Consider the following loop

LXI H, 000AH

LOOP : DCX B

MOV A, B

ORA C

J NZLOOP

This loop will be executed

(A) 1 time (B) 10 times

(C) 11 times (D) infinite times

Ans-B

25. The contents of accumulator after the execution of

following instruction will be

MVI A, A7H

ORA A

RLC

(A) CFH (B) 4FH

(C) 4EH (D) CEH

Ans-B

26. The contents of accumulator after the execution of

following instructions will be

MVI A, B7H

ORA A

RAL

(A) 6EH (B) 6FH

(C) EEH (D) EFH

Ans-A

MPMC

8

27. The contents of the accumulator after the execution

of the following program will be

MVI A, C5H

ORA A

RAL

(A) 45H (B) C5H

(C) C4H (D) None of the above

Ans-A

28. Consider the following set of instruction

MVI A, BYTE1

RLC

MOV B, A

RLC

RLC

ADD B

If BYTE1 =07H, then content of A, after the

execution of program will be

(A) 46H (B) 70H

(C) 38H (D) 68H

Ans-A

29. Consider the following program

MVI A, BYTE1

RRC

RRC

If BYTE1 _ 32H, the contents of A after the

execution of program will be

(A) 08H (B) 8CH

(C) 12H (D) None of the above

Ans-B

30. Consider the following program

MVI A, DATA

MVI B, 64H

MVI C, C8H

CMP B

J C RJ CT

CMP C

J NC RJ CT

OUT PORT1

HLT

RJ CT : SUB A

OUT PORT1

HLT

If the following sequence of byte is loaded in

MPMC

9

accumulator,

then sequence of output will be

(A) 00, 00, 73, B4, 00, FA

(B) 58, 64, 00, 00, C8, FA

(C) 58, 00, 00, 00, C8, FA

(D) 00, 64, 73, B4, 00, FA

Ans-D

31. Consider the following instruction to be executed by

a 8085 _p. The input port has an address of 01H and

has a data 05H to input:

IN 01H

ANI 80H

After execution of the two instruction the contents

of flag register are

Ans-C

32.What is SIM?

(A) sorting interrupt mask

(B)select interrupt mask

(C)set interrupt mask

(D)software interrupt mask

Ans-B

33. What are software interrupt ?

(A)RST 0-7 (B) RST 5.5-RST 7.5 (C) INTR (D) TRAP

Ans-A

34 . Why 8085 is a 8 bit processor ?

(A) because 8085 has 8 bit ALU .

(B) because 8085 has 8 bit data bus.

(C) because 8085 has 8 bit FLAGS ..

(D) both (A) and (B).

Ans B

MPMC

10

35. RIM is used to check whether

(A) The write operation is done or not .

(B) The interrupt is masked or not .

(c) The read operation is done or not .

(D) both (A) and (C).

Ans- B

36. In 8085 address for TRAP is

(A) 0023 (B) 0024 (C)0033 (D)0034

Ans - B

37.What does microprocessor speed depends on ?

(A) clock

(B)data bus width

(C)address bus width

(D) size of register

Ans - B

38.Which microprocessor structure is pipelined ?

(A) All X80 processor

(B) All X85processor

(C) All X86processor

(D) Pentium

Ans-C

39.Which stack is used in 8085 ?

(A) FIFO (B) LIFO (C) FILO (D) LILO

Ans-B

40.Address line for RST-3 is

(A)0020 (B)0028 (C)0018 (D)0038

Ans- C.

You might also like

- BC0046 Microprocessor MQPDocument20 pagesBC0046 Microprocessor MQPMeet PandyaNo ratings yet

- IES - Electrical Engineering - MicroprocessorDocument31 pagesIES - Electrical Engineering - Microprocessors_subbulakshmiNo ratings yet

- a094mMPMC Multiple Choice QuestionsDocument7 pagesa094mMPMC Multiple Choice QuestionsVenkata SureshNo ratings yet

- 8085 microprocessor program execution and register contentsDocument3 pages8085 microprocessor program execution and register contentsvarun89goelNo ratings yet

- Mi CropDocument3 pagesMi CropAbhishek KarwaNo ratings yet

- MPI Compre PartA 2019 SolDocument2 pagesMPI Compre PartA 2019 SolVishweshRaviShrimaliNo ratings yet

- Microprocessors & Interfacing - CS 402Document9 pagesMicroprocessors & Interfacing - CS 402Subhodh PapannaNo ratings yet

- 346Document60 pages346Anjan SenguptaNo ratings yet

- 8085 Lab AssignmentDocument4 pages8085 Lab AssignmentShaswata Dutta50% (2)

- Digital and MPMC QuizDocument17 pagesDigital and MPMC QuiznjparNo ratings yet

- 8085 Multiple Choice QuestionsDocument22 pages8085 Multiple Choice QuestionsMaari SenjiduveNo ratings yet

- UNIT V Microcontroller I - MCQsDocument10 pagesUNIT V Microcontroller I - MCQsPadmaja Venkataraman100% (2)

- Microprocessor Assignment (Assignment-2)Document7 pagesMicroprocessor Assignment (Assignment-2)Ajay SahuNo ratings yet

- First QuesDocument3 pagesFirst QuesArun KumarNo ratings yet

- CaoDocument13 pagesCaoragavendharNo ratings yet

- 8051 MCQDocument6 pages8051 MCQSamruddhi JadhavNo ratings yet

- ICO, Quiz # 2Document1 pageICO, Quiz # 2Sujata RoyNo ratings yet

- GateDocument8 pagesGateGopinathManoharanNo ratings yet

- 10292020214439ECET Computer Science - 2020Document13 pages10292020214439ECET Computer Science - 2020M.hanmandluNo ratings yet

- Tutorial 3 2022 StudentsDocument5 pagesTutorial 3 2022 StudentsIndongo EliaserNo ratings yet

- 1000+ MCQ On Microprocessor & MicrocontrollerDocument113 pages1000+ MCQ On Microprocessor & MicrocontrollerSyed Wajid87% (15)

- Aptitude and Technical Interview Preparation GuideDocument12 pagesAptitude and Technical Interview Preparation GuidePrasad NagaNo ratings yet

- Module 05 MpiDocument14 pagesModule 05 MpiAditi VermaNo ratings yet

- Microcontrollers Multiple Choice QuestionsDocument11 pagesMicrocontrollers Multiple Choice QuestionsDeepak SharmaNo ratings yet

- Computer Architecture Objective Type Questions and AnswersDocument129 pagesComputer Architecture Objective Type Questions and AnswersRajesh TiwaryNo ratings yet

- Ca Q&aDocument129 pagesCa Q&aRavi TejaNo ratings yet

- Computer Architecture-OBJECTIVE TYPE 75 QUESTIONS-GateDocument8 pagesComputer Architecture-OBJECTIVE TYPE 75 QUESTIONS-GatepranavbommiNo ratings yet

- Homework2b1803Document2 pagesHomework2b1803Rahul YadavNo ratings yet

- Digital QuizDocument17 pagesDigital QuizSri MathiNo ratings yet

- Shivaji University KolhapurDocument8 pagesShivaji University KolhapurPallavi PatilNo ratings yet

- Toshiba Placement PaperDocument12 pagesToshiba Placement PaperpanakkaltinoNo ratings yet

- Computer Architecture MCQ TitleDocument8 pagesComputer Architecture MCQ TitleVishal ThakurNo ratings yet

- 8085 Microprocessor Unit NotesDocument20 pages8085 Microprocessor Unit NotesdeptNo ratings yet

- Computer Architecture MCQ-4Document6 pagesComputer Architecture MCQ-4Kuldeep KushwahaNo ratings yet

- OltDocument15 pagesOltSadish KumarNo ratings yet

- Microprocessor Question BankDocument67 pagesMicroprocessor Question BankArpit SNo ratings yet

- Microprocessor MCQsDocument67 pagesMicroprocessor MCQsHarsimran100% (1)

- Microprocessor 49 Important MCQDocument8 pagesMicroprocessor 49 Important MCQAawez AkhterNo ratings yet

- HT TP: //qpa Pe R.W But .Ac .In: 2012 Microprocessor & MicrocontrollerDocument7 pagesHT TP: //qpa Pe R.W But .Ac .In: 2012 Microprocessor & MicrocontrollerAbhishek DasNo ratings yet

- Microprocessor Multiple Choice QuesDocument6 pagesMicroprocessor Multiple Choice Quesrraje82100% (9)

- Mppapersp 101009073701 Phpapp02Document2 pagesMppapersp 101009073701 Phpapp02Jamie SchultzNo ratings yet

- 1000+ Microprocessor 8085,8086 MCQDocument164 pages1000+ Microprocessor 8085,8086 MCQSurajAnand48% (29)

- Microprocessor: (1 Mark Each)Document14 pagesMicroprocessor: (1 Mark Each)SeekEducationNo ratings yet

- Amazon Online Assessment 2021 QuestionsDocument12 pagesAmazon Online Assessment 2021 QuestionsCoder Coder0% (2)

- MicroprocessDocument8 pagesMicroprocesschadobrienNo ratings yet

- Microprocessor (KCS-403) Question BankDocument29 pagesMicroprocessor (KCS-403) Question BankCubic SectionNo ratings yet

- CSC 9Document10 pagesCSC 99989219809No ratings yet

- Aeie 3105Document2 pagesAeie 3105Sanjay DuttaNo ratings yet

- CSE211 MCQ S TXT 426394401 CSE211 MCQ SDocument18 pagesCSE211 MCQ S TXT 426394401 CSE211 MCQ SD StudiosNo ratings yet

- The Acronym PLC Stands For:: Unit 4 MCQDocument4 pagesThe Acronym PLC Stands For:: Unit 4 MCQpradnya sadigaleNo ratings yet

- Digital Signal Processing Using the ARM Cortex M4From EverandDigital Signal Processing Using the ARM Cortex M4Rating: 1 out of 5 stars1/5 (1)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- Digital Signal Processing: Instant AccessFrom EverandDigital Signal Processing: Instant AccessRating: 3.5 out of 5 stars3.5/5 (2)

- Boolean Circuit Rewiring: Bridging Logical and Physical DesignsFrom EverandBoolean Circuit Rewiring: Bridging Logical and Physical DesignsNo ratings yet

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemFrom EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNo ratings yet

- Archived Chat About College Exams and ProjectsDocument15 pagesArchived Chat About College Exams and Projectsswaroop1122No ratings yet

- Signals & SystemsDocument1 pageSignals & Systemsswaroop1122No ratings yet

- Form ADocument2 pagesForm Aswaroop1122No ratings yet

- TauntsDocument2 pagesTauntsMrxyuz TrinkleNo ratings yet

- RINL MT 2013 Advertisement PDFDocument6 pagesRINL MT 2013 Advertisement PDFRanjith KaruturiNo ratings yet

- MasksDocument6 pagesMasksHend ElsNo ratings yet

- InterfaceDocument2 pagesInterfaceswaroop1122No ratings yet

- Bank Challan For Application FeeDocument1 pageBank Challan For Application FeeKumar GorlaNo ratings yet

- Form ADocument2 pagesForm Aswaroop1122No ratings yet

- Read Me 1Document10 pagesRead Me 1pmk888No ratings yet

- Ot - HR: Sr. No Application NoDocument3 pagesOt - HR: Sr. No Application Noswaroop1122No ratings yet

- B HGV Id Card ConfigDocument13 pagesB HGV Id Card Configswaroop1122No ratings yet

- Vacancy Notice FinalDocument22 pagesVacancy Notice FinalKushal Dube CorleoneNo ratings yet

- xl2html FilesizesDocument19 pagesxl2html Filesizesswaroop1122No ratings yet

- Code Simple Non WebDocument4 pagesCode Simple Non Webswaroop1122No ratings yet

- Railtel PaymentDocument1 pageRailtel Paymentswaroop1122No ratings yet

- Notification For Selection of Project FellowDocument1 pageNotification For Selection of Project Fellowswaroop1122No ratings yet

- BikesDocument1 pageBikesswaroop1122No ratings yet

- Log Dlful2G1Document8 pagesLog Dlful2G1swaroop1122No ratings yet

- Log PingLT602GDocument4 pagesLog PingLT602Gswaroop1122No ratings yet

- Lastest CodeDocument4 pagesLastest Codeswaroop1122No ratings yet

- What Is TBFDocument10 pagesWhat Is TBFmcmkapilNo ratings yet

- Log Dlful2GDocument11 pagesLog Dlful2Gswaroop1122No ratings yet

- Interview Question & Answers Subject: Data StructureDocument6 pagesInterview Question & Answers Subject: Data Structureswaroop1122No ratings yet

- Annoucement CCMT 2013Document1 pageAnnoucement CCMT 2013swaroop1122No ratings yet

- Traffic Analysis and Optimization of GSM NetworksDocument4 pagesTraffic Analysis and Optimization of GSM NetworksWale OgunniranNo ratings yet

- ECEMicrowave EngineeringDocument14 pagesECEMicrowave EngineeringJoshua DuffyNo ratings yet

- State Bank of IndiaDocument1 pageState Bank of Indiaswaroop1122No ratings yet

- Azure Virtual Desktop On ThinPro OSDocument3 pagesAzure Virtual Desktop On ThinPro OSMihir LakdawalaNo ratings yet

- Seisspace®/Promax®/ Promax® Depthcharge: Release NotesDocument71 pagesSeisspace®/Promax®/ Promax® Depthcharge: Release NoteschenxqNo ratings yet

- CL03 - Studio 5000 Logix Designer Basics Lab ROKTechED 2016Document14 pagesCL03 - Studio 5000 Logix Designer Basics Lab ROKTechED 2016Antony ChumpitazNo ratings yet

- Java I/O Streams and File HandlingDocument69 pagesJava I/O Streams and File HandlingsupriyaNo ratings yet

- Temp Based Fan Speed Control ProjectDocument62 pagesTemp Based Fan Speed Control ProjectKushal Malhotra100% (1)

- ROUTE66Document8 pagesROUTE66Prior LainNo ratings yet

- Oracle Adapter R3 Implementation GuideDocument80 pagesOracle Adapter R3 Implementation GuideFJAutosysuserNo ratings yet

- W54xEL ESMDocument98 pagesW54xEL ESMCarlos ZarateNo ratings yet

- Medal Log 20230522Document59 pagesMedal Log 20230522lagosta hackerNo ratings yet

- Spmp3050 Userguide-Frm ProDocument19 pagesSpmp3050 Userguide-Frm ProAnonymous KPhTy0CE100% (1)

- DudeDocument3 pagesDudesyngates13No ratings yet

- CS Summer Work - 2023Document43 pagesCS Summer Work - 2023priyak131982No ratings yet

- Learners Activity Sheet 3Document10 pagesLearners Activity Sheet 3John Raymund MabansayNo ratings yet

- 8251 - Usart Serial Communication InterfaceDocument17 pages8251 - Usart Serial Communication InterfaceVignesh GuruNo ratings yet

- DEX450 BuildApplicationsProgrammatically ExercisesDocument91 pagesDEX450 BuildApplicationsProgrammatically ExercisesDavid rodrigNo ratings yet

- Tutorial Arduino Bluetooth 8 Lamp PDFDocument12 pagesTutorial Arduino Bluetooth 8 Lamp PDFZulkarnain ZainalNo ratings yet

- TIA Portal S7 1200 1500 Programming Guideline PDFDocument69 pagesTIA Portal S7 1200 1500 Programming Guideline PDFSidonio GuerreiroNo ratings yet

- LP3944Document14 pagesLP3944alephzeroNo ratings yet

- Upgrade Config - PyDocument5 pagesUpgrade Config - PyLeonte StefanNo ratings yet

- Cloud Computing AssignmentDocument4 pagesCloud Computing AssignmentSahil SarwarNo ratings yet

- Timeline of History of ComputerDocument10 pagesTimeline of History of ComputerNuivarez JethroNo ratings yet

- Debug 1214Document17 pagesDebug 1214Lorin VacarasuNo ratings yet

- Service Letter: SL-277 (Rev. A) August 21, 2013 Trilogy Configuration Tool EffectivityDocument1 pageService Letter: SL-277 (Rev. A) August 21, 2013 Trilogy Configuration Tool EffectivityOsvaldo MartinezNo ratings yet

- RUX Uptake Tool Instructions RevisedDocument10 pagesRUX Uptake Tool Instructions RevisedshraynarulaNo ratings yet

- Uttam ResumeDocument4 pagesUttam ResumeGaneshSinghNo ratings yet

- BCN DSC02Document2 pagesBCN DSC02selvamNo ratings yet

- Ltrarc 3500Document91 pagesLtrarc 3500Daniel VieceliNo ratings yet

- Python Object Oriented Programming NewDocument33 pagesPython Object Oriented Programming NewPriyaGandhi100% (3)

- Programming Mac Os X - A Guide For Unix DevelopersDocument385 pagesProgramming Mac Os X - A Guide For Unix DevelopersHenke DaniilNo ratings yet

- TRKX 64D82AR Datasheet CDocument11 pagesTRKX 64D82AR Datasheet CachillemarioNo ratings yet