Professional Documents

Culture Documents

Lecture 350 - Parallel Dacs, Improved Dac Resolution and Serial Dacs

Uploaded by

rkatreepOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lecture 350 - Parallel Dacs, Improved Dac Resolution and Serial Dacs

Uploaded by

rkatreepCopyright:

Available Formats

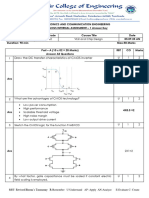

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-1

CMOS Analog Circuit Design P.E. Allen - 2010

LECTURE 350 PARALLEL DACS, IMPROVED DAC

RESOLUTION AND SERIAL DACS

LECTURE ORGANIZATION

Outline

Voltage scaling DACs

Charge scaling DACs

Extending the resolution of parallel DACs

Serial DACs

Summary

CMOS Analog Circuit Design, 2

nd

Edition Reference

Pages 626-652

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-2

CMOS Analog Circuit Design P.E. Allen - 2010

VOLTAGE SCALING DIGITAL-ANALOG CONVERTERS

General Voltage Scaling Digital Analog Converter

v

OUT

Voltage

Scaling

Network

Digital Input Word

V

REF

Decoder

Logic

V

1

V

2

V

3

V

2

N

Fig. 10.2-6

Operation:

Creates all possible values of the analog output then uses a decoding network to

determine which voltage to select based on the digital input word.

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-3

CMOS Analog Circuit Design P.E. Allen - 2010

3-Bit Voltage Scaling Digital-Analog Converter

The voltage at any tap can be expressed as: v

OUT

=

V

REF

8

(n 0.5) =

V

REF

16

(2n 1)

Attributes:

Guaranteed

monotonic

Compatible with

CMOS

technology

Large area if N is

large

Sensitive to

parasitics

Requires a buffer

Large current can

flow through the

resistor string.

b

2

b

1

b

0

b

2

b

1

b

0

V

REF

R/2

R/2

8

7

6

5

4

3

2

1

R

R

R

R

R

R

R

v

OUT

000 001 010 011 100 101 110 111

V

REF

8

2V

REF

8

3V

REF

8

4V

REF

8

5V

REF

8

6V

REF

8

7V

REF

8

V

REF

0

Digital Input Code

v

O

U

T

(a.) (b.)

Figure 10.2-7 - (a.) Implementation of a 3-bit voltage scaling DAC. (b.) Input-output

characteristics of Fig. 10.2-7(a.)

11

16

V

REF

Input = 101

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-4

CMOS Analog Circuit Design P.E. Allen - 2010

Alternate Realization of the 3-Bit Voltage Scaling DAC

b

2

b

1

b

0

V

REF

R/2

R/2

8

7

6

5

4

3

2

1

R

R

R

R

R

R

R

v

OUT

3-to-8 Decoder

Fig. 10.2-8

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-5

CMOS Analog Circuit Design P.E. Allen - 2010

INL and DNL of the Voltage Scaling DAC

Find an expression for the INL and DNL of the voltage scaling DAC using a worst-case

approach. For an n-bit DAC, assume there are 2

n

resistors between V

REF

and ground

and that the resistors are numbered from 1 to 2

n

beginning with the resistor connected to

V

REF

and ending with the resistor connected to ground.

Integral Nonlinearity

The voltage at the i-th resistor from the top is,

v

i

=

(2

n

-i)R

(2

n

-i)R + iR

V

REF

where there are i resistors above v

i

and 2

n

-i below.

For worst case, assume that i = 2

n-1

(midpoint).

Define R

max

= R + R and R

min

= R - R.

The worst case INL is

INL = v

2

n-1

(actual) - v

2

n-1

(ideal)

Therefore,

INL =

2

n-1

(R+R)V

REF

2

n-1

(R+R) + 2

n-1

(R-R)

-

V

REF

2

=

R

2R

V

REF

INL=

2

n

2

n

R

2R

V

REF

=2

n-1

R

R

V

REF

2

n

=2

n-1

R

R

LSBs

Differential Nonlinearity

The worst case DNL is

DNL = v

step

(act) - v

step

(ideal)

Substituting the actual and

ideal steps gives,

=

(RR)V

REF

2

n

R

-

R V

REF

2

n

R

=

RR

R

-

R

R

V

REF

2

n

=

R

R

V

REF

2

n

Therefore,

DNL =

R

R

LSBs

V

REF

R

1

R

2

R

3

R

i-1

R

i

R

i+1

R

2n

R

2n-1

1

2

3

i-2

i-1

i

i+1

2n-2

2n-1

2n

V

i

Fig. 10.2-085

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-6

CMOS Analog Circuit Design P.E. Allen - 2010

Example 350-1 - Accuracy Requirements of a Voltage-Scaling Digital-Analog

Converter

If the resistor string of a voltage scaling digital-analog converter is a 5 m wide

polysilicon strip having a relative accuracy of 1%, what is the largest number of bits that

can be resolved and keep the worst case INL within 0.5 LSB? For this number of bits

what is the worst case DNL?

Solution

From the previous page, we can write that

2

n-1

R

R

= 2

n-1

1

100

1

2

This inequality can be simplified

2

n

100

which has a solution of n = 6.

The value of the DNL for n = 6 is found from the previous page as

DNL =

1

100

LSBs = 0.01LSBs

(This is the reason the resistor string is monotonic.)

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-7

CMOS Analog Circuit Design P.E. Allen - 2010

CHARGE SCALING DIGITAL-ANALOG CONVERTERS

General Charge Scaling Digital-Analog Converter

v

OUT

Charge

Scaling

Network

Digital Input Word

V

REF

Fig. 10.2-9

General principle is to capacitively attenuate the reference

voltage. Capacitive attenuation is simply:

Calculate as if the capacitors were resistors. For example,

V

out

=

1

C

2

1

C

1

+

1

C

2

V

REF

=

C

1

C

1

+ C

2

V

REF

C

1

C

2

V

REF

+

-

V

out

Fig. 10.2-9b

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-8

CMOS Analog Circuit Design P.E. Allen - 2010

Binary-Weighted, Charge Scaling DAC

Circuit:

Operation:

1.) All switches

connected to ground

during

1

.

2.) Switch S

i

closes to V

REF

if b

i

= 1 or to ground if b

i

= 0.

Equating the charge in the capacitors gives,

V

REF

C

eq

= V

REF

b

0

C +

b

1

C

2

+

b

2

C

2

2

+ ... +

b

N-1

C

2

N1

= C

tot

v

OUT

= 2C v

OUT

which gives

v

OUT

= [b

0

2

-1

+ b

1

2

-2

+ b

2

2

-3

+ ... + b

N-1

2

-N

]V

REF

Equivalent circuit of the binary-weighted, charge

scaling DAC is:

Attributes:

Accurate

Sensitive to parasitics

Not monotonic

Charge feedthrough occurs at turn on of switches

+

-

V

REF

1

C

2 2

N-2

2

N-1

C

4

C C C

2

N-1

C

2

S

0

2

2

2

2

S

1

S

2

S

N-2

S

N-1

v

OUT

Terminating

Capacitor

Fig. 10.2-10

+

-

V

REF

Ceq.

2C - C

eq.

v

OUT

Fig. 10.2-11

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-9

CMOS Analog Circuit Design P.E. Allen - 2010

Integral Nonlinearity of the Charge Scaling DAC

Again, we use a worst case approach. Assume an n-bit charge scaling DAC with the

MSB capacitor of C and the LSB capacitor of C/2

n-1

and the capacitors have a tolerance

of C/C.

The ideal output when the i-th capacitor only is connected to V

REF

is

v

OUT

(ideal) =

C/2

i-1

2C

V

REF

=

V

REF

2

i

2

n

2

n

=

2

n

2

i

LSBs

The maximum and minimum capacitance is C

max

= C + C and C

min

= C - C.

Therefore, the actual worst case output for the i-th capacitor is

v

OUT

(actual) =

(CC)/2

i-1

2C

V

REF

=

V

REF

2

i

CV

REF

2

i

C

=

2

n

2

i

2

n

C

2

i

C

LSBs

Now, the INL for the i-th bit is given as

INL(i) = v

OUT

(actual) - v

OUT

(ideal) =

2

n

C

2

i

C

=

2

n-i

C

C

LSBs

Typically, the worst case value of i occurs for i = 1. Therefore, the worst case INL is

INL = 2

n-1

C

C

LSBs

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-10

CMOS Analog Circuit Design P.E. Allen - 2010

Differential Nonlinearity of the Charge Scaling DAC

The worst case DNL for the binary weighted capacitor array is found when the MSB

changes. The output voltage of the binary weighted capacitor array can be written as

v

OUT

=

C

eq.

(2C-C

eq.

) + C

eq.

V

REF

where C

eq

are capacitors whose bits are 1 and (2C - C

eq

) are capacitors whose bits are 0.

The worst case DNL can be expressed as

DNL =

v

step

(worst case)

v

step

(ideal)

- 1 =

v

OUT

(1000....) - v

OUT

(0111....)

LSB

- 1 LSBs

The worst case choice for the capacitors is to choose C

1

larger by C and the remaining

capacitors smaller by C giving,

C

1

=C+C, C

2

=

1

2

(C-C),...,C

n-1

=

1

2

n-2

(C-C), C

n

=

1

2

n-1

(C-C), and C

term

=

1

2

n-1

(C-C)

Note that

n

C

i

i=2

+ C

term

= C

2

+ C

3

++ C

n-1

+ C

n

+ C

term

= C-C

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-11

CMOS Analog Circuit Design P.E. Allen - 2010

Differential Nonlinearity of the Charge Scaling DAC - Continued

v

OUT

(1000...) =

C+C

(C+C)+(C-C)

V

REF

=

C+C

2C

V

REF

=

C+C

2C

V

REF

2

n

2

n

= 2

n

C+C

2C

LSBs

and

v

OUT

(0111...) =

(C-C) -C

term

(C+C)+(C-C)

V

REF

=

(C-C) -

1

2

n-1

(C-C)

(C+C)+(C-C)

V

REF

=

C-C

2C

1 -

2

2

n

V

REF

=

2

n

2

n

C-C

2C

1 -

2

2

n

V

REF

= 2

n

C-C

2C

1 -

2

2

n

LSBs

v

OUT

(1000...) - v

OUT

(0111...)

LSB

-1 LSBs = 2

n

C+C

2C

-2

n

C-C

2C

1-

2

2

n

-1 = (2

n

-1)

C

C

LSBs

Therefore, DNL = (2

n

- 1)

C

C

LSBs

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-12

CMOS Analog Circuit Design P.E. Allen - 2010

Example 350-2 - DNL and INL of a Binary Weighted Capacitor Array DAC

If the tolerance of the capacitors in an 8-bit, binary weighted, charge scaling DAC are

0.5%, find the worst case INL and DNL.

Solution

For the worst case INL, we get from above that

INL = (2

7

)(0.005) = 0.64 LSBs

For the worst case DNL, we can write that

DNL = (2

8

-1)(0.005) = 1.275 LSBs

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-13

CMOS Analog Circuit Design P.E. Allen - 2010

Example 350-3 - Influence of Capacitor Ratio Accuracy on Number of Bits

Use the data shown to estimate the number of

bits possible for a charge scaling DAC assuming a

worst case approach for INL and that the worst

conditions occur at the midscale (1 MSB).

Solution

Assuming an INL of 0.5 LSB, we can write that

INL = 2

N-1

C

C

1

2

C

C

=

1

2

N

Let us assume a unit capacitor of 50 m by 50

m and a relative accuracy of approximately

0.1%. Solving for N in the above equation gives

approximately 10 bits. However, the 0.1% figure

corresponds to ratios of 16:1 or 4 bits. In order to

get a solution, we estimate the relative accuracy of

capacitor ratios as

C

C

0.001 + 0.0001N

Using this approximate relationship, a 9-bit digital-analog converter should be

realizable.

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-14

CMOS Analog Circuit Design P.E. Allen - 2010

Binary Weighted, Charge Amplifier DAC

+

-

b

0

V

REF

2

N-1

C

F

= 2

N

C/K

+

-

v

OUT

C 2

C

1

+

-

b

0

b

1

1 b

1

b

2

1 b

2

b

N-1

1 b

N-1

Fig. 10.2-12

C

b

N-2

1 b

N-2

2

N-2

C 2

N-3

C

Attributes:

No floating nodes which implies insensitive to parasitics and fast

No terminating capacitor required

With the above configuration, charge feedthrough will be V

error

-(C

OL

/2C

N

)V

Can totally eliminate parasitics with parasitic-insensitive switched capacitor circuitry

but not the charge feedthrough

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-15

CMOS Analog Circuit Design P.E. Allen - 2010

EXTENDING THE RESOLUTION OF PARALLEL DIGITAL-ANALOG

CONVERTERS

Background

Technique:

Divide the total resolution N into k smaller sub-DACs each with a resolution of

N

k

.

Result:

Smaller total area.

More resolution because of reduced largest to smallest component spread.

Approaches:

Combination of similarly scaled subDACs

Divider approach (scale the analog output of the subDACs)

Subranging approach (scale the reference voltage of the subDACs)

Combination of differently scaled subDACs

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-16

CMOS Analog Circuit Design P.E. Allen - 2010

COMBINATION OF SIMILARLY SCALED SUBDACs

Analog Scaling - Divider Approach

Example of combining a m-bit

and k-bit subDAC to form a

m+k-bit DAC.

v

OUT

=

b

0

2

+

b

1

4

+ +

b

m-1

2

m

V

REF

+

1

2

m

b

m

2

+

b

m+1

4

+ +

b

m+k-1

2

k

V

REF

v

OUT

=

b

0

2

+

b

1

4

+ +

b

m-1

2

m

+

b

m

2

m+1

+

b

m+1

2

m+2

+ +

b

m+k-1

2

m+k

V

REF

m-MSB

bits

k-LSB

bits

m-bit

MSB

DAC

k-bit

LSB

DAC

2

m

V

REF

V

REF

+

+

v

OUT

Fig. 10.3-1

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-17

CMOS Analog Circuit Design P.E. Allen - 2010

Example 350-4 - Illustration of the Influence of the Scaling Factor

Assume that m = 2 and k = 2 in Fig. 10.3-1 and find the transfer characteristic of this

DAC if the scaling factor for the LSB DAC is 3/8 instead of 1/4. Assume that V

REF

= 1V

What is the INL and DNL for this DAC? Is this DAC monotonic or not?

Solution

The ideal DAC output is given as

v

OUT

=

b

0

2

+

b

1

4

+

1

4

b

2

2

+

b

3

4

=

b

0

2

+

b

1

4

+

b

2

8

+

b

3

16

.

The actual DAC output can be written as

v

OUT

(act.)

=

b

0

2

+

b

1

4

+

3b

2

16

+

3b

3

32

=

16b

0

32

+

8b

1

32

+

6b

2

32

+

3b

3

32

The results are tabulated in the following table for this example.

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-18

CMOS Analog Circuit Design P.E. Allen - 2010

Example 350-4 - Continued

Ideal and Actual Analog Output for the DAC in Ex. 350-4,

The table contains all the

information we are seeking

An LSB for this example is

1/16 or 2/32. The fourth

column gives the +INL as

1. 5LSB and the -INL as

0 L S B. The fifth column

gives the +DNL as -0.5LSB

and the -DNL as -1.5LSB

Because the -DNL is greater

than -1LSB, this DAC is not

monotonic.

Input

Digital

Word

v

OUT

(act.) v

OUT

v

OUT

(act.)

- v

OUT

Change in

v

OUT

(act) -

2/32

0000 0/32 0/32 0/32 -

0001 3/32 2/32 1/32 1/32

0010 6/32 4/32 2/32 1/32

0011 9/32 6/32 3/32 1/32

0100 8/32 8/32 0/32 -3/32

0101 11/32 10/32 1/32 1/32

0110 14/32 12/32 2/32 1/32

0111 17/32 14/32 3/32 1/32

1000 16/32 16/32 0/32 -3/32

1001 19/32 18/32 1/32 1/32

1010 22/32 20/32 2/32 1/32

1011 25/32 22/32 3/32 1/32

1100 24/32 24/32 0/32 -3/32

1101 27/32 26/32 1/32 1/32

1110 30/32 28/32 2/32 1/32

1111 33/32 30/32 3/32 1/32

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-19

CMOS Analog Circuit Design P.E. Allen - 2010

Reference Scaling - Subranging Approach

Example of combining a m-bit and k-bit subDAC to form a m+k-bit DAC.

m-MSB

bits

k-LSB

bits

m-bit

MSB

DAC

k-bit

LSB

DAC

V

REF

V

REF

/2

m

+

+

v

OUT

Fig. 10.3-2

v

OUT

=

b

0

2

+

b

1

4

+ +

b

m-1

2

m

V

REF

+

b

m

2

+

b

m+1

4

+ +

b

m+k-1

2

k

V

REF

2

m

v

OUT

=

b

0

2

+

b

1

4

+ +

b

m-1

2

m

+

b

m

2

m+1

+

b

m+1

2

m+2

+ +

b

m+k-1

2

m+k

V

REF

Accuracy considerations of this method are similar to the analog scaling approach.

Advantage: There are no dynamic limitations associated with the scaling factor of 1/2

m

.

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-20

CMOS Analog Circuit Design P.E. Allen - 2010

Current Scaling Dac Using Two SubDACs

Implementation:

+

-

I

16

I

8

I

4

I

2

I

16

I

8

I

4

I

2

15R

R

LSB MSB

R

F v

OUT

i

o

i

2

i

1

MSB subDAC LSB subDAC

b

0

b

1

b

2

b

3

b

4

b

5

b

6

b

7

Current

Divider

Fig. 10.3-3

v

OUT

= R

F

I

|

|

|

|

|

|

|

|

\

|

|

[

)

j

j

b

0

2

+

b

1

4

+

b

2

8

+

b

3

16

+

1

16

\

|

|

[

)

j

j

b

4

2

+

b

5

4

+

b

6

8

+

b

7

16

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-21

CMOS Analog Circuit Design P.E. Allen - 2010

Charge Scaling DAC Using Two SubDACs

Implementation:

+

-

V

REF

1

C

2

C

4

C

2

b

7

2

2

2

2

b

6

b

5

b

1

b

0

v

OUT

C

2

b

4

8

C

8

2

b

3

2

b

2

C

2

C

4

C C

8

C

s

S

c

a

l

i

n

g

C

a

p

a

c

i

t

o

r

LSB Array MSB Array Terminating

Capacitor

070515-01

Circuit for LSB Thevenin Eq. Circuit for MSB Thevenin Eq.

Design of the scaling capacitor, C

s

:

The series combination of C

s

and the LSB array must terminate the MSB array or

equal C/8. Therefore, we can write

C

8

=

1

1

C

s

+

1

2C

or

1

C

s

=

8

C

-

1

2C

=

16

2C

-

1

2C

=

15

2C

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-22

CMOS Analog Circuit Design P.E. Allen - 2010

Equivalent Circuit of the Charge Scaling Dac Using Two SubDACs

Simplified equivalent circuit:

where the Thevenin equivalent voltage

of the MSB array is

V

1

=

|

|

|

|

|

|

|

|

\

|

|

[

)

j

j

1

15/8

b

0

+

\

|

|

[

)

j

j

1/2

15/8

b

1

+

\

|

|

[

)

j

j

1/4

15/8

b

2

+

\

|

|

[

)

j

j

1/8

15/8

b

3

V

REF

=

16

15

\

|

|

[

)

j

j

b

0

2

+

b

1

4

+

b

2

8

+

b

3

16

V

REF

and the Thevenin equivalent voltage of the LSB array is

V

2

=

|

|

|

|

|

|

|

|

\

|

|

[

)

j

j

1/1

2

b

4

+

\

|

|

[

)

j

j

1/2

2

b

5

+

\

|

|

[

)

j

j

1/4

2

b

6

+

\

|

|

[

)

j

j

1/8

2

b

7

V

REF

=

\

|

|

[

)

j

j

b

4

2

+

b

5

4

+

b

6

8

+

b

8

16

V

REF

Combining the elements of the simplified equivalent circuit above gives

v

OUT

=

\

|

|

[

)

j

j

1

2

+

15

2

1

2

+

15

2

+

8

15

V

1

+

\

|

|

[

)

j

j

8

15

1

2

+

15

2

+

8

15

V

2

=

\

|

|

[

)

j

j

15+1515

15+1515+16

V

1

+

\

|

|

[

)

j

j

16

15+1515+16

V

2

=

15

16

V

1

+

1

16

V

2

v

OUT

=

\

|

|

[

)

j

j

b

0

2

+

b

1

4

+

b

2

8

+

b

3

16

+

b

4

32

+

b

5

64

+

b

6

128

+

b

7

256

V

REF

=

7

X

i=0

b

i

V

REF

2

i+1

+

-

C

s

= 2C/15

C + 7C/8

= 15C/8

V

1

V

2

2C

v

OUT

070515-02

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-23

CMOS Analog Circuit Design P.E. Allen - 2010

Charge Amplifier DAC Using Two Binary Weighted Charge Amplifier SubDACs

Implementation:

V

REF

+

-

v

OUT

+

-

C

b

4

1

b

4

C/2

b

5

1

b

5

b

6

1

b

6

b

7

1

b

7

C/4

C/8

+

-

2C

1

V

REF

+

-

C

b

0

1

b

0

C/2

b

1

1

b

1

b

2

1

b

2

b

3

1

b

3

C/4

C/8

+

-

2C

1

C/8

A1 A2

LSB Array MSB Array

v

O1

Fig. 10.3-6

Attributes:

MSB subDAC is not dependent upon the accuracy of the scaling factor for the LSB

subDAC.

Insensitive to parasitics, fast

Limited to op amp dynamics (GB)

No ICMR problems with the op amp

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-24

CMOS Analog Circuit Design P.E. Allen - 2010

COMBINATION OF DIFFERENTLY SCALED SUBDACs

Voltage Scaling MSB SubDAC And Charge Scaling LSB SubDAC

Implementation:

C

k

=

2

k-1

C

S

k-1,A

S

F

S

F

Bus A

Bus B

S

k,A

S

k,B

C

k-1

=

2

k-2

C

S

k-1,B

C

2

=2C

C

1

=C

C

v

OUT

S

2A

S

2B

S

1A

S

1B

m-to-2

m

Decoder A

m-to-2

m

Decoder B

V

REF

R

1

R

2

R

3

R

2

m-2 R

2

m-1 R

2

m

m-MSB bits

m-MSB bits

m-bit, MSB voltage

scaling subDAC

k-bit, LSB charge

scaling subDAC

Fig. 10.3-7

Operation:

1.) Switches S

F

and S

1B

through S

k,B

discharge all capacitors.

2.) Decoders A and B connect Bus A and Bus B to the top and bottom, respectively, of

the appropriate resistor as determined by the m-bits.

3.) The charge scaling subDAC divides the voltage across this resistor by capacitive

division determined by the k-bits.

Attributes:

MSBs are monotonic but the accuracy is poor

Accuracy of LSBs is good

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-25

CMOS Analog Circuit Design P.E. Allen - 2010

Voltage Scaling MSB SubDAC And Charge Scaling LSB SubDAC - Continued

Equivalent circuit of the voltage scaling (MSB) and charge scaling (LSB) DAC:

C

k

=

2

k-1

C

S

k-1,A

Bus A

Bus B

S

k,A

S

k,B

C

k-1

=

2

k-2

C

S

k,B

C

2

=2C

C

1

=C

C

v

OUT

S

2A

S

2B

S

1A

S

1B

2

-m

V

REF

V'

REF

2

-m

V

REF

V'

REF

v

OUT

C

eq.

2

k

C - C

eq.

Bus A

Bus B

v'

OUT

Fig. 10.3-8

where,

V

REF

= V

REF

b

0

2

1

+

b

1

2

2

+ +

b

m-2

2

m-1

+

b

m-1

2

m

and

v

OUT

=

V

REF

2

m

b

m

2

+

b

m+1

2

2

+ +

b

m+k

2

k-1

+

b

m+k-1

2

k

= V

REF

b

m

2

m+1

+

b

m+1

2

m+2

+ +

b

m+k

2

m+k-1

+

b

m+k-1

2

m+k

Adding V

REF

and v

OUT

gives the DAC output voltage as

v

OUT

= V

REF

+ v

OUT

= V

REF

b

0

2

1

+

b

1

2

2

++

b

m-2

2

m-1

+

b

m-1

2

m

+

b

m

2

m+1

+

b

m+1

2

m+2

++

b

m+k

2

m+k-1

+

b

m+k-1

2

m+k

which is equivalent to an m+k bit DAC.

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-26

CMOS Analog Circuit Design P.E. Allen - 2010

Charge Scaling MSB SubDAC and Voltage Scaling LSB SubDAC

v

OUT

=

b

0

2

1

+

b

1

2

2

++

b

m-2

2

m-1

+

b

m-1

2

m

V

REF

+

v

k

2

m

where v

k

=

b

m

2

1

+

b

m+1

2

2

++

b

m+k

2

k-1

+

b

m+k-1

2

k

V

REF

v

OUT

=

b

0

2

1

+

b

1

2

2

+ +

b

m-2

2

m-1

+

b

m-1

2

m

+

b

m

2

m+1

+

b

m+1

2

m+2

+ +

b

m+k

2

m+k-1

+

b

m+k-1

2

m+k

V

REF

Attributes:

MSBs have good accuracy

LSBs are monotonic, have poor accuracy - require trimming for good accuracy

C

1

=

2

m

C

S

2,A

S

1,A

S

1,B

C

2

=

2

m-1

C

S

2,B

C

m-1

=2

1

C

C

m

=C

C

m

=C

v

OUT

S

m-2A

S

m-2B

S

m-1A

S

m-1B

V

REF

k-

to-

2

k

Decoder

k-LSB bits

R

1

R

2

R

3

R

2

k-2

R

2

k-1

R

2

k

V

REF

m-bit, MSB charge scaling subDAC

k-bit,

LSB

voltage

scaling

subDAC

v

k

Fig. 10.3-9A

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-27

CMOS Analog Circuit Design P.E. Allen - 2010

Tradeoffs in SubDAC Selection to Enhance Linearity Performance

Assume a m-bit MSB subDAC and a k-bit LSB subDAC.

MSB Voltage Scaling SubDAC and LSB Charge Scaling SubDAC (n = m+k)

INL and DNL of the m-bit MSB voltage-scaling subDAC:

INL(R) = 2

m-1

2

n

2

m

R

R

= 2

n-1

R

R

LSBs and DNL(R) =

R

R

2

n

2

m

= 2

k

R

R

LSBs

INL and DNL of the k-bit LSB charge-scaling subDAC:

INL(C) = 2

k-1

C

C

LSBs and DNL(C) = (2

k

-1)

C

C

LSBs

Combining these relationships:

INL = INL(R) + INL(C) =

2

n-1

R

R

+ 2

k-1

C

C

LSBs

and DNL = DNL(R) + DNL(C) =

2

k

R

R

+ (2

k

-1)

C

C

LSBs

MSB Charge Scaling SubDAC and LSB Voltage Scaling SubDAC

INL = INL(R) + INL(C) =

2

k-1

R

R

+ 2

n-1

C

C

LSBs

and DNL = DNL(R) + DNL(C) =

R

R

+ (2

n

-1)

C

C

LSBs

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-28

CMOS Analog Circuit Design P.E. Allen - 2010

Example 350-5 - Design of a DAC using Voltage Scaling for MBSs and Charge

Scaling for LSBs

Consider a 12-bit DAC that uses voltage scaling for the MSBs charge scaling for the

LSBs. To minimize the capacitor element spread and the number of resistors, choose m =

5 and k = 7. Find the tolerances necessary for the resistors and capacitors to give an INL

and DNL equal to or less than 2 LSB and 1 LSB, respectively.

Solution

Substituting n = 12 and k = 7 into the previous equations gives

2 = 2

11

R

R

+ 2

6

C

C

and 1 = 2

7

R

R

+ (2

7

-1)

C

C

Solving these two equations simultaneously gives

C

C

=

2

4

-2

2

11

- 2

6

- 2

4

= 0.0071

C

C

= 0.71%

R

R

=

2

8

- 2

6

-2

2

18

- 2

13

- 2

11

= 0.0008

R

R

= 0.075%

We see that the capacitor tolerance will be easy to meet but that the resistor tolerance

will require resistor trimming to meet the 0.075% requirement. Because of the 2

n-1

multiplying R/R in the relationship, we are stuck with approximately 0.075%.

Therefore, choose m = 2 (which makes the 0.075% easier to achieve) and let k = 10 which

gives R/R = 0.083% and C/C = 0.12%.

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-29

CMOS Analog Circuit Design P.E. Allen - 2010

Example 350-6 - Design of a DAC using Charge Scaling for MBSs and Voltage

Scaling for LSBs

Consider a 12-bit DAC that uses charge scaling for the MSBs voltage scaling for the

LSBs. To minimize the capacitor element spread and the number of resistors, choose m =

7 and k = 5. Find the tolerances necessary for the resistors and capacitors to give an INL

and DNL equal to or less than 2 LSB and 1 LSB, respectively.

Solution

Substituting the values of this example into the relationships developed on a previous

slide, we get

2 = 2

4

R

R

+ 2

11

C

C

and 1 =

R

R

+ (2

12

-1)

C

C

Solving these two equations simultaneously gives

C

C

=

2

4

-2

2

16

-2

11

-2

4

= 0.000221

C

C

= 0.0221% and

R

R

3

2

5

-1

= 0.0968

R

R

= 9.68%

For this example, the resistor tolerance is easy to meet but the capacitor tolerance will

be difficult. To achieve accurate capacitor tolerances, we should decrease the value of m

and increase the value of k to achieve a smaller capacitor value spread and thereby

enhance the tolerance of the capacitors. If we choose m = 4 and k = 8, the capacitor

tolerance is 0.049% and the resistor tolerance becomes 0.79% which is still reasonable.

The largest to smallest capacitor ratio is 8 rather than 64 which helps to meet the

capacitor tolerance requirements.

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-30

CMOS Analog Circuit Design P.E. Allen - 2010

SERIAL DIGITAL-ANALOG CONVERTERS

Serial DACs

Typically require one clock pulse to convert one bit

Types considered here are:

Charge-redistribution

Algorithmic

Charge Redistribution DAC

Implementation:

V

REF

S

2

S

3

S

1

S

4

C

2 C

1

v

C2

Fig. 10.4-1

Operation:

Switch S

1

is the redistribution switch that parallels C

1

and C

2

sharing their charge

Switch S

2

precharges C

1

to V

REF

if the ith bit, b

i

, is a 1

Switch S

3

discharges C

1

to zero if the ith bit, b

i

, is a 0

Switch S

4

is used at the beginning of the conversion process to initially discharge C

2

Conversion always begins with the LSB bit and goes to the MSB bit.

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-31

CMOS Analog Circuit Design P.E. Allen - 2010

Example 350-7 - Operation of the Serial, Charge Redistribution DAC

Assume that C

1

= C

2

and that

the digital word to be converted

is given as b

0

= 1, b

1

= 1, b

2

= 0,

and b

3

= 1. Follow through the

sequence of events that result in

the conversion of this digital

input word.

Solution

1.) S

4

closes setting v

C2

= 0.

2.) b

3

= 1, closes switch S

2

causing v

C1

= V

REF

.

3.) Switch S

1

is closed causing v

C1

= v

C2

= 0.5V

REF

.

4.) b

2

= 0, closes switch S

3

, causing v

C1

= 0V.

5.) S

1

closes, the voltage across both C

1

and C

2

is 0.25V

REF

.

6.) b

1

= 1, closes switch S

2

causing v

C1

= V

REF

.

7.) S

1

closes, the voltage across both C

1

and C

2

is (1+0.25)/2V

REF

= 0.625V

REF

.

8.) b

0

= 1, closes switch S

2

causing v

C1

= V

REF

.

9.) S

1

closes, the voltage across both C

1

and C

2

is (0.625 + 1)/2V

REF

= 0.8125V

REF

=

(13/16)V

REF

.

0 1 2 3 4 5 6 7 8

1

3/4

1/2

1/4

0

t/T

v

C

1

/

V

R

E

F

0 1 2 3 4 5 6 7 8

1

3/4

1/2

1/4

0

t/T

v

C

2

/

V

R

E

F

13/16 13/16

Fig. 10.4-2

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-32

CMOS Analog Circuit Design P.E. Allen - 2010

Pipeline DAC

The pipeline DAC is simply an extension of the sub-DACs concept to the limit where the

bits converted by each sub-DAC is 1.

Implementation:

z

-1

1/2

b

N-1

= 1

z

-1

1/2

b

N-2

= 1

z

-1

1/2

b

0

= 1

0

V

REF

v

OUT

Fig. 10.4-3

V

out

(z) = [b

0

z

-1

+ 2

-1

b

1

z

-2

+ + 2

-(N-2)

b

N-2

z

-(N-1)

+

b

N-1

z

-N

]V

REF

where b

i

is either 1 if the ith bit is high or low. The z

-1

blocks represent a delay of one

clock period between the 1-bit sub-DACs.

Attributes:

Takes N+1 clock cycles to convert the digital input to an analog output

However, a new analog output is converted every clock after the initial N+1 clocks

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-33

CMOS Analog Circuit Design P.E. Allen - 2010

Algorithmic (Iterative) DAC

Implementation:

Sample

and

hold

+1

+1

1

2

+V

REF

A

B

-V

REF

v

OUT

FIG. 10.4-4

Closed form of the previous series expression is,

V

out

(z) =

b

i

z

-1

V

REF

1 - 0.5z

-1

Operation:

Switch A is closed when the ith bit is 1 and switch B is closed when the ith bit is 0.

Start with the LSB and work to the MSB.

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-34

CMOS Analog Circuit Design P.E. Allen - 2010

Example 350-8 - Digital-Analog Conversion Using the Algorithmic Method

Assume that the digital word to be converted is 11001 in the order of LSB to MSB

Find the converted output voltage and sketch a plot of v

OUT

/V

REF

as a function of t/T

where T is the period for one conversion.

Solution

1.) The conversion starts by zeroing the

output (not shown on Fig. 10.4-4).

2.) The LSB = 1, switch A is closed and

V

REF

is summed with zero to give an

output of +V

REF

.

3.) The next LSB = 0, switch B is closed and

v

OUT

= -V

REF

+0.5V

REF

= -0.5V

REF

.

4.) The next LSB = 0, switch B is closed and

v

OUT

= -V

REF

+0.5(-0.5V

REF

) = -

1.25V

REF

.

5.) The next LSB = 1, switch A is closed and v

OUT

= V

REF

+0.5(-1.25V

REF

) = 0.375V

REF

.

6.) The MSB = 1, switch A is closed and v

OUT

= V

REF

+ 0.5(0.375V

REF

) = 1.1875V

REF

= (19/16)V

REF

. (Note that because the actual V

REF

of this example if V

REF

or 2V

REF

,

the analog value of the digital word 11001 is 19/32 times 2V

REF

or (19/16)V

REF

.)

0 1 2 3 4 5

2.0

19/16

1.0

0

-1/2

3/8

-1.0

-5/4

-2.0

v

OUT

/V

REF

t

Fig. 10.4-5

Lecture 350 Parallel DACs, Improved Resolution DACs and Serial DACs (3/28/10) Page 350-35

CMOS Analog Circuit Design P.E. Allen - 2010

SUMMARY

Voltage scaling DACs are monotonic, use equal resistors but are sensitive to capacitve

parasitics

Charge scaling DACs are fast with good accuracy but have large element spread and are

nonmonotonic

DAC resolution can be increased by combining several subDACs with smaller

resolution

Methods of combining include scaling the output or the reference of the non-MSB

subDACs

SubDACs can use similar or different scaling methods

Tradeoffs in the number of bits per subDAC and the type of subDAC allow minimization

of the INL and DNL

Serial, charge redistribution DAC is simple and requires minimum area but is slow and

requires complex external circuitry

Serial, algorithmic DAC is simple and requires minimum area but is slow and requires

complex external circuitry

You might also like

- Kelvin DividerDocument2 pagesKelvin DividerlonemubashirNo ratings yet

- Electronics 3 Checkbook: The Checkbooks SeriesFrom EverandElectronics 3 Checkbook: The Checkbooks SeriesRating: 5 out of 5 stars5/5 (1)

- Experinment 10Document5 pagesExperinment 10mano17doremonNo ratings yet

- Easy(er) Electrical Principles for General Class Ham License (2019-2023)From EverandEasy(er) Electrical Principles for General Class Ham License (2019-2023)No ratings yet

- DAC AnalysisDocument19 pagesDAC Analysisమురళీధర్ ఆది ఆంధ్రుడుNo ratings yet

- Week 3Document25 pagesWeek 3İBRAHİM YÜMLÜNo ratings yet

- Bits, Noise, and Linearity The Imperfections of ADCs - Chemistry LibreTextsDocument4 pagesBits, Noise, and Linearity The Imperfections of ADCs - Chemistry LibreTextsketkyhuNo ratings yet

- Easy(er) Electrical Principles for General Class Ham License (2015-2019)From EverandEasy(er) Electrical Principles for General Class Ham License (2015-2019)Rating: 5 out of 5 stars5/5 (1)

- Isro 2018Document71 pagesIsro 2018gnanarani nambiNo ratings yet

- Adc-DacDocument21 pagesAdc-DacSon SonNo ratings yet

- Unit-III Adc & DacDocument20 pagesUnit-III Adc & DacK Krishna Murthy 184450No ratings yet

- D/A Converters: Digital to Analog Conversion TechniquesDocument14 pagesD/A Converters: Digital to Analog Conversion Techniquesjonathan stevenNo ratings yet

- DLC Lab - 10Document7 pagesDLC Lab - 10Didarul Alam AlifNo ratings yet

- BI Technologies R2R Resistor Ladder NetworksDocument6 pagesBI Technologies R2R Resistor Ladder NetworksChethan JayasimhaNo ratings yet

- Adc ConversionDocument20 pagesAdc Conversionhemantec100% (1)

- Measuring InstrDocument4 pagesMeasuring InstrG ParidaNo ratings yet

- R2R 2013Document4 pagesR2R 2013Suyog DhakneNo ratings yet

- Unit5 - ADC - DAC - Notes - Unit 5Document16 pagesUnit5 - ADC - DAC - Notes - Unit 5Chinmai NimgadeNo ratings yet

- Unit 4 NotesDocument26 pagesUnit 4 NotesJohnsi JNo ratings yet

- Euler's PathDocument10 pagesEuler's PathSatish Kumar0% (1)

- Introduction To A/D ConversionDocument20 pagesIntroduction To A/D ConversionWala SaadehNo ratings yet

- ECEN3250 Lab 7: Design of Common-Source MOS Amplifiers Prelab AssignmentDocument14 pagesECEN3250 Lab 7: Design of Common-Source MOS Amplifiers Prelab AssignmentIhsanAbdillahNo ratings yet

- Lab 11 DAC and ADC Full PackageDocument5 pagesLab 11 DAC and ADC Full PackageLoveWorldCanadaNo ratings yet

- Solns 29Document102 pagesSolns 29ramprakash_rampelliNo ratings yet

- 1V 10-Bit Successive Approximation ADC For Low Power Biomedical ApplicationsDocument4 pages1V 10-Bit Successive Approximation ADC For Low Power Biomedical ApplicationsSounakDuttaNo ratings yet

- MECH 3211 Lecture 9 - Digital Instrumentation - 2Document29 pagesMECH 3211 Lecture 9 - Digital Instrumentation - 2Ahmed NurNo ratings yet

- Dec Exp 6 Student ManualDocument5 pagesDec Exp 6 Student ManualSakib MahmudNo ratings yet

- Uni-Kl Adc-Review Jan03 5782 PDFDocument33 pagesUni-Kl Adc-Review Jan03 5782 PDFMiguel BrunoNo ratings yet

- Lic Solution 4Document24 pagesLic Solution 4Muiz TankiNo ratings yet

- Table 29.1-1 - INL and DNL Calculation of 3-Bit DAC: I I EquivalentDocument102 pagesTable 29.1-1 - INL and DNL Calculation of 3-Bit DAC: I I EquivalentVannala GouthamNo ratings yet

- Charge-Scaling DAC Design and OperationDocument7 pagesCharge-Scaling DAC Design and Operationmilostar6No ratings yet

- Adc and Dac Converters: BY:-PULKIT PARASHAR (17BEE080), Pritam Yaduvanshi (17bee079) Guide:-Prof. Akhilesh NimjeDocument9 pagesAdc and Dac Converters: BY:-PULKIT PARASHAR (17BEE080), Pritam Yaduvanshi (17bee079) Guide:-Prof. Akhilesh NimjePritam YaduvanshiNo ratings yet

- Mismatch-Shaping Serial Digital-To-Analog Converter: Jesper Steensgaard Un-Ku Moon and Gabor C. TemesDocument4 pagesMismatch-Shaping Serial Digital-To-Analog Converter: Jesper Steensgaard Un-Ku Moon and Gabor C. TemesShorav SuriyalNo ratings yet

- 3EJ4 Set 07 Mixed Signal MJDDocument45 pages3EJ4 Set 07 Mixed Signal MJDSoroush AkNo ratings yet

- Lab 09 DacDocument8 pagesLab 09 DacSenthil KumarNo ratings yet

- DLC LAB - 10 - Student - ManualDocument8 pagesDLC LAB - 10 - Student - ManualImtiaj SajinNo ratings yet

- DEC LAB REPORT-06Document9 pagesDEC LAB REPORT-06anon_776365175No ratings yet

- Single Supply Op Amp DesignDocument5 pagesSingle Supply Op Amp DesignDamir KarabasicNo ratings yet

- 2.1 Goals of This Lab 2.2 Diode V-I Characteristics: DVM 1k R +5VDocument4 pages2.1 Goals of This Lab 2.2 Diode V-I Characteristics: DVM 1k R +5VRMK BrothersNo ratings yet

- 40104diDocument6 pages40104dimariastalinNo ratings yet

- Prensa Slua601Document29 pagesPrensa Slua601Miguelina RossiNo ratings yet

- Answer Key - Vlsi CIA IDocument5 pagesAnswer Key - Vlsi CIA IMaadheshNo ratings yet

- ADCDACDocument180 pagesADCDACKireetiNo ratings yet

- REPORTFINALDocument21 pagesREPORTFINALReal HumanityNo ratings yet

- 93004diDocument8 pages93004dirogererfredererNo ratings yet

- Lic Dec 2018 Ans PDFDocument24 pagesLic Dec 2018 Ans PDFVaibhavNo ratings yet

- EDN Design Ideas 2009Document144 pagesEDN Design Ideas 2009chag195675% (4)

- Coen6511 Lecture 9: Digital Circuit HierarchyDocument14 pagesCoen6511 Lecture 9: Digital Circuit Hierarchydeathnote gotNo ratings yet

- integratedelectronicsUNIT 3convertersDocument11 pagesintegratedelectronicsUNIT 3convertersYogeshwaranNo ratings yet

- DAC and ADC Fundamentals: Digital to Analog Conversion and Analog to Digital ConversionDocument63 pagesDAC and ADC Fundamentals: Digital to Analog Conversion and Analog to Digital ConversionMohammad ja'farNo ratings yet

- Mechatronics 06 2023Document32 pagesMechatronics 06 2023Deniz DemirNo ratings yet

- Advanced CMOS Logic Design TechniquesDocument13 pagesAdvanced CMOS Logic Design TechniquesAmjad WadalaNo ratings yet

- Analog Devices - MT-016Document6 pagesAnalog Devices - MT-016ModyKing99No ratings yet

- Clase 12 - AdcDocument57 pagesClase 12 - AdccamilaNo ratings yet

- Digital To Analog ConvertersDocument13 pagesDigital To Analog ConvertersPasha ChauhanNo ratings yet

- Designing DC-DC Converters Based On ZETA TopologyDocument8 pagesDesigning DC-DC Converters Based On ZETA TopologyMayeth MacedaNo ratings yet

- ConvertersDocument54 pagesConvertersyoboiiii649No ratings yet

- Air Cycle Refrigeration:-Bell - Coleman CycleDocument21 pagesAir Cycle Refrigeration:-Bell - Coleman CycleSuraj Kumar100% (1)

- Company's Profile Presentation (Mauritius Commercial Bank)Document23 pagesCompany's Profile Presentation (Mauritius Commercial Bank)ashairways100% (2)

- Critical Values For The Dickey-Fuller Unit Root T-Test StatisticsDocument1 pageCritical Values For The Dickey-Fuller Unit Root T-Test Statisticswjimenez1938No ratings yet

- QDA Miner 3.2 (With WordStat & Simstat)Document6 pagesQDA Miner 3.2 (With WordStat & Simstat)ztanga7@yahoo.comNo ratings yet

- LeasingDocument2 pagesLeasingfollow_da_great100% (2)

- Anthony Flagg's Complaint Against Eddie LongDocument23 pagesAnthony Flagg's Complaint Against Eddie LongRod McCullom100% (1)

- Reynold's Number Flow ExperimentDocument8 pagesReynold's Number Flow ExperimentPatrick GatelaNo ratings yet

- Difference Between Knowledge and SkillDocument2 pagesDifference Between Knowledge and SkilljmNo ratings yet

- BCM Risk Management and Compliance Training in JakartaDocument2 pagesBCM Risk Management and Compliance Training in Jakartaindra gNo ratings yet

- Market Participants in Securities MarketDocument11 pagesMarket Participants in Securities MarketSandra PhilipNo ratings yet

- Movie Review TemplateDocument9 pagesMovie Review Templatehimanshu shuklaNo ratings yet

- E200P Operation ManualDocument26 pagesE200P Operation ManualsharmasourabhNo ratings yet

- Why Companies Choose Corporate Bonds Over Bank LoansDocument31 pagesWhy Companies Choose Corporate Bonds Over Bank Loansতোফায়েল আহমেদNo ratings yet

- Broschuere Unternehmen Screen PDFDocument16 pagesBroschuere Unternehmen Screen PDFAnonymous rAFSAGDAEJNo ratings yet

- Business PlanDocument9 pagesBusiness PlanRico DejesusNo ratings yet

- Admission Checklist (Pre-) Master September 2021Document7 pagesAdmission Checklist (Pre-) Master September 2021Máté HirschNo ratings yet

- Maintenance: ASU-600 SeriesDocument54 pagesMaintenance: ASU-600 SeriesMichael Maluenda Castillo100% (2)

- Presentation Pineda Research CenterDocument11 pagesPresentation Pineda Research CenterPinedaMongeNo ratings yet

- Exercise Manual For Course 973: Programming C# Extended Features: Hands-OnDocument122 pagesExercise Manual For Course 973: Programming C# Extended Features: Hands-OnAdrian GorganNo ratings yet

- Checklist PBL 2Document3 pagesChecklist PBL 2Hazrina AwangNo ratings yet

- ABN AMRO Holding N.V. 2009 Annual ReportDocument243 pagesABN AMRO Holding N.V. 2009 Annual ReportF.N. HeinsiusNo ratings yet

- Blum2020 Book RationalCybersecurityForBusineDocument349 pagesBlum2020 Book RationalCybersecurityForBusineJulio Garcia GarciaNo ratings yet

- Responsibility Centres: Nature of Responsibility CentersDocument13 pagesResponsibility Centres: Nature of Responsibility Centersmahesh19689No ratings yet

- 2014 March CaravanDocument48 pages2014 March CaravanbahiashrineNo ratings yet

- 1 N 2Document327 pages1 N 2Muhammad MunifNo ratings yet

- Axtraxng™: Networked Access Control Management Software V27.XDocument2 pagesAxtraxng™: Networked Access Control Management Software V27.XChiluvuri VarmaNo ratings yet

- ECED Lab ReportDocument18 pagesECED Lab ReportAvni GuptaNo ratings yet

- EE3331C Feedback Control Systems L1: Overview: Arthur TAYDocument28 pagesEE3331C Feedback Control Systems L1: Overview: Arthur TAYpremsanjith subramani0% (1)

- GE Supplier Add Refresh FormDocument1 pageGE Supplier Add Refresh FormromauligouNo ratings yet

- Corena s2 p150 - Msds - 01185865Document17 pagesCorena s2 p150 - Msds - 01185865Javier LerinNo ratings yet