Professional Documents

Culture Documents

Chapitre I Microprocesseur 6809 GSEA12013

Uploaded by

xanafahdCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Chapitre I Microprocesseur 6809 GSEA12013

Uploaded by

xanafahdCopyright:

Available Formats

Conception des systmes Microprocesseurs

A.Cherkaoui

Introduction

chapitre 1: Microprocesseur 6809

Conception des systmes Microprocesseurs

Plan

Architecture du microprocesseur 6809

architecture externe

architecture interne

le schma fonctionnel

l'UAL

l'accumulateur

Introduction au jeu d'instructions du microprocesseur

la pile

Les interruptions

Les mmoires

Les interfaces

le P.I.A. (Interface parallle)

le P.T.M. (Compteur programmable)

l'A.C.I.A. (Interface srie)

2

Conception des systmes Microprocesseurs

Architecture du microprocesseur 6809

Le microprocesseur 6809 est un processeur 8 bits orient 16 bits.

Il est fabriqu en technologie MOS canal N

botier DIL 40 broches.Il est monotension(5V).

6809E est rythm par une horloge externe 2 MHZ

adapt multiprocesseur.

synchronis par une horloge extrieure.

Compatibilit complte entre les 2 versions.

3

Conception des systmes Microprocesseurs

Architecture du microprocesseur 6809

Le bus des donnes 8 bits (Do D7)

. 1 charge TTL et 8 entres de circuits CMOS. Bus en logique 3 tats.

Le bus des adresses 16 bits (A0 A15 )

.Bus en logique 3 tats. valides sur le front montant de Q.

Le bus de contrle

.La broche Read/Write . Valide sur le front montant de Q.

4

Conception des systmes Microprocesseurs

Architecture du microprocesseur 6809

Les lignes d'tat du bus : connatre l'tat du microprocesseur tout moment

BA (Bus available) et BS (Bus state)

1

er

cas : Le microprocesseur gre les bus d'adresses et de donnes.

2

me

cas: reconnaissance d'int pendant 2cycles.Vect Reset,NMI,IRQ,SW1,2,3

3

me

cas : Il attend la synchro sur une des lignes d'interruption. Les bus HZ

Dernier cas : (niveau bas sur HALT).(contrleur de DMA). Les bus HZ La ligne

BA au niveau haut indique que les bus sont en haute impdance.

5

Conception des systmes Microprocesseurs

Architecture du microprocesseur 6809

Broche d'initialisation RESET

Un niveau bas (x cycles d'horloge), rinitialisation complte du circuit:

l'instruction en cours est arrt

le registre de pagination (DP) est mis zro

les interruptions IRQ et FIRQ sont masques

l'interruption non masquable NMI est dsarme

Le PC. est initialis avec le contenu des vecteurs d'initialisation

qui se trouvent aux adresses $FFFE et $FFFF.

Ce contenu reprsente l'adresse du dbut du programme qui sera

excut par le microprocesseur.

6

Conception des systmes Microprocesseurs

Architecture du microprocesseur 6809

la broche : HALT (Arrt du microprocesseur).

7

BA = BS = 1

Dans ce cas :

les demandes d'interruption IRQ et FIRQ sont inhibes

les demandes d'accs direct (DMA) la mmoire sont autorise.

les demandes d'interruptions RESET et NMI sont prises en compte

mais leur traitement est diffr

les broches d'interruption

NMI (No Masquable Interrupt)

IRQ (Interrupt Request)

FIRQ (Fast Interrupt Request)

Entres d'horloge XTAL et EXTAL (Extension crystal)

Q

out

est en quadrature avec E

out

=4 *horloge

*Les donnes sont lues ou crites sur

le front descendant de Eout.

*Les adresses sont correctes partir

du front montant de Qout

Conception des systmes Microprocesseurs

Architecture du microprocesseur 6809

Broches complmentaires du bus de contrle :

MRDY (Memory ready) :

Allonger Eout de multiple de un quart de cycle max 10 cycles pour syst lents

DMA/BREQ (Direct Memory Acces/Bus Request)

-l'accs direct ou du rafrachissement mmoire

-le circuit ayant gnr cette commande le bus pendant de 15 cycles

Broches spcifiques au 6809 E

Entres d'horloge : Ein et Qin comme Eout et Qout du 6809

TSC (Tree States Control) comme DMA/BREQ ,partage de bus

LIC (Last Instruction Cycle):Le cycle qui suit est celui de recherche de code opratoire Ins

AVMA (Advanced Valid Memory Access) niveau haut signifie que le microprocesseur

utilisera les bus au cours du cycle suivant pour multiprocesseur

BUSY : Occupation des bus : Sortie mise au niveau haut pendant les instructions du

type : lecture,criture et excution du premier octet d'un oprande constitu de

deux octets (une adresse par exemple).

Dans un systme multiprocesseur, ce signal indique le besoin pour un Microprocesseur

de disposer des bus au cours du prochain cycle pour assurer l'intgrit de l'opration en

cours. Cela vite l'adressage simultane d'une mme zone mmoire par 2 microprocs.

8

Conception des systmes Microprocesseurs

Architecture du microprocesseur 6809

On ne doit pas activer TSC quand BUSY est actif

Exemple d'application :

9

LIC : fin d'excution de l'instruction

BUSY : besoin du bus au prochain cycle

AVMA : va utiliser les bus au prochain cycle

Conception des systmes Microprocesseurs

Prsentation des diffrents registres

interne au 6809

Les accumulateurs A, B ou D.

Les registres pointeurs

Les registres d'index X et Y 16bits sont utiliss pour les modes d'adresse index.

les registres S et U (16 bits). (pointeur de pile LIFO :U passage de paramtres)

Ces registres "pointent" toujours le haut de la zone mmoire attribue

Le Compteur de Programme (PC)

Le registre de codes condition (CCR)

10

Exemple de sauvegarde de tous les

registres avec S :

Conception des systmes Microprocesseurs

Le jeu d'instructions du 6809

L'ensemble des instructions de base, est 59 instructions. En tenant compte des

variantes (modes d'adressage) il atteint 1464 instructions

Extraction : lecture de la donne en mmoire, t=1(m).TE si m octets

Excution : traduction et interprtation de l'octet (code opratoire)

11

Une priode TE supplmentaire est ncessaire pour raliser concrtement l'opration

demande!

Conception des systmes Microprocesseurs

Le jeu d'Instructions

Instructions de traitement des donnes

Instructions arithmtiques

addition (DAA, ABX, ADC)

multiplication (MUL)

soustraction (SBC, SUB)

Instructions logiques

rotation droite et gauche (ROL, ROR)

dcalage droite et gauche (ASR, LSR et ASL, LSL)

les fonctions logiques de base (AND, OR, EOR)

l'incrmentation/dcrmentation et complmentation (COM - NEG -

NOP - INC - DEC - CLR)

Instruction de transfert de donnes

transferts internes entre registres (EXG - TFR)

transferts externes avec la mmoire (LD - ST)

12

Conception des systmes Microprocesseurs

Le jeu d'Instructions

Instructions de tests et de branchements

instructions de tests sur un bit / un octet (BIT, TST)

instruction de comparaison (CMP)

instruction de branchement conditionnel (branchement si les indicateurs

du CCR sont actifs

Instructions de branchement inconditionnel et de saut.

saut relatif (BRA, BRN : 1 ou 2 octets)

saut absolu (JMP : 2 octets)

Instructions dappel et de retour de sous-programme

Appel : saut absolu (JSR)

saut relatif (BSR)

Retour : RTS

Instructions oprant sur les pointeurs U, S et X, Y.

Load effective adress (in register) : LEA. donnes sur 16 bits.D et A

Empilement des registre dans la pile (PSH) dcrment pointeur

Dpilement des registres de la pile (PUL) incrment pointeur

13

Conception des systmes Microprocesseurs

Les modes d'adressage du 6809

Les modes d'adressage sont :

- ladressage inhrent ou implicite: ABX, ASL, ASR, CLR, INC

- ladressage immdiat: LDA #$35 (PC =Adr+2 ou +4)

- ladressage tendu: LDA $1997 (1997) A

- ladressage tendu indirect: LDA [$1997]: ((1997)) A

- ladressage direct: LDA $97 (DP:97) A

- ladressage par registre: TFR X,Y (transfert de X dans Y).

- ladressage index direct: LDA O,X ou LDA ,X. LDA 0,-X ou LDD 0,X++

- ladressage index indirect :LDA [$35,X]- LDU [D, Y] ([Y+D] et [Y+D+1])D

- ladressage relatif : LDA $FO,PC ou LEAX ETIQ, PC

14

Conception des systmes Microprocesseurs

Lassembleur 6809

Syntaxe du langage assembleur

Etiquette Code Code Commentaire

ORG Expression : Origine (initialisation du compteur programme)

RMB Expression : Reserve Memory Bytes: un "saut" du PC lassemblage

FCB expr1, expr2... Form Constant Byte

FDB Exp1, Exp2,... Form Double Byte Constant

FCC /A/ : Forme Constant Character string

END : la limite du programme

15

Conception des systmes Microprocesseurs

Lopration dassemblage

1re passe :

Analyse lexicographique :

Analyse syntaxique

Analyse smantique

2me passe

Lassembleur gnre le code objet en tenant compte des adresses et des

donnes relles

3me passe :

Cette phase fournit le listing avec son code objet

16

Conception des systmes Microprocesseurs

Plan adopt pour l'criture d'un programme

OPT ABS

Dfinition des variables

DEBUT EQU $4000

TIRQ EQU $5000

TFIRQ EQU $6000

MEM EQU $2000

PIA EQU $EF20

Rservation des cases mmoires

ORG MEM

MEM1 RMB 1

PILE RMB 100

PPILE EQU *

Rservation des ports

ORG PIA

DDRA RMB 1

CRA RMB 1

Programme principal

ORG DEBUT

17

LDS #PPILE

BRA *

Traitement des interruptions IRQ

ORG TIRQ

"

RTI

Traitement des interruptions FIRQ

ORG TFIRQ

"

RTI

Initialisation des vecteurs d'interruption

ORG $FFF6

FDB TFIRQ

FDB TIRQ

FDB TSWI

FDB TNMI

FDB DEBUT

END

Conception des systmes Microprocesseurs

Le fonctionnement en interruption

Dfinition

Une interruption est une procdure qui permet de suspendre l'excution

d'un programme au profit d'un autre, avec la possibilit de reprendre

l'excution du programme initial l o il avait t suspendu

Interruptions "matrielles" 6809 possde quatre:

RESET R-initialisation du microprocesseur.

NMI Non Masquable Interrupt

FIRQ Fast Interrupt Request (3 octets PC,CCR)

IRQ Interrupt Request (12 octets)

On peut forcer l'tat des deux bits voir tableau:

18

Masque concernant l'interruption IRQ.

Conception des systmes Microprocesseurs

Le fonctionnement en interruption

interruption "soft".

SWI (SoftWare Interrupt)

SWI2 (SoftWare Interrupt n2)

SWI3 (SoftWare Interrupt n3)

La sauvegarde du contexte est totale.

Les interruptions de synchronisation:

CWAI (attente d'interruption).

SYNC (attente de synchronisation).

Les lignes NMI, FIRQ, IRQ et RESET ainsi que l'instruction SWI

positionnent automatiquement le flag CCRb4 1 (masquage de l'IRQ).

Les lignes NMI, FIRQ et RESET ainsi que l'instruction SWI positionnent

automatiquement le flag CCRb6 1 (masquage de la FIRQ).

Les bits I et F tant positionns 1 lors de l'excution d'un

programme d'interruption, il est possible, nanmoins d'autoriser la prise

en compte de nouvelles interruptions en les repositionnant O.

19

Conception des systmes Microprocesseurs

Tableau rcapitulatif

Interruptions

20

Conception des systmes Microprocesseurs

Mthodologie de gestion

des priphriques dentres-sorties

Le mode programm

Avant, le microprocesseur teste ltat du priphrique

s assur de sa disponibilit.

Ltat du priphrique (prt ou occup, registre de rception plein ou

registre de transmission vide...) est gnralement indiqu par un bit dtat

appel flag.

Le mode interruptible

Scrutation pour connaitre quel est le contrleur qui a provoqu la demande

21

Conception des systmes Microprocesseurs

Mthodologie de gestion

des priphriques dentres-sorties

Ainsi apparat la notion de Priorit !

Vectorisation par dcodeur de priorit et Mux.

les sorties du codeur de priorit sont multiplexes avec les lignes d'adresse

A1, A2 et A3.

22

Conception des systmes Microprocesseurs

tude de linterface dE/S parallle PIA 6821

Le coupleur dentre/sortie parallle est un circuit dinterface programmable

(ou PIA : Peripheral Interface Adapter).

Le PIA communique avec le P laide des signaux (compatibles TTL)

reprsents sur la figure ci dessous.

D0 D7 du PIA sont relies D0 D7 du P .

E (Enable) du PIA est lie lentre dH du P.

R/W au P pour grer la lecture\criture entre

le PIA et le P.

Reset du PIA Reset du P et au poussoir

de Reset

CS0, CS1 et CS2 slection et @ du PIA activ si CS0= CS1 = 1 et CS2 = 0.

RS0 et RS1 slectionnent les registres internes du PIA selon le tableau :

Gnralement, RS0 est relie A0 et RS1 est relie A1, ce qui place les quatre

registres les uns la suite des autres.

IRQA et/ou IRQB seront ou non relies la ligne IRQ du P 6809 ct A, ou B, ou les deux.

23

Conception des systmes Microprocesseurs

Plan

Introduction

16 lignes dentres/sorties programmables

individuellement une ligne dentre/sortie

peut jouer alternativement le rle dentre

et de sortie,

quatre lignes eux sont des entres

(CA1 et CB1), les deux autres tant

programmables en entre ou en sortie

(CA2 et CB2).

Le PIA possde six registres internes , soit trois registres par port :

DDRA Data Direction Register A :

ORA (Output Register A) ou registre de sortie pour le port A :

CRA Control Register A : Cest un registre de contrle permettant,

pour le port A , de dfinir le mode de fonctionnement des lignes

dinterruption et de dialogue CA1 et CA2 ainsi que les possibilits de

gnration dinterruption via la ligne IRQA.

24

Conception des systmes Microprocesseurs

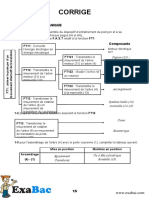

Programmation du PIA

Exemple:

Adresse PIA:

8000 DDRA et ORA

8001 CRA

8002 DDRB et ORB

8003 CRB

1. LDA #$00 Accs au DDRB

STA $8003 ou CLR $8003

2. LDA #$FF Port B en sortie

STA $8002

3. LDA #$04 Accs ORB

STA $8003

4. LDA #$E0 1110 0000 sur PortB

STA $8002

25

Adresses mmoires rserves au PIA en fonction de RS0 et RS1

Registre CRA du PIA

Conception des systmes Microprocesseurs

Etude de linterface srie asynchrone

A.C.I.A. 6850

A.C.I.A. : Asynchronous communication interface adapter.

Format du mot: 5 et 8 bits, prcd 1 bit de start et suivi de 2 bits de stop

compatibles TTL: Conversion TTLRS232 le1489 et RS232TTL le 1488

les niveaux fournis par lACIA : TTL et ceux dlivrs par la ligne:

les infos sont vhicules, dans le code ASCII:

liaison RS 232 (20Kbits)

RS 423 (100 Kbits)

RS 422 (10 mgabits)

26

niveau 1 : -

12V

niveau 0

: +12V

Conception des systmes Microprocesseurs

tude de linterface srie asynchrone

A.C.I.A. 6850

Schma :

Ce circuit intgre :

un metteur de donnes asynchrone

un rcepteur de donnes asynchrone

une logique de commande Modem

des entres dhorloge spares pour lmission et la rception.

Ce circuit comprend quatre registres internes :

1 registre de transmission

1 registre de rception.

1 registre de contrle

1 registre d'tat

27

Conception des systmes Microprocesseurs

ACIA

Cot microprocesseur :

Le bus des donnes : d0 ... D7, botier non slectionn ces lignes en HZ

Le bus de contrle:

1. E : Signal dactivation des changes

2. R/W = 1 ;buffers de sorties activs (possibilit de lire un registre).

3. R/W = O ;buffers dentres activs (possibilit dcriture dans un registre)

4. R/W utilise galement pour ladressage des registres internes

Le bus des adresses : CSO, CS1 ET /CS2 (Chip Select). Valide (110)

RS (Register select) utilise avec R/W pour choisir un registre parmi les 4

IRQ sortie

Cot extrieur :

Les lignes "horloge:

1. Txclk : horloge de transmission sur Txdata. Le Reg de dcalage de trans est syn sur de Txclk

2. Rxclk : horloge de rception sur Rxdata. Reg (charge et dcal) est syn sur Rxclk

3. Les vitesses de transmission et rception peuvent varier de O 500 Kbits/s.

28

Conception des systmes Microprocesseurs

ACIA

Les lignes de contrle dun priphrique type modem.

1.Ligne CTS (Clear To send)

Entre bas ,permet de savoir si le modem est prt recevoir des infos.

Influence sur le bit (TDRE) du SR, CTS bas sil ny a pas de modem

2.Ligne DCD (Data carrier detect)

niveau bas : prsence de la porteuse au niveau modem, tat normal.

remarque : non utilise, elle doit tre toujours au niveau bas !

Cette entre peut gnrer une interruption IRQ, si CR7 = 1 et si sur DCD

3.La sortie RTS (Request To Send)

mission demande par le microprocesseur au modem

RTS dpend du mot crit dans le CR.La demande se traduit par RTS bas

29

Conception des systmes Microprocesseurs

ACIA

Exemples d'utilisation :

Modem command par un ACIA

Liaison Acia Acia

30

Conception des systmes Microprocesseurs

ACIA

Organisation interne

TDR (Transmit Data Register)

O on place le mot (8 bits) transmettre. lcriture du mot sur de E(b

0

en 1er)

Ds que le transfert lieu , un bit du registre dtat est positionn "1"

RDR (Rception Data Register)

O on reoit le mot (8 bits) depuis le priphrique

Quand un caractre complet est reu, est automatiquement transfr du

registre de dcalage de rception dans le RDR. A ce moment l, un bit

dans le SR est positionn "1". Le caractre peut alors tre lu par le

microprocesseur. Le bit b

0

est reu en 1er.

le registre dtat est 1, le transfert automatique est suspendu !

Le registre dtat SR (Status Register)

Permet au microprocesseur de connatre tout instant ltat T\R

registre de contrle CR (Control Register)

Configure le circuit en adquation avec le priphrique,mot de contrle (8

bits) crit sur le front descendant de E. l'ACIA est 2 cases-mmoire,R\W

31

Conception des systmes Microprocesseurs

ACIA

RS et R/W permettent de slectionner l'ensemble des registres:

Tableau rcapitulatif (avec A0=RS) :

Illustrations :

32

Conception des systmes Microprocesseurs

ACIA

Prsentation du registre de contrle

CR0 et CR1 :

1. Dterminent le rapport de division sur les signaux dentre Rxclk et Txclk.

2. La combinaison (11) gnre un reset logiciel Master reset

3. Master reset indispensable avant toute programmation du CR.

4. Remise 0 du SR except les bits lis aux conditions externes :

5. Initialise le TDR et RDR (contenu nul)

CR2, CR3 et CR4 :

format de loctet transmettre o recevoir

CR5 et CR6:

Contrlent la fois la sortie RTS et la demande dinterruption en transmission.

Autorisent ou non une interrupt provoque par le fait que le TDR est vide ,TDRE = 1

Pourquoi ?

Lenvoi dun caractre vers la priphrie est toujours prcd dun test sur TDR pour

sassurer que celui-ci est vide. Ce test peut tre obtenu par :

1- Une scrutation permanente du bit dans le SR (on choisit CR6 et CR5 = 00).

2- Une interruption gnre par lACIA vers le microprocesseur chaque fois que le TDR

est vide (dans ce cas, on choisit CR6 et CR5 = 01).

33

Conception des systmes Microprocesseurs

ACIA

CR7(Ne concerne que le rcepteur):

Ce bit sert de masque dinterruption concernant les vnements suivants :

1- Registre de rception plein

2- Front montant sur lentre DCD indiquant la perte de la porteuse.

Ce bit mis 1 traduit ces vnements par une demande dinterruption IRQ bas.

tude des bits du registre d'tat.

SR0 = 1: registre de Rception RDR plein. SR0 = 0 -->RDR vide --> attend!

SR1 = 1: la donne est dispo ds le TDR. SR1 = 0 -->TDR plein--> on attend !

SR2 = 1 si DCD = 1 (absence porteuse).interup IRQ si autorise (CR7 = 1)

SR3 = 1: CTS est haut ( modem pas prt recevoir), forage de SR1= 1 --> la

transmission est interrompue !

SR4 = 1 :pas de sync absence du (des) bit(s) de stop

SR5 =1: plrs caractres reus avant lecture du caractre prcdent

SR6 = 1: la parit reue avec le caractre est incorrect

SR7=1 : Indique quil y a une demande dinterruption

34

Conception des systmes Microprocesseurs

ACIA

35

Registre de commande Registre dtat

Conception des systmes Microprocesseurs

Programmation

Programmer un ACIA consiste crire dans son registre de contrle un octet

pour dfinir le mode de fonctionnement

Il faut commencer par "Master reset " pour prendre contrle du CR

Le PG de transmission commence par le test du bit SR1 appel TDRE(TDR vide)

Pour un nouveau mot, on doit tester TDRE, ou exploiter la demande

dinterruption gnre lors du passage au niveau 1 de TDRE

Les donnes reues en srie par lentre RxData .Le rapport est programm

linitialisation de lACIA. suivant lun des 3 modes.

Puis ds RDR avec limination des bits de start,de stop et de parit

La rception commence par lecture de SR pour tester le bit RDRF = 1, test ou

demande dinterruption. Ds que RDRF = 1,fin rception mot dispo pour uP.

Conception des systmes Microprocesseurs

Gestion des interruptions

En transmission :

Si CR5 = 1 et CR6 = 0, la ligne IRQ est active au niveau bas ds que le TDR est

dclar vide par le passage au niveau 1 de TDRE. Le programme de traitement

de cette interruption a videmment comme but dcrire le caractre suivant

dans le TDR, ce qui entrane en plus la remise zro de TDRE donc le retour

ltat de repos de la ligne IRQ ainsi que la remise zro du bit SR7 du registre

dtat.

Ce fonctionnement est maintenu tant que lACIA nest pas sous contrle dun

Master Reset et tant que la ligne CTS est maintenue au niveau bas par le

modem.

Rappelons que lorsque le modem ne veut plus transmettre de caractre, il met

CTS au niveau haut ce qui force TDRE au niveau bas et inhibe le processus ci-

dessus.

Conception des systmes Microprocesseurs

Gestion des interruptions

En rception :

Si CR7 vaut 1, la ligne IRQ est activ au niveau bas chaque fois que le RDR est

plein (RDRF=1), le programme dinterruption est charg de lire le caractre

reu, ce qui en outre remet RDRF zro ainsi que la ligne dinterruption au

repos.

Cette opration est dclenche galement si une perte de la porteuse est

signale (DCD=1) ou si le bit OVRN (SR5) passe au niveau haut. Les flags (PE) et

(FE) ne dclenchent pas dinterruption et cest la charge du programme

dinterruption lui-mme de contrler que le mot reu ne comporte pas derreur

en testant les deux bits SR4 et SR6.

Conception des systmes Microprocesseurs

Exercices

1- Enonc du problme:

Le programme doit permettre dobtenir le mme fonctionnement que la carte oubli-clairage, soit

rpondre lquation logique:

A cet effet, le port A est utilis comme port dentre, et le port B en sortie de la faon suivante:

PA7: masse PA3: borne B(entre ds voiture) PB7: Non connect PB3: Non connect

PA6: masse PA2: borne C (veilleuses)PB6: Non connect PB2: Non connect

PA5: masse PA1: borne D (codes) PB5: Non connect PB1: Non connect

PA4: borne A(contact) PA0: borne E (dtresses) PB4: Non connect PB0: Bz

Conception des systmes Microprocesseurs

2- organigramme de fonctionnement et programme:

A complter

Conception des systmes Microprocesseurs

PTM 6840

Principe de fonctionnement

Le PTM (Programmable Timer Module) est un circuit programmable de la

famille 6800 permettant la programmation de temporisations variables.

Le PTM comprend 3 compteurs binaires 16bits, 3 registres de contrle associs

et un registre dtat. Ces compteurs sont sous le contrle du logiciel et peuvent

tre utiliss pour gnrer des interruptions et/ou des signaux en sorties.

Le PTM peut tre utilis pour des mesures de frquence, en compteur

dvnements, en mesure dintervalles de temps et pour dautres tches

similaires. Ce circuit peut gnrer des signaux carrs, des impulsions de largeur

programmable et des signaux de rapport cyclique variable et des interruptions.

Conception des systmes Microprocesseurs

PTM 6840

Les trois temporisateurs peuvent tre programms indpendamment.

*Bus de donnes(D0..D7)

*Slection du botier (CS0|,CS1-Chip Select) .

*Lecture/criture| (R/W|)

*Horloge E(Enable) : ce signal synchronise le transfert

*Demande dinterruption (IRQ|-Interrupt ReQuest) plusieurs lignes OU-cbl .

*Entre dinitialisation interne (Reset|)

Conception des systmes Microprocesseurs

PTM 6840

Reset| : un niveau bas sur cette entre est pris en compte dans le PTM par lhorloge

E. lorsquun niveau bas est reconnu sur cette entre par le PTM, les actions

suivantes ont lieu :

tous les registres tampons des compteurs sont repositionns leur valeur

maximum de comptage

tous les bits des registres de contrle sont mis 0 sauf cr10 qui est mis 1.

tous les compteurs sont chargs avec le contenu de leurs registres tampons

associs.

toutes les sorties Ox des compteurs sont mises 0 et les horloges externes (c|)

sont inhibes.

tous les bits du registre dtat sont mis 0.

Conception des systmes Microprocesseurs

PTM 6840

Lignes de slection des registres (RS0,RS1,RS2) : ces entrs sont utilises en

relation avec la ligne R/W| pour slecter les registres internes, les compteurs et

leurs registres tampons .

Registres de contrle : CR1, CR2, CR3 :

Dans le PTM, 3 registres criture seulement sont utiliss pour modifier le

fonctionnement du temporisateur pour pouvoir sadapter une grande varit

dapplications.

Le bit de poids faible du registre de contrle #1 est utilis comme un bit

dinitialisation interne. Quand ce bit est 0, tous les temporisateurs peuvent

fonctionner dans les modes dfinis par les autres bits des registres de contrle.

Le fait dcrire un 1 logique dans CR10 permet de rinitialiser tous les compteurs

avec le contenu de leurs registres tampons respectifs, toutes les horloges des

compteurs sont inhibes et les sorties des temporisateurs et les indicateurs

dinterruption sont mis 0. les registres tampons des compteurs et les registres

de contrle ne sont pas affects par une initialisation interne et peuvent tre

crits quelque soit ltat du bit CR10

Conception des systmes Microprocesseurs

PTM 6840

Les fonctions des bits des registres de contrle sont rsumes dans le tableau ci-

dessous :

Initialisation interne CR10=0 : tous les temporisateurs fonctionnent

CR10=1 :tous les temporisateurs sont initialiss

Adressage registres de contrle CR20=0 :criture dans CR# 3

CR20=1 :criture dans CR# 1

Contrle horloge temporisatrice #3 CR30=0 :horloge| T3 nest pas prcompte

CR30=1 : horloge| T3 est prcompte par/8

Source dhorloge temporisatrice # x CRx1=0 :Tx utilise horloge externe sur entre Cx|

CRx1=1 :Tx utilise horloge E

Mode du comptage du temporisateur # x CRx2=0 :Tx configur pour mode normal 16bits

CRx2=1 :Tx configur pour mode 2*8bits

Mode de comptage et contrle

dinterruption du temporisateur # x

CRx3, CRx4, CRx5

Validation dinterruption du

temporisateur # x

CRx6=0 :indicateur dinterruption masqu sur IRQ|

CRx6=1 :indicateur dinterruption valid sur IRQ|

Validation sortie compteur du

temporisateur # x

CRx7=0 :Tx sortie masque

CRx7=1 :Tx sortie valide

Conception des systmes Microprocesseurs

PTM 6840

Lignes dentres/sorties asynchrones

entres horloge (C1|, C2|, C3|) : les broches dentre C1|, C2| et C3| acceptent des

signaux asynchrones TTL pour dcrmenter respectivement les temporisateurs 1, 2 et 3.

entres de dclenchement (G1|, G2|, G3|) : les broches dentre G1|, G2| et G3|

acceptent des signaux asynchrones TTL pour dclencher respectivement les fonctions

des temporisateurs 1, 2 et 3.

les sorties des temporisateurs O1, O2 et O3 peuvent commander 2 charges TTL et

produire un signal dont la forme est dfini par les modes de fonctionnement astables ou

monostables. La forme du signal de sortie est dfinie en slectionnant soit le mode

16bits soit le mode 2*8bits. Le mode 16bits fournira un signal carr dans le mode astable

et une seule impulsion dans le mode monostable. Le mode 2*8bits fournira un signal

asymtrique dans les deux modes continus et monostables. Le bit CRx7 de chaque

registre de contrle est utilis pour valider la sortie correspondante. Si ce bit est 0, la

sortie restera ltat bas quelque soit le mode de fonctionnement.

Des signaux apparaissent sur les sorties ( sauf si CRx7=0) pendant les modes de

fonctionnement de comparaison de frquence et de largeur dimpulsion, mais la forme

relle des signaux nest pas dtermine pour les applications typiques.

Conception des systmes Microprocesseurs

Modes de fonctionnement PTM 6840

Le PTM a t conu pour fonctionner dans une grande gamme dapplications.

Les diffrents modes de fonctionnement du temporisateur sont dfinis laide

de trois bits de chaque registre de contrle ( CRx3, CRx4, CRx5 ). Ces modes sont

rsums dans le tableau suivant :

Registre de contrle Mode de fonctionnement du

temporisateur

CRx3 CRx4 CRx5

0 * 0 Continu

0 * 1 Monocoup

1 0 * Comparaison de frquence

1 1 * Comparaison de largeur dimpulsion

Conception des systmes Microprocesseurs

Mode de fonctionnement continu ( Multivibrateur astable)

PTM 6840

G| : transition ngative sur lentr G|

W : commande dcriture dans les registres tampons du temporisateur.

R :initialisation du temporisateur(CR10=1 ou Reset| externe=0)

N :nombre 16bits dans le registre tampon compteur.

L : nombre 8bits dans le registre tampon LSB du compteur( poids faible).

M : nombre 8bits dans le registre tampon MSB du compteur( poids fort).

T :transition ngative sur lentre dhorloge du compteur.

t0 :Cycle dinitialisation du compteur.

T0 :fin du temps de comptage.

Conception des systmes Microprocesseurs

Timer 6850

CR PTM 6850

49

Conception des systmes Microprocesseurs

PTM 6840

Conception des systmes Microprocesseurs

PTM 6840

Conception des systmes Microprocesseurs

PTM 6840

Conception des systmes Microprocesseurs

PTM 6840

Conception des systmes Microprocesseurs

PTM 6840

Conception des systmes Microprocesseurs

PTM 6840

Conception des systmes Microprocesseurs

PTM 6840

You might also like

- 6809 EnsaDocument15 pages6809 EnsaAchraf Rossoneri75% (12)

- Cours 6809 CIDocument117 pagesCours 6809 CIHamid Rezagui85% (13)

- Transformateur À Semi-Conducteurs: Révolutionner le réseau électrique pour la qualité de l'électricité et l'efficacité énergétiqueFrom EverandTransformateur À Semi-Conducteurs: Révolutionner le réseau électrique pour la qualité de l'électricité et l'efficacité énergétiqueNo ratings yet

- Exercices Assembleur MEHDIDocument52 pagesExercices Assembleur MEHDIMehdi Amrani76% (21)

- Langage Assembleur Motorola 6809Document2 pagesLangage Assembleur Motorola 6809MohammedZef100% (1)

- Guide Moto6809Document23 pagesGuide Moto6809Simo Bouna100% (3)

- AssembleurDocument26 pagesAssembleurHedi Yatouji100% (1)

- MicroprocesseurDocument7 pagesMicroprocesseurwalidjoeNo ratings yet

- Cours - Programmation C Pour Systèmes EmbarquésDocument53 pagesCours - Programmation C Pour Systèmes EmbarquéssouilelyNo ratings yet

- ERRAMI AhmedDocument7 pagesERRAMI AhmedYoussef EB0% (1)

- Le Microprocesseur 8086Document31 pagesLe Microprocesseur 8086Imed Abdesslem100% (1)

- Pic 16f877 RapportDocument16 pagesPic 16f877 RapportOmar Medbouh100% (2)

- Cours 8086Document53 pagesCours 8086babiloneNo ratings yet

- 68HC11Document22 pages68HC11Amin Elhamzaoui67% (3)

- Pia 6809Document5 pagesPia 6809Abdelwahab EL Filali100% (2)

- Cours Assembleur 6809 eDocument9 pagesCours Assembleur 6809 ewalidjoeNo ratings yet

- TP Informatique IndustrielleDocument7 pagesTP Informatique IndustrielleYoussef_Consty_4665100% (3)

- Cours Atmega16Document30 pagesCours Atmega16maîgaNo ratings yet

- Cours Microprocesseur ENSADocument138 pagesCours Microprocesseur ENSASheeya FilaliNo ratings yet

- Cours Microprocesseur-Microcontroleur (Trés Complet)Document107 pagesCours Microprocesseur-Microcontroleur (Trés Complet)Iheb Mawhoub94% (16)

- 1-TP Microprocesseur PDFDocument5 pages1-TP Microprocesseur PDFAmin DAHMANI100% (1)

- Ecole Supérieure de Technologie de Béni Mellal Université Sultan Moulay SlimaneDocument7 pagesEcole Supérieure de Technologie de Béni Mellal Université Sultan Moulay SlimaneSimo MabrouukNo ratings yet

- Microprocesseur 6809: Présentation GénéraleDocument11 pagesMicroprocesseur 6809: Présentation GénéraleMOHAMED TAMZAITINo ratings yet

- Cours MicroprocesseurDocument49 pagesCours Microprocesseurachernar09100% (2)

- Cours Et TD Électroniques NumériquesDocument60 pagesCours Et TD Électroniques NumériquesOussama Sadki100% (1)

- MicrocontroleursDocument61 pagesMicrocontroleursJamila DebayaNo ratings yet

- Cours Microcontrôleurs-Tres ImportantDocument132 pagesCours Microcontrôleurs-Tres ImportantNabil Dakhli0% (1)

- Architecture Du Microprocesseur 6809 de MotorolaDocument14 pagesArchitecture Du Microprocesseur 6809 de MotorolaPhylipe Rodrigez100% (1)

- COURS ET TRAVAUX PRATIQUES de MICROPROCESSEURDocument151 pagesCOURS ET TRAVAUX PRATIQUES de MICROPROCESSEURهشام درياس100% (10)

- Exercices Corriges Assembleur PDFDocument2 pagesExercices Corriges Assembleur PDFEmily44% (27)

- Expose MicrocontroleurDocument29 pagesExpose MicrocontroleurAssia Bakali88% (8)

- Processeur 6809Document172 pagesProcesseur 6809Oumar Mané50% (10)

- TD Prog Mikroc PicDocument27 pagesTD Prog Mikroc PicOmar Amri100% (1)

- TD Microprocesseur 8085Document1 pageTD Microprocesseur 8085nourelhouda71100% (3)

- TD2 VHDL Et Logique ProgrammableDocument17 pagesTD2 VHDL Et Logique ProgrammableKais BahrouniNo ratings yet

- Corrigé TD2Document3 pagesCorrigé TD2Nihal TaguercifiNo ratings yet

- Raspberry Pi | Pas à pas: Le guide du débutant avec les bases matériel, logiciel, et programmationFrom EverandRaspberry Pi | Pas à pas: Le guide du débutant avec les bases matériel, logiciel, et programmationNo ratings yet

- Projets Arduino avec Tinkercad | Partie 2: Concevoir des projets électroniques avancés basés sur Arduino avec TinkercadFrom EverandProjets Arduino avec Tinkercad | Partie 2: Concevoir des projets électroniques avancés basés sur Arduino avec TinkercadNo ratings yet

- Chapitre III Microprocesseur 6809 GSEA1Document36 pagesChapitre III Microprocesseur 6809 GSEA1kaoutarNo ratings yet

- Chapitre I Microprocesseur 6809 GSEA12013 PDFDocument56 pagesChapitre I Microprocesseur 6809 GSEA12013 PDFRyan Hj100% (1)

- Partie 2Document66 pagesPartie 2Fadoua MoutaoikilNo ratings yet

- Chapitre 1 Lat 54Document6 pagesChapitre 1 Lat 54radiaNo ratings yet

- Chapitre I Le Microprocesseur 6809Document10 pagesChapitre I Le Microprocesseur 6809Sabri AbidiNo ratings yet

- Architecture Et Programmation Des Micro-Contrôleurs: Khaled - Taouil@enetcom - Usf.tnDocument47 pagesArchitecture Et Programmation Des Micro-Contrôleurs: Khaled - Taouil@enetcom - Usf.tnamalNo ratings yet

- Micro CArduino EI31819 Deuxieme PartieDocument41 pagesMicro CArduino EI31819 Deuxieme Partieclément valleyNo ratings yet

- PIC16F84Document22 pagesPIC16F84Rida bellarraneNo ratings yet

- DSPIC30FDocument51 pagesDSPIC30Fouss18No ratings yet

- TP 1 Info Indus07Document15 pagesTP 1 Info Indus07MOHAMED TAMZAITINo ratings yet

- Chapitre II PIC 16F84ADocument32 pagesChapitre II PIC 16F84Amoumnimeryem2002No ratings yet

- 68hc11 v2 PDFDocument17 pages68hc11 v2 PDFmoutchedNo ratings yet

- Cours Microcontrôleur MCS-51Document19 pagesCours Microcontrôleur MCS-51Maha BadriNo ratings yet

- Pic 2Document49 pagesPic 2jugurthaNo ratings yet

- Chapitre 5 LE TMS320C6701 DSP PDFDocument9 pagesChapitre 5 LE TMS320C6701 DSP PDFSmart ClasseNo ratings yet

- Slide Atmega16bisDocument36 pagesSlide Atmega16bisNadhir BndNo ratings yet

- Microcontrôleur Famille PIC 16oDocument10 pagesMicrocontrôleur Famille PIC 16oAbdellah Faqdani100% (1)

- Chap 3-MicrocontroleurDocument35 pagesChap 3-MicrocontroleurYosra rhim YosraNo ratings yet

- Cours-mcAVRN (Mode de Compatibilité)Document181 pagesCours-mcAVRN (Mode de Compatibilité)larbi33% (3)

- Systèmes À Microprocesseurs - : Cas Du Microprocesseur Intel 8086Document52 pagesSystèmes À Microprocesseurs - : Cas Du Microprocesseur Intel 8086ANWAR ZAFZAFINo ratings yet

- Calendrier Academique 2014 2015 PDFDocument2 pagesCalendrier Academique 2014 2015 PDFxanafahdNo ratings yet

- AII Marocetude - Com Introduction Aux Microprocesseurs MP TP3Document23 pagesAII Marocetude - Com Introduction Aux Microprocesseurs MP TP3Lam ChNo ratings yet

- Chap 4 v2Document46 pagesChap 4 v2xanafahdNo ratings yet

- Cours TH Signal 08 09Document133 pagesCours TH Signal 08 09jojo_swit_gerl_93453No ratings yet

- La Relation Inflation-ChomageDocument2 pagesLa Relation Inflation-ChomagexanafahdNo ratings yet

- Exo EnslDocument14 pagesExo EnslDhiaeddine AtiNo ratings yet

- Chapitre II Les RegistresDocument18 pagesChapitre II Les RegistresMouhamed MoustaphaNo ratings yet

- Leçon A3-2 - Timer 0Document4 pagesLeçon A3-2 - Timer 0Mehdi BouchamiNo ratings yet

- Zelio Sur DouilleDocument224 pagesZelio Sur Douilledegdoug100% (1)

- Test n2 Correction Reduit2 PDFDocument10 pagesTest n2 Correction Reduit2 PDFSoufiane BoulachgourNo ratings yet

- Synthese Grafcet Selon EN 60848Document23 pagesSynthese Grafcet Selon EN 60848Paul DayangNo ratings yet

- GRAFCETDocument24 pagesGRAFCETPape BoyeNo ratings yet

- DM4 20Document4 pagesDM4 20Kahil LaibNo ratings yet

- Sequentiel LioDocument50 pagesSequentiel LioamourgloireNo ratings yet

- TP ElectroniqueDocument25 pagesTP ElectroniqueAymane NabihNo ratings yet

- Technique CDocument8 pagesTechnique CKarim FathiNo ratings yet

- Etld Mi s2 STRM 2015 2016 CorrigeDocument7 pagesEtld Mi s2 STRM 2015 2016 CorrigeRe Sab RinaNo ratings yet

- Formation Des ReleveursDocument101 pagesFormation Des ReleveurshaouachemNo ratings yet

- Cour Step7 PDFDocument60 pagesCour Step7 PDFAhmed Hamada80% (10)

- Convertisseurs TPeDocument6 pagesConvertisseurs TPeYassino WickNo ratings yet

- Eval4 11Document3 pagesEval4 11Hakim SaidiNo ratings yet

- TD 107 CanDocument1 pageTD 107 CanWalid FezzaniNo ratings yet

- TD M2R Machines À États Et ArchitecturesDocument10 pagesTD M2R Machines À États Et ArchitecturesLebongoNo ratings yet

- Chapitre 5Document34 pagesChapitre 5Yannick Stephane NouchiNo ratings yet

- Step 7courscopie2Document123 pagesStep 7courscopie2Mhadheb Med AmineNo ratings yet

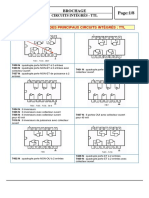

- Brochage Des Principaux CI-TTL PDFDocument8 pagesBrochage Des Principaux CI-TTL PDFFerjani Mohamed100% (1)

- Série D'exercices N°2 - Génie Électrique - Compteur À Base Des Circuits Intégrés - Bac Technique (2015-2016) MR Raouafi AbdallahDocument12 pagesSérie D'exercices N°2 - Génie Électrique - Compteur À Base Des Circuits Intégrés - Bac Technique (2015-2016) MR Raouafi Abdallahfehmi001100% (1)

- Api - PLC SK 2168Document68 pagesApi - PLC SK 2168akremibechirNo ratings yet

- PDF Compteur PDFDocument12 pagesPDF Compteur PDFThe geek CuestaNo ratings yet

- P05c Reg CPTDocument45 pagesP05c Reg CPTMohamed ZarboubiNo ratings yet

- Sherco Manuel 250 300 Sef-R 2017-Web PDFDocument188 pagesSherco Manuel 250 300 Sef-R 2017-Web PDFPier o.f.r.No ratings yet

- LabviewDocument19 pagesLabviewtortorouNo ratings yet

- Station Globale FINALEDocument180 pagesStation Globale FINALEAu DédéNo ratings yet

- Physique TP3 ProfDocument4 pagesPhysique TP3 Profmark jenkoNo ratings yet