Professional Documents

Culture Documents

Highly Integrated CMOS RF SPDT Switch With ESD and Unit Cell Optimisation in MCM

Uploaded by

Byron FischerCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Highly Integrated CMOS RF SPDT Switch With ESD and Unit Cell Optimisation in MCM

Uploaded by

Byron FischerCopyright:

Available Formats

Highly integrated CMOS RF SPDT switch

with ESD and unit cell optimisation in MCM

A.Y.-K. Chen

Presented is the performance of a highly integrated RF single-pole

double-throw (SPDT) switch fabricated in a 0.18 m bulk CMOS

process and housed in a low-cost laminated multi-chip module (MCM-

L) package. A switch controller is also implemented and consumes

40 A from a 3.4 V supply. The switch, based upon the 1.8 V thin-

oxide devices with resistive body-oating and unit cell layout optimis-

ation techniques, achieves an insertion loss of 0.52/0.78 dB at 0.9/2.45

GHz, respectively. TX-to-RX isolation of > 29 dB and return loss of

> 15 dB are achieved at these frequencies. The measured IP

1dB

of 21.7/

21.2 dBm and IIP

3

of 38.3/37.4 dBm are accomplished at 0.9/2.45

GHz, respectively. Finally, the switch achieves a RF electrostatic dis-

charge (ESD) rating of 4 kV for the 2 kV human body model and

500 V for the 200 V machine model.

Introduction: Low-cost silicon bulk CMOS technologies have been

used ubiquitously for decades for modern wireless communication

systems. However, the high power amplier (PA) and transmit/receive

(T/R) switch remain to be the two most critical front-end components

to be ultimately integrated to realise a true system-on-chip (SOC) for

wireless transceivers. Switches with reasonably low insertion loss

(IL), high isolation, linearity, and moderate to high power handling

capability that were once only possible in the III-V compound semicon-

ductors such as the GaAs pHEMT have emerged in silicon bulk CMOS

[16] and silicon- on-insulator (SOI) [7]. In this Letter, we present the

performance of an area-efcient CMOS RF single-pole double-throw

(SPDT) switch and consider the practical aspects of electrostatic dis-

charge (ESD) protection, integrated switch controllers, as well as lam-

inated packaging. Design techniques including resistive body-oating

and unit cell layout optimisation are demonstrated on the 1.8 V thin-

oxide triple-well devices.

Switch design: Illustrated in Fig. 1 are the SPDT switch and switch con-

troller. The switch consists of two series FETs (M1 and M2) and two

shunt FETs (M3 and M4). The width of the series devices (324 m)

is chosen to accommodate the IL performance over the frequency

range of interest (0.92.45 GHz). The shunt device is 1/4 the size of

the series devices to improve the isolation with a marginal penalty on

the IL. The high precision control voltages for the switch are internally

generated by an integrated switch controller, which is composed of a

bandgap reference, low dropout regulator (LDO), and digital logics.

The equivalent circuit of a triple-well FET with biasing for both ON-

and OFF-state is described in Fig. 2. During ON-state, V

SB

/V

DB

is set

to 0 V for best IL (no bulk effect) for a given V

G

. High value unsilicided

poly gate resistors (40 kH) are used to improve IL further and mitigate

the degradation in power handling capability at high input power [7].

The body-oating resistor (R

BF

= 25 k) is introduced to ensure that

the bulk terminal voltage swing is in accordance with the source/

drain. This also guarantees that the source/drain-to-bulk is reversed-

biased to achieve good linearity and avoid excessive capacitive coupling

to the substrate. A customised unit cell technique is applied towards the

device layout that improves IL by reducing the intrinsic distributed

series source/drain resistances and extrinsic source/drain interconnect

resistances, as illustrated in Fig. 3a. A 3 3 unit cell matrix layout

with source/drain sharing to minimise the parasitic capacitance is used

for the series switch devices, with nger width (W

f

) of 4 um and nine

ngers. During OFF-state, V

SB

/V

DB

is biased at 1 V (Fig. 2b) in

order to delay the onset of the junction diodes (C

SB

/C

DB

), thus improv-

ing the power handling capability. Consequently, the V

G

is 2.8 V for

ON-state and 0 V for OFF-state while the source and drain voltages

are biased at 1 V (compromise between turn-on of V

GD

/V

GS

and gate

oxide breakdown for the OFF devices). The V

nwell

is biased at the

highest potential available (3.4 V) to keep C

pwellnwell

and C

nwellpsub

reversed-biased while improving the compression characteristics at

high power levels. RF ESD protection is also implemented at the Ant

port which is typically exposed and most likely to encounter an ESD

event. The reliability issue for a switch design is more susceptible to

time-dependent dielectric breakdown (TDDB) which is a strong func-

tion of the electric eld across the gate dielectric. The diode size and

number of diode stacks are trade-offs among the gate oxide reliability,

IL due to the diode parasitic capacitance and series resistance, and

linearity. In this design, the number of series diode stacks connected

anti-parallel to ground is four. The degradation in the IL due to the

additional ESD diodes is 0.07 and 0.1 dB in simulation at 0.9

and 2.45 GHz, respectively. The core switch area is only 0.02 mm

2

while the effective area for the switch controller is 0.04 mm

2

, as

shown in Fig. 3b.

V

DD

= 3.4 V

V

D

V

D

R

G

R

G

R

G

R

G R

Bias

R

Bias

ESD

RX TX

Ant

(15 p)

(40 k)

Vbg

Iref LDO

EN

+

+

VG_TX

Vpwell_TX

Vpwell_RX

VG_RX

EN

1 V 2.8 V

bandgap

TX_EN

RX_EN

logic and level shifters

(25 k)

(324/0.18)

(0.3 p)

SPDT switch switch controller

(324/0.18)

(90/0.18) (90/0.18)

R

Bias

R

Bias

M2

M4

M1

M3

R

Bias

V

G

C

C

C

B

V

S

V

S

V

G

V

G

C

B

V

S

V

G

Fig. 1 Simplied block diagram of switch controller and SPDT

R

G

C

GS

C

GS

C

GD

C

GD

C

DB

C

DB

C

SB

C

SB

R

Bias

R

sub

R

sub

R

nwell

R

nwell

R

BF

R

BF

(2.5 k) (2.5 k)

(25 k) (25 k)

C

pwell-nwell

C

nwell-psub

C

pwell-nwell

C

nwell-psub

V

nwell

V

nwell

V

pwell

V

pwell

R

Bias

R

Bias

R

Bias

R

on

R

off

C

off

bulk bulk

S D

(1 V)

(1 V) (0 V)

(0 V)

(1 V)

(3.4 V) (3.4 V)

(1 V)

(2.8 V)

(1 V)

D S

V

G

R

G

V

G

a b

Fig. 2 Equivalent circuit model of triple-well FET with biasing scheme

a ON-state

b OFF-state

pwell contact

nwell contact

bandgap

LDO

VDD TX Ant RX

SPDT

C

C

C

B

C

B

source

gate

drain

Fig. 3 Customised unit cell layout and chip microphotograph

a 3 3 unit cell matrix layout of series switch device

b Chip microphotograph of SPDT and switch controller breakout

Experimental results: The characterisation of the multi-chip module

(MCM)-packaged switch was mounted on an evaluation board as

shown in Fig. 4. Due to the symmetrical packaged switch design, the

measurement data for the TX-to-Ant path and the Ant-to-RX path are

nearly identical. Between 900 MHz and 3 GHz, the switch achieves a

return loss (RL) > 15 dB at both the TX port and the Ant port, from

20 to 85 C (Fig. 5a). The measured IL at 25 C is 0.52 and 0.78

dB at 0.9 and 2.45 GHz, respectively. Under the worst-case temperature

(85 C), the measured IL (Fig. 5b) is 0.59 and 0.89 dB at 0.9 and 2.45

GHz, respectively. This increase in IL at the hot condition is mainly

attributed to the mobility degradation of the FET device in strong inver-

sion. The loss associated with the package is 0.05 and 0.14 dB at 0.9

and 2.45 GHz, respectively. The isolation from TX to RX (TX mode)

illustrated in Fig. 5c is > 31 dB while that from Ant to TX (RX

mode) is > 22 dB at 2.45 GHz (85 C). Depicted in Fig. 5d, the

measured IP

1dB

is 21.7 and 21.2 dBm at 0.9 and 2.45 GHz, respectively.

The measured IIP3 (two-tone spacing of 1 MHz) is 38.3 and 37.4 dBm

at 0.9 and 2.45 GHz, respectively. The switch controller draws an

overall current of 40 A from a 3.4 V supply. Finally, the RF ESD

test was demonstrated using a handheld mini-zapper (KeyTek

TPC-2A) with both human body model (HBM) and machine model

(MM) inserts. The switch has successfully achieved a RF ESD rating

of > 4 kV and > 500 V for the target 2 kV HBM and 200 V

MM, respectively. Table 1 summarises the performance of prior

published CMOS RF SPDT switches.

ELECTRONICS LETTERS 11th April 2013 Vol. 49 No. 8

moulding compound

L1

L2

L3

PCB

Au bondwire

die attach adhesive

multilayer laminate

solder

Fig. 4 Packaged switch mounted on PCB

25

20

T

X

p

o

r

t

r

e

t

u

r

n

l

o

s

s

,

d

B

T

X

-

R

X

i

s

o

l

a

t

i

o

n

,

d

B

A

n

t

-

T

X

i

s

o

l

a

t

i

o

n

,

d

B

P

o

u

t

,

d

B

m

i

n

s

e

r

t

i

o

n

l

o

s

s

,

d

B

A

n

t

p

o

r

t

r

e

t

u

r

n

l

o

s

s

,

d

B

15

25 C

25 C

85 C

-25 C

25 C

85 C

-25 C

25 C

85 C

10

25

20

15

10

5

1.5

1.0

0.5

0

0.5 1.0 1.5

frequency, GHz

frequency, GHz

Pin, dBm

fundamental

IIP

3

= 37.4 dBm

IP

1dB

= 21.2 dBm

IM3

2.0 2.5 3.0 0.5 1.0 1.5

frequency, GHz

2.0 2.5 3.0

25

30

35

40

20

25

30

35

60

60

80

40

40

20

20

0

0 0.5 1.0 1.5 2.0 2.5 3.0 5 10 15 20 25 30 35 40 45

Fig. 5 Measured RL, IL, and isolation at different temperatures and linearity

characteristic of SPDT switch

a TX port RL and Ant port RL

b IL

c Isolation

d IP

1dB

and IIP

3

at 2.45 GHz

Table 1: Performance of prior published CMOS RF SPDT switches

Ref. Process Technique

Frequency

(GHz)

IL

(dB)

IPIdB

(dBm)

IIP3

(dBm)

Package

This

work

1,2

0.18

m

CMOS

Resistive

body-oating

0.9

2.45

0.52

0.78

21.7

21.2

38.3

37.4

MCM

[1]

0.5 m

CMOS

Low Rsub 0.9 0.73 18.9 38.2 SOIC

[2]

0.18

m

CMOS

Impedance

transformation

0.9

2.4

0.97

1.1

26.3

22.7

37.7

29.8

SOIC

[4]

3

0.18

m

CMOS

LC substrate

biasing

2.4

TX:

1.5

RX:

1.6

28.5 NA

On-

wafer

[5]

0.18

m

CMOS

Resistive

body-oating

2.4 0.7 21.3 30.3

On-

wafer

[6]

0.13

m

CMOS

Body-oating

and

feed-forward

caps

0.9

TX:

0.5

RX:

1.0

31.3 42

On-

wafer

1

Denotes SPDT switch with measured HBM (4 kV) and MM (500 V) ESD ratings

2

Denotes SPDT switch with integrated switch control

3

Denotes SPDT switch with measured HBM (4 kV) ESD rating

Conclusion: This Letter describes a highly integrated yet area-efcient

CMOS RF SPDT switch. The switch achieves an IL of 0.52/0.78 dB and

IP

1dB

of 21.7/21.2 dBm at 0.9/2.45 GHz while satisfying the target RF

ESD rating of 2 kV HBM and 200 V MM. To the best of the

authors knowledge, this packaged CMOS switch has achieved the

highest level of integration including the switch control and RF ESD

protection among all reported to date.

The Institution of Engineering and Technology 2013

4 October 2012

doi: 10.1049/el.2012.3387

One or more of the Figures in this Letter are available in colour online.

A.Y.-K. Chen (Skyworks Solutions, Newbury Park, CA, USA)

E-mail: austin.chen@;skyworksinc.com

A.Y.-K. Chen: Was also with the Department of ECE, University of

Florida, Gainesville, FL USA, and Alcatel-Lucent, Bell Laboratories,

Murray Hill, NJ, USA

References

1 Huang, F.-J., and O, K.K.: A 0.5-m CMOS T/R switch for 900-MHz

wireless applications, IEEE J. Solid-State Circuits, 2001, (36), (3), pp.

486492

2 Huang, F.-J., and O, K.K.: Single-pole double-throw CMOS switches

for 900-MHz and 2.4-GHz applications on P-silicon substrates, IEEE

J. Solid-State Circuits, 2004, (39), (1), pp. 3541

3 Li, Z., Huang, F.-J., and O, K.K.: 5.8-GHz CMOS T/R switches with

high and low substrate resistance in a 0.18-m CMOS process, IEEE

Microw. Wirel. Compon. Lett., 2003, 13, (1), pp. 13

4 Talwalkar, N., Wong, N., Yue, C.P., Guan, H., and S..: Integrated

CMOS transmit-receive switch using LC-tuned substrate bias for 2.4

GHz and 5.2 GHz applications, IEEE J. Solid-State Circuits, 2004,

39, (6), pp. 863870

5 Yeh, M.-C., Tsai, Z.-M., Liu, R.-C., Lin, K.-Y., Chang, Y.-T., and Wang,

H.: Design and analysis for a miniature CMOS SPDT switch using

body-oating technique to improve power performance, IEEE Trans.

Microw. Theory Tech., 2006, 54, (1), pp. 3139

6 Xu, H., and and O., K.K.: A 31.3-dBm bulk CMOS T/R switch using

stacked transistors with sub-design-rule channel length in oated

p-wells, IEEE J. Solid-State Circuits, 2007, 42, (11), pp. 577584

7 Tinella, C., Fournier, J.M., Belot, D., and Knopik, V.: A high- perform-

ance CMOS-SOI antenna switch for the 2.55GHz band, IEEE

J. Solid-State Circuits, 2003, 38, (7), pp. 12791283

ELECTRONICS LETTERS 11th April 2013 Vol. 49 No. 8

You might also like

- Hikvision ISAPI Core Protocol PDFDocument795 pagesHikvision ISAPI Core Protocol PDFByron Fischer0% (1)

- Internet of Things: The Dzone Guide To TheDocument31 pagesInternet of Things: The Dzone Guide To TheramboriNo ratings yet

- Latest Activation Bonus UpdatedDocument3 pagesLatest Activation Bonus UpdatedByron FischerNo ratings yet

- HW 1 UpDocument6 pagesHW 1 UpByron FischerNo ratings yet

- Antenna Research Centre Faculty of Electrical Engineering Universiti Teknologi MARADocument65 pagesAntenna Research Centre Faculty of Electrical Engineering Universiti Teknologi MARAByron FischerNo ratings yet

- Office 365 for Education allows free collaborationDocument1 pageOffice 365 for Education allows free collaborationZhafri SyazwiNo ratings yet

- School of Engineering: Mid-Term ExaminationDocument3 pagesSchool of Engineering: Mid-Term ExaminationByron FischerNo ratings yet

- Event Report For Tableau Experience Malaysia 280818Document3 pagesEvent Report For Tableau Experience Malaysia 280818Byron FischerNo ratings yet

- Course Outline March18-July18Document4 pagesCourse Outline March18-July18Byron FischerNo ratings yet

- Tutorial 2Document1 pageTutorial 2Byron FischerNo ratings yet

- Assignment #1 AntennaDocument12 pagesAssignment #1 AntennaByron FischerNo ratings yet

- Raspberry Pi EnclosureDocument1 pageRaspberry Pi EnclosureByron FischerNo ratings yet

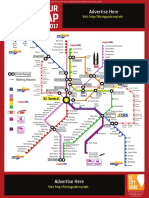

- Kuala Lumpur Train Map July 2017Document1 pageKuala Lumpur Train Map July 2017Mustafidzul MustaphaNo ratings yet

- FiltersDocument8 pagesFiltersByron FischerNo ratings yet

- Office 365 for Education allows free collaborationDocument1 pageOffice 365 for Education allows free collaborationZhafri SyazwiNo ratings yet

- Introducing The Raspberry Pi ZeroDocument48 pagesIntroducing The Raspberry Pi ZeroByron FischerNo ratings yet

- Brief History Computers From Abacus Present DayDocument38 pagesBrief History Computers From Abacus Present DayIan D ValdeztamonNo ratings yet

- Raspberry Pi 3Document1 pageRaspberry Pi 33fzvthNo ratings yet

- Introducing The Raspberry Pi ZeroDocument48 pagesIntroducing The Raspberry Pi ZeroByron FischerNo ratings yet

- IIUM Template TestDocument3 pagesIIUM Template TestByron FischerNo ratings yet

- Introduction To Programmable Logic Controllers (PLC'S) : Industrial Control Systems Fall 2006Document47 pagesIntroduction To Programmable Logic Controllers (PLC'S) : Industrial Control Systems Fall 2006Hamidreza MoaddeliNo ratings yet

- Presentation OFDM ECM740Document21 pagesPresentation OFDM ECM740Byron FischerNo ratings yet

- Electrical Technology 1 Assignment 2 - Capacitor & Inductor CalculationsDocument3 pagesElectrical Technology 1 Assignment 2 - Capacitor & Inductor CalculationsByron FischerNo ratings yet

- Jan-May 2016 PLC Midterm ExamDocument2 pagesJan-May 2016 PLC Midterm ExamByron FischerNo ratings yet

- Logic Symbols, Truth Tables, and Equivalent PLC Ladder DiagramsDocument2 pagesLogic Symbols, Truth Tables, and Equivalent PLC Ladder DiagramsSteve LisleNo ratings yet

- LaddersDocument15 pagesLaddersDhaval PatelNo ratings yet

- Assignment 1 PLC 2015Document2 pagesAssignment 1 PLC 2015Byron FischerNo ratings yet

- Ladder and Functional Block ProgrammingDocument1 pageLadder and Functional Block ProgrammingByron FischerNo ratings yet

- High-Gain Fully Printed Organic Complementary Circuits On Flexible Plastic Foils PDFDocument7 pagesHigh-Gain Fully Printed Organic Complementary Circuits On Flexible Plastic Foils PDFByron FischerNo ratings yet

- 06650081Document8 pages06650081Byron FischerNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5783)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Discourse on Colonialism and CivilizationDocument48 pagesDiscourse on Colonialism and CivilizationEmir özerNo ratings yet

- AREADocument10 pagesAREAhaipm1979No ratings yet

- Technical Manual: Package Air Conditioner Rooftop - Cooling Only (50Hz)Document56 pagesTechnical Manual: Package Air Conditioner Rooftop - Cooling Only (50Hz)Im Chinith100% (1)

- Operation Manual: Impedance Audiometer AT235hDocument102 pagesOperation Manual: Impedance Audiometer AT235hmendezoswaldoNo ratings yet

- This Demonstration Covers The Usage of V-Ray Render Elements in Adobe PhotoshopDocument15 pagesThis Demonstration Covers The Usage of V-Ray Render Elements in Adobe PhotoshopBartek BanterNo ratings yet

- Oral Hygiene: Presented By: Anis Anis Andreas KyriakidisDocument60 pagesOral Hygiene: Presented By: Anis Anis Andreas Kyriakidislenami_91No ratings yet

- Doctors Appointment - 4!14!17 Acid RefluxDocument11 pagesDoctors Appointment - 4!14!17 Acid RefluxRay Edwin Anderson IIINo ratings yet

- Chips Unlimited Blend LibraryDocument20 pagesChips Unlimited Blend Librarymizan sallehNo ratings yet

- Chemistry PropertiesDocument14 pagesChemistry PropertiesconchoNo ratings yet

- Barrett Firearms - REC10 - Operators Manual 8.5x5.5 ALL REVB 17278Document22 pagesBarrett Firearms - REC10 - Operators Manual 8.5x5.5 ALL REVB 17278Ricardo C TorresNo ratings yet

- 02 - AFT - Know Your Pump & System Curves - Part 2ADocument8 pages02 - AFT - Know Your Pump & System Curves - Part 2AAlfonso José García LagunaNo ratings yet

- A Project Report On: "Recreation Club"Document80 pagesA Project Report On: "Recreation Club"Appz100% (2)

- SmogDocument5 pagesSmogAlain MoratallaNo ratings yet

- Assignment IDocument2 pagesAssignment Ivaishnavi priyaNo ratings yet

- MSE Admission and Degree RequirementsDocument6 pagesMSE Admission and Degree Requirementsdeathbuddy_87No ratings yet

- Naval Noise Psycho-Acoustic Backpropagation NNDocument12 pagesNaval Noise Psycho-Acoustic Backpropagation NNSilvia FlorentinaNo ratings yet

- CH 01Document24 pagesCH 01Gabriel FlorêncioNo ratings yet

- D-Glucitol (420i) Dextrose MonohydrateDocument3 pagesD-Glucitol (420i) Dextrose MonohydrateSilvia Melendez HNo ratings yet

- Safety Data Sheet Permatreat® Pc-191T: Section: 1. Product and Company IdentificationDocument9 pagesSafety Data Sheet Permatreat® Pc-191T: Section: 1. Product and Company IdentificationMajd DraidiNo ratings yet

- CP I-O Modules PDFDocument91 pagesCP I-O Modules PDFVlad ChioreanNo ratings yet

- Sony Ericsson K610i, K610m, and V630i Service ManualDocument53 pagesSony Ericsson K610i, K610m, and V630i Service ManualJane TodoroskiNo ratings yet

- D5293Document8 pagesD5293Carlos Olivares ZegarraNo ratings yet

- June 2023 BillingDocument10 pagesJune 2023 BillingEsther AkpanNo ratings yet

- Tabel Benkelman Beam Baru - AsisDocument21 pagesTabel Benkelman Beam Baru - AsisAsisNo ratings yet

- Techint Group Brochure 2013Document100 pagesTechint Group Brochure 2013MD AFROZ RAZANo ratings yet

- X Wing - Quick.referenceDocument6 pagesX Wing - Quick.referenceatilaT0RNo ratings yet

- HTP 12 SkodaDocument3 pagesHTP 12 SkodamihnutzuNo ratings yet

- TATA Gluco PDFDocument5 pagesTATA Gluco PDFsidharth dasNo ratings yet

- Environmental Design BasisDocument31 pagesEnvironmental Design BasisNBTC Tubes & PipesNo ratings yet