Professional Documents

Culture Documents

ManArray PDF

Uploaded by

Jessica ThompsonOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ManArray PDF

Uploaded by

Jessica ThompsonCopyright:

Available Formats

The ManArray Embedded Processor Architecture

Gerald G. Pechanek

1

and Stamatis Vassiliadis

2

1

Billions of Operations Per Second, (BOPS) Inc.,

Chapel Hill, NC, USA gpechanek@bops.com

2

Delft University of Technology, Department of Electrical Engineering

Delft, The Netherlands stamatis@einstein.et.tudelft.nl

Abstract. The BOPS ManArray architecture is presented as a coprocessor platform for the

embedded processor domain, consisting of scalable design points. As an array processor, a

single architecture definition and tool set supports multiple configurations of processing

elements (PEs) from low end single PE to large arrays of PEs. The ManArray selectable

parallelism architecture mixes control-oriented operations, practical VLIW, packed data,

and distributed array processing in a cohesive independently selectable manner. In addition,

scalable conditional execution and single cycle communications across a high connectivity

low cost network are integrated in the architecture allowing another level of selectivity that

enhances the application of the parallel resources to providing high performance algorithms.

Coupled with the array coprocessor is a scalable DMA engine that runs in the background

and provides programmer selectable data distribution patterns and a high bandwidth data

streaming interface to system peripherals and global memory. This paper introduces the

embedded scalable ManArray architecture and selectable parallelism. A number of

benchmarks are presented demonstrating the capability of this new architecture. For

example, a 2x2 ManArray can process a distributed 256 point complex FFT in 425 cycles

and a 8x8 2D IDCT in 34 cycles that meets IEEE standards.

1 Introduction

As chip densities continue to improve, demand increases for the low cost integration of high

performance parallel processing systems. For example audio, video, and communication signal

processing are but three areas requiring very high performance that are in demand for low cost consumer

products. For such application domains a number of proposals exist that intend to improve the over all

execution of specialized software. The proposed architectures can be divided in the following three main

categories: Specialized, specialized augmented, and general-purpose. A general discussion regarding

those classes follows:

Specialized processors: In this class of processors a specific standard such as MPEG-2 may be

assumed, and for such a standard a processor is designed that uniquely performs this standards

requirements. There are several processors available that assume this approach. Examples of such

processors are for example MPEG-2 Decoders.[1,2]. Additionally, a standard may not be assumed. These

processors are targeted to a specific application domain, such as video-recorders and television sets. The

programmability of these processors is limited, in that way they can only perform a predefined set of

operations. Typical operations executed by these processors are image enhancement, picture-in-picture

and on-screen-display. Examples of these processors can be found in [3,4] and [5].

Specialized augmented processors: In this class of processors, programmability is assumed and

no restrictions to standards are imposed. That is, the processing follows the usual general purpose

paradigm of programmability and the instructions set definition. These C-programmable processors are

general program processors with extensions that make them particularly suited for media processing. For

the Philips Trimmedia architecture and processors [6] these are fine-grain extensions to the VLIW

processor as well as coarse-grain coprocessors for e.g. VLD decoding. Another example of this class of

processors is the Texas Instruments Multimedia Video Processor (MVP) [7].

General-purpose processors: The family of general purpose machines is extended with co-

processing capabilities to improve the performance of multimedia applications. This approach follows

the traditional extension oriented processing. That is, a general-purpose processor is extended with new

architectural features in order to improve a certain application domain, which allows the design of

coprocessors specialized for the considered application. Examples of such extensions include the floating

point and vector extension of general purpose computing. Examples of this type of extensions with

respect to multimedia include:

Intel MMX (Multi Media eXtensions) [8],

ALPHA MVI (Motion Video Instruction extensions) [9],

Sun VIS (Visual Instruction Set) [10] and

MIPS DME (Digital Media Extensions) [11].

Our goal is to describe a scalable family of programmable coprocessors based upon an

architectural definition for application specific processors containing features of all these categories.

The proposed processor family provides three basic levels of parallelism namely indirect VLIW(iVLIW),

packed-data, and multi-processing. This paper introduces the ManArray processor platform as a strong

contender to be a ubiquitous, high-volume signal processor in commercial applications. The presentation

is as follows: The embedded ManArray processor architecture is presented in section 2. Consequently,

we describe a ManArray processor design point and present some benchmark performance evaluations.

We conclude the presentation with some final remarks.

2 The Embedded ManArray Processor Architecture

The ManArray architcture consists of a control sequence processor (SP) and an array of processing

elements (PEs) that use a distributed register file model with simple instructions defining operations on

local register operands. All arithmetic and load/store instructions execute in one or two cycles with no

hardware interlocks. Further, all arithmetic and load/store instructions can be combined in VLIW format

that can be indirectly selected for execution from small distributed VLIW memories. Parallel array or

sequential execution is controlled by a dedicated bit in all instruction formats that specifies whether an

instruction is an SP or a PE instruction. In addition, the instruction set is partitioned into four equal

groups using the high two bits of the instruction format; a control group, an arithmetic group, a load/store

group, and a reserved proprietary instruction group, Fig. 1. Control and branch instructions are e xecuted

by the Sequence Processor which can also indirectly execute local VLIWs. To minimize the effects of

branch latencies an extensive scalable conditional execution approach is also defined in the instruction

set format. To optimize the use of the distributed register files the ManArray network [12] is integrated

into the architecture providing single cycle data transfers between orthogonal clusters of PEs. The

communication instructions can also be included into VLIWs thereby overlapping communications with

computation operations effectively rendering the communications latency to zero. The ManArray

network operation is independent of background DMA operations which provide a data streaming path

between peripherals, such as a global memory

Specifically, the ManArray architecture reserves over a quarter of the i nstruction set space for

future definition by partitioning the instruction set format into four groups. Any of the four groups of

instructions can be dynamically mixed on a cycle-by-cycle basis. An additional bit is dedicated to

differentiating between SP and PE type instructions. The single ManArray instruction set architecture

supports the entire ManArray family of cores from the single PE core (the 1x1) to any of the highly

parallel multi-processor arrays (1x2, 2x2, 2x4, 4x4, etc..). The ManArray instruction set summary, Fig.

2, shows 32-bit simplex instructions in groupings that represents the five execution unit slots of the first

ManArray implementation plus a control group. The execution units include an arithmetic logic unit

(ALU), a multiply accumulate unit (MAU), a data select unit (DSU), a load unit, and a store unit.

Each PE and the array controller SP contain an iVLIW Instruction Memory (VIM) and each

addressable location in the VIM consists of five simplex instructions slots (one per execution unit) Fig. 3.

Using the Load iVLIW instruction (LV), the programmer or compiler loads individual instruction slots

with the 32-bit simplex instructions optimized for the algorithm. A single 32-bit Execute iVLIW

instruction (XV) triggers the execution of an iVLIW at a specific VIM address in the SP or in all PEs.

Instructions in the five slots execute in parallel, each within its respective execution unit. Consequently,

the VIM contains application-specific iVLIW s optimized for the task being executed and can be easily

changed on a task by task basis.

Figure 1 ManArray Instruction Groupings

Figure 2 ManArray Instruction Set Summary

Parallel Decode & Execute

Control

iVLIWMemory (VIM)

Instruction Opcode

Memory

Switch

Local PE

Memory

32x32/16/64

Register File

Ex1

64-bit

Data Buses

Ex1 Ex2

Ex3

32-bits

Instruction bus

iVLIW

bypass for

Simplex SIMD

operations

To/From

Cluster

Switch

Ex3 Ex4 Ex5

Ex4 Ex5

Ex2

Figure 3 indirect VLIW Architecture in the Spand each PE

Instruction Types

A, B,C

0 1

1 0

1 1

S

P

Proprietary Instructions

0 0

30-bits

32-bit ManArray Groupings

00 Pluggable Proprietary

Instruction Set

01 Flow Control

10 Load/Store

11 Arithmetic/Logical

Next two variations of a PE communication instruction and a Multiply Complex instruction are reviewed.

In Fig. 4 a PE exchange instruction is shown (PEXCHG Rt, Rs, Transpose). In the figure a 2x4 cluster

switch is shown and a symbolic depiction of the operation shown in the upper left hand corner. For the

transpose operation on a 2x2 with row-major PE ordering as shown, a transfer of data between PEs 1 and

2 is to occur. This is a single cycle DSU operation which can be specified in an iVLIW and uses the

receive model of communications. In the receive model each PE makes a specified source operand

available to its output port and provides the proper control signals to its path control portion of the cluster

switch. In the example shown, PE 1 provides Rs1 to its output port and PE2 provides Rs2 to its output

port. PE 1 receives the Rs2 value through its cluster switch multiplexors and PE 2 receives Rs1. The

received values are loaded into the specified target register in each PE.

Figure 4 Single Cycle Data Transfers Between PEs

In Fig. 5, a PE exchange (PEXCHG Rt, Rs, 2x4PE6) operation is shown on a 2x4 demonstrating

the broadcast capability of the ManArray network and receive model of communications used. The

symbolic depiction in the upper left hand corner shows that PE6 is the source of the data to be broadcast

to all active PEs in the 2x4. This single cycle DSU operation can also be specified in a iVLIW. In this

case PE6 makes its source operand available and each of the other active PEs in the array specify the

proper path control to receive PE6s data. This is a cross cluster broadcast of data to all PEs in the 2x4

array. It should be noted that all intercluster paths are primarily "point-to-point" supporting the high

performance interface.

Figure 5 PE Broadcast Between PEs

PE-#2 PE-#3

PE-#1

H

C

H

C

PE-#0

H

C

H

C

In

In In

In

Out

Out

Out

Out

Ctrl Ctrl

Ctrl Ctrl

Cluster Switch

0

3

2

1

0

3

2

1

0

3

2

1

0

3

2

1

R

T1

R

T0

R

T3

R

T2

R

S1

R

S3

R

S0

R

S2

PEXCHG R

target

, R

source

Transpose

TRANSPOSE

0

0,0

1

0,1

2

1,0

3

1,1

H H H

C C C C

PE0 PE4 PE1 PE5

C C

4

5

6

7

C

4

5

6

7

C PE2

PE6 PE3 PE7

H H H H

out

4

5

6

7

4

5

6

7

H

0

0,0

5

1,1

4

1,0

1

0,1

2

0,3

7

1,2

6

1,3

3

0,2

PEXCHG R

target

, R

source

, 2x4PE

Fig. 6 depicts the pipelined operation sequence for a Multiply Complex Instruction. For

ManArray high performance PEs the Multiply Complex provides superior performance support for

algorithms requiring complex multiply operations. Complex numbers are stored in two halfwords where

H1 represents the real component and H0 the imaginary component. The complex result returned contains

the real part in H1 and the imaginary part in H0. This is a two cycle operation with rounding occurring in

the second cycle. By pipelining, 2 cycles latency and single-cycle throughput are achieved.

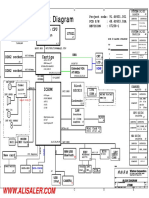

3 ManArray Core Processors

Generally speaking, ManArray combines PEs in clusters that also contain a Sequence Processor

(SP), uniquely merged into the PE array, and a cluster-switch, interconnecting the PEs. Fig. 7 shows the

BOPS 2040 [13] 2x2 cluster processor core (without DMA) described further in this section and for which

benchmarks are provided. The SP provides program control, contains the instruction and data address

generation units, and controls the dispatch of instructions to the processor array. Merging the SP with a

PE provides a low cost 1x1 building block for other array configurations. For example, a 2x4 is built

from two 2x2 clusters each with their own SP thereby allowing the 2x4 to be configured as two 2x2s or a

single 2x4 depending upon an applications needs. In addition, merging the controller SP into the array

allows the SP access to the PE-to-PE interconnection network and consequently easy access to each PEs

internal resources. A rich set of addressing modes are provided in the SP and each PE. In addition, high

performance interrupts, and unique event point looping are provided.

A 64-entry register space is used by the SP and PEs, and it is configured as a 32x32

Reconfigurable Compute Register File (RCRF), 8x32 Address Register File (ARF), and 24x32

Miscellaneous Registers (MRF). For the ManArray processor, the address registers are separated from the

compute register file. This approach maximizes the number of registers available for compute operations

and guarantees a minimum number of dedicated address registers. This approach does not require any

additional address generation ports from the compute register file, and it allows independent PE memory

addressing for such functions as local data dependent table lookups. The RCRF is configurable to support

both 32-bit data types including quad byte, dual halfword, and word, and 64-bit data types including octal

byte, quad halfword, dual word, and double word. The balanced architectural approach taken for the

compute register file provides the high performance features needed by many applications. It supports

octal byte and quad halfword operations in a logical 16x64-bit register file space without sacrificing the

32-bit data type support in the logical 32x32-bit register file. Providing both allows optimum usage of

register file space and minimum overhead in manipulating packed data items. By adding PEs, the packed

data support grows such that a 1x2 effectively provides 128-bit packed data support, a 2x2 256-bit packed

data support, etc. growing the level of parallelism needed by appropriate choice of the selected core.

Each PE, Fig. 7, contains five execution units, identified in the instruction set groupings of Fig.

2, each supporting various 8/16/32/64-bit packed-data types, a 32x32-bit reconfigurable compute

register file, a VLIW-Instruction-Memory unit (VIM), and local data memory. The DSU supports shifts,

rotates, and single-cycle PE-to-PE communications across the ManArray network. With the indirect

VLIW (iVLIW) architecture, the communications operations can be overlapped with the compute

operations, thereby providing zero-latency data transfers between PEs. The 32x32-bit reconfigurable

register file is multi-ported allowing the parallel iVLIW execution. The load and store units provide

independent data paths between the local memory in each PE in the array. The local PE data memory is a

two port memory configured into two 32-bit banks, that support byte, halfword, word, and double word

loads. With the twin banks one memory can be loading and storing data simultaneously to/from the PEs

register file while the DMA unit is loading/storing to/from the other bank . This effectively hides DMA

delays and supports a data streaming approach to processing on the array. This allows very high memory

bandwidth support for compute-intensive algorithms.

6

x

R

x

I

y

R

y

I

x

R

* y

I

*

+

*

-

x

R

* y

R

Rx :

x

I

* y

R

x

I

* y

I

* *

x

R

* y

R

- x

I

* y

I

x

R

* y

I

+ x

I

* y

R

t

R

t

I

Rt :

: Ry

H1 H1

Fig. 6 Multiply Complex Instruction Pipeline

The VIM can contain an unlimited number of iVLIWs, though typical products for video

compression, graphics, signal processing, or communications will typically require no more than 64

iVLIWs. Local PE data memory is not limited by the architecture but is also sized according to the

intended applications.

Conditional execution, also referred to as predicated execution, allows the programmer to have a

given instruction execute or not, based upon the machine state generated previously. This feature

improves performance by avoiding the use of branches that incur a branch delay penalty on pipelined

processors. ManArray extends the concept of conditional execution to an array of processing elements by

specifying the type of conditional execute action desired in a hierarchical manner, with a 1-bit, 2-bit, and

3-bit specifier depending upon the instruction type. In addition, ManArray supports conditional execution

within the iVLIWs. The ManArray PE independent conditional execution architecture provides a

comprehensive level of data-dependent parallelism that none of the currently known and available SIMD

machines provide. The standard conditional branch capability is also provided in the SP, as well as SP

local data dependent conditional execution in all its arithmetic operations. Initially, four basic types of

SP Instruction Memory

SP Data Memory

Cluster

Switch

32x32/16x64

8 R/4 W

SP RCRF

8x32 6 R/4 W SP ARF

Local PE

Memory

LMIU Inst.Reg

VIM

Store

Load

ALU

MAU

DSU

SP/PE 0

Instruction Fetch

Unit (PC, Branch,

Loop, Interrupt,

Memory Controls)

32x32/16x64

8 R/4 W

SP RCRF

8x32 6 R/4 W SP ARF

Local PE

Memory

LMIU

VIM

Store

Load

ALU

MAU

DSU

32x32/16x64

8 R/4 W

SP RCRF

8x32 6 R/4 W SP ARF

Inst.Reg

PE 2

Local PE

Memory

LMIU

VIM

Store

Load

ALU

MAU

DSU

32x32/16x64

8 R/4 W

SP RCRF

8x32 6 R/4 W SP ARF

Inst.Reg

PE 3

Local PE

Memory

LMIU

VIM

Store

Load

ALU

MAU

DSU

32x32/16x64

8 R/4 W

SP RCRF

8x32 6 R/4 W SP ARF

Inst.Reg

PE 1

Figure 6 2x2 ManArray Processor Core

7

operations are supported in ManArray cores, namely unconditional execution, execute on true condition,

execute on false condition, and specialized conditional execution actions specified on an instruction basis.

4 Benchmarks

The ManArray architecture contains application specific instructions for video, graphics,

communications, and generalized DSP applications. The first silicon is a 2x2 core that includes both

fixed and floating point ALU, MAU, and DSU and all the architectural features discussed in this paper

for use on an evaluation board. Subset of the architecture can be prepared to optimize a core for a

specific task if it is seen as necessary. Consequently, BOPS is developing application libraries of

algorithms for use by product developers. Many of these are reported in the BOPS web site [14]. Two

example algorithms are briefly discussed next.

In this first algorithm, discussed in detail in [15], an 8x8 2 dimensional inverse discrete cosine

transform (8x8 2D IDCT) is executed on the BOPS 2040 core in 34-cycles meeting the IEEE standard

1180-1990. The algorithm is developed from the 2D 8x8 IDCT algorithm by separating it into 1D 1x8

IDCTs on all eight rows and then on all eight columns. The 8x8 data is distributed among the four PEs

according to the 1x8 IDCT signal flow graph. The strategy for processing the IDCT algorithm makes use

of a number of features of the ManArray processor to provide a unique software pipeline usi ng indirect

VLIWs operating in multiple PEs. For example, the indirect execute VLIW XV instruction, with the

unique enable feature, allows a software pipeline to be built up and torn down without creating new

VLIWs. Quad 16x16 multiplications are used on each PE in the Sum of Two Products with and without

accumulate instructions to produce two 32-bit results on each PE. The use of common instructions that

can execute in either the ALU or MAU or both, for example the butterfly with saturate instruction

improves performance. In addition, the DSU supports permute instructions to aid in organizing the data

prior to processing and PEXCHG instructions for communicating between PEs. Tests on the 34-cycle

algorithm verified that the 2D 8x8 IDCT meets the IEEE standard 1180-1990 for precision of the IDCT.

In this next algorithm, discussed in detail in [16], a 256 point complex FFT is executed on the

BOPS 2040 core in 425-cycles. Our implementation utilizes the multiple levels of parallelism that are

available on the ManArray such as the special multiply complex instruction, that calculates the product

of two complex 32-bit fixed point numbers in 2-cycles pipelineable. Instruction level parallelism is

exploited via the indirect VLIW. With the iVLIW, in the same cycle a complex number is read from

memory, another complex number is written to memory, a complex multiplication starts and another

finishes, two complex additions or subtractions are done, and a complex number is exchanged with

another processing element. Both PE local FFTs and distributed FFTs are executed in this algorithm

which is described by use of Kronecker product mathematics. Not only are the total cycles for the

calculation of the 256 point complex FFT very small but the program code is also very compact.

5 Conclusions

Using the ManArray network, BOPS has implemented an advanced, scalable family of DSP

cores for emerging applications such as broadband communications, digital video, digital audio, imaging,

and graphics. The BOPS ManArray (Hardware, Software, and Programming Environment [17]) is the

result of a thorough examination of DSP requirements. The ManArray provides three basic levels of

parallelism (indirectVLIW, packed-data, and multi-processing), all independent of each other and

available to the compiler or programmer on an as-needed basis. These features are combined in a way

which allows a 2x2 ManArray processor to produce a distributed 256 point FFT in 425 cycles using

complex numbers of 32 bits (16 bits for real and imaginary parts) and an 8x8 IDCT in 34 cycles that

meets IEEE standards. And finally, because these emerging markets are primarily System-On-Chip

markets, BOPS is providing the ManArray as licensable IP in the form of Cores, SW, and Programming

Tools.

8

REFERENCES

[1] SGS Thomson Microelectronics, MPEG audio/MPEG-2 Video intergrated decoder Sti3520. http://www.st.com,

October 1996.

[2] SGS Thomson Microelectronics, MPEG 2.5 Layer III audio decoder STA013. http://www.st.com, September

1999.

[3] A. Van Roermond, P. Snijder, H. Dijkstra, C. Hemeryck, C. Huizer, J.Schimtz, and R. Sluijter. A Genera;-

Purpose Programmable Video Signal Processor. IEEE Transactions on Consumer electronics, 1989.

[4] J. Goto, K. Ando, T. Inoue, M. Yamashina, H. Yamada, and T. Enomoto. 250-Mhz BiCMOS Super-High-Speed

Video Signal Processor (S-VSP) ULSI. IEEE Journal of Solid-State Circuits, 1991.

[5] P.A. Ruetz, P. Tong, D. Bailey, D.A. Luthi, and P.H. Ang. A High-Performance Full-Motion Video Compression

Chip Set. IEEE Transactions on Circuits and Systems for Video Technology, 1992.

[6] S.Rathnam and G. Slavenburg. An Architectural Overview of the Programmable Multimedia Processor, TM-1. In

Proceedings of COMPCON 96, pages 319-326. IEEE, 1996.

[7] K. Guttag, R. J. Gove, and J.R. van Aken. A single-chip multiprocessor for multimedia: The MVP, IEEE

Computer Graphics and Applications, November 1992.

[8] A. Peleg and U. Weiser. MMX Technology Extension to the Intel Architecture. IEEE Micro, 16(4):42-50, August

1996.

[9] P. Rubinfeld, B. Rose, and M. McCallig. Motion Video Instruction Extensions for Alpha,

http://www.digital.com/semiconductor/papers/pmvi-abstract.htm, October 1996.

[10] M. Tremblay, J. M. OConner, V. Narayanan, and L. He. Vis speeds new media processing. IEEE Micro,

16(4):10-20, August 1996

[11] MIPS digital media extension. http://www.sgi.com/MIPS/products/.

[12] G.G. Pechanek, S. Vassiliadis, N. Pitsianis. ManArray Processor Interconnection Network: An Introduction. In

Proceedings of 5

th

Intl EURO-PAR Conference Toulouse, France, August/September 1999

[13] BOPS, Inc., BOPS 2040 core data sheet, http://bopsnet.com/cores_bops2040.shtml

[14] BOPS, Inc., BOPS benchmarks, http://bopsnet.com/benchmarks.shtml

[15] G. G. Pechanek, B. Schulman, and C. Kurak. Design of MPEG-2 Function with Embedded ManArray Cores.

In Proceedings of DesignCon 2000 IP World Forum Santa Clara, California, January/February 2000.

[16] N. P. Pitsianis and G. Pechanek. High-Performance FFT Implementation on the BOPS ManArray Parallel DSP.

In proceedings International Symposium on Optical Science, Engineering, and Instrumentation, Denver, Colorado,

July, 1999.

[17] BOPS, Inc., BOPS Software Development Kit (SDK), http://bopsnet.com/tools.shtml

You might also like

- CGRA Express: Accelerating Execution Using Dynamic Operation FusionDocument10 pagesCGRA Express: Accelerating Execution Using Dynamic Operation FusionJessica ThompsonNo ratings yet

- p241 PDFDocument9 pagesp241 PDFJessica ThompsonNo ratings yet

- p97 PDFDocument10 pagesp97 PDFJessica ThompsonNo ratings yet

- p21 PDFDocument9 pagesp21 PDFJessica ThompsonNo ratings yet

- Speedster™ DVI Adapter Card: Product BriefDocument1 pageSpeedster™ DVI Adapter Card: Product BriefJessica ThompsonNo ratings yet

- Futuro em VLIW PDFDocument5 pagesFuturo em VLIW PDFJessica ThompsonNo ratings yet

- Artigo R-Vex - Icfpr2008 PDFDocument4 pagesArtigo R-Vex - Icfpr2008 PDFJessica ThompsonNo ratings yet

- p155 PDFDocument8 pagesp155 PDFJessica ThompsonNo ratings yet

- p51 PDFDocument10 pagesp51 PDFJessica ThompsonNo ratings yet

- p1 PDFDocument10 pagesp1 PDFJessica ThompsonNo ratings yet

- SPD60 DDR3 Solution Guide PDFDocument16 pagesSPD60 DDR3 Solution Guide PDFJessica ThompsonNo ratings yet

- Speedster™ Fpga Family: Product BriefDocument2 pagesSpeedster™ Fpga Family: Product BriefJessica ThompsonNo ratings yet

- Common-Mode Failures PDFDocument11 pagesCommon-Mode Failures PDFJessica ThompsonNo ratings yet

- Achronix introFPGADocument7 pagesAchronix introFPGAjbakker42No ratings yet

- ManArray PDFDocument8 pagesManArray PDFJessica ThompsonNo ratings yet

- Speedster™ ADA Adapter Card: Product BriefDocument1 pageSpeedster™ ADA Adapter Card: Product BriefJessica ThompsonNo ratings yet

- Wishbone System-On-Chip (Soc) Interconnection Architecture For Portable Ip CoresDocument140 pagesWishbone System-On-Chip (Soc) Interconnection Architecture For Portable Ip Coresashrafuli_44No ratings yet

- SDK60 Product Brief PB003 PDFDocument2 pagesSDK60 Product Brief PB003 PDFJessica ThompsonNo ratings yet

- Achronix introFPGADocument7 pagesAchronix introFPGAjbakker42No ratings yet

- Sythesis From C PDFDocument8 pagesSythesis From C PDFJessica ThompsonNo ratings yet

- The Raw Microprocessor PDFDocument11 pagesThe Raw Microprocessor PDFJessica ThompsonNo ratings yet

- Wishbone System-On-Chip (Soc) Interconnection Architecture For Portable Ip CoresDocument140 pagesWishbone System-On-Chip (Soc) Interconnection Architecture For Portable Ip Coresashrafuli_44No ratings yet

- SoftCore N Embedded Proc Survey PDFDocument6 pagesSoftCore N Embedded Proc Survey PDFJessica ThompsonNo ratings yet

- 10 1 1 86 9432Document99 pages10 1 1 86 9432Harish MudimelaNo ratings yet

- Nomadik PDFDocument15 pagesNomadik PDFJessica ThompsonNo ratings yet

- Paper Reconf PDFDocument11 pagesPaper Reconf PDFJessica ThompsonNo ratings yet

- SerDes PDFDocument14 pagesSerDes PDFJessica ThompsonNo ratings yet

- Paper SoftcoresDocument8 pagesPaper SoftcoreslegendarykxNo ratings yet

- 1 - MibenchDocument12 pages1 - MibenchmatheustcheNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5782)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- How To Test BLE AdaptersDocument7 pagesHow To Test BLE AdaptersBender RodriguezNo ratings yet

- Module 5 PDFDocument14 pagesModule 5 PDFDiksha ChoudharyNo ratings yet

- DISTO Connectivity Overview - enDocument14 pagesDISTO Connectivity Overview - enabdulharisihanafiNo ratings yet

- DpiDocument1 pageDpiorsonorsonNo ratings yet

- Manuscript Alfamart BranchesDocument37 pagesManuscript Alfamart BranchesRamirez Mike BrianNo ratings yet

- Apache Oozie - A workflow scheduler to manage Hadoop jobsDocument5 pagesApache Oozie - A workflow scheduler to manage Hadoop jobsarjuncchaudharyNo ratings yet

- How To Install PHP 8Document9 pagesHow To Install PHP 8Obelisco WirelessNo ratings yet

- Using Inline Assembly With GCCDocument25 pagesUsing Inline Assembly With GCCgohan48100% (1)

- Tandberg Codian MCU 4500 Getting Started GuideDocument19 pagesTandberg Codian MCU 4500 Getting Started GuideAbdul RafayNo ratings yet

- IxChariot TrainingDocument57 pagesIxChariot TrainingJohn QwristewsNo ratings yet

- Home Automation Using Packet Tracer: Samarth Gupta (159101121)Document17 pagesHome Automation Using Packet Tracer: Samarth Gupta (159101121)Reti ZeeNo ratings yet

- NodeB Initial Configuration Guide - (V100R010 - 01)Document397 pagesNodeB Initial Configuration Guide - (V100R010 - 01)hippozooNo ratings yet

- Maxbox Starter 6: Start With Network ProgrammingDocument5 pagesMaxbox Starter 6: Start With Network ProgrammingMax KleinerNo ratings yet

- RTL8712 (8188 8191 8192SU) Usb Quick Installation GuideDocument8 pagesRTL8712 (8188 8191 8192SU) Usb Quick Installation GuideMauricio Navarro MirandaNo ratings yet

- Vmware Site Recovery Manager 8.2 Theory and LabDocument428 pagesVmware Site Recovery Manager 8.2 Theory and LabFeliz Bunguele100% (1)

- DRMDocument3 pagesDRMhatzsNo ratings yet

- SRS Document FormatDocument6 pagesSRS Document FormatAnirbanNo ratings yet

- How To Configure Listeners in Websphere Using TOCF (EE)Document27 pagesHow To Configure Listeners in Websphere Using TOCF (EE)Nett2kNo ratings yet

- OPNET Chapter 1-IntroductionDocument83 pagesOPNET Chapter 1-IntroductionnavidabedpoorNo ratings yet

- 1-CD DVD MGNT SystemDocument9 pages1-CD DVD MGNT SystembittuwarvadeNo ratings yet

- Cisco Live Multisite Evpn Vxlan BRKDCN-2035Document124 pagesCisco Live Multisite Evpn Vxlan BRKDCN-2035Harpreet Singh BatraNo ratings yet

- IpaddressDocument27 pagesIpaddressCyber DjomlaNo ratings yet

- Collection of HUAWEI Server BrochuresDocument20 pagesCollection of HUAWEI Server BrochuresJohanz RoqueNo ratings yet

- How to install Siae radio connection softwareDocument18 pagesHow to install Siae radio connection softwareguevaragus100% (2)

- Resolved - Reset Esxi Forgotten Root Password Using Hiren bootCD Step by StepDocument18 pagesResolved - Reset Esxi Forgotten Root Password Using Hiren bootCD Step by StepArash TorabiNo ratings yet

- Olympus 07258-1 48.4Y603.0SADocument55 pagesOlympus 07258-1 48.4Y603.0SACarlosNo ratings yet

- FPGA DesignDocument19 pagesFPGA DesignDana HowellNo ratings yet

- PDF 3374660 en-US-6Document176 pagesPDF 3374660 en-US-6jorgeNo ratings yet

- BE-CSE-IT Network Lab ManualDocument41 pagesBE-CSE-IT Network Lab ManualadmachewNo ratings yet

- Contents (2013 - 10 - 27 16 - 26 - 15 UTC)Document8 pagesContents (2013 - 10 - 27 16 - 26 - 15 UTC)Jhon GreigNo ratings yet