Professional Documents

Culture Documents

High Speed A2D Convertor Survey

Uploaded by

Adrian PostavaruOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

High Speed A2D Convertor Survey

Uploaded by

Adrian PostavaruCopyright:

Available Formats

High-Speed Analog-to-Digital Converter Survey

Kent H. Lundberg

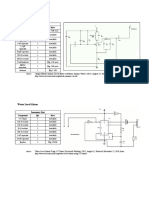

Every year, higher and higher sampling rates as well as lower and lower power dissipations

are reported in the literature. The table in Figure 1 lists published results for nineteen high-

speed, low-resolution A/D converters (mostly six to eight bits), along with a few commercial parts,

representing a wide variety of fabrication technologies. In the following sections, these reported

specications are analyzed and compared.

1 Quantization Energy Figure of Merit

The analog program committee of the IEEE International Solid-State Circuits Conference suggested

a gure of merit for A/D converters that takes into account power dissipation, resolution, and

sampling rate [1]. It has units of energy, and represents the energy used per conversion step

E =

P

2

N

F

S

where P is the power dissipation, N is the stated number of bits, and F

S

is the sampling rate. This

quantity is nearly the inverse of a similar gure of merit suggested earlier by Robert Walden [2, 3]

that uses the eective number of bits (ENOB), B, instead of the stated number of bits

F =

2

B

F

S

P

Waldens gure of merit F correctly includes the performance limitation of signal-to-noise-and-

distortion ratio (SNDR), but still produces optimistic results for some A/D converters

1

. In most

applications, A/D converters are expected to faithfully convert all input-signal frequencies below

the Nyquist frequency (one half of the sampling rate F

S

), but many A/D converters exhibit severe

degradation of SNDR at frequencies well below the Nyquist frequency. For this reason, the literature

has recently started using the eective resolution bandwidth (ERBW) instead of the sampling rate

in the equation for the gure of merit [4, 5]. This gure of merit is known as the quantization

energy

E

Q

=

P

2

B

(2F

BW

)

where P is the power dissipation, B is the high-frequency ENOB (calculated from SNDR), and

F

BW

is either the eective resolution bandwidth or the Nyquist frequency, which ever is less.

1

Hopeless pedants, like this author [6], also complain about its nonsensical units of inverse joules.

1

Pub F

S

stated ENOB ERBW Power E

Q

Pub

Year MS/s bits bits MHz mW pJ Ref

CMOS Flash Topologies

1998 200 6 5.0 100 380 59.4 [7]

1998 350 6 5.8 87 225 23.2 [8]

1998 400 6 5.0 100 190 29.7 [9]

1998 400 6 4.7 100 200 38.5 [10]

1999 500 6 5.3 250 400 20.3 [11]

1999 500 6 4.7 50 330 127 [12]

1999 500 6 5.3 180 225 15.9 [13]

2000 600 6 4.7 150 193 24.8 [14]

2000 700 6 5.5 136 187 15.2 [15]

2000 800 6 5.0 200 400 31.3 [16]

2001 1100 6 5.3 450 300 8.5 [4]

2001 1300 6 5.0 650 545 13.1 [17]

2002 1600 6 5.2 600 328 7.4 [5]

Bipolar Processes (including Si, GaAs, InP, etc)

1995 2000 8 6.5 1000 5300 29.3 [18]

1995 4000 6 5.1 1800 5700 46.2 [3, 19]

1996 8000 3 2.4 4000 3500 82.9 [20]

1999 500 8 7.2 250 950 12.9 [21]

Interleaved Topologies

1997 8000 8 5.3 2000 13500 85.7 [22]

2002 4000 8 6.5 900 2400 14.7 [23]

Commercial Parts

1995 1000 8 5.5 500 5500 122 [24]

1998 2000 8 5.9 500 5000 83.7 [25]

2001 1500 8 7.5 750 5300 19.5 [26]

Figure 1: Table of nineteen high-speed analog-to-digital converter specications gathered from the

literature, along with commercial parts from Fairchild, Rockwell, and Maxim.

2

2 High Speed

High-speed analog-to-digital converters are used in radar signal receivers, digital sampling oscil-

loscopes, read channels for magnetic storage systems, and local-area-network interfaces. Figure 2

shows the steady increase in eective resolution bandwidth with time. The average speed of high-

speed A/D converters has increased by a factor of ten over the past ve years.

10

100

1000

1997 1998 1999 2000 2001 2002 2003

E

f

f

e

c

t

i

v

e

r

e

s

o

l

u

t

i

o

n

b

a

n

d

w

i

d

t

h

(

M

H

z

)

Year of publication

10

100

1000

1997 1998 1999 2000 2001 2002 2003

E

f

f

e

c

t

i

v

e

r

e

s

o

l

u

t

i

o

n

b

a

n

d

w

i

d

t

h

(

M

H

z

)

Year of publication

Figure 2: Published CMOS ash A/D converters: eective resolution bandwidth versus year of

publication. The best-t line shows a factor of ten increase in ERBW over ve years.

3 Low Power

In this era of wireless communications, portable high-speed test equipment, and networked laptop

computers, the motivation for low-power electronics is clear. Reducing the power requirements of

existing components extends the battery life of portable devices, or allows additional functionality

to be incorporated on the same power budget. Alternatively, battery size (a signicant, often

dominant, contribution to the size and weight of portable devices) can be reduced by decreasing

the power consumption while maintaining feature set and battery life.

The total power consumption of massively-parallel systems, such as phased-array radar systems,

is also a concern, if for no other reason than the attendant cooling issues.

Figure 3 shows a minimum quantization energy of about 10 picojoules/conversion-step for a

wide range of bandwidths, with a sharp rise above one gigahertz. However, Figure 4 shows that

much of this progress in eciency has occurred recently, with the lowest reported quantization

energy decreasing yearly. Unfortunately, this data shows slow progress, with only a factor of ten

improvement over nine years.

3

1

10

100

1000

10 100 1000 10000

Q

u

a

n

t

i

z

a

t

i

o

n

e

n

e

r

g

y

(

p

J

)

Effective resolution bandwidth (MHz)

Figure 3: All high-speed ash A/D converters: quantization energy versus eective resolution

bandwidth.

1

10

100

1000

1994 1995 1996 1997 1998 1999 2000 2001 2002 2003

Q

u

a

n

t

i

z

a

t

i

o

n

e

n

e

r

g

y

(

p

J

)

Year of publication

1

10

100

1000

1994 1995 1996 1997 1998 1999 2000 2001 2002 2003

Q

u

a

n

t

i

z

a

t

i

o

n

e

n

e

r

g

y

(

p

J

)

Year of publication

Figure 4: All high-speed ash A/D converters: quantization energy versus year of publication. The

best-t line shows a factor of ten improvement in quantization energy over nine years.

4

4 Absolute Minimum Power

The absolute minimum power for an analog-to-digital converter can be calculated from rst princi-

ples [27, 28]. Assuming that the voltage to be converted is sampled and stored on a single capacitor,

C, the minimum thermal noise is

V

2

ntc

=

kT

C

If this capacitor is charged and discharged during every conversion cycle, the maximum power

dissipated is

P = CV

2

FS

F

S

where V

FS

is the full-scale voltage of the A/D converter and F

S

is the sampling rate. The quanti-

zation noise for this A/D converter is

V

2

nq

=

V

2

LSB

12

=

V

2

FS

2

2N

12

Limiting the thermal-noise power to be less than one quarter of the quantization-noise power, the

total signal-to-noise ratio of the A/D converter will be degraded by less than 1 dB (since 1 dB

corresponds to a factor of 1.25 in power units)

kT

C

<

1

4

V

2

FS

2

2N

12

Solving this inequality for the expression V

2

FS

C

V

2

FS

C > 48kT 2

2N

and substituting this quantity into the above expression for power gives the nal result

P > 48kT 2

2N

F

S

This expression implies an absolute lower bound on the quantization energy E

Q

for an A/D con-

verter of a given resolution N at any speed

E

Q

=

P

2

N

F

S

>

48kT 2

2N

F

S

2

N

F

S

= 48kT 2

N

for a six-bit A/D converter at room temperature (such as most of the A/D converters listed in

Figure 1), this limit is

E

Q

> 1.3 10

17

J

which is more than ve orders of magnitude below the best A/D converter in Figure 4.

5

5 Aperture Jitter

A limitation in the performance of state-of-the-art A/D converters has been observed and com-

mented on by Robert Walden [3]. Aperture jitter is the the sample-to-sample variation in the

instant of conversion. There is an rms voltage error caused by rms aperture jitter (measured in

picoseconds), and it decreases the overall signal-to-noise ratio.

Since the aperture-time variations are random, these voltage errors behave like a random noise

source. The signal-to-jitter-noise ratio can be expressed as

SJNR = 20 log

1

2t

a

F

S

The graph in Figure 5 shows the eective number of bits versus sampling rate for the A/D converters

listed in Figure 1. No A/D converter exhibits an aperture uncertainty better than 0.4 ps. Walden

observes that this situation has not improved much over time, and will not without signicant

research and development.

4

5

6

7

8

9

10

1e+08 1e+09 1e+10

E

f

f

e

c

t

i

v

e

n

u

m

b

e

r

o

f

b

i

t

s

Sampling rate (Samples per second)

4

5

6

7

8

9

10

1e+08 1e+09 1e+10

E

f

f

e

c

t

i

v

e

n

u

m

b

e

r

o

f

b

i

t

s

Sampling rate (Samples per second)

Figure 5: All high-speed ash A/D converters: eective number of bits versus sampling rate. The

line corresponds to the limitation imposed by an rms aperture jitter of 0.4 ps.

6 Additional Power Consumption

Clearly, thermal noise is not the only limiting factor, and the simply-derived lower bound on power

may never be approached. The development in Section 4 considers only the power consumption of

an ideal sample-and-hold. It completely ignores the power consumption of active circuitry in the

A/D converter for analog amplication or digital encoding. The power required to drive parasitic

capacitances was also ignored. Considering these real-world requirements, several other limitations

on performance can be calculated.

6

6.1 Transistor Matching

Random voltage osets in the comparators cause a limitation to accuracy that can only be overcome

with improved transistor matching. Oset reduction through transistor matching increases power

consumption. Transistor matching can be improved by increasing device size (which increases

parasitic capacitances), by introducing calibration or error-correcting techniques (which consume

additional power), or by introducing auto-zero cycles (which decrease speed). The additional power

required to overcome the eects of transistor mismatch in high-speed CMOS systems is two orders

of magnitude higher than the limit imposed by thermal noise [29, 30].

Reported data shows that transistor matching improves with decreasing gate-oxide thickness

[30], thus for the same transistor area higher accuracy and speed, or lower power consumption,

should be achievable in a technology with smaller feature sizes. However, lower supply voltages

adversely aect the signal-to-noise ratio and decrease the potential improvements [31].

6.2 Device Parasitics

Scaled technologies with smaller feature sizes often have larger parasitics, since the increased doping

increases the values of the depletion capacitances that form around the junctions. These parasitics

directly aect performance. In particular, gate-overlap capacitances and drain-to-bulk depletion-

layer capacitances have been shown to have increasing inuence in scaled processes [32]. It is

possible that power consumption will actually need to increase to maintain accuracy and speed in

the face of shrinking feature sizes [33].

6.3 Calibration

Calibration of A/D converters generally increases power consumption and decreases speed. Compa-

rable digital and analog calibration techniques [34, 35], designed for similar performance improve-

ments, signicantly increase power consumption.

7 Conclusions

Aperture jitter, transistor matching, and increasing drain-bulk capacitance remain major problems

in the development of high-speed, low-power A/D converters. In spite of these diculties, steady

progress in speed and power has been made in recent years, as shown in Figures 2 and 4.

Following these trends, a six-bit A/D converter with a 10-GHz eective resolution bandwidth

will be available in ve to six years, but with a projected quantization energy of E

Q

= 3 pJ, it will

carry a power consumption of four watts.

7

References

[1] Frank Goodenough. Analog technology of all varieties dominate ISSCC. Electronic Design,

44(4):96111, February 19, 1996.

[2] Robert H. Walden. Analog-to-digital converter technology comparison. In IEEE GaAs IC

Symposium, Technical Digest, pages 217219, October 1994.

[3] Robert H. Walden. Analog-to-digital converter survey and analysis. IEEE Journal on Selected

Areas in Communication, 17(4):539550, April 1999.

[4] Govert Geelen. A 6b 1.1GSample/s CMOS A/D converter. In IEEE International Solid-State

Circuits Conference, Digest of Technical Papers, pages 128129, February 2001.

[5] Peter Scholtens and Maarten Vertregt. A 6b 1.6GSample/s ash ADC in 0.18m CMOS

using averaging termination. In IEEE International Solid-State Circuits Conference, Digest of

Technical Papers, pages 168169, February 2002.

[6] Joshua W. Phinney. Student Evaluation for MIT Course 6.331: Advanced Circuit Techniques,

May 2002. In his evaluation, Mr. Phinney wrote: Recitation Instructor [Kent Lundberg] is

hopelessly pedantic. This comment was taken as a compliment.

[7] Declan Dalton, G. Spalding, H. Reyhani, T. Murphy, K. Deevy, M. Walsh, and P. Grin.

A 200-MSPS 6-bit ash ADC in 0.6-m CMOS. IEEE Transactions of Circuits and Systems

II: Analog and Digital Signal Processing, 45(11):14331444, November 1998.

[8] P. Setty, J. Barner, J. Plany, H. Burger, and J. Sonntag. A 5.75b 350MSample/s or 6.75b

150MSample/s recongurable ash ADC fpr a PRML read channel. In IEEE International

Solid-State Circuits Conference, Digest of Technical Papers, pages 148149, February 1998.

[9] Sanroku Tsukamoto, William G. Schoeld, and Toshiaki Endo. A CMOS 6-b, 400-MSample/s

ADC with error correction. IEEE Journal of Solid-State Circuits, 33(12):19391947, December

1998.

[10] Michael Flynn and Ben Sheahan. A 400-Msample/s, 6-b CMOS folding and interpolating

ADC. IEEE Journal of Solid-State Circuits, 33(12):19321938, December 1998.

[11] Yuko Tamba and Kazuo Yamakido. A CMOS 6b 500MSample/s ADC for hard disk drive read

channel. In IEEE International Solid-State Circuits Conference, Digest of Technical Papers,

pages 324325, February 1999.

[12] Kwangho Yoon, Sungkyung Park, and Wonchan Kim. A 6b 500MSample/s CMOS ash ADC

with a background interpolated auto-zeroing technique. In IEEE International Solid-State

Circuits Conference, Digest of Technical Papers, pages 326327, February 1999.

[13] Iuri Mehr and Declan Dalton. A 500-MSample/s 6-bit nyquist-rate ADC for disk-drive read-

channel applications. IEEE Journal of Solid-State Circuits, 34(7):912920, July 1999.

[14] Peter Scholtens. A 2.5 volt 6 bit 600MS/s ash ADC in 0.25m CMOS. In Proceedings of the

European Solid-State Circuits Conference, pages 196199, September 2000.

8

[15] K. Nagaraj, D. Martin, M. Wolfe, R. Chattopadhyay, A. Pavan, J. Cancio, and

T. Viswanathan. A dual-mode 700MSample/s 6-bit 200MSample/s 7-bit A/D converter in

a 0.25-m digital CMOS process. IEEE Journal of Solid-State Circuits, 35(12):17601768,

December 2000.

[16] Kouji Sushihara, H. Kimura, Y. Okamoto, K. Nishimura, and A. Matsuzawa. A 6b 800MSam-

ple/s CMOS A/D converter. In IEEE International Solid-State Circuits Conference, Digest of

Technical Papers, pages 428429, February 2000.

[17] Michael Choi and Asad A. Abidi. A 6-b 1.3Gsample/s A/D converter in 0.35-m CMOS.

IEEE Journal of Solid-State Circuits, 36(12):18471858, December 2001.

[18] Kevin R. Nary, R. Nubling, S. Beccue, W. Colleran, J. Penney, and K. Wang. An 8-bit

2 gigasample per second analog to digital converter. In IEEE GaAs IC Symposium, Technical

Digest, volume 17, pages 303306, October 1995.

[19] Ken Poulton, K. Knudsen, J. Corcoran, K. Wang, R. Nubling, R. Pierson, M. Chang, P. As-

beck, and R. Huang. A 6-b, 4 GSa/s GaAs HBT ADC. IEEE Journal of Solid-State Circuits,

30(10):11091118, October 1995.

[20] Cynthia Baringer, Joe Jensen, Larry Burns, and Bob Walden. 3-bit, 8 GSPS ash ADC. In

Proceedings of the International Conference on Indium Phosphide and Related Materials, pages

6467, April 1996.

[21] Koichi Irie, N. Kusayanagi, T. Kawachi, T. Nishibu, and Y. Matsumori. An 8b 500MS/s full

nyquist cascade A/D converter. In Symposium on VLSI Circuits, Digest of Technical Papers,

pages 7778, June 1999.

[22] Ken Poulton, K. Knudsen, J. Kerley, J. Kang, J. Tani, E. Cornish, and M. VanGrouw. An

8-GSa/s 8-bit ADC system. In Symposium on VLSI Circuits, Digest of Technical Papers,

pages 2324, June 1997.

[23] Ken Poulton, R. Ne, A. Muto, W. Liu, A. Burstein, and M. Heshami. A 4GSample/s 8b

ADC in 0.35-m CMOS. In IEEE International Solid-State Circuits Conference, Digest of

Technical Papers, pages 166167, February 2002.

[24] Fairchild Semiconductor. SPT7760 8-bit, 1 GSPS, ash A/D converter. Datasheet, 1995.

[25] Robert H. Walden. Spreadsheet of data for ADC survey. Available from HRL web site at

http://www.hrl.com/TECHLABS/micro/ADC/adc.html, July 1999. Includes data for Rock-

well RSC-ADC080S.

[26] Maxim Integrated Products. MAX108 5V, 1.5GSPS, 8-bit ADC with on-chip 2.2GHz

track/hold amplier. Datasheet, 2001.

[27] Eric A. Vittoz. Future of analog in the VLSI environment. In Proceedings of the IEEE

International Symposium on Circuits and Systems, pages 13721375, May 1990.

[28] Thomas Byunghak Cho and Paul R. Gray. A 10 b 20 Msample/s 35 mW pipeline A/D

converter. IEEE Journal of Solid-State Circuits, 30(3):166172, March 1995.

[29] Peter Kinget and Michiel Steyaert. Impact of transistor mismatch on the speed-accuracy-

power trade-o of analog CMOS circuits. In Proceedings of the IEEE Custom Integrated

Circuits Conference, pages 333336, May 1996.

9

[30] Marcel J.M. Pelgrom, Hans P. Tuinhout, and Maarten Vertregt. Transistor matching in analog

CMOS applications. In International Electron Devices Meeting, Technical Digest, pages 915

918, December 1998.

[31] M. Steyaert, V. Peluso, J. Bastos, P. Kinget, and W. Sansen. Custom analog low power design:

the problem of low voltage and mismatch. In Proceedings of the IEEE Custom Integrated

Circuits Conference, pages 285292, May 1997.

[32] Willy Sansen. Analog circuit design in scaled CMOS technology. In Symposium on VLSI

Circuits, Digest of Technical Papers, pages 811, June 1996.

[33] Koen Uyttenhove and Michiel Steyaert. Speed-power-accuracy trade-o in high-speed ADCs:

what about nano-electronics? In Proceedings of the IEEE Custom Integrated Circuits Confer-

ence, pages 341344, May 2001.

[34] D. Fu, K. Dyer, S. Lewis, and P. Hurst. Digital background calibration of a 10b 40MSample/s

parallel pipelined ADC. In IEEE International Solid-State Circuits Conference, Digest of

Technical Papers, pages 140141, February 1998.

[35] K. Dyer, D. Fu, S. Lewis, and P. Hurst. Analog background calibration of a 10b 40MSample/s

parallel pipelined ADC. In IEEE International Solid-State Circuits Conference, Digest of

Technical Papers, pages 142143, February 1998.

Copyright c 2002 Kent Lundberg. All rights reserved.

10

You might also like

- Large Margin Multi Channel Analog To Digital Conversion With Applications To Neural ProsthesisDocument8 pagesLarge Margin Multi Channel Analog To Digital Conversion With Applications To Neural ProsthesisAdrian PostavaruNo ratings yet

- Lewis Pipelined A2D PDFDocument8 pagesLewis Pipelined A2D PDFAdrian PostavaruNo ratings yet

- SM G935 ManualDocument16 pagesSM G935 ManualAdrian PostavaruNo ratings yet

- A 8 Bits Pipeline Analog To Digital Converter Design For High Speed For Camera ApplicationDocument5 pagesA 8 Bits Pipeline Analog To Digital Converter Design For High Speed For Camera Applicationclurado1980No ratings yet

- An Ultralow-Energy ADC For Smart Dust PDFDocument7 pagesAn Ultralow-Energy ADC For Smart Dust PDFAdrian PostavaruNo ratings yet

- Design Low Power EncoderDocument8 pagesDesign Low Power EncoderAdrian PostavaruNo ratings yet

- Design of Low Power Nyquist A2D PDFDocument75 pagesDesign of Low Power Nyquist A2D PDFAdrian PostavaruNo ratings yet

- AD ConvertersDocument15 pagesAD ConvertersNathalia Parra GarzaNo ratings yet

- Signal GeneratorsDocument35 pagesSignal GeneratorsAdrian PostavaruNo ratings yet

- Laptop Repair Complete Guide Including Motherboard Component Level Repair!Document89 pagesLaptop Repair Complete Guide Including Motherboard Component Level Repair!smooky1980100% (2)

- Sperm SeparationDocument2 pagesSperm SeparationAdrian PostavaruNo ratings yet

- Meditation Clicks PDFDocument115 pagesMeditation Clicks PDFAdrian PostavaruNo ratings yet

- Signal Generator ManualDocument672 pagesSignal Generator ManualAdrian PostavaruNo ratings yet

- A2D Covertor in Wireless LANDocument15 pagesA2D Covertor in Wireless LANAdrian PostavaruNo ratings yet

- Sperm Selection PDFDocument17 pagesSperm Selection PDFAdrian PostavaruNo ratings yet

- Signal Generator AgilentDocument362 pagesSignal Generator AgilentAdrian PostavaruNo ratings yet

- Magic Tree HouseDocument49 pagesMagic Tree HouseAdrian Postavaru80% (74)

- Insects Identification GuideDocument24 pagesInsects Identification GuideAdrian Postavaru100% (1)

- Oscilloscope BasicsDocument19 pagesOscilloscope Basicsmedia1112No ratings yet

- Notes On Signal GeneratorsDocument3 pagesNotes On Signal GeneratorsAdrian PostavaruNo ratings yet

- Corn Insect PestsDocument0 pagesCorn Insect PestsAdrian PostavaruNo ratings yet

- Tree House PlanDocument12 pagesTree House PlanAdrian Postavaru100% (3)

- Tree House ComunityDocument2 pagesTree House ComunityAdrian PostavaruNo ratings yet

- Signal Generator AeroflexDocument8 pagesSignal Generator AeroflexAdrian PostavaruNo ratings yet

- Tree Literate TreehousesDocument2 pagesTree Literate TreehousesAdrian PostavaruNo ratings yet

- Treehouse PlansDocument66 pagesTreehouse PlansAdi Badescu100% (2)

- Garden BugsDocument12 pagesGarden BugsAdrian PostavaruNo ratings yet

- How To Bug Proof Your HomeDocument32 pagesHow To Bug Proof Your HomeAdrian PostavaruNo ratings yet

- Soybean Insect Identification GuideDocument8 pagesSoybean Insect Identification GuideAdrian PostavaruNo ratings yet

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5784)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (890)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (72)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Servo Weld Guns - VX TYPE: 2M MTBF 100% BodyshopDocument2 pagesServo Weld Guns - VX TYPE: 2M MTBF 100% BodyshopLuciana LuNo ratings yet

- Ohm's LawDocument11 pagesOhm's LawMarifer RamirezNo ratings yet

- Aiwa Cx-jds20 Cx-jds50 Ver1.1 SMDocument69 pagesAiwa Cx-jds20 Cx-jds50 Ver1.1 SMmientrasvivoNo ratings yet

- LCD Test Tool InstructionsDocument8 pagesLCD Test Tool Instructionsjo snadaNo ratings yet

- Drofenik APE07Document11 pagesDrofenik APE07saravanajsrNo ratings yet

- Klv-17hr1 LCD Colour TVDocument74 pagesKlv-17hr1 LCD Colour TVMICHAEL THOULASSNo ratings yet

- Project - Review ThermoelectricDocument30 pagesProject - Review ThermoelectricAbhishek KumarNo ratings yet

- Mechatronics MCQ: Dhirajlal Gandhi College of Technology, Salem Department of Mechanical EngineeringDocument16 pagesMechatronics MCQ: Dhirajlal Gandhi College of Technology, Salem Department of Mechanical EngineeringUbedullah SaeedNo ratings yet

- Basic Electronic Troubleshooting For Biomedical Technicians 2edDocument239 pagesBasic Electronic Troubleshooting For Biomedical Technicians 2edClovis Justiniano100% (22)

- Installation Of Heavy Duty PVC CablesDocument1 pageInstallation Of Heavy Duty PVC CablesYaserNo ratings yet

- Communications PDFDocument3 pagesCommunications PDFBMNo ratings yet

- Pac120 5715-719ukDocument88 pagesPac120 5715-719ukDiego LorenziNo ratings yet

- Install & Maintain Pressure Regulator GuideDocument4 pagesInstall & Maintain Pressure Regulator GuideBrandon TrocNo ratings yet

- KARNATAKA POWER TRANSMISSION CORPORATION LIMITED RELAYS AND PROTECTIONDocument43 pagesKARNATAKA POWER TRANSMISSION CORPORATION LIMITED RELAYS AND PROTECTIONSaurabh Kumar SinghNo ratings yet

- Power System Power Solution For Green Base Station Energy Efficient, Space Saving, Environment FriendlyDocument2 pagesPower System Power Solution For Green Base Station Energy Efficient, Space Saving, Environment FriendlyNguyễnĐìnhDầnNo ratings yet

- (L8) - (JLD 2.0) - Current Electricity - 27th JuneDocument43 pages(L8) - (JLD 2.0) - Current Electricity - 27th JuneAtishay VermaNo ratings yet

- Power Distribution System Master Plan Study For GhanaDocument82 pagesPower Distribution System Master Plan Study For Ghanabudi hermawanNo ratings yet

- Features:: Powered LoudspeakerDocument6 pagesFeatures:: Powered LoudspeakerYerko LucoNo ratings yet

- Build your own Atari Punk ConsoleDocument15 pagesBuild your own Atari Punk ConsoleNatalia RabellNo ratings yet

- RRL 2Document2 pagesRRL 2Jessie BasasNo ratings yet

- Sick - Product Information Safe AGV EasyDocument36 pagesSick - Product Information Safe AGV EasySafetyjoe2100% (1)

- Half & Full Wave Rectifier Circuits, Zener Diode Voltage Regulator ExperimentDocument22 pagesHalf & Full Wave Rectifier Circuits, Zener Diode Voltage Regulator ExperimentHardik RangwaniNo ratings yet

- En 50155 (2017)Document110 pagesEn 50155 (2017)彭以和100% (1)

- G7100-90000 CE System User Ebook PDFDocument286 pagesG7100-90000 CE System User Ebook PDFjohn chinNo ratings yet

- Mobile Jammer Circuit: Inventory ListDocument2 pagesMobile Jammer Circuit: Inventory ListCarlo Piere DayaoNo ratings yet

- INSOCOAT-Brochure SKFDocument8 pagesINSOCOAT-Brochure SKFLuis EstradaNo ratings yet

- Active Barrier RN221NDocument8 pagesActive Barrier RN221NOleg SidNo ratings yet

- Hella Battery - BAPDocument1 pageHella Battery - BAPagus cahyadiNo ratings yet

- Cable Specification Chart for ESM CablesDocument1 pageCable Specification Chart for ESM Cablesjulian_binevNo ratings yet

- SUN 72MD-H8S大Document2 pagesSUN 72MD-H8S大Helvécio OliveiraNo ratings yet