Professional Documents

Culture Documents

Boost Conveter Battery and Solar Cell Operation Sensor Network

Uploaded by

Jaziel CabralCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Boost Conveter Battery and Solar Cell Operation Sensor Network

Uploaded by

Jaziel CabralCopyright:

Available Formats

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 48, NO.

8, AUGUST 2013

1933

0.5 V Start-Up 87% Efficiency 0.75 mm On-Chip

Feed-Forward Single-Inductor Dual-Output

(SIDO) Boost DC-DC Converter for Battery

and Solar Cell Operation Sensor Network

Micro-Computer Integration

Yasunobu Nakase, Shinichi Hirose, Hiroshi Onoda, Yasuhiro Ido, Yoshiaki Shimizu, Tsukasa Oishi,

Toshio Kumamoto, and Toru Shimizu, Senior Member, IEEE

AbstractAn on-chip low power single-inductor dual-output

(SIDO) DC-DC boost converter is proposed for battery and solar

cell operating sensor network applications. A proposed feed

forward control determines the Ton/Toff ratio precisely for each

output without any compensation or linear capacitor. This feature

helps reduce the costs of the external components and utilize

an inexpensive process technology. A test chip was fabricated by

190-nm flash-memory embedded micro-computers CMOS process

technology and can achieve an efficiency of 87% with a small area

size of just 0.75 mm. For solar cell operation, a 0.5 V start-up

was achieved even with a high threshold voltage of 0.7 V with a

proposed forward back biased charge pump. A constant voltage

algorithm was implemented as a maximum power point tracking

(MPPT) control. With this MPPT control, a solar cell with an open

voltage of 1.03 V and a short current of 83 mA was able to charge

a super capacitor of 0.4 F up to 5 V within 80 s.

Index TermsBoost, DC-DC converter, energy harvesting, feed

forward control.

I. INTRODUCTION

ECENTLY, wireless sensor networks have been widely

used to improve energy efficiency by controlling

building, office, and home environments [1][3]. A large

number of sensor nodes are distributed to monitor environmental parameters such as temperature, humidity, illumination

intensity, and so on. Each node consists of a micro-computer for

controlling the node operation, sensors, and sensor interfaces

Manuscript received November 29, 2012; revised March 28, 2013; accepted

March 28, 2013. Date of publication May 13, 2013; date of current version July

19, 2013. This paper was approved by Guest Editor Ken Suyama.

Y. Nakase, Y. Ido, and T. Kumamoto are with the Core Technology Business

Division, Renesas Electronics Corporation, Hyogo 664-0005, Japan (e-mail:

yasunobu.nakase.yg@renesas.com).

T. Oishi and Y. Shimizu are with Fundamental Technology Unit, Renesas

Design Corporation, Hyogo 664-0005, Japan.

S. Hirose and H. Onoda are with Renesas Design Corporation, Hyogo 6640005, Japan.

T. Shimizu is with Global Business Innovation and Strategy Marketing Division, 1st Solution Business Unit, Renesas Electronics Corporation, Tokyo 1000004, Japan.

Color versions of one or more of the figures in this paper are available online

at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2013.2258826

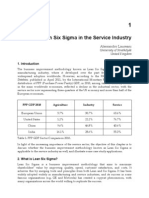

Fig. 1. SIDO DC-DC converter for battery operating sensor node.

and a radio frequency (RF) module to send the measured data.

The sensor nodes are placed in every conceivable indoor location, so battery operation is required to ensure flexibility of the

placement. A single-inductor dual-output (SIDO) architecture

is suitable for such application. As shown in Fig. 1, one output

VCCX supplies power between 3 V and 5 V with around 10 mA

to the sensors. The other output VCCY supplies power of 3 V

with more than 25 mA to a micro-computer control circuits

(Cntrl CKT) of the DC-DC converter and sensor network RF

modules such as ZigBee.

When the clock MCLK is at a high level (Ton period), an

inductor stores the current, and when it is at a low level (Toff

period), the current is delivered to the output VCCX or VCCY

when the respective signal CLKX or CLKY is low. It is preferable for the SIDO converter to be embedded in a relatively small

area with a micro-computer because of the size limitation of the

sensor nodes.

To determine the Ton period, feed back control has generally

been used. When the output voltage is lower than that of an expected value, the Ton period is increased through a feed back

loop. To obtain a precise output level, the gain of this feed back

loop should be high enough. Therefore, phase compensation is

necessary to prevent an oscillation. This requires additional capacitors outside the chip for the compensation. This is problematic for the feed back control because the capacitors slow the

response. In a case of load transient, it takes almost from 0.5 ms

to 1 ms [4] for the output voltage to become stable. For sensor

network applications, the SIDO converter frequently changes

0018-9200/$31.00 2013 IEEE

1934

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 48, NO. 8, AUGUST 2013

Fig. 2. Single output DC-DC converter.

Fig. 3. Conventional discontinuous conduction mode (DCM) controls for dual

outputs.

Fig. 4. Conventional feed forward control. OSP refers to one-shot pulse

generator.

the outputs for charging up. The Ton/Toff ratio needs to be determined immediately when the output changes, so feed back

control is not suitable for SIDO architecture. The other problem

of feed back control can be explained simply by using a single

output boost converter as shown in Fig. 2. The transfer function

is given by [5]

voltage

is lower than that of the triangle waveform, the clock is set low and the Ton/Toff ratio is determined

as

(1)

(2)

The transfer function depends on all of the parameters. For

each different value of L, C, R, Vin, and Vout, compensation

circuits should be optimized. Therefore, it is difficult to support

a wide range of input and output voltages and the values of L,

C, and R.

Many types of discontinuous conduction mode (DCM) operation have been proposed as methods that do not require compensation. Fig. 3 (i) shows a case in which each output is alternately charged in every cycle [6], [7]. In Fig. 3 (ii), both outputs

are charged in every cycle [8]. Large transistors are necessary

in DCM to obtain a high efficiency because the peak inductor

current is large. Fig. 3 (iii) shows the pseudo continuous conduction mode (CCM). The peak inductor current IL can be reduced

by flowing a constant current [9]. This mode has achieved efficiencies of 88.4% and 89.4% with chip sizes of 2.4 mm [6]

and 4.25 mm [9], respectively. These sizes, however, are too

large for micro-computer integration. Furthermore, each output

is required to supply almost the same amount of load current in

[9] to keep the offset current at a constant level.

Feed forward control [10] is another method that does not

require compensation. Its operation is shown in Fig. 4. A current source charges a capacitor C. When the capacitor voltage

reaches VREF, a one-shot pulse (OSP) generator discharges the

capacitor, thus generating a triangle waveform. When the scaled

(3)

(4)

The Ton/Toff duty ratio is set to

in an ideal

case [11]. From (4), the desired ratio can be obtained by setting

VREF as

. There are a few problems with this scheme in

terms of practical use. For example, to obtain a precise ratio, the

capacitor needs to have linear characteristics, but such a capacitor requires a large area size or expensive additional processes

such as a polysilicon process. When is set to 0.2 and the input

voltage range is assumed to range from 0.5 V to 3 V, the value

of

varies from 0.1 V to 0.6 V. For the lower Vin, the

offset voltage of the comparator creates a larger impact.

When sensor nodes are placed outdoors, a solar cell is used

for power in order to reduce or eliminate battery maintenance

issues. In this case, a maximum power point tracking (MPPT)

control is used to extract the maximum power from a solar cell

by modulating the clock pulsewidth [12][14]. Since the output

of a solar cell is unstable, a super capacitor is used to store the

electric power generated by the solar cell [15], [16]. The super

capacitor then supplies power to the sensor node through a low

drop-out regulator (LDO) as shown in Fig. 5. In the case of a

single output converter, the output must supply the power to

both a super capacitor and its control circuits. It takes a very

long time for the control circuits to operate properly because

the output voltage rises very slowly due to the super capacitor.

The SIDO architecture also has an advantage in that one output

charges the super capacitor while the other simultaneously supplies the power to the control circuits.

A boost converter is required to start up from a single cell

voltage of 0.5 V [13]. It has been realized by using low threshold

voltage process technology [17], by supplying a clock signal

from outside [14], or by using a dedicated start-up IC [18]. Selfcontained systems do not employ these methods.

NAKASE et al.: ON-CHIP FEED-FORWARD SIDO BOOST DC-DC CONVERTER

1935

Fig. 5. SIDO DC-DC converter for solar cell operating sensor node.

In this paper, we propose an on-chip low power SIDO DC-DC

converter operating with both a battery and a single solar cell

[19]. A high efficiency of 87% is achieved with a small area

size of just 0.75 mm and no external components for compensation by using a new feed forward control. This feed forward control does not require a linear capacitor and reduces

the impact of comparator offset because the operating point can

be set to a higher voltage. Quick response is also realized by

the feed forward control because it can determine the proper

duty ratio immediately. Two-stage start-up architecture realizes

0.5 V start-up without any special process technology, additional ICs, or assistance from the outside. A constant voltage

or fractional open-circuit voltage method [20], [21] is implemented as an MPPT function. This method is both simple and

effective. The proposed converter is applicable to a power supplier for a sensor node in both indoor and outdoor systems with

a small foot-print.

Fig. 6. Block diagram of SIDO DC-DC boost converter.

Fig. 7. Control circuits (Cntrl CKT) from Fig. 6 composed of two parts: FF

and CLK Gen.

II. FEED FORWARD CONTROL FOR SIDO ARCHITECTURE

The block diagram of the proposed converter is shown in

Fig. 6. VBAT is the input voltage. The first output VCCX can

be set between 3 V and 5 V to deal with the wide variety of

supply voltages for the sensors. The voltage of the second output

VCCY is predefined at 3 V. DVCCY supplies power to the internal control circuits (Cntrl CKT). pMOS transistors PX0 and

PY0 are used as rectifier transistors. When DVCCY reaches

3 V, the VCCX and VCCY power lines become available by

setting the signal PWS to low. The pMOS transistors PX1 and

PY1 have two roles. One is to control the slew rate of VCCX

and VCCY at the beginning of supplying powers. When one of

the outputs supplies the power to a micro-computer, it requires

some voltage slew rate of the power line to invoke power on the

reset function. The other role is to shut down the power lines

when a large load current flows.

The control circuits are composed of two parts as shown in

Fig. 7, the feed forward pulsewidth modulator (FF-PWM) and

the clock signal generator (CLK Gen). FF-PWM generates the

basic clock signal CLK. As explained later, the optimum duty

ratio is calculated immediately from the input and the expected

output voltages.

The circuit configuration of the control circuits (Cntrl CKT)

is shown in Fig. 8. This block generates the main clock MCLK

and the rectifier pMOS control signals CLKX and CLKY from

the CLK signal through the non-overlap circuit. A short current

is prevented since the nMOS driver and the pMOS rectifier transistors do not turn on at the same time. CLK Gen also provides

Fig. 8. Clock generator (CLK Gen) circuit configuration.

the signals SCTY and NOP. When SCTY is at a high level, the

VCCY is selected to be charged. The NOP signal indicates that

both VCCX and VCCY have reached their expected voltages.

When NOP becomes a high level, the FF-PWM block stops.

The SIDO operation is shown in Fig. 9. For each cycle, the inductor stores a current and delivers it to either one of the outputs.

1936

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 48, NO. 8, AUGUST 2013

Fig. 10. Feed-forward pulsewidth modulation (FF-PWM). OSP refers to oneshot pulse generator.

Fig. 11. Simple model for analyzing effect of parasitic resistances.

The duties are therefore

(7)

(8)

Fig. 9. Proposed feed-forward control of charging outputs.

Each output is alternately charged for several cycles in continuous conduction mode (CCM). When VCCY is lower than the

expected voltage of 3 V, the SCTY is set to high as shown in

Fig. 8. The signal CLKY then becomes active. DVCCY and

VCCY are charged before VCCX, and as a result, the control

circuits (Cntrl CKT) are always stable. After VCCY reaches 3 V,

DVCCX and VCCX are selected. When both outputs of VCCX

and VCCY have reached the expected voltages, operation stops

by setting the NOP signal to high.

Fig. 10 shows the circuit configuration of the feed forward

pulsewidth modulator (FF-PWM). It consists of three parts:

a standard current generator

, a Ton period generator

, and a Toff period generator

. OSP refers to a

one-shot pulse generator. The

block generates a current

that is proportional to VBAT. At the end of the Toff period,

the

block is activated. The Ton period is determined

as the interval until the capacitor voltage reaches the reference

voltage VREF. Ton and Toff periods are given as

The resistor R in (5) and (6) is equal to RY or

when VCCY or VCCX is selected, respectively. In

an ideal case, the Ton/Toff ratio should be equal to

[11]. The desired duty ratio is obtained

by setting

and

.

For example, with reference to Fig. 10, when VREF and Rcs

are 0.8 V and 80

, respectively, Ics is set to 10 A. RY and

RX should be set to 300

and 100

.

The expected VCCX can be changed by setting VREF2 at

another voltage since Ics is determined by VREF2 when VCCX

is selected as shown in Fig. 10. If VREF2 is set to 1 V, Ics is

12.5 A. The expected VCCX is set to 5 V because VCCX is

given as

A. In contrast,

if VREF2 is set to 0.6 V, Ics becomes 7.5 A. The expected

VCCX is 3 V because VCCX is given as

A.

In practice, the duty ratio should be set to larger than the ideal

values to compensate for the power loss due to parasitic resistances. A simple model as shown in Fig. 11 explains the effect

of these resistances. The figure shows one of the outputs. The

on-resistances of nMOS and pMOS transistors N0 and P0 are

indicated by Rn and Rp. The power loss of pMOS transistor P1

is small and can be neglected. The effective input voltage

is lower than Vin by a voltage drop in the resistance. In contrast,

the effective output voltage

is higher than Vout.

(9)

(10)

(5)

(6)

Rn and Rp are 0.5 and 1.2 , respectively. The third term

in (10) is an input offset voltage generated during the Ton

period. M is the effective voltage conversion ratio given by

. Then,

can be considered an inductor

NAKASE et al.: ON-CHIP FEED-FORWARD SIDO BOOST DC-DC CONVERTER

1937

Fig. 13. Control circuits for constant voltage maximum power point tracking

(MPPT).

Fig. 12. Electrical characteristics of solar cell.

current. From (9) and (10), the sustainable load current can be

calculated for a given M value.

(11)

As the M value is set larger than its ideal value of Vout/Vin,

the sustainable load current increases. However, the power loss

increases because the inductor current increases. We therefore

set the M value to 7% larger than its ideal value. The sustainable

load current of VCCX is given as follows. When the VBAT is

0.5 V, the M value is

. VCCX

can supply a load current of 3.7 mA. When VBAT is 1.5 V, the

sustainable load current increases up to 30 mA.

As shown in (11), the sustainable load current is not determined from the Ton and Toff periods themselves but rather their

ratio. Equations (7) and (8) mean that the ratio is independent of

the value of the capacitors. Therefore, capacitor linearity is not

required in this proposed control. In practice, varactors are used

as non-linear capacitors. Furthermore, a precise ratio is obtained

even at low VBAT. Since the comparator operates at the input

range around VREF (0.8 V in this case), the offset voltage has

only minimal impact compared with the conventional control.

III. OPERATION WITH SOLAR CELL

In the case of solar cell operation, an MPPT control is used instead of the feed forward control. Fig. 12 shows electrical characteristics of a solar cell. Open voltage is defined as the voltage

when no current flows and short current is defined as the current

when the voltage is zero. For each point, the power is zero. As

the Ton period increases, the solar cell current increases and its

voltage decreases. Various methods have been proposed to operate a converter at the maximum power point, most of them requiring complicated calculation algorithms. An exception is the

constant voltage or fractional open-circuit voltage method. This

method takes advantage of the fact that the maximum power

is obtained at some fixed fraction (around 80%) of the open

voltage as shown in Fig. 12. The proposed converter employs

this simple method.

Fig. 13 shows the main part of the control circuits for the

MPPT function. The VMON signal is asserted every 20 ms from

an external controller. When VMON is high, the main clock

MCLK stops and the solar cell voltage is sampled. This is an

open voltage because the converter does not drive a load. A

Fig. 14. Circuit configuration during start-up operation.

comparator CMP compares the solar cell voltage (VBAT) with

80% of its open voltage. When VBAT becomes lower than 80%

of its open voltage, the CLK_EN signal becomes low and the

clock signal MCLK halts at a low level. In this situation, more

current is pulled from a solar cell than it can supply. After the

input voltage has recovered, the converter resumes operation.

As a result, the duty ratio is automatically determined to operate

at the maximum solar power.

IV. 0.5-V START-UP CIRCUITS OPERATION AND ANALYSIS

Fig. 14 shows the circuit configuration during start-up. Since

the control circuits are inactive, the main clock MCLK is at

a low level and the rectifier signals CLKX and CLKY are at

a high level. The signal PWS is also at a high level. A ring

oscillator (Ring Osc) supplies a substitute clock signal SCLK

with a 50% duty ratio. Since pMOS transistors PX0 and PY0

are off, an inductor current charges the capacitor CX through the

parasitic PN diodes of PX0 and PY0. In this period, both back

gates of these pMOS transistors PX0 and PY0 are connected to

the DVCCY node.

When the VBAT is higher than 1.5 V, it directly supplies

power to the ring oscillator. In contrast, when it is lower than

1.5 V, a charge pump supplies the power through the VRNG

node. In this case, a charge pump supplies a current ICP to the

capacitor CCP. After the VRNG voltage reaches 1.2 V, the ring

oscillator begins to operate. The ring oscillator raises the voltage

of DVCCY and when it reaches 2.5 V, the feed forward control is activated. As shown later, it takes 20 ms for DVCCY

to rise to 2.5 V when VBAT is 0.5 V. During this period, the

charge pump supplies a current ICP of 0.28 A and the ring

oscillator consumes a current IRNG of 3 A. Therefore, the capacitor CCP must supply the difference of these currents, i.e.,

1938

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 48, NO. 8, AUGUST 2013

Fig. 15. Ring oscillator start-up period analysis.

2.7 A (IRNG-ICP). If the voltage drop of the VRNG during

20 ms is less than 50 mV, the CCP should be larger than

A

(12)

considering the

We selected a four times larger CCP of 4.5

variation of transistor performance and possible different external inductor values.

A waiting time of VRNG to reach 1.2 V occupies almost all

of the start-up time. This wait time

can be expressed by

(13)

,

, and

Substituting

A, we obtain

.

Here, we develop an expression for the DVCCY rising time.

Fig. 15 shows the inductor current at start-up. The converter

operates in the DCM. Since the sub-clock SCLK oscillates at

330 KHz, the cycle time Tcyc is 3 s. An nMOS switch is turned

on during the Ton period, which is equal to a half of the Tcyc.

The inductor current reaches its peak value Ip at the end of the

Ton period and decreases to zero during the

period. Ip and

are given as

(14)

(15)

If all of the inductor current is used to charge the outputs, the

average current Ix of charging the capacitor CX is given by

(16)

However, a half of Ix is wasted by the parasitic PNP transistors

of pMOS transistors PX0 and PY0 as shown in Fig. 14. Therefore, the voltage of DVCCY is expressed as

(17)

(18)

,

,

By substituting the parameters of

, and

s, we obtain the time of 20 ms

for DVCCY to reach 2.5 V.

Fig. 16 shows the circuit configuration of a charge pump and

its back gate voltage controller. The charge pump is composed

of nMOS transistors. When the VBAT is below 1.5 V, the

detector outputs at a high level. In addition, when the VBAT is

higher than 0.5 V, nMOS transistor N1 and pMOS transistors P1

and P2 are turned on. Since the voltage of VP is equal to VBAT,

VBAT is supplied to both the local oscillator and the charge

pump. Voltages VB1 and VB2 are then set as (VBAT-VF). VF

is a forward voltage drop of parasitic PN diodes between the

source and the back gate of transistors P1 and P2. Therefore, all

pMOS transistors in the local oscillator are deeply forward biased. Fig. 17 shows the relationship between the forward back

bias voltages VB2 and VBAT. When the VBAT is lower than

VF, which is around 0.7 V, the forward bias is equal to the

VBAT. In contrast, when the VBAT is higher than VF, the forward bias voltage is fixed to VF. The charge pump supplies

a current to the capacitor CCP, and the capacitor supplies the

power to the ring oscillator through VRNG by pMOS transistor

P3.

When the VBAT is in the range between 1.5 V and 3 V, the

voltages between any nodes of thin oxide transistors must be

lower than the breakdown voltage of 2 V. In this case, transistors P1 and P2 are turned off. The local oscillator and the charge

pump are isolated from the VBAT. The VBAT directly supplies the power to the ring oscillator via VRNG. The back gate

voltage VB1 is set equal to the VBAT. The back gate voltage

VB2 is equal to a half of the VBAT due to the resistors R2.

Since the transistors N1 and N3 are off and N2 is on, the gate

and source voltages of the transistor P2 are also equal to a half

of the VBAT due to the resistors R1. As a result, the voltages

between any nodes in the thin oxide transistors never exceed a

half of the VBAT.

V. IMPLEMENTATION AND EXPERIMENTAL RESULTS

We fabricated a test chip by 190 nm CMOS process technology as shown in Fig. 18. The threshold voltage is 0.7 V and

the active area size is 1.7 mm 0.44 mm.

Fig. 19 shows the measurement and simulation results of the

charge pump supply current. A current of 0.28 A was obtained

at a VBAT of 0.5 V.

Fig. 20 shows the start-up waveforms at the VBAT of 0.5 V.

The charge pump supplied a current to the capacitor CCP. When

its voltage VCP reached 1.2 V, the ring oscillator started to oscillate. The ring oscillator operation time was of the order of ten

milliseconds. This result indicates that the DVCCY is charged

up first. It takes 13 s for the outputs to reach their expected voltages of 3 V and 5 V. This rising interval is almost identical to

the calculated result. After DVCCY reached 2.5 V, the feed forward control (FF-PWM) began to operate.

Fig. 21 shows the waveforms of the feed forward control with

battery operation at a VBAT of 1.5 V. The waveform of the

terminal INDCNT shown in Fig. 6 can be considered an inverse

of the main clock MCLK. When charging VCCX or VCCY, the

amplitude of the waveform of INDCNT is equal to 5 V or 3 V,

respectively. This result shows that VCCY can be charged when

NAKASE et al.: ON-CHIP FEED-FORWARD SIDO BOOST DC-DC CONVERTER

1939

Fig. 16. Circuit configuration of charge pump and back gate controller.

Fig. 17. Back gate bias of pMOS transistors.

Fig. 19. Charge pump supply current.

Fig. 18. Micrograph of SIDO DC-DC converter test chip.

its voltage is lower than 3 V. The ripple voltage is within 50 mV

for each output.

Fig. 22 shows comparison results of the measured and simulated Ton/Toff ratios. The desired ratios were obtained within a

VBAT range of 0.5 V and 2.5 V. In the conventional feed forward control, as the input voltage becomes lower, the Toff period becomes shorter. Therefore, a small error in the Toff period

can cause a large difference in the Ton/Toff ratio. In contrast,

with the proposed control, the impact of any errors in the Toff

Fig. 20. Start-up waveforms at VBAT of 0.5 V. VCP refers to the voltage of

capacitor CCP.

period is small. From (5) and (6), the clock cycle time Tcyc is

given as

(19)

1940

Fig. 21. Feed forward control measured waveforms. Measurement conditions

,

mA, and

mA.

are

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 48, NO. 8, AUGUST 2013

Fig. 23. Experimental results of efficiency and output voltage dependence on

VCCX load current IloadX.

Fig. 22. Comparison of Ton/Toff ratio for each output. Expected VCCX is 5 V.

Fig. 24. Experimental results of efficiency and output voltage dependence on

VCCY load current IloadY.

This indicates that the proposed feed forward control sets the

cycle time longer as the input voltage becomes lower. Therefore, the Toff period also becomes longer compared with the

conventional control.

Figs. 23 and 24 show the measured results of the efficiency

dependence of the VCCX and VCCY on load currents IloadX

and IloadY, respectively. The IloadY is kept at 4 mA (Fig. 23).

The voltage VCCX maintains within 10% of the 5 V target while

supplying 10 mA, 20 mA, and 40 mA of IloadX at VBAT of

1 V, 1.5 V, and 2 V, respectively. The IloadX is kept at 6 mA

(Fig. 24). The voltage VCCY maintains within 10% of the 3 V

target while supplying 15 mA, 40 mA, and more than 50 mA

of IloadY at VBAT of 1 V, 1.5 V, and 2 V, respectively. An

efficiency of 87% was achieved at a VBAT of 2 V and IloadY of

15 mA. The power consumption with zero load current, 0.5 mW,

was measured at the input node.

Fig. 25 shows the line transient results. The VBAT changed

from 1 V to 2 V every 800 s. The rise and fall times of the

VBAT were 17 s. The response is stable even without any compensation. There are no overshoot or undershoot phenomena

when VBAT changed.

Fig. 26 shows the measured results of charging a super capacitor from a solar cell. The solar cell had an open voltage of

1.03 V and a short current of 83 mA under an indoor light condition as shown in Fig. 12. A super capacitor of 0.4 F was attached

to a VCCX and charged from 0 V to 5 V within 80 s. The solar

Fig. 25. Measured waveforms of line regulation. Measured conditions are

mA and

mA. X and Y refer to charging VCCX and

VCCY, respectively.

cell output voltage, which was equal to the VBAT, is stable at

0.77 V due to the implemented constant voltage MPPT control.

VI. SUMMARY

We have proposed an on-chip low power single-inductor

dual-output (SIDO) DC-DC converter for battery and solar

NAKASE et al.: ON-CHIP FEED-FORWARD SIDO BOOST DC-DC CONVERTER

Fig. 26. Experimental results of charging super capacitor with MPPT control.

cell operating sensor network applications. The proposed feed

forward control does not require any phase compensation. In

addition, it determines the Ton/Toff ratio precisely even at a

low input voltage without a linear capacitor. These features

help reduce the cost of external components and process technology. A test chip was fabricated by 190 nm CMOS process

technology and achieved an efficiency of 87% with a small area

size of just 0.75 mm .

For solar cell operation, we were able to achieve 0.5 V

start-up even with a process technology for flash-memory

embedded micro-computers by utilizing the proposed forward

back biased charge pump. A constant voltage algorithm was

implemented as the maximum power point tracking (MPPT)

control. With this MPPT control, a solar cell with an open

voltage of 1.03 V and a short current of 83 mA charged a super

capacitor of 0.4 F up to 5 V within 80 s.

1941

[10] M. K. Kazimierczuk and A. Massarini, Feedforward control of

DC-DC PWM boost converter, IEEE Trans. Circuits Syst., vol. 44,

no. 2, pp. 143148, Feb. 1997.

[11] R. W. Erickson and D. Maksimovic, Fundamentals of Power Electronics, 2nd ed. Norwell, MA, USA: Kluwer, 2001.

[12] K. K. Win, X. Wu, S. Dasgupta, W. J. Wen, R. Kumar, and S. K. Panda,

Efficient Solar Energy Harvester for Wireless Sensor Nodes, in Proc.

ICCS, Nov. 2010, pp. 289294.

[13] Y. Qiu, C. V. Liempd, B. O. Veld, P. G. Blanken, and C. V. Hoof, 5

W-to-10 mW input power range inductive boost converter for indoor

photovoltaic energy harvesting with integrated maximum power point

tracking algorithm, in IEEE ISSCC Dig. Tech. Papers, Feb. 2011, pp.

118119.

[14] P. H. Chen, K. Ishida, X. Zhang, Y. Okuma, Y. Ryu, M. Takamiya, and

T. Sakurai, 0.18-V input charge pump with forward body biasing in

startup circuit using 65 nm CMOS, in Proc. ICC, Sep. 2010.

[15] J. Sankman, H. Chen, and D. Ma, Supercapacitor-based reconfigurable energy management unit for autonomous wireless sensor

nodes, in Proc. IEEE ISCAS, May 2011, pp. 25412544.

[16] S. Kim, K. No, and P. H. Chou, Design and performance analysis of

supercapacitor charging circuits for wireless sensor nodes, IEEE J.

Emerg. Sel. Topics Circuits Syst., vol. 1, no. 3, pp. 391402, Sep. 2011.

[17] P. H. Chen, K. Ishida, K. Ikeuchi, X. Zhang, K. Honda, Y. Okuma, Y.

Ryu, M. Takamiya, and T. Sakurai, A 95 mV-startup step-up converter

with VTH-tuned oscillator by fixed-charge programming and capacitor

pass-on scheme, in IEEE ISSCC Dig. Tech. Papers, Feb. 2011, pp.

216217.

[18] S. Matsumoto and T. Shodai, A novel strategy of a control IC for

boost converter with ultra low voltage input and maximum power point

tracking for single solar cell application, in Proc. ISPSD, Jun. 2009,

pp. 180183.

[19] Y. Nakase, S. Hirose, H. Onoda, Y. Ido, Y. Shimizu, T. Oishi, T.

Kumamoto, and T. Shimizu, A 0.5 V start-up 87% efficiency 0.75

mm on-chip feed-forward single-inductor dual-output (SIDO) boost

DC-DC converter for battery and solar cell operation sensor network

micro-computer integration, in Proc. IEEE CICC, Sep. 2012, pp. 14.

[20] K. Kobayashi, H. Matsuo, and Y. Sekine, A novel optimum operating

point tracker of the solar cell power supply system, in Proc. 35th Annu.

IEEE Power Electron Specialists Conf., Jun. 2004, pp. 21472151.

[21] T. Esram and P. L. Chapman, Comparison of photovoltaic array maximum power point tracking techniques, IEEE Trans. Energy Conv.,

vol. 22, no. 2, pp. 439449, Jun. 2007.

REFERENCES

[1] R. Mittal and M. P. S. Bhatia, Wireless sensor networks for monitoring

the environmental activities, in Proc. ICCIC, Dec. 2010, pp. 15.

[2] J. Byun, B. Jeon, J. Noh, Y. Kim, and S. Park, An intelligent self-adjusting sensor for smart home services based on ZigBee communications, IEEE Trans. Consum. Electron., vol. 58, no. 3, pp. 791802,

Aug. 2012.

[3] M. T. Penella and M. Gasulla, Runtime extension of low-power wireless sensor nodes using hybrid-storage units, IEEE Trans. Instrum.

Meas., vol. 59, no. 4, pp. 857865, Apr. 2010.

[4] N. Sze, F. Su, Y. Lam, W. Ki, and C. Tsui, Integrated single-inductor

dual-input dual-output boost converter for energy harvesting applications, in Proc. IEEE ISCAS, May 2008, pp. 22182221.

[5] C. P. Basso, Switch-Mode Power Supplies. New York, NY, USA:

McGraw-Hill, 2008, ch. 2.

[6] D. Ma, W. H. Ki, C. Y. Tsui, and P. K. T. Mok, Single-inductor multiple-output switching converters with time-multiplexing control in discontinuous conduction mode, IEEE J. Solid-State Circuits, vol. 38, no.

1, pp. 89100, Jan. 2003.

[7] X. Jing, P. K. T. Mok, and M. C. Lee, A wide-load-range single-inductor-dual-output boost regulator with minimized cross-regulation by

constant-charge-auto-hopping (CCAH) control, in Proc. CICC, Sep.

2009, pp. 299302.

[8] H. P. Le, C. S. Chae, K. C. Lee, G. H. Cho, S. W. Wang, G. H. Cho, and

S. Kim, A single-inductor switching DC-DC converter with 5 outputs

and ordered power-distributive control, in IEEE ISSCC Dig. Tech. Papers, Feb. 2007, pp. 534535.

[9] D. Ma, W. H. Ki, and C. Y. Tsui, A pseudo-CCM/DCM SIMO

switching converter with freewheel switching, in IEEE ISSCC Dig.

Tech. Papers, Feb. 2002, pp. 390391.

Yasunobu Nakase received the B.S. and M.S.

degrees in physics from Ritsumeikan University,

Kyoto, Japan, and the Ph.D. degree in electronic

engineering from Osaka University, Osaka, Japan.

He joined Mitsubishi Electric Corp. in 1983. He

worked for research and development of high speed

SRAMs, CMOS arithmetic processing units and high

speed interface circuits. From 2002 to 2008, he transferred temporally to Renesas Design Corp., Hyogo,

Japan, to build an analog design division. He moved

to Renesas Electronics Corp. in 2010. Since then, he

has been a senior engineer for development of analog IPs, especially DC-DC

converters for energy harvesting applications. He is a member of the Institute

of Electronics, Information and Communication Engineers (IEICE) of Japan.

Shinichi Hirose received B.E. degree in Industry

Chemistry from Kyushu Institute of Technology

in 1978 and M.E. degree in Applied Electronics

from the University of Electro-Communications

in 1982. He joined Mitsubishi Electric Corp. in

1982. He worked for development of one chip

MCUs and their embedded analog IPs. He moved to

Renesas Electronics Corp. in 2010. From then, he is

developing DC-DC converters for energy harvesting

applications.

1942

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 48, NO. 8, AUGUST 2013

Hiroshi Onoda received the B.E. and M.E. degrees

in Faculty of Engineering from Osaka University,

Osaka, Japan, in 1981 and 1983, respectively.

He joined Mitsubishi Electric Corp. in 1983. He

worked for research and development of Focused

Ion Beam lithography, flash memory process integration, and HVIC (high voltage analog IC) process

integration. He moved to Renesas Electronics Corp.,

Hyogo, Japan, in 2010. Since then, he has been

working for development of analog IPs, especially

DC-DC converters.

Yasuhiro Ido received the B.E. degree in electrical

and electronic engineering from Tokushima University, Japan, in 1994 and the M.E. degree in energy

engineering and science from Nagoya University,

Japan, in 1996.

He joined Mitsubishi Electric Corp. in 1996. He

worked for research and development of memory

testing. He moved to Renesas Electronics Corp.,

Hyogo, Japan, in 2010. Since then, he has been

working for development of analog IPs, especially

DC-DC converters.

Yoshiaki Shimizu received the B.E. degree in Faculty of Engineering from Kansai University, Japan,

in 1982.

He joined Mitsubishi Electric Corp. in 1982.

He worked for research and development of SoC.

He moved to Renesas Electronics Corp., Hyogo,

Japan, in 2010. Since then, he has been working for

development of several kinds of analog IPs.

Tsukasa Oishi received the B.S. and M.S. degrees

from Shibaura Institute of Technologies, Tokyo,

Japan, in 1985 and 1987, respectively. He received

the Ph.D. degree from Waseda University, Japan, in

2005.

He joined Mitsubishi Electric Corp. in 1987. Since

then, he has been working for R&D of memory (Dynamic RAM and system memory) design. From 1987

to 2002, he developed Dynamic RAM (large scale,

low voltage, multi-function, and system application)

and Magnetic RAM. In 2003, he joined Renesas

Technology Corp., Hyogo, Japan. From 2003 to 2006, he was a manager of

R&D activities for various IPs of microcontroller applications. From 2003 to

2008, he developed Flash memory technology (NOR-type and MONOS-type)

for microcontroller application. From 2006 to 2009, he developed analog

circuit technology for Microcontroller application. In 2010, he joined Renesas

Electronics Corp. From 2010, he is a department manager of the Platform

Integration Division. He is managing R&D activities for various analog IPs and

microcontroller design platform. In the academic area, he is a visiting senior

researcher for system memories and analog IPs in Waseda University.

Toshio Kumamoto received the B.E. and Ph.D.

degrees in electrical engineering from Osaka Prefecture University, Osaka, Japan, in 1983 and 1991,

respectively.

He joined Mitsubishi Electric Corp. in 1983. He

worked for research and development of A/D and

D/A converters. He moved to Renesas Electronics

Corp., Hyogo, Japan, in 2010. Since then, he has

been working for development of several analog IPs

including A/D and D/A converters.

Dr. Kumamoto is a member of the Institute of Electronics, Information and Communication Engineers (IEICE) of Japan.

Toru Shimizu (M86SM05) received the B.S.,

M.S., and Ph.D. degrees in information science from

The University of Tokyo, Japan.

Since 1986, he has been involved in microprocessor, microcontroller and SoC design R&D,

working in Mitsubishi Electric, Renesas Technology,

and Renesas Electronics, Hyogo, Japan. He leads

many design projects of embedded microprocessor

LSIs. Leading edge RISC microprocessors with

embedded DRAM, micro-controllers with embedded

flash memory, multi-core SoCs for embedded processing are some of the project outputs. His R&D activities cover not only LSI

design and architecture but embedded software and application systems.

Dr. Shimizu is a senior member of the IEICE. He is a steering committee

member of the A-SSCC and a director of the Executive Committee.

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Design of 4-Channel RF Remote Control Using DTMF ICsDocument40 pagesDesign of 4-Channel RF Remote Control Using DTMF ICsprateek0291100% (5)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- AMC EtherCATCommunicationManualDocument244 pagesAMC EtherCATCommunicationManualJaziel CabralNo ratings yet

- Technical Instructions For Configuring An S7 ConnectionDocument35 pagesTechnical Instructions For Configuring An S7 ConnectionJaziel CabralNo ratings yet

- Analysis of A Flying Capacitor Converter A Switched Systems ApproachDocument20 pagesAnalysis of A Flying Capacitor Converter A Switched Systems ApproachJaziel CabralNo ratings yet

- PCC Special eDocument18 pagesPCC Special eJaziel CabralNo ratings yet

- What Should You Watch Out For When Setting Up A Connection Between S7 - 200 and SIMATIC Panels or WinCC Flexible PC Runtime and What Are The Options?Document25 pagesWhat Should You Watch Out For When Setting Up A Connection Between S7 - 200 and SIMATIC Panels or WinCC Flexible PC Runtime and What Are The Options?Jaziel CabralNo ratings yet

- Cables Pinout PLC Communication ProgrammingDocument6 pagesCables Pinout PLC Communication ProgrammingJaziel Cabral100% (1)

- Strategic ManagementDocument173 pagesStrategic Managementjirufeleke1428100% (2)

- EtherCAT Introduction RoadshowDocument25 pagesEtherCAT Introduction RoadshowJaziel CabralNo ratings yet

- THEME2 PresentationDocument24 pagesTHEME2 PresentationChirag DaveNo ratings yet

- DH-485 Cables Used With SLC-500 Processors and The 1747Document5 pagesDH-485 Cables Used With SLC-500 Processors and The 1747Jaziel CabralNo ratings yet

- R144-E1-03 - Function Block Structured Text Introduction GuideDocument92 pagesR144-E1-03 - Function Block Structured Text Introduction GuideJaziel CabralNo ratings yet

- 41 E131Document12 pages41 E131Hogj SkyNo ratings yet

- Basic Programming Simatic S7-300Document41 pagesBasic Programming Simatic S7-300Jaziel Cabral100% (1)

- Communication All Cables PLC Pinout (Pinagem de Todos Os Cabos de Comunicação PLC)Document3 pagesCommunication All Cables PLC Pinout (Pinagem de Todos Os Cabos de Comunicação PLC)Jaziel CabralNo ratings yet

- Red - Lion SiemensDocument18 pagesRed - Lion SiemensHerick509No ratings yet

- Ten Keys To Successful Strategic Planning For Nonprofit and Foundation LeadersDocument12 pagesTen Keys To Successful Strategic Planning For Nonprofit and Foundation LeadersJaziel CabralNo ratings yet

- System Manual SIMOCODE Pro enDocument694 pagesSystem Manual SIMOCODE Pro enСтоян Пехливанов100% (1)

- Strategic Planning: 3.1 Outline of ChapterDocument30 pagesStrategic Planning: 3.1 Outline of ChapterMoses OryemaNo ratings yet

- Primavera P6 7.0 Project Management Reference ManualDocument560 pagesPrimavera P6 7.0 Project Management Reference ManualCristian Cornejo Catalán100% (1)

- Universal Serial Bus (USB) To DH-485 InterfaceDocument16 pagesUniversal Serial Bus (USB) To DH-485 InterfaceFeri HandoyoNo ratings yet

- InTech-Lean Six Sigma in The Service IndustryDocument13 pagesInTech-Lean Six Sigma in The Service IndustryJaziel CabralNo ratings yet

- Iec 1131-3Document5 pagesIec 1131-3Jaziel CabralNo ratings yet

- CaboDocument4 pagesCabomurilofesslerNo ratings yet

- CaboDocument4 pagesCabomurilofesslerNo ratings yet

- PLC Communication CableDocument2 pagesPLC Communication CableJaziel CabralNo ratings yet

- Seminar Report On 8051 MicrocontrollerDocument21 pagesSeminar Report On 8051 MicrocontrollerHapi ER50% (2)

- H8 500 Eprom SecurityDocument4 pagesH8 500 Eprom SecurityΠαντελήςΓεωργίουΦλούδαςNo ratings yet

- Heliyon: Sathish Pasika, Sai Teja GandlaDocument9 pagesHeliyon: Sathish Pasika, Sai Teja GandlaAuras PopescuNo ratings yet

- Embedded System ClassificationDocument4 pagesEmbedded System ClassificationkathirdcnNo ratings yet

- Chen, Lin, Liu - Edge Computing Gateway of The Industrial Internet of Things Using Multiple Collaborative MicrocontrollersDocument9 pagesChen, Lin, Liu - Edge Computing Gateway of The Industrial Internet of Things Using Multiple Collaborative MicrocontrollersJose Edson Moreno JuniorNo ratings yet

- PSG Tech ProfileDocument48 pagesPSG Tech ProfileReddy BabuNo ratings yet

- BL808 DatasheetDocument92 pagesBL808 DatasheetJOSE FRANÇANo ratings yet

- Sipeed Maixbit Datasheet V2.0: Key FeaturesDocument6 pagesSipeed Maixbit Datasheet V2.0: Key FeaturesVlad TimisoaraNo ratings yet

- Spru I 11444Document24 pagesSpru I 11444aalvarcaNo ratings yet

- Mini Usb ProgrammatorDocument37 pagesMini Usb ProgrammatorZoran DjukicNo ratings yet

- Faculty Class Alert Using GSMDocument80 pagesFaculty Class Alert Using GSMpraveen_kodgirwarNo ratings yet

- Eps-Bli HYG: User ManualDocument75 pagesEps-Bli HYG: User ManualEwerton BianchiNo ratings yet

- Line Following RobotDocument50 pagesLine Following RobotNorhafizah MokhtarNo ratings yet

- Micro Report PDFDocument68 pagesMicro Report PDFankur mehtaNo ratings yet

- SAMR34 R35 Low Power LoRa Sub GHZ SiP Data Sheet DS70005356B PDFDocument62 pagesSAMR34 R35 Low Power LoRa Sub GHZ SiP Data Sheet DS70005356B PDFEduardo MarquesNo ratings yet

- MonitorDocument86 pagesMonitorsabNo ratings yet

- ST92195C7B1 DatasheetDocument249 pagesST92195C7B1 DatasheetlnedeleaNo ratings yet

- Mbed Course Notes - Timers and InterruptsDocument20 pagesMbed Course Notes - Timers and InterruptszaddlerNo ratings yet

- E Notice Board - 2Document4 pagesE Notice Board - 2Magical MKNo ratings yet

- Digital Image EngineDocument1 pageDigital Image EngineFabioMaranhaoLealNo ratings yet

- Embedded Engineer CVDocument3 pagesEmbedded Engineer CVCharleskiranNo ratings yet

- Iot MajrrDocument25 pagesIot MajrrSrinivas ReddyNo ratings yet

- Design and Construction of A Smart Electric Metering System For Smart Grid Applications Nigeria As A Case StudyDocument9 pagesDesign and Construction of A Smart Electric Metering System For Smart Grid Applications Nigeria As A Case StudyamankusNo ratings yet

- Stm32, The Optimal Platform Choice The Stm32 Key Benefits: 72 MHZ Cortex-M3 Cpu - Wide Selection of DevicesDocument6 pagesStm32, The Optimal Platform Choice The Stm32 Key Benefits: 72 MHZ Cortex-M3 Cpu - Wide Selection of DevicesBa VuVanNo ratings yet

- Cellphone Operated Robotcv - 2vDocument82 pagesCellphone Operated Robotcv - 2vRajasekharreddy KarumuriNo ratings yet

- Axe 003Document1 pageAxe 003albertoacosNo ratings yet

- IEEE PaperDocument4 pagesIEEE PaperArshia TabassumNo ratings yet

- Freescale-HCS12 - S12X-S12P-MC9S12P128-Learning Centre MCU-Application Notes-Freescale - Application - Notes - 1Document14 pagesFreescale-HCS12 - S12X-S12P-MC9S12P128-Learning Centre MCU-Application Notes-Freescale - Application - Notes - 1Phạm QuangNo ratings yet