Professional Documents

Culture Documents

2.Linear-Integrated-Circuits-Lab V+

Uploaded by

ECEOCETCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

2.Linear-Integrated-Circuits-Lab V+

Uploaded by

ECEOCETCopyright:

Available Formats

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

CHENDU COLLEGE OF ENGINEERING

AND TECHNOLOGY

ZAMIN ENDATHUR, MADURANTAKAM,

KANCHEEPURAM-603311.

DEPARTMENT OF ELECTRONICS AND

COMMUNICATION ENGINEERING

147452-LINEAR INTEGRATED CIRCUITS LAB

IV SEMESTER- ECE

(AS PER THE REVISED SYLLABUS OF ANNA UNIVERSITY OF

TECH)

www.vidyarthiplus.com

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

INDEX

EXPT.NO

NAME OF THE EXPERIMENT

PAGE

NO

INVERTING, NON-INVERTING AND

DIFFERENTIAL AMPLIFIERS USING OP-AMP

INTEGRATOR AND DIFFERENTIATOR USING OPAMP.

INSTRUMENTATION AMPLIFIER

13

ACTIVE LOWPASS, HIGH PASS AND BAND PASS

FILTER USING OP-AMP.

17

ASTABLE, MONOSTABLE MULTIVIBRATOR AND

SCHMITT TRIGGER USING OP-AMP.

25

RC PHASE SHIFT AND WIEN BRIDGE

OSCILLATOR

USING OP-AMP

35

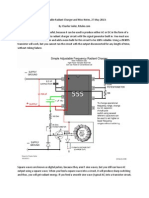

ASTABLE & MONOSTABLE MULTIVIBRATOR

USING IC 555 TIMER.

41

PLL CHARACTERISTICS AND FREQUENCY

49

MULTIPLIER USING PLL

9

DC POWER SUPPLY USING LM317 AND LM723

53

10

STUDY OF SMPS

59

11

SIMULATION OF EXPERIMENTS 3,4,5,6,7 USING

61

PSPICE NETLISTS

12

ADDITION EXPERIMENTS AND VIVA VOCE

79

QUESTIONS & ANSWERS

www.vidyarthiplus.com

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

INVERTING AMPLIFIER:CIRCUIT DIAGRAM:-

Rf

+15v

R1=10K

IC 741

Signal

Generator

Vin

+

CRO

-15v

TABULATION:

S.No

Rf (K)

1.

1K

2.

10K

3.

33K

4.

100K

Vin (Volts)

Vout (Volts)

Theoretical Gain

A = -Rf / R1

Practical Gain

A = V0 / Vin

MODEL GRAPH:

Vin

INPUT

Time (ms)

Vout

OUTPUT

Time (ms)

www.vidyarthiplus.com

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

INVERTING, NON-INVERTING AND DIFFERENTIAL

AMPLIFIERS USING OP-AMP

EXP.NO: 01

DATE:

AIM:

To design the Inverting, Non-Inverting and Differential Amplifiers using

Op-amp IC741 and test their performance.

APPARATUS REQUIRED:

S.NO

COMPONENTS

RANGE

QUANTITY

01

EACH 01

EACH 02

01

1.

IC 741

2.

RESISTORS

3.

DIGITAL TRAINER KIT

1K, 33K

10K, 100 K.

---

4.

SIGNAL GENERATOR

(0-3)MHz

01

5.

CATHODE RAY OSCILLOSCOPE

(0-30)MHz

01

6.

CONNECTING WIRES

---

FEW

THEORY:

Op-amp in open-loop configuration has a very few application because

of its enormous open-loop gain. Controlled gain can be can be achieved by taking a

part of output signal to the input with the help of feedback. This is called as ClosedLoop Configuration. The three basic types of closed-loop amplifier configuration

are: 1. Inverting amplifier.

2. Non-inverting amplifier.

3. Differential amplifier.

The entire configuration can be operated with either AC or DC input.

INVERTING AMPLIFIER:If the input signal is applied to the inverting terminal through an input

resistance, a part of output is feedback to the inverting terminal through feedback

resistance Rf and the non-inverting terminal grounded, then the configuration is said

to be Inverting Amplifier. It provides 1800 phase shift or polarity reversal for the

given input.

The circuit closed-loop voltage gain is

Avcl

Rf

.

R1

www.vidyarthiplus.com

Integrated Circuits. www.vidyarthiplus.com

Dept of Electronics & Communication Engg

NON-INVERTING AMPLIFER:147452-Linear

CIRCUIT DIAGRAM:Rf

+15v

R1=10K

+

2

3

Signal Vin

Generator -

7

IC 741

+

CRO

-15v

TABULATION:

S.No

Rf (K)

1.

1K

2.

10K

3.

33K

4.

100K

Vin

(Volts)

Vout

(Volts)

Theoretical Gain

A = 1+(Rf / R1)

Practical Gain

A = V0 / Vin

MODEL GRAPH:

Vin

INPUT

Time (ms)

OUTPUT

Vout

Time (ms)

www.vidyarthiplus.com

Integrated Circuits. www.vidyarthiplus.com

Dept of Electronics & Communication Engg

THEORY (NON-INVERTING AMPLIFIER):-

147452-Linear

If the input signal is given to non inverting terminal & the feedback

from output is connected to inverting terminal of an op-amp through a potential

divider network, then it is called as Non-Inverting Amplifier Configuration. It

operates in a same way as a voltage follower (unity gain buffer), except that the

output voltage is potentially divided before it is fedback to the inverting input

terminal. No phase shift or change in the circuit closed loop polarity occurs voltage

gain is Avcl 1

Rf

R1

PROCEDURE-(INVERTING & NON-INVERTING AMPLIFIER):1. Select R1 as a constant value and choose a value of Rf.

2. Connect the circuit as per as the circuit diagram.

3. Apply the constant amplitude input voltage to the circuit.

4. Measure the output voltage amplitude for different value of Rf from CRO.

5. Calculate the practical gain for different value of Rf & compare it with

theoretical gain.

6. Practical gain & theoretical gain should be approximately equal.

7. Plot the graph of the input wave versus output wave for any one practical case.

www.vidyarthiplus.com

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

DIFFERENTIAL AMPLIFIER:CIRCUIT DIAGRAM:Rf=R2=100K

+15v

R1=10k

Signal

Generators

+

~

Vin1

R1=10K

Vin2

7

IC 741

+

3

4

R2=100K

-15v

+

CRO

-

TABULATION:

S.No

Vin1

(Volts)

Vin2

(Volts)

Vin2 - Vin1

(Volts)

V0

(Volts)

Theoretical Gain

A = -Rf / R1

Practical Gain

A=V0 / (Vin2 - Vin1)

1.

2.

3.

www.vidyarthiplus.com

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

THEORY-(DIFFERENTIAL AMPLIFIER):A

configuration

which

combines

inverting

&

non-inverting

configuration with both input terminals are supplied with Vin1 & Vin2, then it is

called as Differential Amplifier configuration. This circuit amplifies the difference

between the two inputs. Differential amplifier with a single op-amp has the exact gain

of an inverting amplifier and it is given as

AD (Using One Op-Amp)

AVCL

Vo

(Vin1 Vin 2 )

Rf

R1

A differential amplifier with two op-amps has the exact gain of a non-inverting

amplifier and it is given as:

AD (Using Two Op-Amps)

AVCL

Vo

(Vin1 Vin 2 )

Rf

.

R1

PROCEDURE:

1. Select the value of R1, R2, R3 & Rf such that R1=R2 and R3=Rf.

2. Connect the circuit as per as the circuit diagram.

3. Provide constant input voltage Vin1 to Non-inverting terminal of op-amp

through R1 & constant input voltage Vin2 to inverting terminal of op-amp

through R2.

4. Measure the output voltage using CRO.

5. Calculate the theoretical gain and compare it with practical gain.

6. Practical gain & theoretical gain should be approximately equal.

7. Plot the graph of the input wave versus output wave for any one practical case.

RESULT:

Thus the Inverting, Non-Inverting and Differential Amplifiers are

designed and their performance was successfully tested using op-amp IC 741.

www.vidyarthiplus.com

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

INTEGRATOR:CIRCUIT DIAGRAM:Cf=0.01uf

Rf=15k

+15v

2 7

IC 741

R1=1.5k

Signal

Generators

+

Vin

1.5K

Rcomp

+

RL=10k

-15v

CRO

-

TABULATION:

S.No

Frequency

(Hz)

Output Voltage

(Volts)

Gain = 20 log (V0 /Vin)

(dB)

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

MODELGRAPH:

www.vidyarthiplus.com

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

INTEGRATOR AND DIFFERENTIATOR USING OP-AMP.

EXP.NO: 02

DATE:

AIM:

To design an Integrator and Differentiator using op-amp IC 741 and to test their

performance.

APPARATUS REQUIRED:

S.NO

COMPONENTS

RANGE

QUANTITY

---

01

100 , 1.5K

Each 02

10K, 15K

Each 01

0.1f, 0.01f

Each 01

0.001f,

05

1.

IC 741

2.

RESISTORS

3.

CAPACITOR

4.

DIGITAL TRAINER KIT

---

01

5.

6.

SIGNAL GENERATOR

(0-3)MHz

01

CATHODE RAY OSCILLOSCOPE

01

7.

CONNECTING WIRES

(0-30)MHz

---

FEW

THEORY (INTEGRATOR):A circuit in which the output voltage waveform is the integral of the

input voltage waveform is the integrator or integration amplifier; Such a circuit is

obtained by using basic inverting amplifier configuration, if the feed back resistor R f

is replaced by a capacitor Cf. The Output voltage expression is given as

VO

1

R1C f

Vin dt

C.

The frequency of input at which the gain is 0 db is given as fb

1

2 R1C f

The point up to which the gain is constant & maximum is called as gain limiting

frequency & given as fa

1

2 Rf C f

Where Rf is the feedback resistor used to correct

the stability & roll-off problems. Between fa & fb the circuit acts as an integrator and

it is similar to a LPF. Integrator is most commonly used in analog computers, A/D

converter & signal wave shaping circuits.

Integrator as LPF (Characteristics of integrator)

Design of integrator with a lower frequency (Break Frequency) limit of

integration at fa = 1 KHz & the frequency at which 0dB results fb = 10 KHz.

PROCEDURE:

1. From the given frequency fa & fb, the values of Rf, Cf, R1 & Rcomp are

calculated as given in the design procedure.

2. Connect the circuit as shown in the circuit diagram.

3. Apply the sinusoidal input as the constant amplitude to the inverting terminal

of op-amp.

4. Gradually increase the frequency & observe the output amplitude.

5. Calculate the gain with respect to frequency & plot its graph.

10

www.vidyarthiplus.com

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

CIRCUIT DIAGRAM:

Cf=0.005f

Rf=1.5k

R1=100 C1=0.1f

+

Signal

Generators

+15v

7

IC 741

ROM=100

R3=10K

-15v

+

CRO

-

TABULATION:

1.

Frequency (Input)

2.

Input Voltage (Vin peak)

3.

Input Time Period (tVin)

4.

Output Voltage (Vout peak)

5.

Output Time Period (tVo)

MODEL GRAPH:

(i) SINE WAVE INPUT

www.vidyarthiplus.com

11

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

THEORY- (DIFFERENTIATOR):A differentiator or differentiation amplifier is a circuit which performs

the mathematical operation of differentiation; that is, the output waveform is the

derivative of the input waveform. The differentiator may be constructed from the

basic inverting amplifier if an input resistor R1 is replaced by capacitor C1. The

differentiation is very useful to find the rate at which a signal varies with time. For

maintaining the stability of differentiator, a series resistor R1 is connected with input

capacitor C1. the circuit will provide differentiation function but only over a limited

frequency range & over this range differentiator tend to oscillate (or) poor stability

results. The expression for output voltage is Vo

R f C1

dVin

dt

PROCEDURE:

1. Select fa equal to the highest frequency of the input signal to be differentiated.

Calculate the component values of C1 & Rf.

2. Choose fb = 20fa & calculate the values of R1 & Cf, so that R1C1=Rf Cf.

3. Connect the components as shown in the circuit diagram.

4. Apply a sinusoidal & square wave input to the inverting terminal of op-amp

through R1 C1.

5. Observe the shape of the output signal for the given input in CRO.

6. Note down the reading and plot the graph of input versus output wave for both

cases.

(ii) SQUARE WAVE INPUT

www.vidyarthiplus.com

12

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

DESIGN PROCEDURE-(INTEGRATOR):Design of integrator to integrate at cut-off frequency 1 KHz.

Take fa =

1

2 Rf C f

= 1KHz.

Always take Cf < f and

Let Cf = 0.01f

Rf =

1

2 C f fa

Rf = 15.9K

Rf = 15K

Take fb =

R1 =

1

= 10KHz.

2 R1C f

1

= 1.59K.

2 fbC f

R1 1.5K

Rcomp = R1 // Rf =

R1 R f

R1

Rf

R1, Assume RL = 10K

Rcomp = 1.5K

DESIGN PROCEDURE-(DIFFERENTIATOR):Design a differentiator to differentiate an input signal that varies in frequency

from 10Hz to 1KHz. Apply a sine wave & square wave of 2Vp-p & 1KHz frequency

& observe the output.

To find Rf & C1

Given: fa = 1KHz.

fa =

1

2 R f C1

fa = 1KHz.

Assume C1 = 0.1f

Rf = 1.59K 1.5K

www.vidyarthiplus.com

13

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

To find R1 & Cf

Select fb = 20fa with R1 C1 = Rf Cf

fb = 20KHz =

1

2 R1C1

R1 = 79.5 100

RC

82 X 0.1X 10

Cf = 1 1 =

Rf

1.5K

Cf = 0.005f.

Rom R1 // Rf = 100

SINE WAVE INPUT:

Vp-p = 2V

f=1KHz

Vp = 1V,

Vin = Vp sin

= sin (2 )(103)t

Vo = -Rf c1

dVin

dt

= -(1.5K) (0.1f)

d

[sin [(2 )(103)t]

dt

= -(1.5K) (0.1f) (2 ) (103) cos [(2 )(103)t]

= - 0.94 cos [(2 )(103)t]

RESULT:

Thus an Integrator and Differentiator using op-amp are designed and their

performance was successfully tested using op-amp IC 741.

www.vidyarthiplus.com

14

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

CIRCUIT DIAGRAM:

+15v

3

Rf=1K

IC 741

6

+15v

R2=1K

-15v

R1=1K

IC 741

RG 22K

+

V1

-

R1=1K

-15v

R2=1K

+15v

2

+

R1=1K

V

-

IC 741

+

V2

-

-15v

www.vidyarthiplus.com

15

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

INSTRUMENTATION AMPLIFIER

EXP.NO: 03

DATE:

AIM:

To construct and test the CMRR of an instrumentation amplifier using op-amp

IC741.

APPARATUS REQUIRED:

S.NO

COMPONENTS

1.

IC 741

2.

RESISTORS

3.

RANGE

QUANTITY

03

1K.

22K

06

01

DIGITAL TRAINER KIT

---

01

4.

SIGNAL GENERATOR

(0-3)MHz

02

5.

CATHODE RAY OSCILLOSCOPE

01

6.

CONNECTING WIRES

(0-30)MHz

---

FEW

THEORY:

An instrumentation amplifier is the intermediate stage of a instrumentation

system. The signal source of the instrumentation amplifier is the output of the

transducer. Many transducers output do not have the ability or sufficient strength to

drive the next following stages. Therefore, instrumentation amplifiers are used to

amplify the low-level output signal of the transducer so that it can drive the following

stages such as indicator or displays.

The major requirements of a instrumentation amplifier are precise,

low-level signal amplification where low-noise, low thermal and time drifts, high

input resistance & accurate closed-loop gain, low power consumption, high CMRR &

high slew rate for superior performance.

www.vidyarthiplus.com

16

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

TABULATION:

COMMON MODE GAIN CALCULATION AC

S.No

RG

(K)

VI

(Volts)

V2

(Volts)

Vo

(Volts)

Ac =

Vo

V1 V2

2

1.

2.

3.

4.

5.

DIFFERENTIAL MODE GAIN AD & CMRR CALCULATION.

S.No

RG (K)

V1

(Volts)

V2

(Volts)

Vo

(Volts)

Ad =

Vo

V1 V2

CMRR =

20 log ( Ad

)(dB)

Ac

1.

2.

3.

4.

5.

www.vidyarthiplus.com

17

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

PROCEDURE:

1. Select the entire resistor with same value of resistance R. Let RG be the gain

varying resistor with different values of resistance for simplicity let RG, be a

constant value.

2. Connect the circuit as shown in the circuit diagram.

3. Give the input V1 & v2 to the non-inverting terminals of first & second opamp respectively.

4. By varying the value of RG, measure the output voltage for common mode and

differential mode operation. Since RG is selected as constant value, provide

different input value of V1 & V2.

5. Calculate the differential mode gain Ad and common mode gain Ac to

calculate the CMRR as CMRR=20 log

Ad

.

Ac

RESULT:

Thus an instrumentation amplifier was constructed and CMRR is

tested using op-amp IC 741.

www.vidyarthiplus.com

18

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

LOWPASS FILTER:CIRCUIT DIAGRAM:R1=27K

RF=20K

+15v

2

Signal

Generator

+

Vin

1.5K

3

0.1uf

7

IC 741

6

RL=10K

-15v

+

CRO

-

TABULATION:

S.No

Frequency

(Hz)

Output Voltage

(Volts)

Gain = 20 log (V0 /Vin)

(dB)

1.

2.

3.

4.

5.

6.

7.

8.

9.

10.

MODEL GRAPH:

www.vidyarthiplus.com

19

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

ACTIVE LOWPASS, HIGH PASS AND BAND PASS FILTER

USING OP-AMP.

EXP.NO: 04

DATE:

AIM:

To design an Active Lowpass and Band Pass Filter using op-amp and to test

their performance

APPARATUS REQUIRED:

S.NO

COMPONENTS

RANGE

QUANTITY

---

02

1.5 K,22K, 27K

EACH 02

10K

01

0.1f, 0.01f

01

1.

IC 741

2.

RESISTORS

3.

CAPACITORS

4.

DIGITAL TRAINER KIT

---

01

5.

SIGNAL GENERATOR

(0-3)MHz

01

6.

CATHODE RAY OSCILLOSCOPE

(0-30)MHz

01

7.

CONNECTING WIRES

---

FEW

THEORY (ACTIVE LPF):A filter circuit which allows only low frequency range up to a higher

cut-off frequency fH is called as Low Pass Filter. An active filter uses transistor and

components such as resistor & capacitor for its design. An active filter offers the

following advantages over a passive filter.

1. Gain & frequency adjustment flexibility.

2. No loading problem because of high input impedance & low output impedance.

3. More economical because of variety of op-amps and absence of inductors.

From the frequency response, when f<fH; the gain is maximum lAl. When

f=fH; the gain is 70.7% of the maximum gain

A

2

and when f

fH; the gain drops or

rolls off. The frequency range from 0 to fH is called as Passband & fH to

is called

as Stopband. Out of Butterworth, chebyshev & cauer filters, Butterworth filter is

preferred because it has flat pass band as well as flat stop band (flat-flat) filter.

www.vidyarthiplus.com

20

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

CIRCUIT DIAGRAM - (HIGH PASS FILTER):R1=27K

RF=22K

+15v

2

Signal

Generator

+

Vin

0.1f

3

7

IC 741

6

RL=10K

1.5K

TABULATION:

Frequency

S.No

(Hz)

1.

-15v

Output Voltage

(Volts)

+

CRO

-

Gain = 20 log (V0 /Vin)

(dB)

2.

3.

4.

5.

6.

7.

8.

9.

10.

MODEL GRAPH:

www.vidyarthiplus.com

21

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

THEORY- (ACTIVE HPF):An active high pass filter is simply formed by interchanging the

frequency determining resistor and capacitor in lowpass filter. A filter circuit which

allows only high frequency range greater then a lower cut-off frequency fL is called

as HIGH PASS FILTER. From the frequency response, when f<fL; the gain

gradually increases from the lowest value. When f = fL; the gain reaches 70.7% of the

maximum gain

A

2

and when f > fL, the gain is maximum lAl. The frequency range

from 0 to fL is called as Stopband & fL to

is called as Passband. (This is exactly

opposite to active LPF)The order of the filter tells the roll-off rate at stop band. Order

n = 1 indicates -20dB / dec (-6db / octave); Order n = 2 indicates -40dB / dec & so on.

Higher the order of the filter, better the quality will be & complex the circuit will be.

DESIGN PROCEDURE: (ACTIVE HPF):

Design a HPF at cutoff frequency fL of 1KHZ & P.B gain of 2. Follow the same

procedure as LPF & interchange the R & C position with capacitor first & resistor in

parallel.

In high pass filter Theoretical gain is given as

Vo

Vin

Af ( f / f L )

1 ( f / f H )2

PROCEDURE - (LPF & HPF):

1. Connect the circuit as shown in the circuit diagram.

2. Select the corresponding cut-off frequency (higher or lower) and determine the

value of C&R. select the value of R1 & Rf depending on desired passband

gain Af..

3. Apply a constant voltage input sinusoidal signal to the non-inverting terminal

of op-amp.

4. Tabulate the output voltage Vo with respect to different values of input

frequency.

5. Calculate passband gain and plot the graph of frequency versus voltage gain &

check the graph to get approximately the same characteristic as shown in the

model graph.

www.vidyarthiplus.com

22

147452-Linear

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Integrated Circuits.

CIRCUIT DIAGRAM: (BANDPASS FILTER)

R1=27K

R1=27K

RF=20K

RF=20K

+15v

+15v

2

Signal

Generator

0.1uf

Vin

1.5K

0.01uf

1.5K

IC 741

IC 741

3

-15v

CRO

-15v

RL=10K

TABULATION:

S.No

Frequency

(Hz)

Output Voltage

(Volts)

Gain = 20 log (V0 /Vin)

(dB)

MODEL GRAPH:

www.vidyarthiplus.com

23

147452-Linear

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Integrated Circuits.

THEORY (ACTIVE BANDPASS FILTER):A filter which has a pass band between two cut-off frequencies fH & fL

is called as Bandpass filter. Where fH > fL BPF is basically of two types

(i) Wide band pass filter. (ii) Narrow band pass filter.

Based on figure of merit or quality factor Q, the types are classified as follows. If

Q<10, selectivity is poor & allows higher bandwidth & such BPF is called as wide

BPF.

If Q > 10, selective is more and allows only narrow bandwidth & such

BPF is called as Narrow BPF. Relationship between Q & center frequency fC is

given as

fc

BW

fc

fH

&

fL

fc

fH fL

When frequency fL < f < fH then gain is maximum. At f < fL the gain is

gradually increasing (positive roll-off) from lower value & at f > fH the gain is

gradually decreasing (Negative roll-off) & exactly when f = fL & f = fH the gain is

70.7% of maximum gain

A

2

PROCEDURE:

1. Select the lower and higher cut-off frequency and calculate the value of R & C

for the given frequencies.

2. Design for LPF & HPF separately and then combine the circuit by first placing

the HPF followed by a LPF (i.e) HPF in series with LPF.

3. Connect the circuit as shown in the circuit diagram.

4. Apply a constant voltage input sinusoidal signal to the non-inverting terminal

of op-amp.

5. Tabulate the output voltage Vo with respect to different values of input

frequency.

6. Calculate passband gain and plot the graph of frequency versus voltage gain &

check the graph to get approximately the same characteristic as shown in the

model graph.

www.vidyarthiplus.com

24

147452-Linear

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

DESIGN PROCEDURE - (ACTIVE BPF):-

Integrated Circuits.

Design a BPF to pass a band of 1KHz to 10KHz with a passband gain of 4.

1. Select the highest cut-off frequency of LPF as fH = 10 KHz and the lowest cutoff frequency of HPF as fL = 1 KHz.

2. Design the HPF first by taking fL = 1KHz. Assume the value of C < 1f.

Let C = 0.1f.

3. Calculate R from the expression.

1

1

FL =

;

Therefore R1 =

2 f LC

2 RC

R=

1

;

2 (1KHz )(0.1X 10 6 )

R = 1.59K R=1.5K

4. Then design the LPF by taking fH = 10KHz. Assume the value of C < 1f. Let

C = 0.01f.

5. Calculate R from the expression fH =

R=

1

1

; Therefore R =

2 fHC

2 RC

1

;

2 (10 KHz )(0.01X 10 6 )

R = 1.59K R=1.5K

6. Calculate the values of Rf & R1 with the use of pass band gain.

Overall P.B gain of BPF = 4 = 2 (HPF) X 2 (LPF)

Therefore for both HPF & LPF the value of Rf = R1 to obtain a individual

P.B gain of 2.

Af = (1+

Rf

) = 2 (for HPF)

R1

Rf

) = 2 (for LPF)

R1

Let Rf = R1 = 22K.

Af = (1+

7. Q of the filters is calculated as

Where fC =

fc

fc

=

B.W

fH fL

f H f L is the center frequency.

8. Cascade HPF & then LPF to form BPF.

Calculate the practical gain dB using 20 log (Vo/Vin)

Vo

And Theoretical gain is

=

Vin

Af T (

[1

www.vidyarthiplus.com

f

)

fL

f 2

f 2

) ][1 (

) ]

fH

fL

25

147452-Linear

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

DESIGN PROCEDURE (ACTIVE LPF):

Integrated Circuits.

Design a LPF at cutoff frequency fH of 1KHz with a passband gain of 2.

1. Choose the given value of fH = 1KHz.

2. Select the value of C < 1f

1

2 RC

1

R=

2 fHC

3. Assume C = 0.1f. Calculate R from FH =

R=

R = 1.5K

1

= 1.5K

2 X 1X 10 3 X 0.1 f

C = 0.1f

4. Determine the value of R1 & Rf from pass band gain of the filter.

Rf

Af = 1 +

= 2.

R1

Therefore Rf =R1 to select Af = 2.

Assume Rf = R1 = 22K

&

Assume RL = 10K

5. Calculate the practical gain in dB using Gain (dB)=20log (Vo/Vin);

Theoretical gain is given as

Vo

=

Vin

Af

1 ( f / f H )2

Af P.B gain.

f Input frequency.

fH Higher cut-off frequency of LPF.

RESULT:

Thus an Active Lowpass, High pass and Band Pass Filters are designed

and tested using op-amp IC 741.

www.vidyarthiplus.com

26

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

CIRCUIT DIAGRAM - (ASTABLE):R=47K

+15v

0.01uf

Vc

7

IC 741

R2=DRB

+

CRO

Vref

R1=10K

TABULATION:

Waveforms

Amplitude

(volts)

DESIGN VALUE

tH

tL

(ms)

(ms)

(ms)

OBSERVED VALUE

F

(Hz)

tH

tL

(ms)

(ms)

(ms)

F

(Hz)

Output

waveform

Capacitive

waveform

MODEL GRAPH:

www.vidyarthiplus.com

27

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

ASTABLE, MONOSTABLE MULTIVIBRATOR AND

SCHMITT TRIGGER USING OP-AMP.

EXP.NO: 05

DATE:

AIM:

To design an Astable, Monostable multivibrator and Schmitt trigger

using op-amp IC 741 and to test their characteristics.

APPARATUS REQUIRED:

S.NO

COMPONENTS

RANGE

QUANTITY

---

01

100, 100K,

10K, 47K,

EACH 01

EACH 03

(0-10)M

01

0.01f, 0.1f

01

1N4007

02

1.

IC 741

2.

RESISTORS

3.

DRB

4.

CAPACITORS

5.

DIODE

6.

DIGITAL TRAINER KIT

---

01

7.

SIGNAL GENERATOR

(0-3)MHz

01

7.

CATHODE RAY OSCILLOSCOPE

(0-30)MHz

01

8.

CONNECTING WIRES

---

FEW

THEORY-(ASTABLE MULTIVIBRATOR):An op-amp Astable multivibrator is also called as free running

oscillator. The basic principle of generation of square wave is to force an op-amp to

operate in the saturation region (Vsat). A fraction =

R2

of the output is

R1 R 2

fedback to the positive input terminal of op-amp. The charge in the capacitor

increases & decreases upto a threshold value called Vsat. This charge in the

capacitor triggers the op-amp to stay either at +Vsat or Vsat. Asymmetrical square

wave can also be generated with the help of zener diodes. Astable multivibrator do

not require a external trigger pulse for its operation & output toggles from one state to

another and does not contain a stable state. Astable multivibrator are mainly used in

timing applications & waveforms generators.

www.vidyarthiplus.com

28

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

DESIGN PROCEDURE:Design of square wave generator at f0 = 1 KHz.

1. The expression of fo is obtained from the charging period t1 & t2 of capacitor

as fo =

1

2 RC ln[1 (2 R1 / R2 )]

2. To simplify the above expression, the value of R1 & R2 should be taken as R2

= 1.16R1, such that fo simplifies to fo =

1

2 RC

3. Assume the value of R1 = 10K and find R2.

R2 = 1.16K (10K)

R2 = 11.6K (DRB)

4. Assume the value of C & Determine R from fo =

1

2 RC

Let C = 0.01f

R=

1

1

=

3

2 f oC

2 X (1X 10 )(0.01X 10 6 )

R = 50K R = 47K

5. Calculate the threshold point from

lVTl or lVSATl =

R1

lVSATl where is the feedback ratio.

R1 R 2

www.vidyarthiplus.com

29

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

PROCEDURE:

1. Calculate the value of components using the design procedure given.

2. Connect the circuit as per as the circuit diagram.

3. As there is no specific input signal for this circuit switch ON the power

supply.

4. Note down the reading for output square wave (i.e) time & amplitude and

tabulate it.

5. Note down the reading for capacitor voltage & tabulate it.

6. Plot the reading in the graph and compare it with model graph.

www.vidyarthiplus.com

30

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

CIRCUIT DIAGRAM - (MONOSATBLE):

RF=R3=47K

+15v

2

R3=47K

IC 741

C=0.01uf

D1

6

R1=10K

-15V

+

CRO

D2

C1=0.1uf

R2=10K

Triggering

Input

Vin

R4=100

TABULATION:

Amplitude

(volts)

S.No

Waveforms

1.

Input waveform

2.

Output waveform

3.

Capacitive waveform

Time period

(ms)

MODEL GRAPH:

INPUT

TIME (ms)

AMPLITUDE

OUTPUT

TIME (ms)

www.vidyarthiplus.com

31

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

THEORY - (MONOSTABLE MULTIVIBRATOR):A multivibrator which has only one stable and the other is quasi-stable

state is called as Monostable multivibrator or one-short multivibrator. This circuit is

useful for generating single output pulse of adjustable time duration in response to a

triggering signal. The width of the output pulse depends only on the external

components connected to the op-amp. Usually a negative trigger pulse is given to

make the output switch to other state. But, it then returns to its stable state after a time

interval determined by circuit components. The pulse width T can be given as T =

0.69RC. For Monostable operation the triggering pulse width Tp should be less then

T, the pulse width of Monostable multivibrator. This circuit is also called as time

delay circuit or gating circuit.

DESIGN PROCEDURE:

1. Assume R1 = R2 = 10K & calculate from expression

R1

10 K

=

=

= 0.5.

R1 R 2 20 K

2. Find the value of R & C from the pulse width time expression.

(1 V D / Vsat )

1

(1 V D / Vsat )

T = RC ln

0.5

T 0.69RC.

T = RC ln

3. Assume c = 0.01f and R = 50K 47K. Find T where Rf = R3 = R

T = 0.69 (50X103) (0.01X10-6)

T = 0.345ms.

4. Triggering pulse width Tp must be much smaller than T. Tp < T.

5. Assume a HPF in the input session with C1=0.1f (Assumption) & R4 = 100.

PROCEDURE:

1. Calculate the value of components using the design procedure given.

2. Connect the circuit as per as the circuit diagram.

3. Apply the negative trigger voltage to the non-inverting terminal.

4. Note down the reading for output voltage Vo & ON & OFF time period &

tabulate it.

5. Note down the reading for capacitor voltage & tabulate it.

6. Plot the reading in the graph and compare it with model graph.

www.vidyarthiplus.com

32

147452-Linear

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Integrated Circuits.

SCHMITT TRIGGER:CIRCUIT DIAGRAM:+15v

7

IC 741

ROM=R1//R2

10K

3

+

Vin

-15V

RL=10K

R2=100K

R1

+

CRO

-

10K

TABULATION:

I/P Voltage

(Volts)

I/P Time

(ms)

VUT (UTP) VLT (LTP)

(Volts)

(Volts)

O/P

Voltage

(ms)

O/P Time

(ms)

MODEL GRAPH:

www.vidyarthiplus.com

33

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

THEORY-(SCHMITT TRIGGER):A circuit which converts a irregular shaped waveform to a square wave

or pulse is called a Schmitt trigger or squaring circuit. The input voltage Vin triggers

the output Vo every time it exceeds certain voltage levels called upper threshold

voltage VUT and lower threshold voltage VLT. The threshold voltages are obtained by

using the voltage divider. A comparator with positive feedback is said to exhibit

hysteresis, a dead band condition. The hysteresis voltage is the difference between

VUT & VLT.

There are two types of Schmitt trigger based on where the irregular wave is

given. They are, Inverting & non-inverting Schmitt trigger. Schmitt trigger finds

application in wave shaping circuits. The other name given to Schmitt trigger is

regenerative comparator.

www.vidyarthiplus.com

34

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

DESIGN PROCEDURE:1. Select the desire value of Vut & Vlt with same magnitude & opposite polarity.

Let Vut = 1V & Vlt = -1V.

2. For Op-amp 741C Vsat 13V to 14V. And assume Vref = 0, Since the

another end of R1 is grounded.

3. if Vo = +Vsat the voltage at the positive terminal will be (voltage from

potential divider R1 & R2).

Vut = Vref +

R1

(Vsat - Vref )

R1 R 2

Therefore Vref = 0.

Vut =

R1

(+ Vsat).

R1 R 2

4. Similarly Vlt will be Vlt = (

R1

) Vsat.

R1 R 2

5. Sub Vut & assume R1 or R2 & find the other component value.

1V =

R1

(13)

R1 R 2

R1 + R2 = 13R1

if R1 = 10K then R2 = 120K 100K.

R2 = 12R1

6. Calculate ROM by

ROM = R1 // R2 =

ROM =

1000 K

110 K

R1R 2

R1 R 2

(10 K )(100 K )

.

110 K

10K. & select RL = 10K (Assumption)

7. Calculate hystersis voltage

Vhy = Vut Vlt

=

=

R1

[+Vsat (-Vsat)]

R1 R 2

10 K

[26V]

110 K

Since Vsat = 13V

= 0.0909 [26V]

Vhy = 2.363V

www.vidyarthiplus.com

35

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

PROCEDURE:

1. Design the value of circuit components and select VUT & VLT as given in the

design procedure.

2. Connect the circuit as shown in the circuit diagram.

3. Apply the input signal to the input terminal of op-amp & set VUT & VLT

values.

4. Note down the readings from the output waveform.

5. Plot the graph & show the relationship between Input sine wave & Output

square wave.

RESULT:

Thus an Astable, Monostable multivibrator and Schmitt trigger are

designed and tested using op-amp IC 741.

www.vidyarthiplus.com

36

Integrated Circuits. www.vidyarthiplus.com

Dept of Electronics & Communication Engg

RC PHASE SHIFT OSCILLATOR:147452-Linear

CIRCUIT DIAGRAM:Rf=1M

+15v

R1=33K

R1//Rf

33K

C=0.1f

C=0.1f0

7

IC 741

-15v

C=0.1f

+

CRO

-

R=3.3K

R=3.3K

R=3.3K

TABULATION:.

OBSERVED OUTPUT WAVEFORM

Amplitude

Time period

Frequency

(volts)

(ms)

(Hz)

Design Frequency

(Hz)

MODEL GRAPH:

Vout

OUTPUT

Time (ms)

www.vidyarthiplus.com

37

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

RC PHASE SHIFT AND WIEN BRIDGE OSCILLATOR

USING OP-AMP

EXP.NO: 06

DATE:

AIM:

To design RC Phase Shift and Wien Bridge Oscillator using op-amp IC

741 and to test its performance.

APPARATUS REQUIRED:

S.NO

COMPONENTS

1.

IC 741

2.

RESISTORS

3.

CAPACITORS

4.

DIGITAL TRAINER KIT

5.

CATHODE RAY OSCILLOSCOPE

6.

CONNECTING WIRES

RANGE

QUANTITY

---

01

1.5K 3.3K, 33K,

EACH 03

10 K 22 K, 1M,

EACH 01

0.1f

03

---

01

(0-30)MHz

01

---

FEW

THEORY:

RC phase shift oscillator produces 360 of phase shift in two parts. Firstly,

each and every RC pair in the feedback network produces 60 phase shift and totally

there were three pairs, thus producing 180 Phase shift and secondly, the feedback

input is given to the inverting terminal of op-amp to produce another 180 phase shift

and a total phase shift of 360.

1

The frequency of oscillation is given by f0 =

2

; If an inverting

6 RC

amplifier is used, the gain must be atleast equal to 29 to ensure the oscillations with

constant amplitude that is, AV

< 1. Otherwise the oscillation will die out.

DESIGN PROCEDURE:

Design a RC phase shift oscillator to oscillate at 200Hz.

1. Select fo = 200Hz.

2. Assume C = 0.1f & determine R from fo.

1

1

fo =

=R=

= 3.3K.

2 6 f oc

2 6 RC

3. To prevent the loading of amp because it is necessary that R1>>10R.

Therefore R1=10R=33K.

4. At this frequency the gain must be atleast 29 (i.e)Rf / R1 =29.

Therefore Rf = 29R1.

Rf = 29 (33K) = 957K.

Therefore use Rf = 1M.

www.vidyarthiplus.com

38

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

WIEN BRIDGE OSCILLATOR:CIRCUIT DIAGRAM:-

Rf=22K

R1=10K

+15v

2

IC 741

R=1.5K

-15v

C=0.1uf

+

CRO

C=0.1uf

R=1.5K

TABULATION:

OBSERVED OUTPUT WAVEFORM

Amplitude

Time period

Frequency

(volts)

(ms)

(Hz)

Design Frequency

(Hz)

MODEL GRAPH:

Vout

OUTPUT

Time (ms)

www.vidyarthiplus.com

39

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

PROCEDURE- (RC PHASE SHIFT):1. Select the given frequency of oscillation f0 = 200Hz.

2. Assume either R or C to find out the other using formula f0 =

.

2 6 RC

3. The gain is selected such that Rf / R1 = 29K. Assume Rf or R1 to find the other.

4. Connect the circuit as per as the circuit diagram.

5. Measure the amplitude frequency of the output signal plot the graph.

THEORY (WIEN BRIDGE):A bridge circuit with two components connected in series and parallel

combination is used to archived the required of phase shift of 00. When the bridge is

balanced the phase shift of 00 is achieved and the feedback signal is connected to the

positive terminal; of Op-amp. So the Op-amp is acting as a non-inverting amplifier

and the feedback network do not provide any phase shift.

The major drawback of wien bridge oscillator is difficulty in balancing

the bridge circuit. This occurs because of drift in component values due to external

and internal disturbances. The frequency of oscillation is given as f0 =

1

.

2 RC

DESIGN PROCEDURE:

(i)

Select frequency f0 = 1KHz.

1

(ii)

Use f0 =

, A = 1+(Rf / R1) = 3. To find R & Rf.

2 RC

(iii) Therefore Rf = 2R1 & assume C = 0.1f & find R from

1

R=

= 1.59K.

2 f oC

(iv)

Assume R1 = 10K & find Rf from Rf = 2R1

Therefore Rf = 20K 22K

PROCEDURE:

1. Select the given frequency of oscillation f0 = 1 KHz.

2. Assume either R or C to find out the other using formula

1

. Also

2 RC

determine the value of other components as given in design procedure.

3. Connect the circuit as per as the circuit diagram.

4. Measure the amplitude and frequency of the output signal to plot the graph.

RESULT:

Thus RC Phase Shift and Wien Bridge Oscillator were designed and

tested using op-amp IC 741.

www.vidyarthiplus.com

40

147452-Linear

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Integrated Circuits.

PIN CONFIGURATION OF 555 TIMER IC

Features of 555 IC:1. The load can be connected to o/p in two ways i.e. between pin 3 & ground 1 or

between pin 3 & VCC (supply)

2. 555 can be reset by applying negative pulse, otherwise reset can be connected to

+Vcc to avoid false triggering.

3. An external voltage effects threshold and trigger voltages.

4. Timing from micro seconds through hours.

5. Monostable and bistable operation

6. Adjustable duty cycle

7. Output compatible with CMOS, DTL, TTL

8. High current output sink or source 200mA

9. High temperature stability

10. Trigger and reset inputs are logic compatible.

Specifications:1. Operating temperature

2.

3.

4.

5.

:

:

:

:

Supply voltage

Timing

Sink current

Temperature stability

SE 555-- -55oC to 125oC

NE 555-- 0o to 70oC

+5V to +18V

Sec to Hours

200mA

50 PPM/oC change in temp or 0-005% /oC.

Applications:1.

2.

3.

4.

5.

6.

7.

8.

9.

Monostable and Astable Multivibrator

dc-ac converters

Digital logic probes

Waveform generators

Analog frequency meters

Tachometers

Temperature measurement and control

Infrared transmitters

Regulator & Taxi gas alarms etc.

www.vidyarthiplus.com

41

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Block Diagram of IC 555:

Function of Various Pins of 555 IC:

Pin (1) of 555 is the ground terminal; all voltages r measured with respect to this pin.

Pin (2) of 555 is the trigger terminal, If the voltage at this terminal is held greater than

one-third of VCC, the output remains low. A negative going pulse from Vcc to less

than Vec/3 triggers the output to go high. The amplitude of the pulse should be able to

make the comparator (inside the IC) change its state. However the width of the

negative going pulse must not be greater than the width of the expected output pulse.

Pin (3) is the output terminal of IC 555. There are 2 possible output states. In the

low output state, the output resistance appearing at pin (3) is very low (approximately

10 ). As a result the output current will goes to zero , if the load is connected from

Pin (3) to ground , sink a current I Sink (depending upon load) if the load is connected

from Pin (3) to ground, and sinks zero current if the load is connected between +VCC

and Pin (3).

Pin (4) is the Reset terminal. When unused it is connected to +Vcc. Whenever the

potential of Pin (4) is drives below 0.4V, output is immediately forced to low state.

The reset terminal enables the timer over-ride command signals at Pin (2) of the IC.

Pin (5) is the Control Voltage terminal. This can be used to alter the reference levels

at which the time comparators change state. A resistor connected from Pin (5) to

ground can do the job. Normally 0.01F capacitor is connected from Pin (5) to

ground. This capacitor bypasses supply noise and does not allow it affect the

threshold voltages.

Pin (6) is the threshold terminal. In both Astable as well as Monostable modes, a

capacitor is connected from Pin (6) to ground. Pin (6) monitors the voltage across the

capacitor when it charges from the supply and forces the already high O/p to Low

when the capacitor reaches +2/3 VCC.

Pin (7) is the discharge terminal. It presents an almost open circuit when the output is

high and allows the capacitor charge from the supply through an external resistor and

presents an almost short circuit when the output is low.

Pin (8) is the +Vcc terminal. 555 can operate at any supply voltage from +3 to +18V.

42

www.vidyarthiplus.com

147452-Linear

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Integrated Circuits.

CIRCUIT DIAGRAM - (ASTABLE):

+5V

6.8K

RA

HI

3.3K

RB

IC 555

6

+

CRO Vo

-

Vc

0.01uf

C=0.1f

TABULATION:

Waveforms

Amplitude

(volts)

DESIGN VALUE

tH

tL

(ms)

(ms)

(ms)

OBSERVED VALUE

F

(Hz)

tH

tL

(ms)

(ms)

(ms)

F

(Hz)

Output

waveform

Capacitor

waveform

(Capacitor

voltage Vc)

www.vidyarthiplus.com

43

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

ASTABLE & MONOSTABLE MULTIVIBRATOR

USING IC 555 TIMER.

EXP.NO: 07

DATE:

AIM:

To Design and test Astable and Monostable multivibrator using 555 timer IC.

APPARATUS REQUIRED:

S.NO

COMPONENTS

RANGE

QUANTITY

---

01

3.3K,6.8K,10K.

EACH 01

0.1f, 0.01f.

EACH01

1.

IC 555

2.

RESISTORS

3.

CAPACITORS

4.

DIGITAL TRAINER KIT

---

01

5.

SIGNAL GENERATOR

(0-3)MHz

01

6.

CATHODE RAY OSCILLOSCOPE

(0-30)MHz

01

7.

CONNECTING WIRES

---

FEW

THEORY:

When the power supply VCC is connected, the external timing capacitor C

charges towards VCC with a time constant (RA+RB) C. During this time, pin 3 is high

(VCC) as Reset R=0, Set S=1 and this combination makes Q = 0 which has

unclamped the timing capacitor C.

When the capacitor voltage equals 2/3 VCC, the upper comparator triggers the

control flip flop on that Q =1. It makes Q1 ON and capacitor C starts discharging

towards ground through RB and transistor Q1 with a time constant RBC. Current also

flows into Q1 through RA. Resistors RA and RB must be large enough to limit this

current and prevent damage to the discharge transistor Q1. The minimum value of R A

is approximately equal to VCC/0.2 where 0.2A is the maximum current through the

ON transistor Q1.

During the discharge of the timing capacitor C, as it reaches VCC/3, the lower

comparator is triggered and at this stage S=1, R=0 which turns Q =0. Now Q =0

unclamps the external timing capacitor C. The capacitor C is thus periodically

charged and discharged between 2/3 VCC and 1/3 VCC respectively. The length of

time that the output remains HIGH is the time for the capacitor to charge from 1/3

VCC to 2/3 VCC.

The capacitor voltage for a low pass RC circuit subjected to a step input of VCC

volts is given by VC = VCC [1- exp (-t/RC)]

Total time period T = 0.69 (RA + 2 RB) C

f = 1/T = 1.44/ (RA + 2RB) C

www.vidyarthiplus.com

44

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

MODEL GRAPH:

(a): Square wave output

(b): Capacitor voltage of Square wave output

www.vidyarthiplus.com

45

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

DESIGN PROCEDURE:Design of Astable multivibrator of operation frequency = 1 KHz & duty cycle of 30%

using 555 timer IC.

Given Frequency=1000Hz

Duty cycle=30%

D= T low/T high = RB/RA+2RB*100 -----------------------------------(1)

T high =0.69(RA+RB)C

T low = 0.69 RBC

From equation 1

0.30 T high = T low

0.30 * 0.69(RA+RB)C = 0.69 RBC

0.201(RA+RB)C = 0.69 RBC

0.483 RB-0.207 RA= 0 -----------------------------------------------(2)

given f=1khz we know that T=1/f

T=1ms

T= T high + T low

0.69(RA+RB)C +0.69 RBC= 1ms.

0.69(RA+RB) +0.69 RB = 1ms./C

Let C=0.1F

0.69RA+0.69RB +0.69 RB = 1ms./0.1*10-6

0.69RA+1.38RB = 10 4 ------------------------------------------------(3)

Solving equation 2 & 3 we get

RA=6.8K

RB= 2.674K 3.3K

Procedure:

1. Calculate the component values using the design procedure.

2. Connect the circuit as shown in the circuit diagram.

3. Observe and note down the output waveform.

4.

Measure the frequency of oscillations and duty cycle and then compare with

the given values.

5. Plot both the waveforms to the same time scale in a graph.

www.vidyarthiplus.com

46

147452-Linear

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Integrated Circuits.

MONOSATBLE MULTIVIBRATOR:CIRCUIT DIAGRAM:HI

+5V

10K

7

IC 555

6

0.1uf

Vc

+

CRO Vo

Trigger

Input

Vin

0.01uf

TABULATION:

S.No

Waveforms

1.

Input waveform

2.

Output waveform

3.

Capacitive waveform

(Capacitor voltage Vc)

Amplitude

(volts)

Time period

(ms)

MODEL GRAPH:

www.vidyarthiplus.com

47

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

THEORY- (MONOSATBLE):A Monostable Multivibrator, often called a one-shot Multivibrator, is a pulsegenerating circuit in which the duration of the pulse is determined by the RC network

connected externally to the 555 timer. In a stable or stand by mode the output of the

circuit is approximately Zero or at logic-low level. When an external trigger pulse is

given, the output is forced to go high ( VCC). The time for which the output remains

high is determined by the external RC network connected to the timer. At the end of

the timing interval, the output automatically reverts back to its logic-low stable state.

The output stays low until the trigger pulse is again applied. Then the cycle repeats.

The Monostable circuit has only one stable state (output low), hence the name

Monostable. Normally the output of the Monostable Multivibrator is low.

DESIGN PROCEDURE:Let, RA = 10K

Out put pulse width tp = 10s

tp=1.1RAC

C= 0.909F

C=0.1F

PROCEDURE:1. Calculate the value of R & C using design procedure.

2. Connect the circuit as shown in the circuit diagram.

3. Apply Negative triggering pulses at pin 2 of frequency 1 KHz.

4. Observe the output waveform and measure the pulse duration.

5. Theoretically calculate the pulse duration as Thigh=1.1 RAC

RESULT:

Thus the Astable and Monostable multivibrator is designed and tested using

555 timer IC

www.vidyarthiplus.com

48

147452-Linear

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Integrated Circuits.

Pin Configuration:

Specifications:

1. Operating frequency range

0.001 Hz to 500 KHz

2. Operating voltage range

6 to 12V

3. Inputs level required for tracking

10mV rms minimum to 3v (p-p)

4. Input impedance

10 K typically

5. Output sink current

1mA typically

6. Drift in VCO center frequency

300 PPM/oC typically

1.5%/V maximum

8. Triangle wave amplitude

typically 2.4 VPP at 6V

9. Square wave amplitude

typically 5.4 VPP at 6V

10. Output source current

10mA typically

11. Bandwidth adjustment range

<1 to > 60%

max.

(fout) with temperature

7. Drif in VCO centre frequency with

supply voltage

Center frequency fout = 1.2/4R1C1 Hz

= free running frequency

FL = 8 fout/V Hz

V = (+V) (-V)

fc =

fL

2 (3.6) x10 3 xC 2

1/ 2

Applications:

1. Frequency multiplier

2. Frequency shift keying (FSK) demodulator

3. FM detector

www.vidyarthiplus.com

49

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

PLL IC 565

THEORY:The Signetics SE/NE 560 series is monolithic phase locked loops. The SE/NE

560, 561, 562, 564, 565, & 567 differ mainly in operating frequency range, power

supply requirements and frequency and bandwidth adjustment ranges. The device is

available as 14 Pin DIP package and as 10-pin metal can package. Phase comparator

or phase detector compare the frequency of input signal fs with frequency of VCO

output fo and it generates a signal which is function of difference between the phase of

input signal and phase of feedback signal which is basically a d.c voltage mixed with

high frequency noise. LPF remove high frequency noise voltage. Output is error

voltage. If control voltage of VCO is 0, then frequency is center frequency (f o) and

mode is free running mode. Application of control voltage shifts the output frequency

of VCO from fo to f. On application of error voltage, difference between fs & f tends

to decrease and VCO is said to be locked. While in locked condition, the PLL tracks

the changes of frequency of input signal.

Block Diagram of IC 565

PROCEDURE:

1. Determine the component values using the design procedure given here.

2. Connect the components as shown in the circuit diagram.

3. Note down the readings of output waveform with respect to input signal.

www.vidyarthiplus.com

50

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

CIRCUIT DIAGRAM:

NE 565 PLL connection diagram

DESIGN PROCEDURE:If C= 0.01F and the frequency of input trigger signal is 2KHz, output pulse

width of 555 in Monostable mode is given by

1.1RAC = 1.2T =1.2/f

RA= 1.2/(1.1Cf)=54.5K

fIN=fOUT/N

Under locked conditions,

fOUT = NfIN = 2fIN = 4KHz

www.vidyarthiplus.com

51

147452-Linear

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Integrated Circuits.

PLL CHARACTERISTICS AND FREQUENCY

MULTIPLIER USING PLL

EXP.NO: 08

AIM:

DATE:

To design & test the characteristics of PLL and to construct and test frequency

multiplier using PLL IC565.

APPARATUS REQUIRED:

S.NO

COMPONENT

VALUE

QUANTITY

IC 565

---

01

IC 555

---

01

RESISTORS

12K, 54.5 K,

6.8K

Each one

0.01F

0.1 f, 10f, 1 f

EACH 01

---

01

CAPACITORS

DIGITAL TRAINER KIT

REGULATED POWER SUPPLY

(0 -30V), 1A

CATHODE RAY OSCILLOSCOPE

(0 30MHz)

CONNECTING WIRES

---

FEW

www.vidyarthiplus.com

52

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

PLL as Frequency Multiplier

(a): Input

(b): PLL output under locked conditions without 555

(c): Output at pin4 of 565 with 555 connected in the feedback

www.vidyarthiplus.com

53

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Theory:

The frequency divider is inserted between the VCO and the phase

comparator of PLL. Since the output of the divider is locked to the input frequency

fIN, the VCO is actually running at a multiple of the input frequency .The desired

amount of multiplication can be obtained by selecting a proper divide by N

network ,where N is an integer. To obtain the output frequency fOUT=2fIN, N = 2 is

chosen. One must determine the input frequency range and then adjust the free

running frequency fOUT of the VCO by means of R1 and C1 so that the output

frequency of the divider is midway within the predetermined input frequency range.

The output of the VCO now should be 2fIN . The output of the VCO should be

adjusted by varying potentiometer R1. A small capacitor is connected between pin7

and pin8 to eliminate possible oscillations. Also, capacitor C2 should be large enough

to stabilize the VCO frequency.

SAMPLE READINGS:

PARAMETER

INPUT

OUTPUT

Amplitude (Vp-p)

Frequency (KHz)

PROCEDURE:1. The circuit is connected as per the circuit diagram.

2. Apply a square wave input to the pin2 of the 565

3. Observe the output at pin4 of 565 under locked condition.

4. Give the output of 565 to the pin2 of 555 IC.

5. Observe the output of 555 at pin3.

6. Now give the output of 555 as feedback to the pin5 of the 565.

7. Observe the frequency of output signal fo at pin4 of 565 IC.

8. Plot the waveforms in graph.

RESULT:

Thus the PLL characteristics are designed and tested and Frequency multiplier

using IC 565 is constructed and tested.

www.vidyarthiplus.com

54

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

PIN DIAGRAM:

CIRCUIT DIAGRAM - (LM723):

HI

Vref=5V

HI

Vin (0-30) V

12

11

10

R4=100E

Vo

R1=1K

IC 723

5

R2=3.3K

3

R3=30E

7

13

4

C=220pf

www.vidyarthiplus.com

55

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

DC POWER SUPPLY USING LM317 AND LM723.

EXP.NO: 09

DATE:

AIM:

To design and test the power supply voltage regulator using LM317 and

LM723

APPARATUS REQUIRED:

S.NO

COMPONENTS

RANGE

QUANTITY

---

EACH 01

30, 100, 1K,

3.3K, 220,

EACH 01

1.

LM317 and LM723

2.

RESISTORS

3.

DIGITAL TRAINER KIT

---

01

4.

ANALOG VOLTMETER

(0-10)V

01

5.

DUAL POWER SUPPLY

(0-30)V

01

THEORY:

A voltage regulator is a circuit that supplies a constant voltage regardless of

changes in load current and input voltage variations. Using IC 723, we can design

both low voltage and high voltage regulators with adjustable voltages.

For a low voltage regulator, the output VO can be varied in the range of

voltages Vo < Vref, where as for high voltage regulator, it is VO > Vref. The voltage

Vref is generally about 7.5V. Although voltage regulators can be designed using Opamps, it is quicker and easier to use IC voltage Regulators.

IC 723 is a general purpose regulator and is a 14-pin IC with internal short

circuit current limiting, thermal shutdown, current/voltage boosting etc. Furthermore

it is an adjustable voltage regulator which can be varied over both positive and

negative voltage ranges. By simply varying the connections made externally, we can

operate the IC in the required mode of operation. Typical performance parameters are

line and load regulations which determine the precise characteristics of a regulator

www.vidyarthiplus.com

56

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

TABULATION:

S.NO

INPUT VOLTAGE

(Volts)

OUTPUT VOLTAGE

(Volts)

1.

2.

3.

4.

5.

6.

7.

8.

MODEL GRAPH:

www.vidyarthiplus.com

57

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

CHARACTERISTICS OF THE LM317HVK:

The LM317HVK will provide a regulated output current of upto

1.5A,Provided that if is not subjected to a power dissipation of more than about

15W.This means it should be electrically isolated from, and fastened to, a large heat

sink such as the metal chassis of the power supply.

The LM317 requires a minimum dropout voltage of 3v across its input and

output terminals or it will drop out of regulation. Thus the upper limit of Vo is 3V

below the minimum input voltage from the unregulated supply.

It is good practice to connect bypass capacitors .This reduces the ripple

voltage from the rectifier.

The LM317HVK protects itself against over heating, too much internal power

dissipation and too much current. When the chip temperature reaches 175 degrees, the

317 shuts down. If the product of output current and input-to-output voltage exceeds

15 to 20W, or if currents greater than about 1.5A are required the LM317 also shuts

down. When the overload condition is removed the Operation is resumed. All these

features are made possible by the remarkable internal circuitry of LM317.

Along with the simple 3 pin fixed regulators; a number of adjustable or

programmable devices are available. Some devices also include features such as

programmable current limiting. It is also possible to configure multiple regulators so

that they track or follow each other.

DESIGN PROCEDURE: (IC723)

Given :

Vref =5v

Vo=4v

We know that

Vo=Vref(R2/(R1+R2))

4R1+4R2=5R2

R2=4R1

Let R1=1k

R2=4K

3.3K

www.vidyarthiplus.com

58

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

PIN DIAGRAM:

CIRCUIT DIAGRAM - (LM317):

MODEL GRAPH:

www.vidyarthiplus.com

59

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

TABULATION:

S.NO

INPUT VOLTAGE

(Volts)

OUTPUT VOLTAGE

(Volts)

PROCEDURE:

1) Connections are made as per the circuit diagram.

2) The reference voltage of 5v is set and the input voltage is varied between (0-30) v

3) The corresponding output is taken using voltmeter.

4) The readings are tabulated and the graph is plotted.

RESULT:

The 723 & 317 voltage regulators are designed and the regulation of supply voltage

was tested.

www.vidyarthiplus.com

60

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

PIN DETAILS:

PIN NO.

FUNCTION

Inverting input

Non Inverting input

Oscillator output

(+)CL sense

(-)CL sense

RT

CT

Ground(-ve supply voltage)

Compensation

10

Shutdown

11

Emitter-A

12

Collector-A

13

Collector-B

14

Emitter-B

15

Vin

16

Vref

TECHNICAL INFROMATION:

DESCRIPTION

TEMPERATURE

RANGE

SG3524N(16-pin plastic DIP)

0 C to 70 C

SG3524F(16-pin cerdip)

0 C to 70 C

SG3524D(16-pin SO)

0 C to 70 C

www.vidyarthiplus.com

61

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

STUDY OF SMPS

EXP.NO: 10

DATE:

AIM:

To study the control of SMPS

THEORY:

The switching regulator is also called as switched mode regulator. In

this case, the pass transistor is used as a controlled switch and is operated at either

cutoff or saturated state. Hence the power transmitted across the pass device is in

discrete pulses rather than as a steady current flow. Greater efficiency is achieved

since the pass device is operated as a low impedance switch. When the pass device is

at cutoff, there is no current and dissipated power. Again when the pass device is in

saturation, a negligible voltage drop appears across it and thus dissipates only a small

amount of average power, providing maximum current to the load. The efficiency is

switched mode power supply is in the range of 70-90%.

A switching power supply is shown in figure. The bridge rectifier and

capacitor filters are connected directly to the ac line to give unregulated dc input. The

reference regulator is a series pass regulator. Its output serves as a power supply

voltage for all other circuits. The transistors Q1, Q2 are alternatively switched on &;

off, these transistors are either fully on or cut-off, so they dissipate very little

power. These transistors drive the primary of the main transformer. The secondary is

centre tapped and full wave rectification is achieved by diodes D1 and D2. This

unidirectional square wave is next filtered through a two stage LC filter to produce

output voltage Vo.

SG 3524:

FUNCTION:

Switched Mode Power Supply Control Circuit

FEATURES:

Complete PWM Power Controlled circuitry.

Single ended or push-pull outputs.

Line and Load regulation of 0.2%.

1% maximum temperature variation.

Total Supply current is less than 10mA

Operation beyond 100KHz

RESULT:

Thus the control of SMPS IC SG3524 had been studied.

www.vidyarthiplus.com

62

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Instrumentation Amplifier:

www.vidyarthiplus.com

63

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Program:

.LIB EVAL.LIB

VCC1 4

0

VEE1 0

5

VCC2 9

0

VEE2 0

10

VCC3 14 0

VEE3 0

15

V1 7

0

V2 1

0

R1 3

2

R2 8

6

R3 2

6

R4 3

11

R5 8

12

RF 11

13

R6 12

0

X1 1

2

X2 7

6

X3 12

11

.TRAN 0 20MS

.OP

.PROBE

.END

DC 15

DC 15

DC 15

DC 15

DC 15

DC 15

SIN(0 5V 100)

SIN(0 3V 100)

1K

1K

500

1K

1K

1K

1K

4

5

3

9

10

8

14

15

13

UA741

UA741

UA741

www.vidyarthiplus.com

64

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Lowpass Filter:

www.vidyarthiplus.com

65

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Program:

.LIB EVAL.LIB

VCC 5

0

DC

VEE 0

6

DC

VIN 2

0

AC

R1 1

0

22K

R2 1

4

22K

R3 2

3

1.5K

RL 4

0

10K

C1 3

0

0.1U

X1 3

1

5

.AC DEC 10 10 1MEG

.OP

.PROBE

.END

15

15

4

UA741

www.vidyarthiplus.com

66

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Highpass Filter:

www.vidyarthiplus.com

67

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Program:

.LIB EVAL.LIB

VCC 5

0

DC

VEE 0

6

DC

VIN 2

0

AC

R1 1

0

22K

R2 1

4

22K

C1 2

3

0.1U

RL 4

0

10K

R3 3

0

1.5K

X1 3

1

5

.AC DEC 10 10 100K

.OP

.PROBE

.END

15

15

4

UA741

www.vidyarthiplus.com

68

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Active Bandpass Filter:

www.vidyarthiplus.com

69

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Program:

.LIB EVAL.LIB

VCC 5

0

DC 15

VEE 0

6

DC 15

VCC110

0

DC 15

VEE1 0

11

DC 15

VIN 2

0

AC 4

R1 1

0

22K

R2 1

4

22K

R3 3

0

1.5K

R4 4

7

1.5K

R5 8

0

22K

R6 8

9

22K

RL 9

0

10K

C1 2

3

0.1U

C2 7

0

0.01U

X1 3

1

5

6

X2 7

8

10

11

.AC DEC 10 10 10MEG

.OP

.PROBE

.END

4

9

UA741

UA741

www.vidyarthiplus.com

70

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Astable Multivibrator:

www.vidyarthiplus.com

71

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Program:

.LIB EVAL.LIB

VCC 4

0

DC 15

VEE 0

5

DC 15

R1 2

0

10K

R2 2

3

11.6K

R3 1

3

50K

C1 1

0

0.01U

X1 2

1

4

5

.TRAN 0 5MS UIC

.OP

.PROBE

.END

UA741

www.vidyarthiplus.com

72

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Monostable Multivibrator:

www.vidyarthiplus.com

73

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Program:

.LIB EVAL.LIB

VCC 6

0

DC 15

VEE 0

7

DC 15

VIN 4 0 PULSE(4 0

1MS 0.001MS 0.001MS 1MS 2MS)

R1 5

2

10K

R2 2

0

10K

R3 1

5

50K

R4 3

0

100

C1 4

3

0.1U

C2 0

1

0.1U

D1 1

0

D1N4148

D2 2

3

D1N4148

X1 2

1

6

7

5

UA741

.TRAN 0 20MS

.OP

.PROBE

.END

www.vidyarthiplus.com

74

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Schmitt Trigger:

www.vidyarthiplus.com

75

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Program:

.LIB.EVAL.LIB

VCC 5

0

VEE 0

6

VIN 1

0

R1 3

0

R2 3

4

R3 1

2

RL 4

0

X1 3

2

.TRAN 0 30MS

.OP

.PROBE

.END

DC 15

DC 15

SIN(0 4 100)

10K

100K

10K

10K

5

6

4

UA741

www.vidyarthiplus.com

76

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

RC Phase shift Oscillator:

www.vidyarthiplus.com

77

147452-Linear

Integrated Circuits.

www.vidyarthiplus.com

Dept of Electronics & Communication Engg

Program:

.LIB EVAL.LIB

VCC 7

0

VEE 0

8

IS

3

0

50US 0MA

R1 1

2

R2 2

4

R3 5

0

R4 6

0

R5 1

0

R6 3

0

C1 5

4

C2 6

5